# Welcome! Texas Instruments New Product Update

- This webinar will be recorded and available at <u>www.ti.com/npu</u>

- Phone lines will be muted

- Please post questions in the chat or contact your sales person or field applications engineer

.

# New Product Update: Keep your system safe and accurate through Voltage References & Supervisors

Shridhar More Marcoo Zamora 18<sup>th</sup> March 2021

# **Agenda**

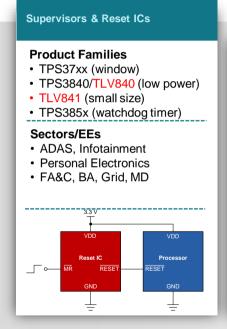

# **Product Family Overview**

## Series References **Product Families** REF70xx/REF50xx (precision) • REF33xx (low power) • REF34xx/REF4132 (gen. purpose) Sectors/Customers Factory automation - PLC · Medical - BGM Automotive HEV/EV Reference MCU

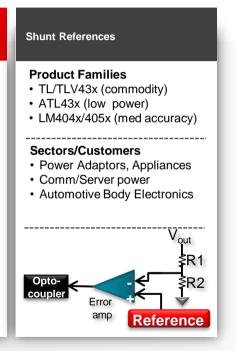

Voltage References & Supervisors on Tl.COM

# **Key Investment Areas**

Automotive

Technology Highlights:

- Wide V<sub>IN</sub> operation

- · Highest accuracy across temperature

- Functional Safety compliant

Industrial

Technology Highlights:

- · Lowest quiescent current

- · Smallest form factor

- · Lowest output noise

6

# REF70xx The Best VREF yet.

### Industry lowest noise 0.1Hz - 10Hz

Enhanced signal integrity to improve system-level accuracy by increasing overall SNR

### **Best initial accuracy**

±0.025%

Out of the box accuracy

### Best temperature drift over temperature

2ppm/°C

1ppm/°C (-40°C to 85°C)\*

Minimizes error sources from thermal variation

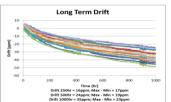

1000 hr Low Long Term Drift

Ceramic (5x5mm)

28ppm

Minimizes error sources from aging and thermal cycling to enable best product lifetime performance at highest possible precision

# **Supervisor & Reset IC – New device familie**

### Pin compatible - Lower cost

<u>EE</u> – Industrial, GI, PoS, STB etc <u>TLV8xxE</u> – SC70-3, SOT23-3

Competition families – RT9818/9, MAX803/9, S-809, SGM803/9, DS1812, ADM803/9 etc

#### TLV840 - SOT23-5, SC82

Competition families – NCP30x, S-1003/9, S-1910, S-809, PST81/2, BD53, BU42, XC6118, R3116 etc

#### **Small size**

EE – Comms Infra, Personal Electronics, Handheld instruments TLV841 – Industry smallest (0.73mm\*0.73mm) WCSP supervisor TLV8xxE – X2SON package (1mm \* 1mm)

TPS3899 – Sense delay feature + Sense in small DSE package (1.5mm \* 1.5mm)

### Nano Io

<u>EE</u> –Power tools, Battery powered appliances TLV840, TLV841, TPS3899 – 120nA

**TYP**

#### TLV8xxE - 250nA TYP

Longer battery life.

Monitor high voltage supplies through resistance divider

### Specified low V<sub>POR</sub> & V<sub>DDMIN</sub>

<u>EE</u> – Industrial, GI, Medical, TnM TLV840, TLV841, TPS3899 –

0.7V V<sub>POR</sub>

0.85V V<sub>DDMIN</sub> Active low

1V V<sub>DDMIN</sub> Active High

Specified across Industrial -40°C to 125°C temperature range.

V<sub>POR</sub> - Controlled RESET assert even at low supply level. Helps system stability over wide voltage range.

V<sub>DDMIN</sub> - Reliable supervision over wide voltage rail.

# Resources

Overview Products Applications Reference designs Technical documents Support & training

#### Voltage references – Technical documents

Voltage Reference Overview

Review the Shunt and Series selection quide parameters at a glance to choose the right VREF for your application.

Download (PDF 1130KB)

Tins and tricks for designing with voltage references

Tips and Tricks for Designing with Voltage References provides a comprehensive overview of voltage reference basics and application design.

Download (PDF 5486KB)

Voltage reference selection basics white paper (Rev. A)

Voltage references are a key building block in data conversion systems, and understanding their specifications and how they contribute to error is necessary for selecting the right reference for the application.

Download (PDF, 1231KB)

#### Supervisor & reset ICs - Technical documents

Voltage Supervisor and Reset ICs: Tips. Tricks and Basics

Get an introduction to voltage supervisors and an in-depth overview of their various applications.

Download (PDE 2025KB)

Voltage Supervisors (Reset ICs) Quick Reference Guide (Rev.

Check out our most popular supervisors and reset ICs.

Download (PDF, 422KB)

Read about the most frequently asked questions (FAQs) for voltage supervisors, reset ICs, voltage detectors, watchdog timers and all related monitoring devices.

Download (PDF, 387KB)

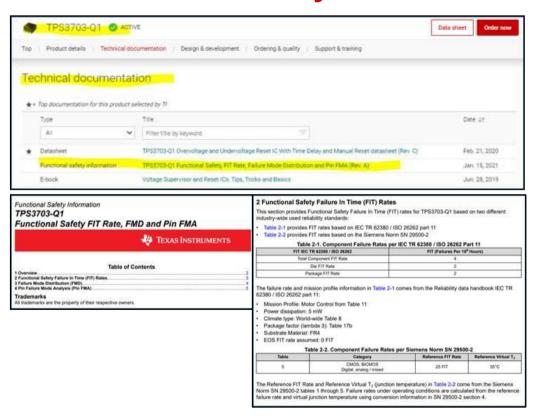

# **Functional Safety Documentation on TI.COM**

### 3 Failure Mode Distribution (FMD) The failure mode distribution estimation for TPS

The failure mode distribution estimation for TPS3703-Q1 in Table 3-1 comes from the combination of common failure modes listed in standards such as IEC 61508 and ISO 26262, the ratio of sub-circuit function size and complexity and from best engineering judgment.

The failure modes listed in this section reflect random failure events and do not include failures due to misuse or overstress.

#### Table 3-1. Die Failure Modes and Distribution

| Die Failure Modes                                   | Failure Mode Distribution (%) |  |

|-----------------------------------------------------|-------------------------------|--|

| nRESET fails to trip                                | 15%                           |  |

| nRESET false trip                                   | 15%                           |  |

| nRESET trip outside specification (voltage or time) | 65%                           |  |

| nRESET delay outside specification                  | 5%                            |  |

#### 4 Pin Failure Mode Analysis (Pin FMA)

This section provides a Failure Mode Analysis (FMA) for the pins of the TPS3703-Q1. The failure modes covered in this document include the typical pin-by-pin failure scenarios:

- Pin short-circuited to Ground (see Table 4-2)

- Pin open-circuited (see Table 4-3)

- . Pin short-circuited to an adjacent pin (see Table 4-4)

- Pin short-circuited to VDD (see Table 4-5)

- Pin short-circuited to /RESET is also included (see Table 4-6)

Table 4-2 through Table 4-6 also indicate how these pin conditions can affect the device as per the failure effects classification in Table 4-1.

#### Table 4-1. TI Classification of Failure Effects

| Class | Failure Effects                                              | -    |

|-------|--------------------------------------------------------------|------|

| A     | Potential device damage that affects functionality           | - 1  |

| 8     | No device damage, but loss of functionality                  | - 1  |

| c     | No device damage, but performance degradation                |      |

| D.    | No device damage, no impact to functionality or performance. | - 55 |

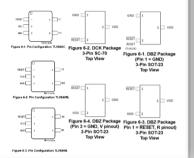

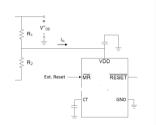

Figure 4-1 shows the TPS3703-Q1 pin diagram. For a detailed description of the device pins please refer to the Pin Configuration and Functions section in the TPS3703-Q1 data sheet.

| SENSE | 1 | 6. | MR    |

|-------|---|----|-------|

| VDD   | 2 | 8  | GND   |

| CT    | 3 | 4  | RESET |

#### Figure 4-1. Pin DiagramDSE Package 6-Pin WSON

Following are the assumptions of use and the device configuration assumed for the pin FMA in this section:

VDD = 3.3 V, V SENSE = 1.2 V, /RESET pulled-up to VDD unless stated otherwise

#### Table 4-2. Pin FMA for Device Pins Short-Circuited to Ground

| Pin Name | Pin No. | Description of Potential Failure Effect(s)                                                                     | Failure<br>Effect<br>Class |

|----------|---------|----------------------------------------------------------------------------------------------------------------|----------------------------|

| SENSE    | 1       | No damage to device, can affect application functionality. Shorts voltage supply to ground, increases current. | c                          |

| VDD      | 20      | No damage to device, can affect application functionality. Shorts voltage supply to ground, increases current. | C                          |

| CT       | 3.      | Normal operation, device in Latch mode. Usually has pull-down resistance to limit currEnt.                     | 0                          |

| RESET    | 40      | No damage to device, can affect application functionality. Forces heset to be asserted.                        | C                          |

| GND      | - 5     | Normal operation.                                                                                              | 0                          |

| MR       | 6       | Normal operation in some cases, but forces ireset to be asserted.                                              | C                          |

|          |         |                                                                                                                |                            |

# Visit <u>www.ti.com/npu</u>

For more information on the New Product Update series, calendar and archived recordings

### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated