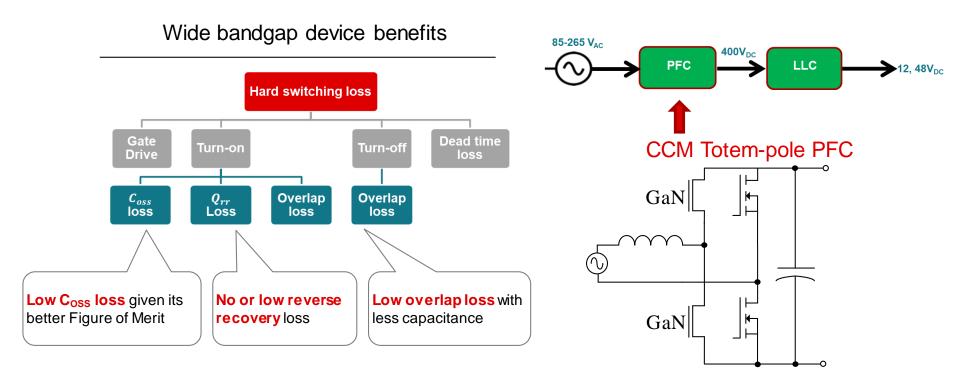

## Why wide bandgap device in hard-switching converters?

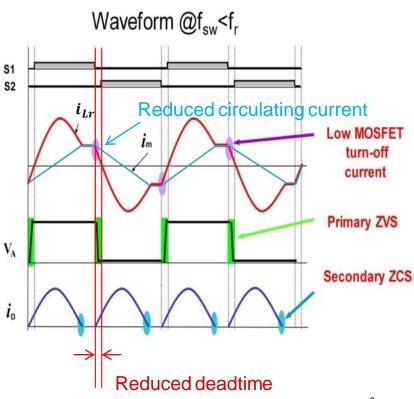

## Why wide bandgap device in soft-switching converters?

## Reduced output capacitance Coss

- Reduces dead-time

- Low transformer magnetizing current to minimize circulating current loss & eddy loss.

- Reduced turn-off overlap and gate driver losses

Negligible turn-off loss in TI GaN with gate driver integration

- High power density in system

- GaN enables higher  $f_{sw}$  to reduce magnetic components, and enables magnetic integration.

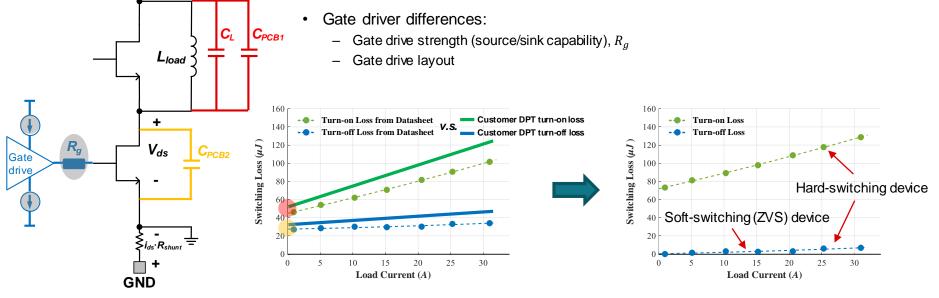

## 1) Why actual switching loss can be different from datasheet?

Interpret the datasheet loss correctly to applications

Double Pulse Test (DPT)

$V_{\text{bus}}$

Datasheet Loss

**Device Hard-switching Loss**

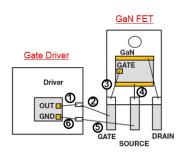

Gate driver layout affects switching loss

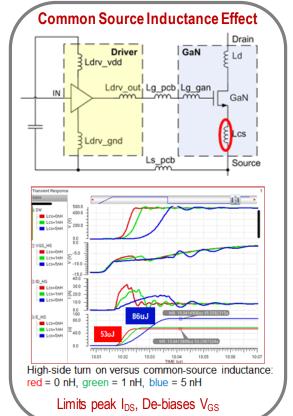

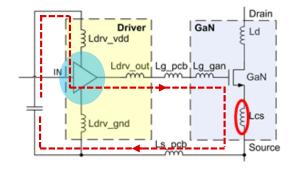

## Common Source Inductance (CSI)

- Slows V<sub>DS</sub> transitions.

- Higher overlap losses (Hard-Switching).

- Longer dead-times (Soft-Switching).

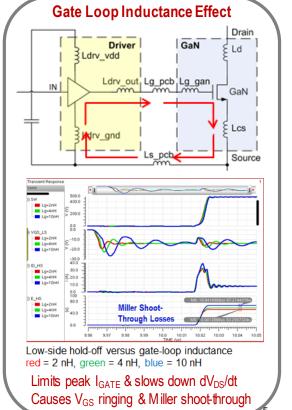

## Gate Loop Inductance

- Limit peak gate current: slow down gate drive and induce high overlap losses in hard switching.

- Gate overstress reliability risk.

- Miller shoot-through risk.

## **Gate drive optimizations**

## Discrete Layout in PCB

**Reduce cross-talk:** gate drivers with active miller clamping is preferred for high *dv/dt* operation.

Reduce gate loop inductance: Place bypass cap closer and use vertical loop in PCB.

**Reduce**  $L_{cs}$ : Kelvin source connection for gate drive loop

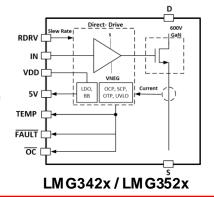

## Gate Drive Integration

#### **Gate driver integration benefits:**

- The gate loop inductance in between the driver and GaN is minimized.

- Gate drive strength and noise immunity are better controlled.

**Layout:** external bypass capacitor needs to be placed close to the driver supply.

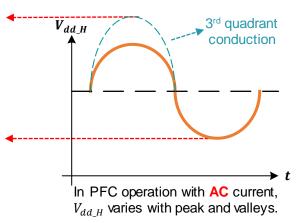

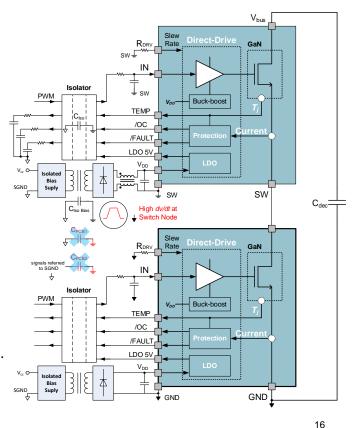

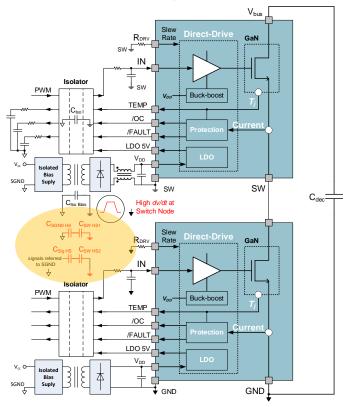

## 2) Why bootstrap needs proper designs in WBG devices?

Challenges in Bootstrap Circuit in GaN / SiC

$V_{dd\_H} \approx V_{dd_L} - V_{diode} - V_{GaN\_L} \approx V_{dd\_L} - V_{diode} - I_{ds_L} \cdot R_{ds,on\_L}$

The peak drive voltage can exceed the maximum  $V_{gs}$  rating in GaN devices.

The valley drive voltage can affect the on-resistance and switching speed of high-side devices.

#### Solutions:

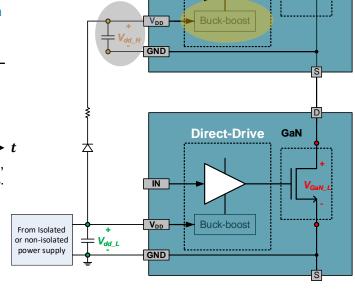

Add pre-regulation circuits (e.g. buck-boost converter) such that the output for drive voltage is stable.

**Direct-Drive**

GaN

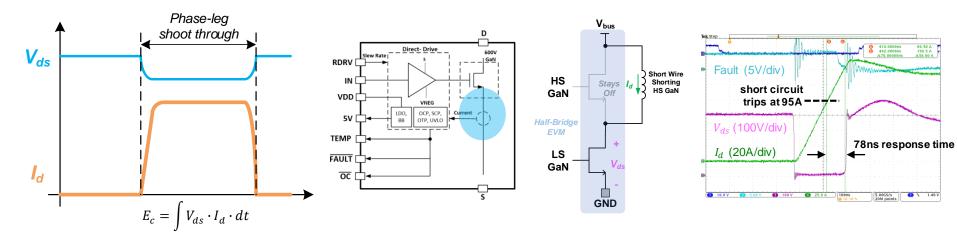

# 3) Why fast SCP is needed in WBG device?

- During short circuit, device is dissipating more energy and cause over-heating.

- SiC / GaN has smaller chip size, thus shorter short-circuit withstand time with less thermal capacity.

- Integrated Short Circuit Protection

- Provides fast response time with accurate tripping points.

- No external components.

Short Circuit Test Diagram

Short Circuit Test at 400V

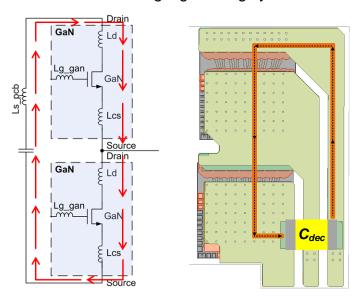

# 4) Why power loop layout is critical?

#### Large Power Loop Inductance will

- Increase ringing and cause EMI concerns

- Increase voltage spikes

- Induce noises causing signal integrity issue

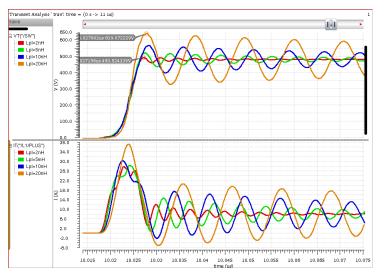

$V_{sw}$  ringing versus power loop inductance red = 2nH, green = 5nH, blue = 10nH, orange = 20nH

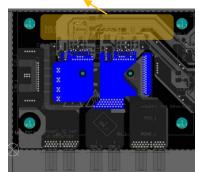

# Good practice for power loop layout

#### Good Practice Procedures

- Place GaN devices and decoupling capacitors close together.

- Use multiple ceramic decoupling capacitors with low-inductance.

- Vertical loop: use wide return path in the adjacent layer for inductance cancellation.

$$L_{ds} = 12.7 \text{ nH}$$

$$L_{ds} = 2.0 \text{ nH}$$

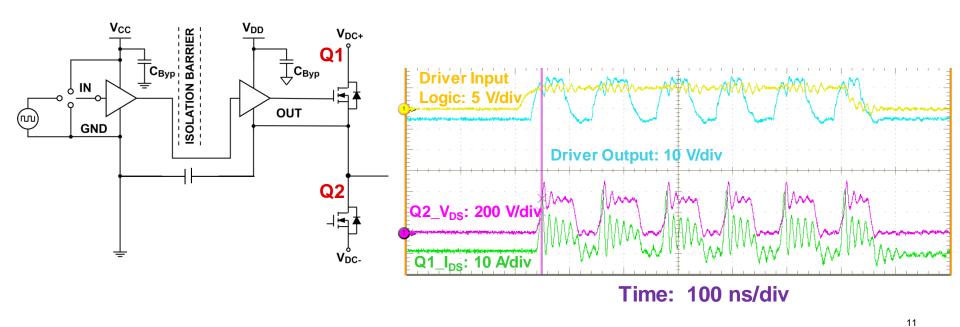

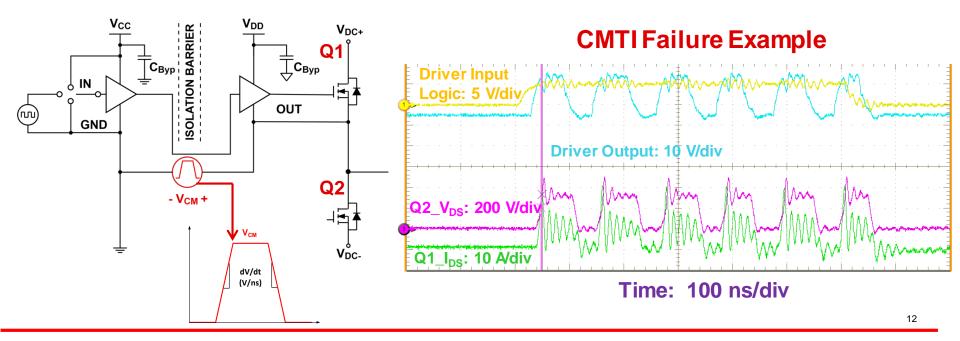

# 5) Why driver output doesn't follow input?

## 5) Isolated driver doesn't have enough CMTI capability

Without good common mode transient immunity (CMTI), parasitic noise currents could cause malfunction of the driver which includes <u>missing pulse</u>, <u>excessive</u> <u>propagation delay</u>, <u>high or low error</u> or <u>output latch</u>

6) Why a false signal on isolator output?

$V_{bus}$ The isolator's insufficient CMTI is causing the glitch at isolator output. Direct-Drive Solution Isolato Choose higher CMTI isolator Isolator with default low output is preferred Current An RC filter is recommend on the high-side isolator's output LDO 5V SW **Direct-Drive HS** Fault after 148V/ns dv/dt Isolator (2V/div) ~12ns **Buck-boost** LDO 5V *V<sub>ds</sub>* (60V/div) ■ LDO GND

13

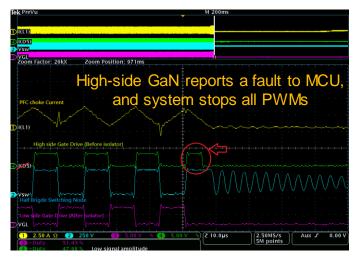

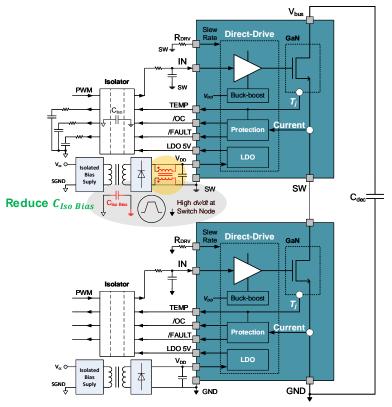

## 7) Why CMTI is critical for high-side isolated bias supply?

• Large  $C_{Iso\ Bias}$  induces common-mode noise to signal ground and affects signals like fault feedback or PWMs.

#### Solutions:

- Low coupling capacitance in the transformer and PCB layout.

- Add common mode choke.

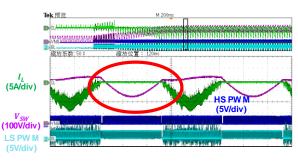

system stops switching at high dv/dt

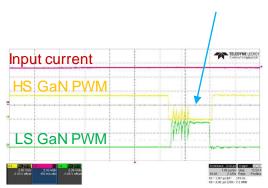

# 8) Why system cannot start at high dv/dt?

Root cause: the switch node has overlap with the <u>control</u> <u>ground</u> and signals leading to capacitive coupling noises.

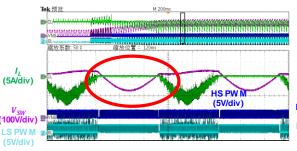

- No current in positive AC cycle

- LS GaN triggered fault

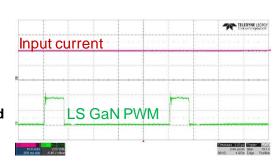

When LS GaN is turning on, HS PWM has a 1.8V noise causing shoot-through.

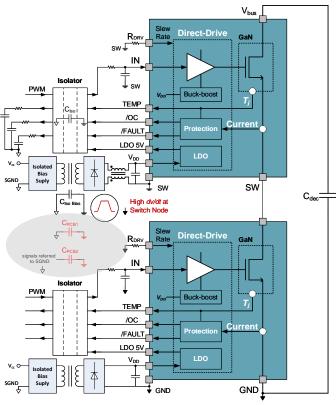

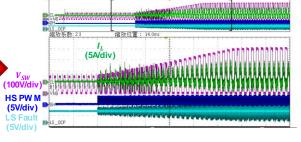

# Check switch node coupling

- Root cause: the switch node has overlap with the <u>control</u> <u>ground</u> and signals leading to capacitive coupling.

- Solution: avoid signal tracing above or below the switch node plan unless the signals are referring to switch-node.

- No current in positive AC cycle

- LS GaN triggered fault

When LS GaN is turning on, HS PWM has a 1.8V noise causing shoot-through.

# Check switch node coupling

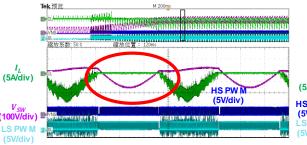

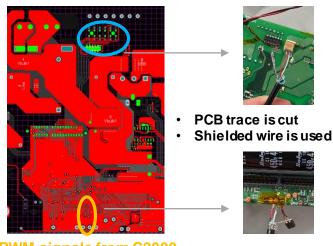

- **Root cause:** the switch node has overlap with the control ground and signals leading to capacitive coupling.

- **Solution:** avoid signal tracing above or below the switch node plan unless the signals are referring to switch-node.

- No current in positive AC cycle

- LS GaN triggered fault

When LS GaN is turning on, HS PWM has a 1.8V noise causing shoot-through.

- Rework the board and remove the noise coupling from switch node.

- Modified their layout and solved the problem.

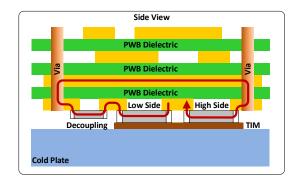

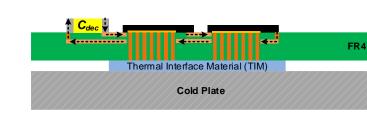

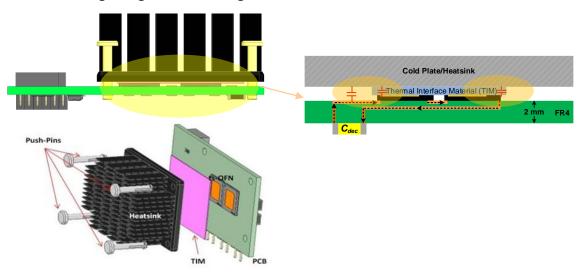

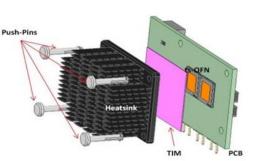

## 9) Why to avoid noise coupling to and from cooling plane?

## Noise coupling through cooling:

- Most GaN / SiC devices' exposed thermal pad is electrically connected to device's drain or source.

- Capacitive coupling exists between the switch-node and signal ground or signals.

18

# Ways to reduce noise coupling to cooling plane

- Minimize the traces and vias in adjacent layers to cooling plane.

- Increase distance to cooling plane in certain area to reduce coupling capacitance.

$$C = \frac{\varepsilon \cdot A}{\mathbf{d}}$$

PWB Cold Plate

**GaN FETs**

Thermal Interface Material (TIM)

most traces in inner layers

# 10) Why PWM signals are noisy at high dv/dt?

• **Issue:** PWM signals from the controller have large noises at high *dv/dt* operations.

No shielding on the PWM traces from controller to GaN card: high *dv/dt* and *di/dt* noises are coupled to PWMs

Noise Issue at 100V/ns, 380V

Operate Properly at 100V/ns, 380V

**PWM** signals from C2000

# Good practices to maintain signals integrity

- **Signal Shielding:** all signals need to be shielded by its reference ground. Shielding is recommended for both the controller's outputs and the isolator outputs.

- Kelvin Signal Connection:

- Avoid the noise area where high transient power passes through due to PCB trace impedance.

- The quiet area with significantly less power transition is used for signal ground.

# Signals traces with Ground Shielding

# Summary: design guidelines with WBG devices

#### Gate driver

- Optimize gate loop layout

- For bootstrap operation, add pre-regulations for drive voltage

- Fast short circuit protection

## Powerloop

- Reduce power loop inductance for EMI and noise immunity improvement

## CMTI in high dv/dt operation

- Good CMTI performance in isolator / isolated gate driver, and isolated bias supply

- Additional RC filter can help on glitch noises

## Noise coupling

- Avoid switch-node coupling to signals unless the signals are referred to switch-node

- Minimize capacitive coupling to cooling plane

- Provide good shielding to signals

© Copyright 2023 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated