## Design Guide: TIDA-010985

# 大容量 Y キャパシタを用いたリファレンス デザインを備える、800V DC システム向け抵抗ブリッジ方式の絶縁監視デバイス

## 説明

このリファレンス デザインは、抵抗性ブリッジ絶縁監視デバイス (IMD) を採用しています。この設計は、対称および非対称の絶縁抵抗故障を正確に検出します。このリファレンス デザインは、大容量の Y キャパシタ (Y cap) を備えた高電圧 DC システムにおける容量測定にも対応しています。この設計は、UL 規格における応答時間要件を満たしています。

## リソース

|                       |            |

|-----------------------|------------|

| TIDA-010985           | デザイン フォルダ  |

| LP-MSPM0G3507         | ツール フォルダ   |

| TPSI2240-Q1           | プロダクト フォルダ |

| RES60A-Q1、TLV9002-Q1  | プロダクト フォルダ |

| ISOW1044、TPSM33620-Q1 | プロダクト フォルダ |

| TPS7A20、TSM24CA       | プロダクト フォルダ |

テキサス・インスツルメンツ™ E2E サポート エキスパートにお問い合わせください。

## 特長

- 大容量 Y キャパシタ対応 (合計最大 9 $\mu$ F)

- 低演算量の予測アルゴリズムで応答時間を短縮

- Y キャパシタの電圧変動が小さい (保護接地に対して ±10%)

- 対称および非対称の故障検出の両方に対応

- 抵抗測定誤差 ±5%、容量測定誤差 ±15% ( $\pm 3\sigma$ )

- UL 2231-2 に準拠した ±15% の精度および 10 秒の応答時間

- 最大 1kV のバス電圧に対応

- 通信用の絶縁型コントローラ エリア ネットワーク (CAN) 2.0

## アプリケーション

- 高電圧バッテリ システム

- ESS (エネルギー ストレージ システム) – バッテリ管理システム (BMS)

- ストリング インバータ

- DC 高速充電パワー モジュール

## 1 システムの説明

高電圧 (HV) DC システムは、エネルギーストレージシステム、データセンター、ソーラーインバータ、DC 高速充電器など、さまざまな最終製品としての用途で採用が急速に伸びています。こうしたアプリケーションにおける標準的な DC 電圧の範囲は、150V ~ 1000V です。より大きいエネルギーストレージシステムでは、最大 1500V の電圧で動作します。

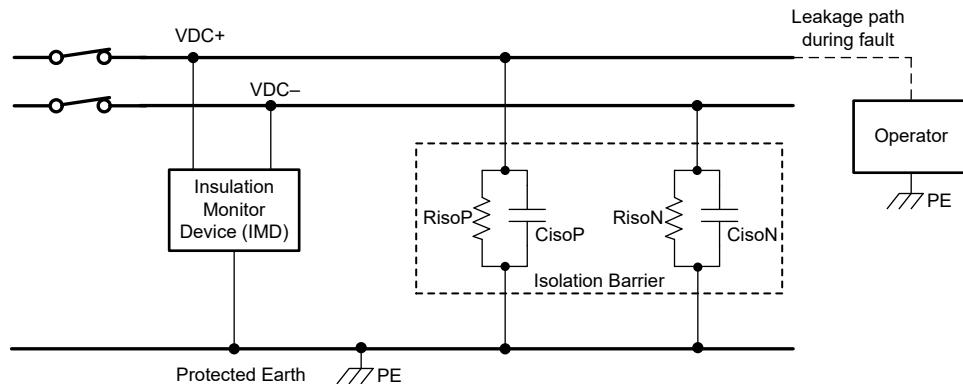

ユーザー保護は、これらの HV DC システムの設計上の重要な検討事項になります。システムにおけるすべての HV 部品は、高抵抗値パス (通常は高い  $M\Omega$  レンジ) を経由して、PE から電気的に絶縁されています。この絶縁により、最大リーケ電流が制限されます。国際規格 (例えば、EV 充電用の UL 2231-2、IEC 61851-23) では、システムとの接触による人的負傷を防止するため、リーケ電流を 10mA (すなわち  $100\Omega/V$ ) に制限することが求められています。IEC 61851-23 では、リーケ電流が 2mA ( $500\Omega/V$ ) 未満の場合を、安全な絶縁定格として規定しています。表 1-1 には、絶縁監視デバイス (IMD) の主要なスレッショルドを示しています。図 1-1 は、IMD が絶縁抵抗を監視し、絶縁抵抗が不十分になるとメインコントローラに異常を通知することを示しています。メインシステムコントローラは、異常発生後に、安全なシャットダウンシーケンスを開始します。絶縁状態の変化は緩やかに起きるため、これらの IMD は、1Hz ~ 2Hz の低周波数で連続的に動作します。

図 1-1. DC 非接地配電システムの絶縁監視デバイス

表 1-1. IEC および UL 規格に基づく、IMD の主要なスレッショルド

| STATUS | $\Omega/V$ | リーケ電流 | 800V VBus     | 1000V VBus    |

|--------|------------|-------|---------------|---------------|

| 警告     | 500        | 2mA   | 400k $\Omega$ | 500k $\Omega$ |

| フォルト   | 100        | 10mA  | 80k $\Omega$  | 100k $\Omega$ |

### 1.1 絶縁監視

絶縁を測定する方法はいくつかあります。しかし、最も一般的な方法は、AC 電流注入と抵抗ブリッジの 2 つです。一般に、AC 電流注入方式はさまざまな動作条件に対して柔軟性があり、DC 充電で広く使用されていますが、抵抗性ブリッジ方式に比べて複雑で、コストも高くなります。どのような方法においても、精度、応答時間、動作電圧制限などの標準的な要件を満たす必要があります。抵抗性ブリッジ方式に関連する主な課題のひとつは、大きい RC 時定数への対処です。メガワットチャージャなどの一部のシステムには、非常に大きな Y 容量 (例えば  $4\mu F$ ) が必要とされます。このリファレンスデザイン TIDA-010985 は、抵抗ブリッジ方式を採用しており、大きな Y 容量に対応できるよう特別に設計されています。また、浮動小数点演算などの大きな計算を必要とせずに測定時間を短縮できる、新しい予測アルゴリズムが用いられています。加えて、この新しい設計トポロジにより、Y キャパシタの電圧変動が制限されます。表 1-2 に各種方式の比較概要を示します。

**表 1-2. 各種 IMD 手法の比較**

| 方法                                                                                                                              | 利点                                                                                                                                                                                        | 欠点                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>AC 電流注入</b><br><ul style="list-style-type: none"><li>• 通常、スタンドアロン モジュールとして販売</li></ul>                                       | <ul style="list-style-type: none"><li>• 通電ライン、非通電ラインを測定可能</li><li>• 測定中に絶縁抵抗が低下しない</li><li>• 大容量 Y キャパシタを含め、UL 2231-2 に対応</li></ul>                                                       | <ul style="list-style-type: none"><li>• ハードウェアが複雑でコストが高い</li><li>• ソフトウェアが複雑 (AC 信号処理、浮動小数点演算が必要)</li></ul>                                                                                                                                   |

| <b>抵抗ブリッジ</b><br><ul style="list-style-type: none"><li>• TIDA-01513、BQ79731 EVM</li><li>• TIDA-010232 (MCU は絶縁 GND 上)</li></ul> | <ul style="list-style-type: none"><li>• ハードウェア、ソフトウェアともに実装が容易</li><li>• 低コスト</li><li>• 計算負荷が小さい</li></ul>                                                                                 | <ul style="list-style-type: none"><li>• 大容量 Y キャパシタ (<math>&gt;100\text{nF}</math>) では、UL 2231-2 に非対応</li><li>• 測定中、PE に対して電圧スイングが大きいため、IEC 61851-23 に非対応。アプリケーションが 500Vbus 未満に制限</li><li>• 通電ラインのみ測定可能</li><li>• 測定中に絶縁抵抗がわずかに低下する</li></ul> |

| <b>バランス型抵抗ブリッジ + 予測アルゴリズム</b><br><ul style="list-style-type: none"><li>• TIDA-010985 (MCU は接地 GND 上)</li></ul>                  | <ul style="list-style-type: none"><li>• ハードウェア、ソフトウェアともに実装が容易</li><li>• 低コストで計算負荷が小さい</li><li>• 測定中、PE に対して電圧スイングが小さいため、IEC 61851-23 に対応</li><li>• 大容量 Y キャパシタを含め、UL 2231-2 に対応</li></ul> | <ul style="list-style-type: none"><li>• 通電ラインのみ測定可能</li><li>• 測定中に絶縁抵抗がわずかに低下する</li></ul>                                                                                                                                                     |

## 1.2 主なシステム仕様

**表 1-3. UL 2231-2、IEC 61851-23 の主な仕様**

| パラメータ                     | UL 2231-2 / IEC 61851-23 の仕様 | TIDA-010985                                                      |

|---------------------------|------------------------------|------------------------------------------------------------------|

| トリップ精度 (対称型および非対称型故障)     | 15%                          | 5%                                                               |

| 応答時間                      | 10 秒未満                       | 2 秒未満 ( $C_{iso} = 4\mu\text{F}$ , $R_{iso} = 1\text{M}\Omega$ ) |

| ライン、PE 間の電圧変動 (VDC 対する %) | 10%                          | 10% (すなわち、1kV パスの場合は 50V)                                        |

**表 1-4. 主な電気的仕様**

| パラメータ                   | 仕様                      | 単位   |

|-------------------------|-------------------------|------|

| Riso 測定範囲 (テスト済み最大値)    | 2                       | MΩ   |

| Riso 測定誤差 (3σ)          | ±5                      | %    |

| Ciso 測定範囲 (テスト済み最大値)    | 9                       | μF   |

| Ciso 測定誤差 (3σ)          | ±15                     | %    |

| 絶縁測定サイクル時間 (設定可能)       | 2                       | s    |

| HV バス電圧 (最大値)           | 1000                    | V    |

| ADC フルスケール入力値           | 3.3                     | V    |

| 分圧器の抵抗                  | 12.5 ±15%               | MΩ   |

| IMD リーク電流 (最大値、アクティブ時)  | 2                       | mA   |

| IMD リーク電流 (最大値、非アクティブ時) | 100                     | μA   |

| 抵抗ブリッジの消費電力 (最大値)       | 0.85                    | W    |

| 電源                      | 6 ~ 36、または絶縁型 USB から LP | V    |

| 消費電力 (最大値)              | 2                       | W    |

| 動作温度                    | -40~85                  | °C   |

| インターフェイス                | CAN 2.0                 | 該当なし |

## 2 システム概要

### 2.1 ブロック図

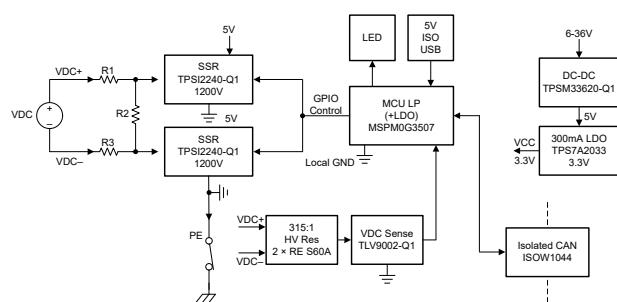

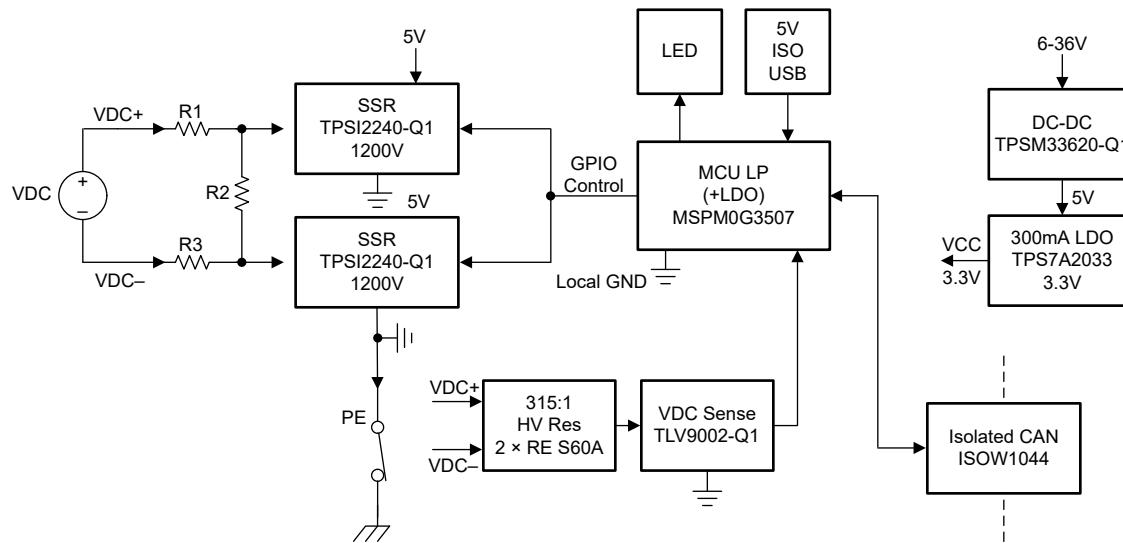

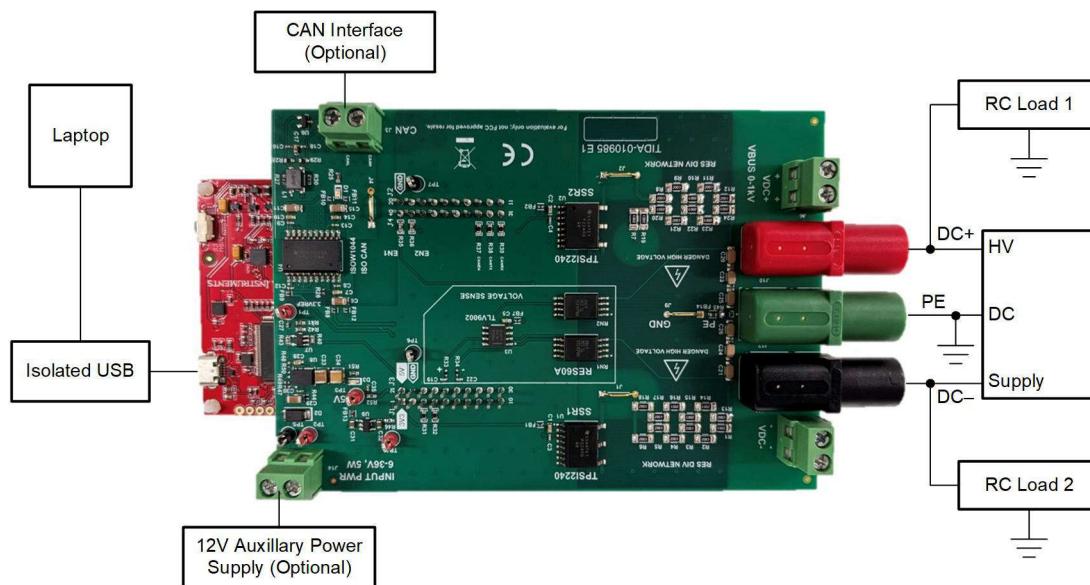

図 2-1. システム ブロック図

### 2.2 設計上の考慮事項

#### 2.2.1 TIDA-010985 の概要

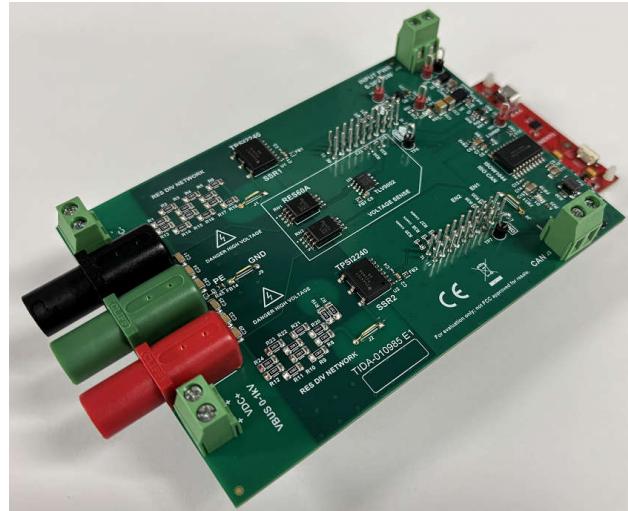

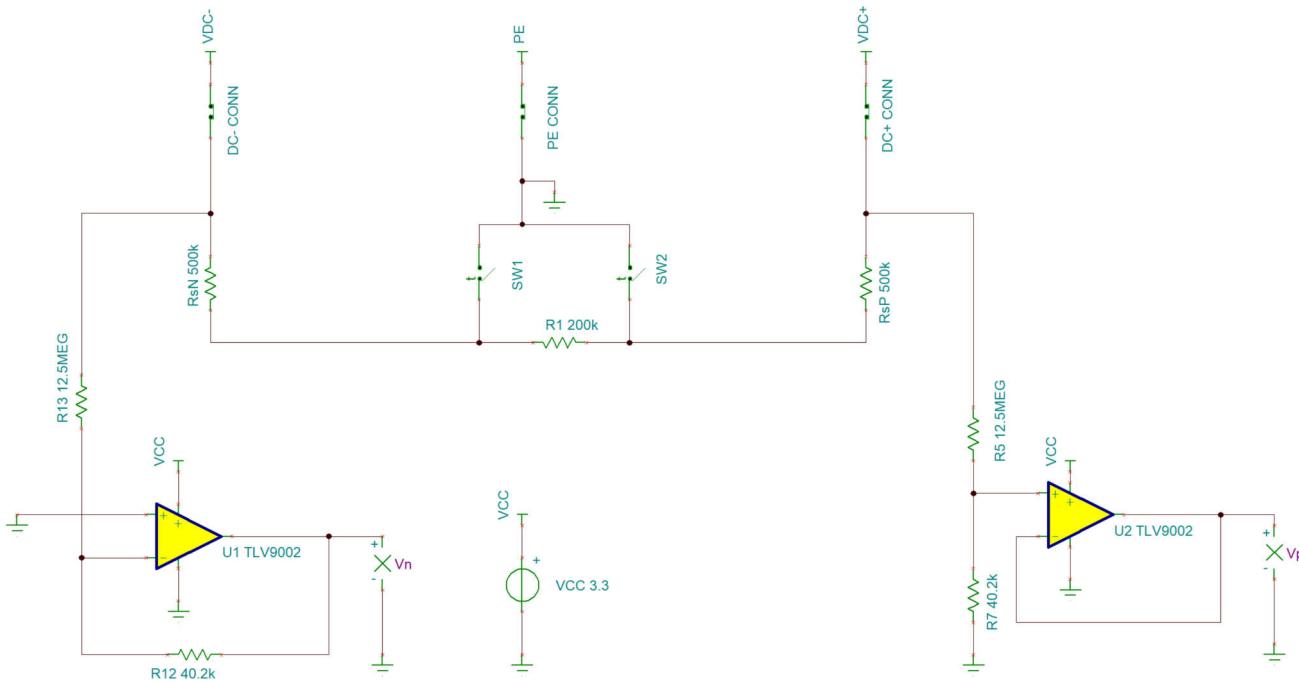

図 2-2 は、以下のリストに記載されている TIDA-010985 アナログ フロント エンド (AFE) の主要なシステム部品を示しています:

1. DC+、DC−、および保護接地 (PE) への機械的コネクタ

2. 複数のテスト抵抗の組み合わせ (Rsn, R1, Rsp) を可能にする準平衡抵抗ネットワーク。

3. 抵抗ネットワークを切り替える TPSI2240 双方向ソリッド ステート スイッチ (SW1, SW2)

4. PE に対する VDC− の電圧検知用、単一電源反転アンプ。電圧が ADC レベル (Vn) までスケール ダウンされます。RisoN および RisoP の計算に必要です。

5. PE に対する VDC+ の電圧センシング用、単一電源電圧バッファ。電圧が ADC レベル (Vp) までスケール ダウンされます。RisoN および RisoP の計算に必要です。

6. これらのスイッチの制御、アナログ出力のサンプリング (同時)、絶縁抵抗の計算を行うマイコン。

図 2-2. ターゲットシステム未接続の TIDA-010985 簡略化回路図

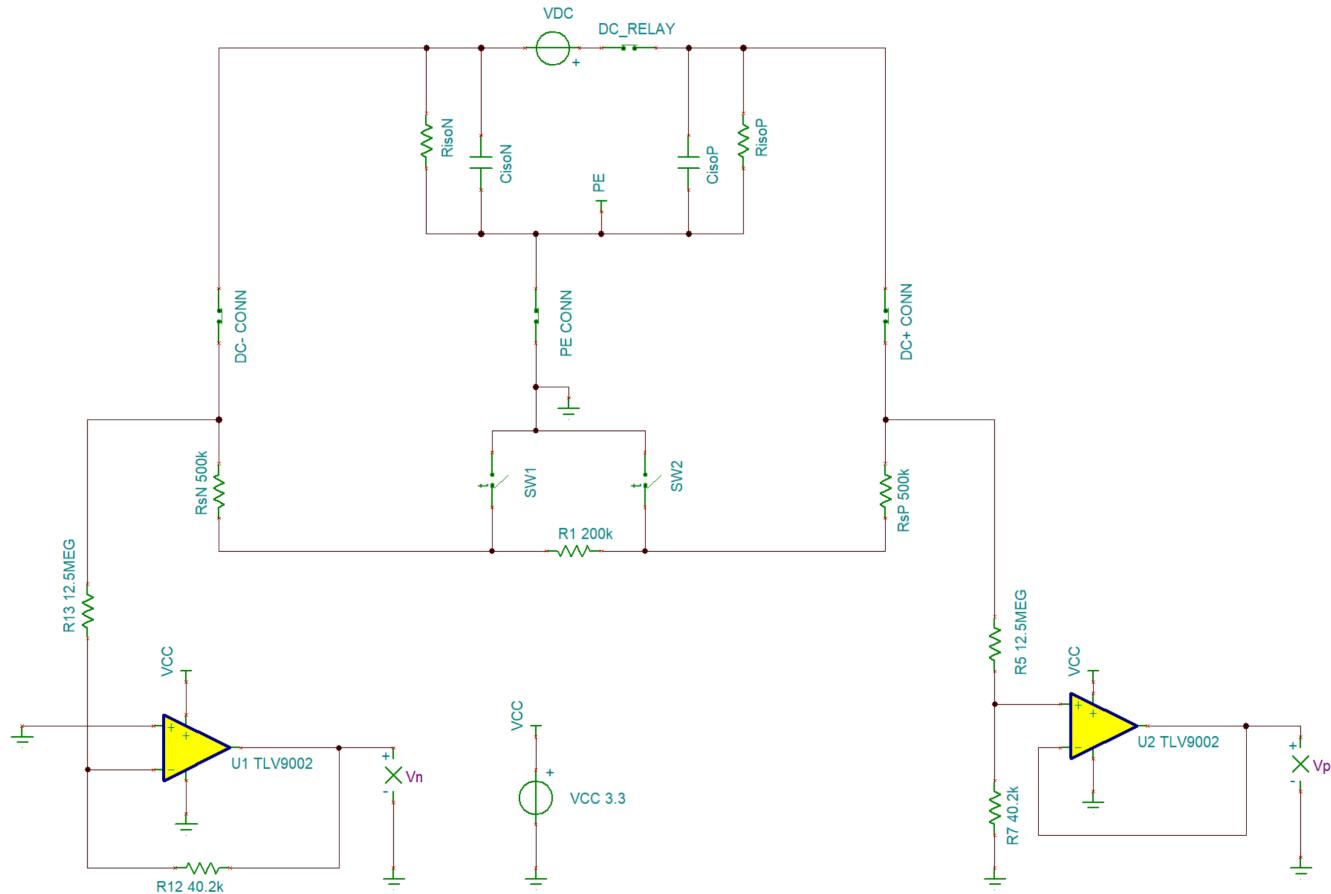

図 2-3 に、ターゲットシステムを接続した状態の簡略化回路図を示します。IMD は、すべての  $R_{iso}$  および  $C_{iso}$  のパッジ値を決定する必要があります。

図 2-3. ターゲットシステム接続状態の簡略化設計回路図

## 2.2.2 未知の絶縁抵抗の算出

2つのスイッチにより、RsP、RsN、R1を使用した複数の抵抗ブリッジのテスト比の切り替えが可能となります。この構成により、任意の Risop と Rison の比率を検出できます。システムは、非対称型フォルトと対称型フォルトの両方を検出します。TIDA-010985 の可能なスイッチング状態と、対応する方程式を表 2-1 に示します。Risop と Rison を求めるのに必要なのは、2つのスイッチング状態 (D を除く) のみです。2つの方程式で、2つの未知数を求められます。

表 2-1. TIDA-010985 の可能なすべてのスイッチング状態

| 状態 | SW1 | SW2 | RsP:RsN 比 | 定常状態の方程式                                                 |

|----|-----|-----|-----------|----------------------------------------------------------|

| A  | ON  | OFF | 7:5       | $\frac{V_p}{V_n} = \frac{-RisoP    (7R)}{RisoN    (5R)}$ |

| B  | OFF | オン  | 5:7       | $\frac{V_p}{V_n} = \frac{-RisoP    (5R)}{RisoN    (7R)}$ |

| C  | ON  | ON  | 5:5       | $\frac{V_p}{V_n} = \frac{-RisoP    (5R)}{RisoN    (5R)}$ |

| D  | OFF | OFF | 該当なし      | 該当なし                                                     |

理論上、設計者は A、B、C のスイッチング状態から 2つの組み合わせを選択できます。このリファレンス デザインでは、スイッチング状態 A と B を使用して絶縁抵抗を求めます。この AB の組み合わせにより、IEC 要件に基づく電圧変動の制限を行いつつ、スイッチング状態間で最大の電圧差を生成することで、信号対雑音比 (SNR) が最大化されます。この選択では、関連する 2つの方程式は次の通りです：

$$\frac{V_{p1}}{V_{n1}} = \frac{-RisoP || (7R)}{RisoN || (5R)} \quad (1)$$

$$\frac{V_{p2}}{V_{n2}} = \frac{-RisoP || (5R)}{RisoN || (7R)} \quad (2)$$

ここで、

- Vp1 は最初の DC+ 測定 (スイッチ状態 A) の電圧

- Vn1 は最初の DC- 測定 (スイッチ状態 A) の電圧

- Vp2 は 2 回目の DC+ 測定 (スイッチ状態 B) の電圧

- Vn2 は 2 回目の DC- 測定 (スイッチ状態 B) の電圧

2つの方程式を使用し、2つの未知数 (Risop および Rison) を求められます。この方程式は、MATLAB® を使用して解きました。

```

% solve for two equations with two unknowns assuming settled voltages

clc

syms rp rn vp1 vp2 vn1 vn2 rs

% change the sign if we're using inverting op amp for the vn sense

eq1 = vp1/vn1 == (rp*7*rs/(rp+7*rs)) / (rn*5*rs/(rn+5*rs));

eq2 = vp2/vn2 == (rp*5*rs/(rp+5*rs)) / (rn*7*rs/(rn+7*rs));

eq3 = rs > 0 & vp1 > 0 & vn1 > 0;

eqns = [eq1, eq2, eq3];

%

[srna, srpa, parametersa, conditionsa] = solve(eqns,[rn, rp],ReturnConditions=true)

%

```

この計算から、次の結果が得られます：

$$RisoN = \frac{-(35 \times V_{n1} \times V_{p2} - 35 \times V_{n2} \times V_{p1}) \times RS}{(7 \times V_{n1} \times V_{p2} - 5 \times V_{n2} \times V_{p1} + 2 \times V_{p1} \times V_{p2})} \quad (3)$$

$$RisoP = \frac{-(35 \times V_{n1} \times V_{p2} - 35 \times V_{n2} \times V_{p1}) \times RS}{(2 \times V_{n1} \times V_{n2} + 7 \times V_{n1} \times V_{p2} - 5 \times V_{n2} \times V_{p1})} \quad (4)$$

RS 定数は  $100\text{k}\Omega$  と定義されることに注意してください。ユーザーが別の比率を使用する場合は、MATLAB スクリプトを変更して、新しく選択した比率を求めることができます。

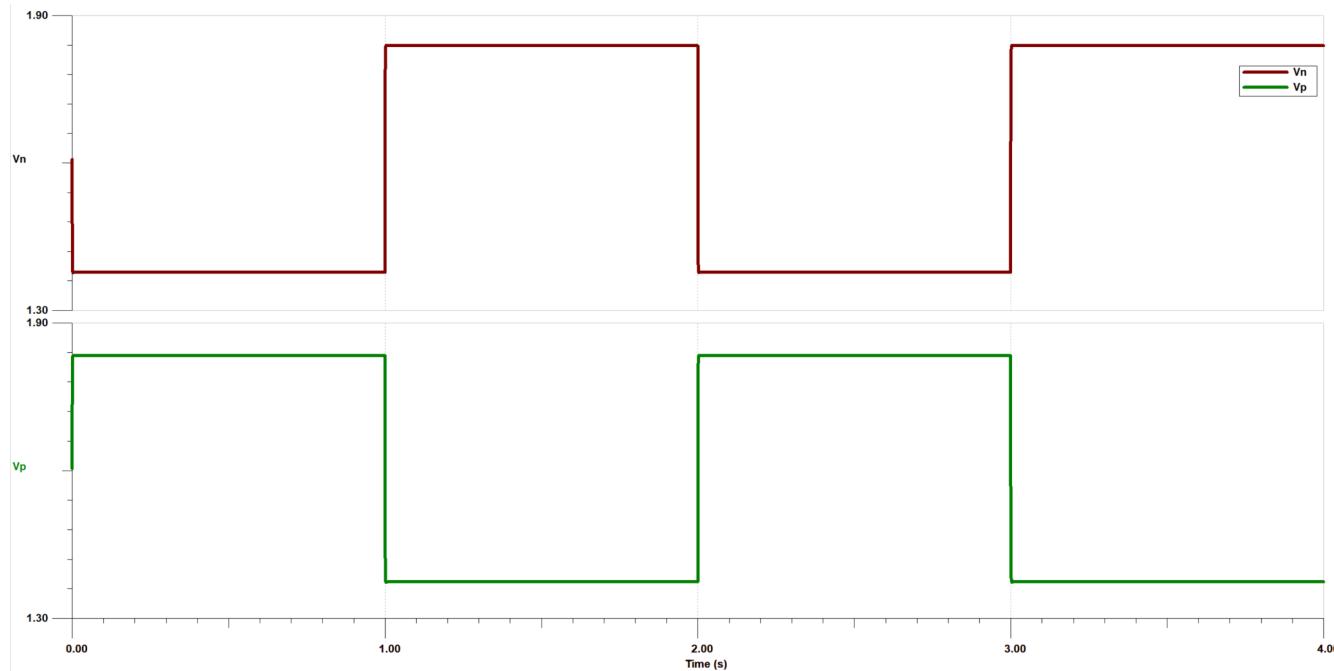

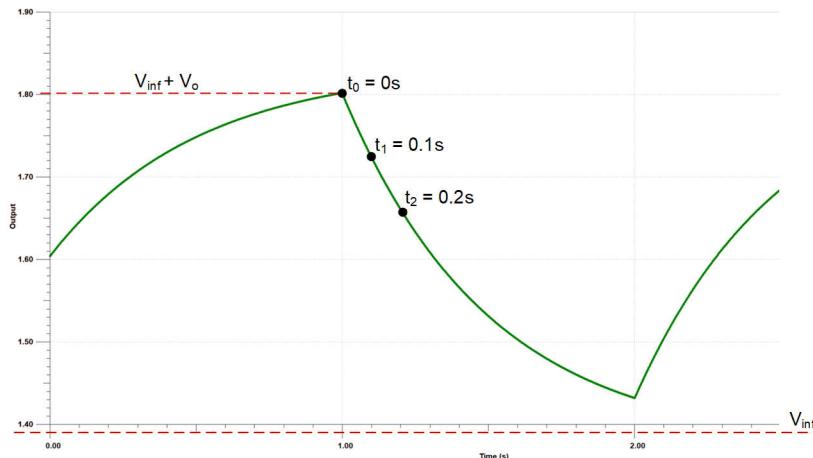

図 2-4 に、AB の組み合わせによる電圧波形の例を示します。この例では、各スイッチング状態が 1 秒間続きます。2 つの状態の測定が必要なため、1 回の IMD 測定サイクルには 2 秒かかります。 $V_{p1}$  と  $V_{n1}$  は最初の 1 秒で同時に測定され、 $V_{p2}$  と  $V_{n2}$  は次の 1 秒で同時に測定されます。 $V_p$  と  $V_n$  を同時に ADC 測定すると、HV バスのノイズの影響が除去されることに注目してください。Riso の解は、 $V_p$  と  $V_n$  の比率の差に依存します ( $V_p$  および  $V_n$  の個々の絶対値には依存しません)。

図 2-4. AB スイッチのトグル モードの波形例

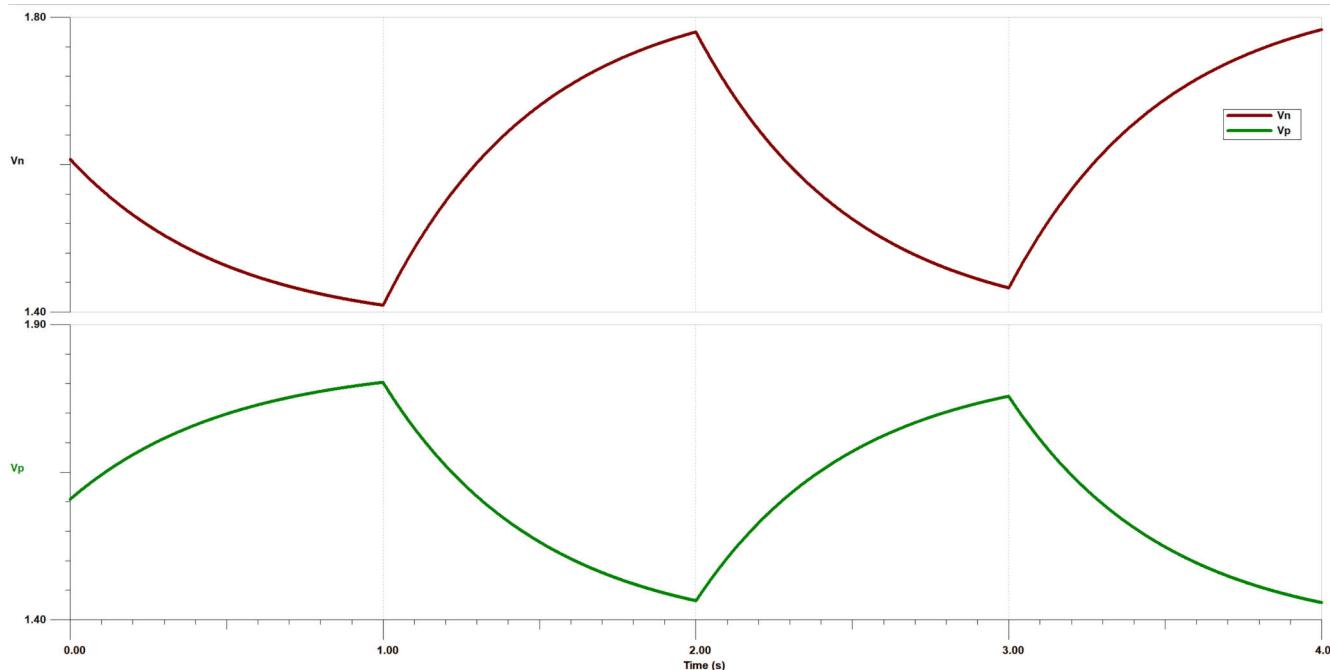

### 2.2.3 時定数が大きい場合の対処

前の例では、ADC が  $V_p$  と  $V_n$  を測定する前に、大幅な RC セトリング タイムはないものと仮定しています。しかし、図 2-5 の例のような条件では、時定数が非常に長くなることがあります。回避方法がないと、電圧が安定するまでに長時間を要する場合があり、そのため、標準的な応答時間の要件を満たせなくなる可能性があります（例えば、UL 2231-2 では 10 秒です）。

図 2-5. 時定数が大きい場合の波形例

SW1 がオン、SW2 がオフのときの時定数  $\tau$  は次のようになります:

$$\tau = (\text{RisoP} \parallel \text{RisoN} \parallel \text{RsP} + \text{R1} \parallel \text{RsN}) \times (\text{CisoP} + \text{CisoN}) \quad (5)$$

時定数が大きいケース (すなわち、 $\mu\text{F}$  レンジの大きい Y キャパシタの場合) に対処するには、いくつかの方法があります:

- 消費電力とリーク電流の増加を犠牲にして、 $\text{Rsp}$  と  $\text{Rsn}$  の値を低くする方法。リーク電流が大きくなると規格要件に違反するため、多くの場合、実用的ではありません。

- 追加のセッティングタイムを考慮して、サイクル時間を (例えば、2 秒から 3 秒へ) 延ばす方法。UL の応答時間制限があるため、多くの場合、実用的ではありません。

- 複数の測定値とアルゴリズムを使用し、最終的なセッティング電圧を予測する方法。正しく行えば、電力や時間を増やすずに IMD の動作範囲を拡張できます。これについては、[セクション 2.2.4](#) で説明します。

## 2.2.4 予測アルゴリズム

SW2 がオンのとき、応答は指数関数的減衰の式に従います:

$$V(t) = V_{\text{inf}} + V_0 e^{-\frac{t}{\tau}} \quad (6)$$

ここで、

- $V_{\text{inf}}$  は最終的に安定した電圧 ( $t = \text{無限大}$ )

- $V_0$  は時刻ゼロでの初期電圧  $V(t_0)$  と  $V_{\text{inf}}$  の差。

この概念の詳細については [図 2-6](#) を参照してください。

セッティング電圧  $V_{\text{inf}}$  は特に重要です。この方程式における未知数は、 $V_{\text{inf}}$ 、 $\tau$ 、 $V_0$  の 3 つです。ADC が 3 つのサンプル電圧をそれぞれ異なる時刻で測定すると、次のような 3 つの連立方程式が作成されます:

$$V(t_0) = V_{\text{inf}} + V_0 \quad (7)$$

$$V(t_1) = V_{\text{inf}} + V_0 e^{-\frac{t_1}{\tau}} \quad (8)$$

$$V(t_2) = V_{\text{inf}} + V_0 e^{-\frac{t_2}{\tau}} \quad (9)$$

$t_2 = 2 \times t_1$  を用いることで、 $V_{\text{inf}}$  の計算は大幅に簡略化されます：

$$V_{\text{inf}} = \frac{V(t_0) \times V(t_2) - V(t_1)^2}{V(t_0) - 2V(t_1) + V(t_2)} \quad (10)$$

- 四則演算のみで  $V_{\text{inf}}$  を計算できることに注目してください。 $V_{\text{inf}}$  を計算すれば、 $V_0$  は  $V(t_0)$  から  $V_{\text{inf}}$  を引くことで計算できます。

- 理論上、 $t_0$  の位置は、 $t_1$  と  $t_2$  の間隔が互いに適切である限り、減衰曲線上のどこであっても問題はありません。具体的には、3つのサンプル間の時間差を一定に保つ必要があります。時定数が長い場合、同じサイクル時間でも、電圧セトリング曲線が比較的平坦になることがあります。ノイズの多い状況では、3つのサンプル間の時間間隔を広げることで信号対雑音比が向上し、予測アルゴリズムの性能が改善します。

この連立方程式を解くために使用される MATLAB スクリプトは次の通りです：

```

%> solution for exponential decay

clc

syms vt0 vt1 vt2 vinf v0 x

eq1 = vt0 == vinf+v0;

eq2 = vt1 == vinf+v0xx;

eq3 = vt2 == vinf+v0xxxx;

eq4 = vt0 ~= vt1;

eqns = [eq1, eq2, eq3, eq4];

[vinf, v0, x, para, conditions] = solve(eqns,[vinf, v0, x],ReturnConditions=true)

```

TIDA-010985 のデフォルトコードでは、3つのサンプル間の時間間隔は 330ms です。これにより、固定小数演算を簡略化しつつ、IMD の全測定サイクル時間を 2 秒未満に保っています。デフォルトのサイクル時間は、次のいずれかの操作で変更できます：

- IMD.c における E1 の #define を変更します。例えば、E1 の #define を 990 から 600 (ms) に変更すると、IMD のサイクル時間が約 2 秒から約 1.2 秒に短縮されます。正確な時間は、データ アクイジョン期間後の数ミリ秒 (ms) の計算 (約 2ms) によって異なります。ユーザーが何らかの理由でサイクル時間を増やしたい場合、E1 の #define に加えて、データ バッファ「SamplesSize」もそれに応じて変更する必要があります。デフォルトの ADC サンプリング周期を変更せずにデータ バッファを増やす場合、利用可能な SRAM (合計 32kB) によって増加を制限される可能性があります：

```

#define SamplesSize 2000 // ADC buffer size

#define E1 990 // total time for Riso measurement is 2xE1 in ms

```

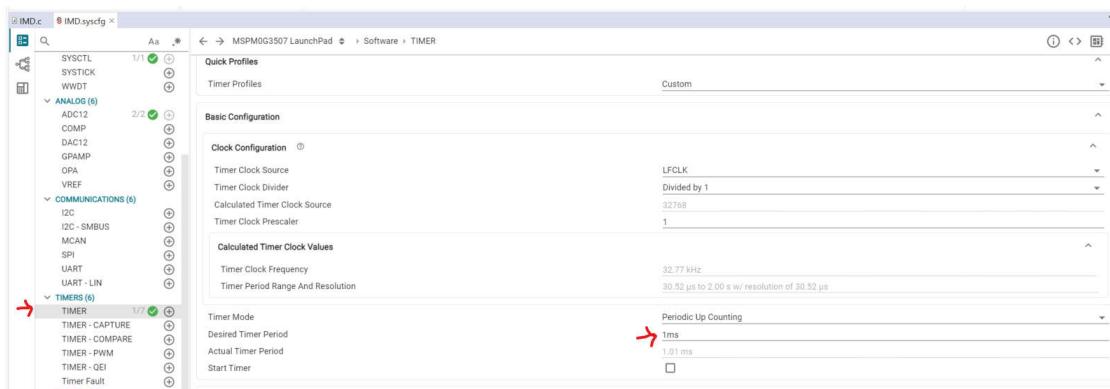

- syscfg の TIMER\_0 周期を変更して (例えば 1ms から 0.5ms へ)、ADC サンプリング間隔を変更します。このコードは、デフォルトの 1ms の ADC サンプリング周期を想定しているため、残りのコードも多少変更する必要があります。

時定数は、次の式で計算されます：

$$\tau = \frac{-V_0}{V'(t_0)} \quad (11)$$

絶縁抵抗を求めるには、 $V_{\text{inf}}$  だけが必要です。システム全体の Y キャパシタ (CisoP + CisoN) については、隣接する 2 つの ADC 測定値を用いて、 $t_0$  における  $V'(t)$  を近似します。すると、Ciso は次のようにになります：

$$Ciso = \frac{\tau}{RisoP || RisoN || RsP + R1 || RsN} \quad (12)$$

図 2-6. 予測アルゴリズムに使用される ADC サンプルを含んだ電圧減衰曲線の例

充電曲線についても同様の分析ができます。最終的な定常状態電圧  $V_{inf}$  の計算式は次の通りです：

$$V_{inf} = V(t_0) + \frac{V(t_0)^2 - 2 \times V(t_0) \times V(t_1) + V(t_1)^2}{-V(t_0) + 2 \times V(t_1) - V(t_2)} \quad (13)$$

この連立方程式を解くために使用される MATLAB スクリプトは次の通りです：

```

%> charging solution

clc

syms vt0 vt1 vt2 vi v0 x

eq1 = vt0 == vi;

eq2 = vt1 == vi + v0*(1-x);

eq3 = vt2 == vi + v0*(1-xxx);

eq4 = vt0 ~= vt1;

eqns = [eq1, eq2, eq3, eq4];

%

[svi, sv0, sx, para, conditions] = solve(eqns,[vi, v0, x],ReturnConditions=true)

```

重要な問題の 1 つは、予測アルゴリズムをいつ適用するかを把握することです。電圧のセッティング タイムが短い場合は、予測アルゴリズムを使用しないでください。Riso または Ciso を求める前に、もう少し時間を待つ方が実用的です。現状、このソフトウェアでは、電圧の時間微分 ( $V_{bus}$  電圧で正規化) に基づいていくつかの基本的なチェックを行い、予測モードのスレッショルドを設定しています。この方法では、信頼性の高い動作を実現するために、既知の負荷でいくらかのチューニングが必要です。コード内で使用可能な動作モードは次の通りです：

- `#define SETTLED_MODE`

- `#define DECAY_MODE`

- `#define CHARGE_MODE`

- `#define OUT_OF_RANGE_MODE`

## 2.2.5 エラー ソースの理解

MSPM0G3507 は固定小数点演算のみをサポートしているため、誤差や精度の低下を最小限に抑えるには、数値のオーバーフローに対する多少の配慮が必要です。現在のコードは、最も重要な箇所である、故障および警告のスレッショルド付近の精度と正確性を維持するよう最適化されています。浮動小数点演算に対応したマイコンに切り替えることで、この課題を回避できます。

部品の許容差は、特に設計目標の精度を満たすように選定されます。RES60A 抵抗など一部の受動部品の最大絶対許容差は 15% で、Riso が  $M\Omega$  レンジの場合、測定精度に影響を及ぼします。ただし、これは重要ではありません。最高の精度が求められるのは、 $100\Omega/V$  の故障トリップ ポイント付近であるためです。 $1kV$  バスの場合、 $100k\Omega$  に相当します。このレベルでは、5% 精度目標に対して RES60A の許容差は重要ではありません。ただし、RES60A と他の抵抗を並列接続する場合は、等価抵抗の読み取り値を補正する必要があります。

これまでのところ、IMD はノイズのない例外的な条件下で動作すると仮定されており、基本的な概念を理解するための良い出発点となります。実際には、TIDA-010985 の性能は、いかにうまくノイズを制御するかに大きく依存します。この設計でノイズを軽減するための手順を以下に示します：

- 入力ノイズを抑えるためのハードウェア フィルタリング

- PCB レイアウトのガイドラインに従い、信号対雑音比を最適化

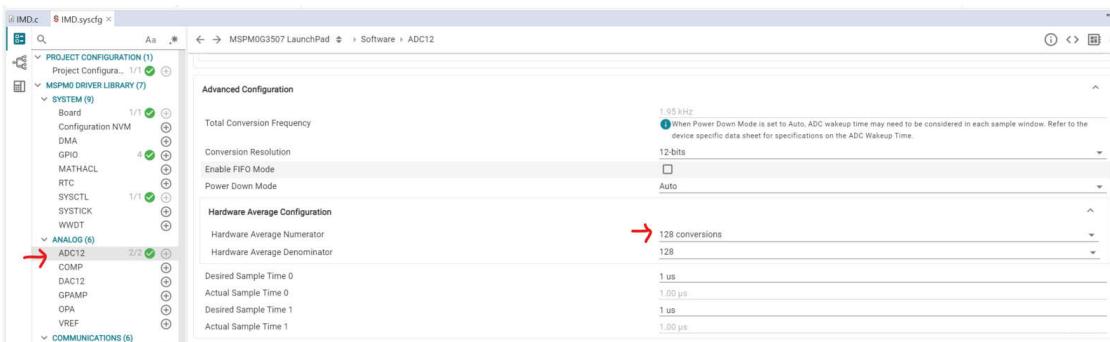

- ADC ハードウェア平均化（デフォルトは 128 に設定）

- 複数の ADC 読み取り値や予測値をソフトウェアで平均化し、定常状態電圧を推定します。予測に基づかない IMD 計算の場合、ソフトウェアは隣接する 50 個の ADC サンプルを平均化し、安定した電圧を推定します。

- 予測に基づく IMD 計算の場合、ソフトウェアは 330 個の予測値を平均化し、安定した電圧（すなわち  $V_{p1}$ 、 $V_{n1}$ 、 $V_{p2}$ 、 $V_{n2}$ ）を推定します。時定数が長いと、電圧セトリング曲線が平坦になり、ノイズの多い状況では予測精度が低下します。前述したように、3 つのサンプル間の時間間隔を長くすることで、予測性能を向上させることができます。

## 2.3 主な使用製品

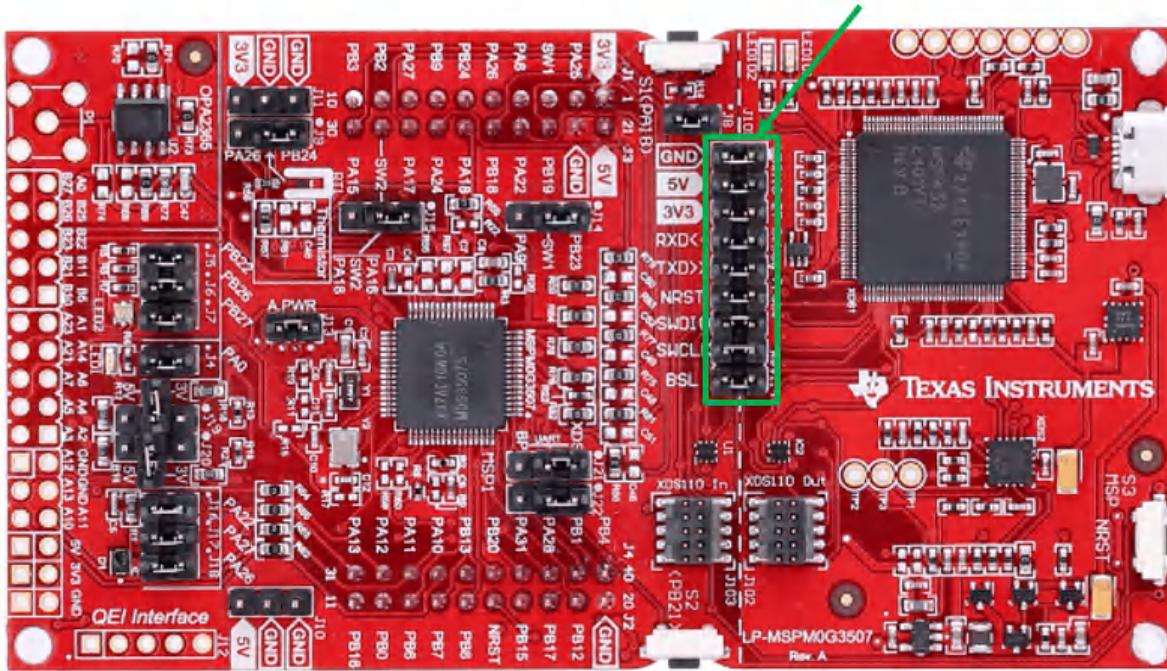

### 2.3.1 LP-MSPM0G3507

LP-MSPM0G3507 LaunchPad™ 開発キットは、MSPM0G3507 をベースとする、使いやすい評価基板 (EVM) です。プログラミング、デバッグ、エネルギー測定を行うためのオンボード デバッグ プローブなど、MSPM0G3507 M0+ マイコン プラットフォームの開発を開始するために必要なすべての機能を搭載しています。このボードは、3 個のボタン、2 個の LED (1 個は RGB LED)、1 個のアナログ温度センサ、1 個の光センサを搭載しています。また、4MSPS で動作する高速 ADC の性能を提示するための外部バッファも搭載しています。

### 2.3.2 TPSI2240-Q1

TPSI2240-Q1 は、高電圧車載用および産業用アプリケーション向けに設計された絶縁型ソリッドステートリレーです。TPSI2240-Q1 は、テキサス インスツルメンツの高信頼性容量性強化絶縁技術と内蔵の双方向 MOSFET を組み合わせることにより、2 次側電源を必要としない統合アプローチを形成しています。

### 2.3.3 RES60A-Q1

RES60A-Q1 は、マッチングされた抵抗分周器で、テキサス インスツルメンツの最新の高性能アナログ ウエハ プロセスで薄膜 SiCr に実装されています。高品質の SiO<sub>2</sub> 絶縁層は抵抗器をカプセル化し、継続的動作で最大 1400VDC、HiPOT テスト (60 秒) で最大 4000VDC という非常に高い電圧で使用できるようにします。このデバイスは、公称入力抵抗  $R_{HV} = 12.5\text{M}\Omega$  であり、幅広いシステムの要求を満たすため、いくつかの公称比率で供給されます。

### 2.3.4 TLV9002-Q1

TLV900x-Q1 ファミリには、低電圧 (1.8V~5.5V) でレールツー レール入出力スイギング能力を備えた、シングル (TLV9001-Q1)、デュアル (TLV9002-Q1) およびクワッド (TLV9004-Q1) チャネルのオペアンプがあります。これらのオペアンプは、低電圧動作と大容量負荷駆動が必要なインフォティメントおよび照明などのスペース制約が厳しい車載アプリケーション向けに、コスト効率の優れたオプションを提供します。TLV900x-Q1 ファミリの容量性負荷の駆動能力は 500pF であり、オープン ループ出力インピーダンスが抵抗性なので、はるかに大きな容量性負荷についても容易に安定化できます。これらのオペアンプは低電圧 (1.8V~5.5V) で動作し、TLV600x-Q1 デバイスと同様の性能仕様を満たすよう、特別に設計されています。

### 2.3.5 TPSM33620-Q1

TPSM336xx-Q1 は、0.6A、1A または 2A、36V 入力、車載用の同期降圧 DC/DC パワー ジュールで、フリップ チップ オンリード パッケージ、統合型パワー MOSFET、AEC-Q100 認定の内蔵インダクタ、ブートコンデンサをコンパクトで使いやすいパッケージに統合しています。小型 HotRod QFN パッケージにより、放熱性能が向上し、高い周囲温度での動作が可能となっています。拡散スペクトラムは優れた EMI 性能を実現します。本デバイスは、3.3V および 5V をサポートする 2 つの固定出力電圧オプションで利用可能です。フィードバック デバイダにより、1V から 7V までの出力に設定でき、MODE/SYNC ピンを介して自動または強制 PWM モードで動作させることができます。また、3.3V および 5V 固定出力設計において、必要なのは 4 つの外付け部品だけなので、PCB レイアウトと設計を簡素化できます。

### 2.3.6 TPS7A2033

TPS7A20 は、300mA の出力電流を供給できる超小型の低ドロップアウト (LDO) リニア レギュレータです。TPS7A20 は、無線周波数回路やその他の敏感なアナログ回路の要件を満たすため、低ノイズ、高 PSRR、および非常に優れた負荷ライン過渡性能を実現できるよう設計されています。設計手法により、TPS7A20 は、ノイズバイパスコンデンサを追加しなくても超低ノイズ性能を発揮します。TPS7A20 は、静止電流が小さいという利点も備えており、バッテリ駆動のアプリケーションに適しています。1.6V~6.0V の入力電圧範囲と 0.8V~5.5V の出力電圧範囲を持つ TPS7A20 は幅広いアプリケーションに使用できます。本デバイスは、負荷、ライン、温度の変化に対して誤差 1.5% 以下の精度を達成するために高精度の基準電圧回路を使用しています。

### 2.3.7 ISOW1044

ISOW1044 デバイスは、ガルバニック絶縁されたコントローラ エリア ネットワーク (CAN) トランシーバで、絶縁型 DC/DC コンバータが内蔵されており、スペースに制約のある絶縁設計のための別の絶縁型電源が不要になります。低放射の絶縁型 DC/DC コンバータは、単純な 2 層 PCB でフェライトビーズを 2 個使用するだけで、CISPR 32 放射エミッション Class B 規格に適合可能です。ボード上の他の回路への電力供給には、追加の 20mA 出力電流を使用できます。10Mbps GPIO チャネルを内蔵しているため、追加のデジタル アイソレータやフォトカプラを使わずに、診断、LED 表示、電源監視が可能です。

### 2.3.8 TSM24CA

TSM24CA は、低容量 TVS ダイオードであり、テキサス インスツルメンツのサージ保護デバイス ファミリの製品です。TSM24CA は、最大 30A の IEC 61000-4-5 (8μs ~ 20μs) フォルト電流を確実にシャントして、システムを高電力過渡事象や落雷から保護します。このデバイスは、一般的な産業用信号ラインの EMC 要件に対応しており、42Ω のインピーダンスにより結合される、最大 1kV の IEC 61000-4-5 開路電圧に耐え、40V (IPP = 24A) でそのサージをクランプします。また、TSM24CA は、12pF の非常に低いライン容量を備えているため、EV 充電アプリケーションにおけるサージから、CAN などの一般的な車載通信ネットワークを保護できます。

### 2.3.9 TLV431B

TLV431 デバイスは低電圧、3 端子の可変電圧リファレンスであり、該当する産業用および民生用温度範囲全体にわたって規定の熱的安定性を維持します。出力電圧は、2 つの外付け抵抗により VREF (1.24V) と 6V の間の任意の値に設定できます。これらのデバイスは、広く使用されている TL431 および TL1431 シャント レギュレータ基準電圧よりも低い電圧 (1.24V) で動作します。

#### 注

この電圧リファレンスは、リファレンス デザインの動作に必須ではありません。デフォルトでは、ADC は VDD を電圧リファレンスとして使用しますが、結果は  $V_p$  と  $V_n$  の比で決まるため、問題はありません。

### 3 ハードウェア、ソフトウェア、テスト要件、テスト結果

#### 3.1 ハードウェア要件

このリファレンス デザインの評価に使用されたハードウェアは以下で構成されます:

- TIDA-010985

- LP-MSPM0G3507

- USB Type-C® ケーブル

- USB アイソレータ (LP への電力供給および、ノート PC の保護)。リファレンス デザインを評価するための標準的な方法は、USB でシステム全体に電力を供給することです。

- ノートブック PC

- 4 チャネル オシロスコープ

- 定格電圧が 1kV 以上の 2 本の高電圧差動プローブ

- 低電圧信号測定用の 2 本のシングルエンドプローブ (TPP0500B)

- デジタル信号デバッグ用のロジックアナライザ (Saleae Logic 16、オプション)

- HV DC 電源 SL1250 — 1.2/UI + LXI

- HV テストを安全に行うためのインターロック付きセーフティボックス

- LP の USB 電源 (デフォルト設定) の代わりに外部電源を希望する場合に使用する、オプションの 12V DC ラボ電源 (5W)

#### 3.2 ソフトウェア

このリファレンス デザインを評価するには、Code Composer Studio™ (CCS) ソフトウェアが必要です。サンプルコードは TIDA-010985 ツール フォルダにあります。この設計には、CCS バージョン 12.8.1.00005 が使用されています。CCS を初めてインストールする際は、インストール中に MSP パッケージを必ず確認してください。

- この設計には、[MSPM0-SDK](#) バージョン 2.7.0.05 が使用されています。CCS のインストール時に SDK がインストールされていない場合は、SDK をダウンロードしてインストールしてください。インストールパスの例は次の通りです:

C:\ti\mspm0\_sdk\_2\_07\_00\_05 プロジェクトのリンク済みリソースパス変数に、この SDK パスが含まれていることを確認してください。これらの設定は、「Project」→「Properties」→「Resources」→「Linked Resources」の順に進んでおこなってください。

#### 3.3 テスト設定

##### 3.3.1 ハードウェアのテスト構成

図 3-1 に基本的なテスト構成を示します。

図 3-1. ハードウェアのテスト構成

図 3-2. LaunchPad™ J101 のデフォルト ジャンパ構成

- 図 3-1 に示すように、必要なすべてのハードウェア接続を行います。すべての接続が確実に行われ、安全ボックス内に適切に配置されるまで、HV 電源を供給しないでください。

- ターゲットのテスト RC 負荷を HV コネクタに接続してください。ユーザー向けに、次のような便利なオプションがあります:

- VDC+ 接続用の J6 または TP11

- VDC- 接続用の J7 または TP10

- 保護接地 (PE) 用の J9。システム グランドは PE に接続されていることに注意してください。

- 基板をデバッグするために、オシロスコープのプローブを目的の SW\_EN ピン (J13 ピン 39 および 40) と ADC 入力ピン (J5 ピン 25 および 27) に接続してください

- 必要に応じて、HV 差動プローブを HV コネクタに接続してデバッグを実行します

- デモプロジェクトをインポートし、CCS ソフトウェア デバッグ モードを開始します

- HV 電源をオンにし、波形および、抵抗と静電容量の計算値を観測します

#### 注

外部 DC 電源 (TIDA-010985 基板の J14 への入力) を使用してリファレンス デザインに電力を供給するには、R52 と R46 を短絡し、LP デバイスの J101 上のジャンパを取り外す必要があります (デバッガの動作に必要な、GND、SWDIO、SWCLK を除くすべて)。

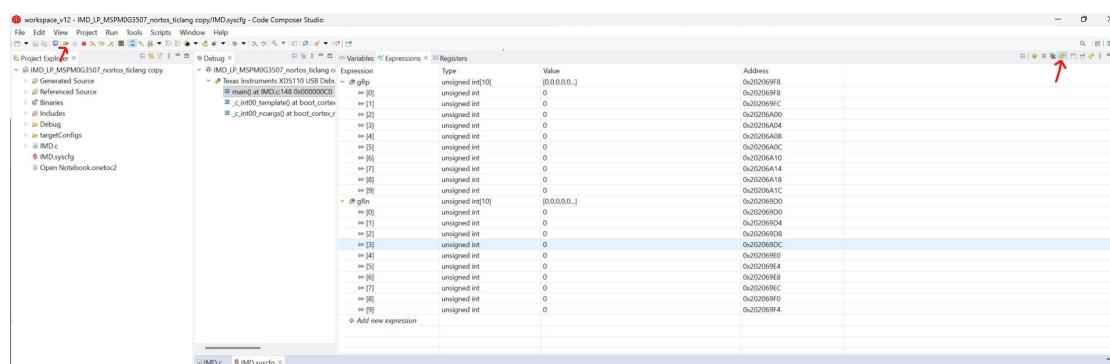

### 3.3.2 ソフトウェア テスト設定

- サンプルのデモ プロジェクトは [TIDA-010985](#) ツール フォルダにあります。CCS バージョン: この設計には、バージョン 12.8.1.00005 が使用されています。CCS と MSPM0 SDK をまだインストールしていない場合は、インストールしてください。

- デモ プロジェクトをダウンロードしてインポートします

- CCS ソフトウェアのデバッグ モードを開始します

- CCS の WATCH ウィンドウで連続更新オプションにチェックを入れます

## ハードウェア、ソフトウェア、テスト要件、テスト結果

- 測定値を観測するために、gRn や gRp などの変数を WATCH ウィンドウに追加します。gRn および gRp は、RP および RN と並列に接続された 2 つの 12.5MΩ RES60A 抵抗に基づいて補正された値です。有効な RP および RN については、WATCH ウィンドウに「rn」と「rp」を追加します。

- タイミング平均化やハードウェア平均化など、ADC のデフォルト設定を変更する必要がある場合は、プロジェクトの **syscfg** ファイルを修正してください。デフォルトでは、2 つの ADC (ADC0 および ADC1) のサンプリング周期は 1ms に設定され、ハードウェア平均化の数は 128 回の変換に設定されています ([図 3-3](#) ~ [図 3-5](#))。ハードウェア平均化は、測定値におけるノイズの影響を軽減するのに役立つことに注目してください。IMD サイクリング時間を適切に変更する方法の詳細については、[予測アルゴリズム](#)のセクションを参照してください。

図 3-3. デバッグ セッション中に連続更新モードで実行される CCS の式 Watch ウィンドウ

図 3-4. syscfg タイマ周期設定

図 3-5. syscfg ADC ハードウェア平均化設定

### 3.4 テスト結果

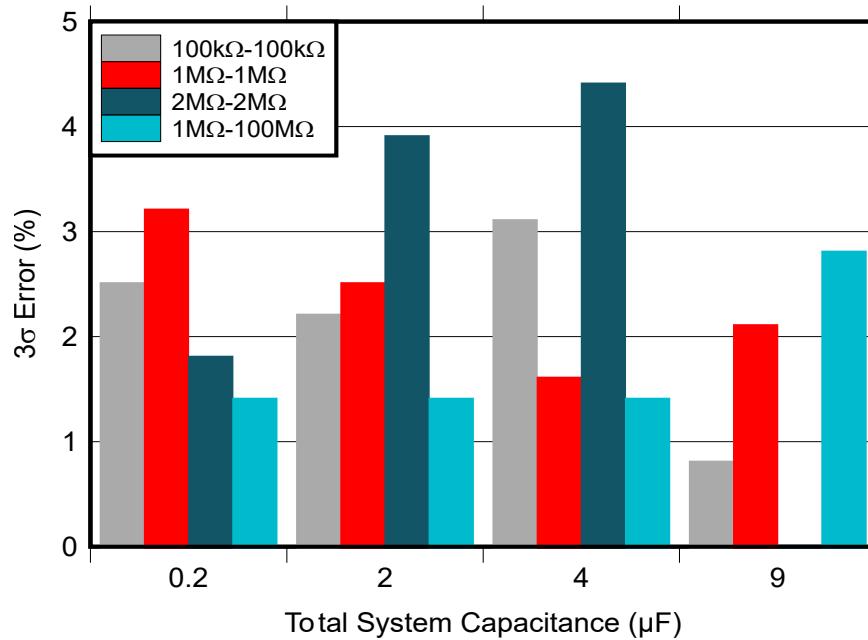

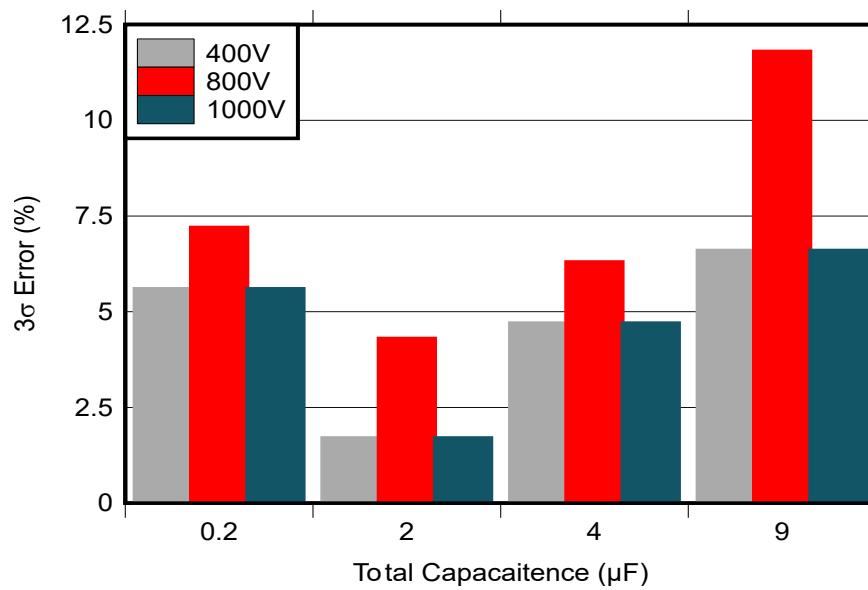

各試験条件には、統計分析（平均および標準偏差）のために、10回のIMD測定が含まれています。固定小数点演算の誤差は、場合によって顕著に出ます。全体として、測定誤差と応答時間は、UL 2231-2の要件（±15%、10秒）を十分に下回っています。

図3-6において、非対称型フォルトの場合、表示される誤差はフォルト状態のRisoとなります。「1MΩ – 1MΩ」の場合、時定数が非常に大きいため、解決に3秒のサイクル時間が必要です。

図3-6. IMD Riso 測定誤差、1000VDC、2秒サイクル

図3-7. IMD Ciso 誤差、1MΩ ~ 100kΩ、2秒 サイクル

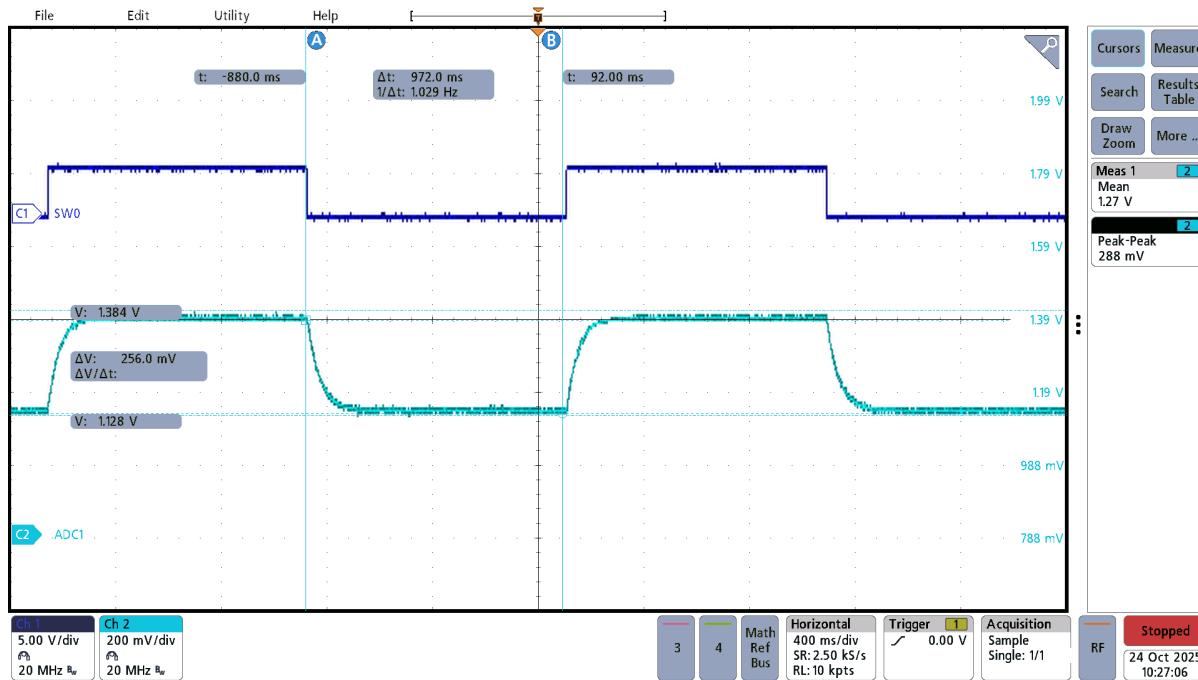

図 3-8 では、時定数が比較的短いため、最終的な定常状態電圧を予測する必要はありません。

図 3-8. 800VDC、 $0.1\mu\text{F}$ 、 $1\text{M}\Omega$  対称条件でのスイッチング波形キャプチャ

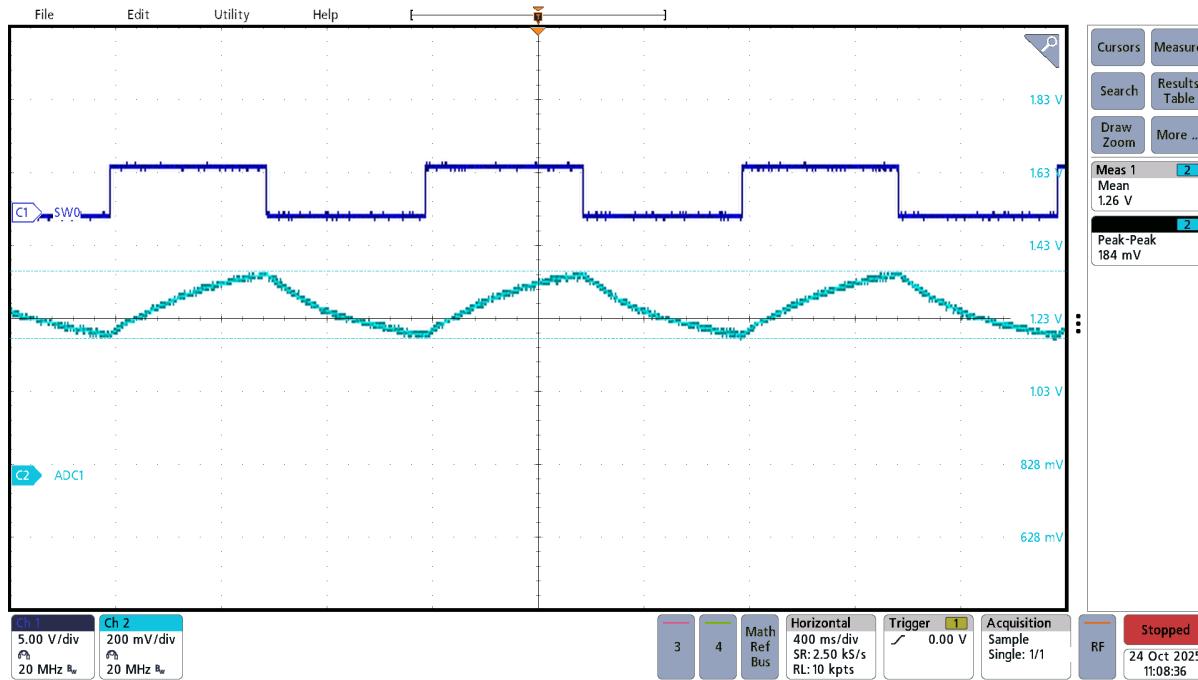

図 3-9 では、時定数が比較的長いため、最終的な定常状態電圧を予測する必要があります。

図 3-9. 800VDC、 $1\mu\text{F}$ 、 $1\text{M}\Omega$  対称条件でのスイッチング波形キャプチャ

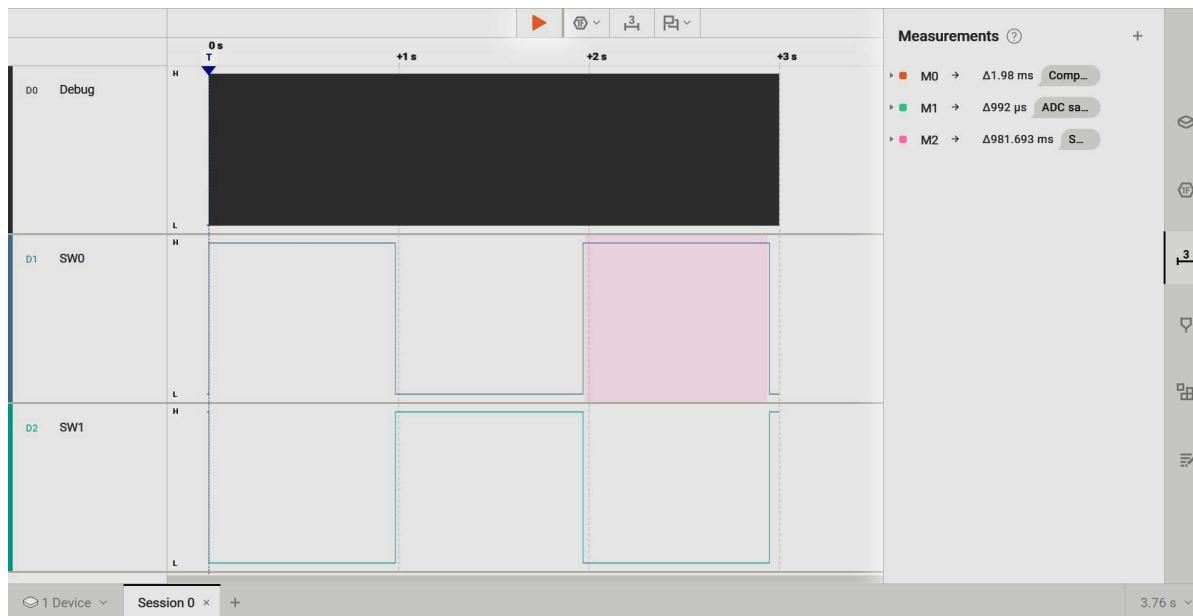

図 3-10 に、スイッチングのタイミング図を示します。各スイッチ状態は約 980ms オンのままであることに注意してください。ADC サンプリング周期は約 1ms です。ADC アクイジション期間後の計算時間は約 1.98ms です。

図 3-10. スイッチング タイミング図

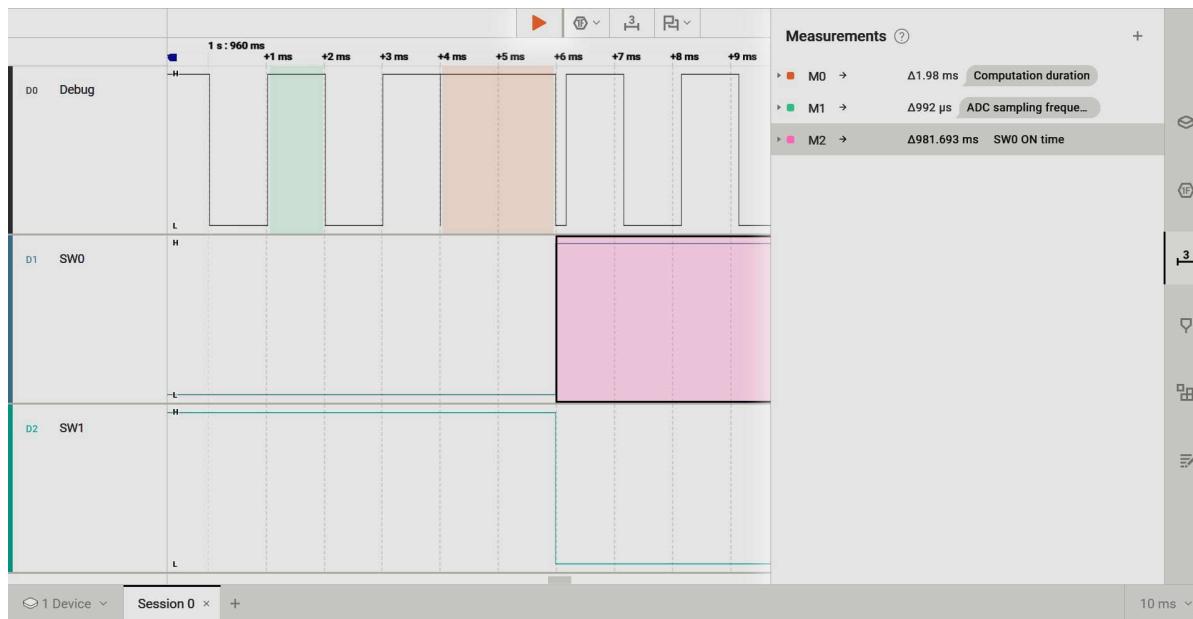

図 3-11 では、未知数の予測や算出など、すべての数学的な計算にかかった時間が約 2ms であることを示しています。

図 3-11. タイミング図の拡大図

## 4 設計とドキュメントのサポート

### 4.1 デザイン ファイル

#### 4.1.1 回路図

回路図をダウンロードするには、[TIDA-010985](#) のデザイン ファイルを参照してください。

#### 4.1.2 BOM

部品表 (BOM) をダウンロードするには、[TIDA-010985](#) のデザイン ファイルを参照してください。

#### 4.1.3 PCB レイアウトに関する推奨事項

PCB レイアウトは、絶縁定格や設計で選択する部品など、特定の設計要件に応じて変動する場合があります。

- 基本的には、デバイス固有の推奨レイアウトについては、各デバイスのデータシートに記載されたガイドラインを参照してください。

- HV システム設計では、PCB のレイアウトを行う際に、空間距離と沿面距離のルールが重要な要素となります。汚染度、動作電圧、材料特性、その他の環境要因 (高度、湿度など) が、特定の設計における沿面距離および空間距離の要件に影響を及ぼすことがあります。これらは通常、IEC-61851-1 や UL-2202 などの規格で規定されています。

- ノイズ結合を最小限に抑えるため、デジタル信号とアナログ信号を近くに配線しないようにしてください。適切なグランドプレーンを設け、シールド、最小限の信号ループ領域、フィルタを使用することで、ノイズを制御できます。

- TIDA-010985 は、TI LaunchPad と組み合わせて動作する、モジュール性重視の考えに基づいた AFE リファレンス デザインの例です。理想的には、MCU の ADC を AFE と同じ PCB 上に配置し、パターン長を最短にすることで、システムの性能を向上させます。

#### 4.1.3.1 レイアウト プリント

レイヤ プロットをダウンロードするには、[TIDA-010985](#) のデザイン ファイルを参照してください。

### 4.2 ツールとソフトウェア {必須トピック}

#### ツール

|           |                                    |

|-----------|------------------------------------|

| CCSTUDIO  | Code Composer Studio™ 統合開発環境 (IDE) |

| MSPM0-SDK | MSPM0 ソフトウェア開発キット (SDK)            |

#### ソフトウェア (該当する場合)

|        |        |

|--------|--------|

| ソフトウェア | 説明テキスト |

|--------|--------|

### 4.3 ドキュメントのサポート

1. テキサス インスツルメンツ、[『高電圧 EV 充電および太陽光エネルギー分野での絶縁監視用 AFE』リファレンス デザイン ガイド](#)

2. テキサス インスツルメンツ、[『TPSI2240-Q1 1200V, 50mA、アバランシェ保護付き、車載用強化ソリッド ステート リレー』データシート](#)

3. テキサス インスツルメンツ、[『RES60A-Q1 車載用、1400V<sub>DC</sub>、高精度分圧抵抗』データシート](#)

4. テキサス・インスツルメンツ、[『MSPM0G3507 LaunchPad 開発キット \(LP-MSPM0G3507\)』ユーザー ガイド](#)

slau873

### 4.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

## 4.5 商標

テキサス・インスツルメンツの™, LaunchPad™, Code Composer Studio™, and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

MATLAB® is a registered trademark of The MathWorks, Inc.

USB Type-C® is a registered trademark of USB Implementers Forum.

すべての商標は、それぞれの所有者に帰属します。

## 5 著者について

**KELVIN LE**、テキサス インスツルメンツのシステム エンジニア。EV 充電を中心に、エネルギー分野におけるシステム設計の開発に従事。テキサス インスツルメンツには、2015 年より勤務。セントラル オクラホマ大学で生体医工学の理学士号を取得。テキサス大学オースティン校で電気およびコンピュータ工学の理学修士号を取得。

**ANDREAS LECHNER**、テキサス インスツルメンツのエネルギー インフラおよび再生可能エネルギー部門のシステム チームで働くシステム エンジニア。ドイツ ランツフートにある応用科学大学で電気工学の修士号を取得。

## 6 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (December 2025) to Revision A (January 2026) | Page |

|----------------------------------------------------------------------|------|

| • TPSI2240-Q1 デバイスをサポートするようにブロック図を更新。                                | 1    |

| • DC 非接地配電システムの絶縁監視デバイスを更新。                                          | 2    |

| • TPSI2240-Q1 デバイスをサポートするようにブロック図を更新。                                | 5    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月