*Application Note***DP83TC812、DP83TC813、およびDP83TC814:Open Alliance 仕様準拠のための構成****概要**

Open Alliance (OA) は、100Base-T1 PHY に対してさまざまなテストを実施することを要求しています。このドキュメントでは、DP83TC812、DP83TC813、DP83TC814（以下では **DP83TC81x**）デバイスを必要なテストモードに移行して、さまざまな Open Alliance テストを実行する手順について説明しています。

このドキュメントには、DP83TC81x のテスト中に使用されたソフトウェアおよびハードウェアの構成について記載されています。この構成は、さまざまな OA コンプライアンス ハウスでテストされています。UNH、FTZ、および C&S を最小要件として扱う必要があります。ハードウェアとソフトウェアの追加構成を使用すると、お客様のシステム使用事例に基づいてさらに改善することができます。

**目次**

|                             |    |

|-----------------------------|----|

| 1はじめに.....                  | 2  |

| 2ハードウェアの構成.....             | 2  |

| 2.1回路図.....                 | 2  |

| 3ソフトウェアの設定.....             | 7  |

| 4PMA テスト.....               | 10 |

| 4.1 PMA テスト手順.....          | 10 |

| 5IOP テスト:リンクアップとリンクダウン..... | 11 |

| 5.1 IOP テスト手順.....          | 11 |

| 6SQI テスト.....               | 12 |

| 6.1 SQI 値の解釈.....           | 12 |

| 7TDR テスト.....               | 13 |

| 7.1 TDR テスト手順.....          | 13 |

| 8EMC と EMI のテスト.....        | 15 |

| 9改訂履歴.....                  | 16 |

**図の一覧**

|                                                                      |   |

|----------------------------------------------------------------------|---|

| 図 2-1. 電源ネットワーク:スリープ モード要件を持つアプリケーションの場合 (DP83TC812).....            | 2 |

| 図 2-2. 電源ネットワーク:スリープ モード要件を持つアプリケーションの場合 (DP83TC813).....            | 3 |

| 図 2-3. 電源ネットワーク:スリープ モード要件なしアプリケーション用 (DP83TC812 および DP83TC814)..... | 4 |

| 図 2-4. 電源ネットワーク:スリープ モード要件なしアプリケーション用 (DP83TC813).....               | 5 |

| 図 2-5. MDI と水晶振動子の回路図.....                                           | 5 |

**表の一覧**

|                                        |    |

|----------------------------------------|----|

| 表 2-1. パラメーター、構成要素、および値.....           | 5  |

| 表 3-1. マスタ モード構成.....                  | 7  |

| 表 3-2. スレーブ モード構成.....                 | 9  |

| 表 4-1. PMA テストモードのプログラミング.....         | 10 |

| 表 6-1. レジスタビット 0x871[3:1] の SQI 値..... | 12 |

| 表 7-1. TDR の実行手順.....                  | 13 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

DP83TC81x は、次の Open Alliance (OA) 仕様に従って評価しました。

- FTZ Zwickau によるトランシーバ用 Open Alliance 100BASE-T1 EMC テスト仕様 - リビジョン 2.0

- OPEN Alliance 100BASE-T1 相互運用性テストスイート v1.0 (C&S Group, GmbH 発行)

- ニューハンプシャー大学 (UNH) Inter-operability Lab による物理符号化副層 (v.1.0)、PHY 制御 (v.1.0)、物理メディア接続 (v.1.2) の Open Alliance 100BASE-T1 テスト仕様。

このアプリケーションノートでは、前述のすべてのテストに使用された独自のハードウェアおよびソフトウェアの構成について詳細を説明します。

このドキュメントには、これらのテストに必要な手順の詳細も記載されています。これは、対応する ECU レベル テストを実施するお客様に役立つはずです。

## 2 ハードウェアの構成

### 2.1 回路図

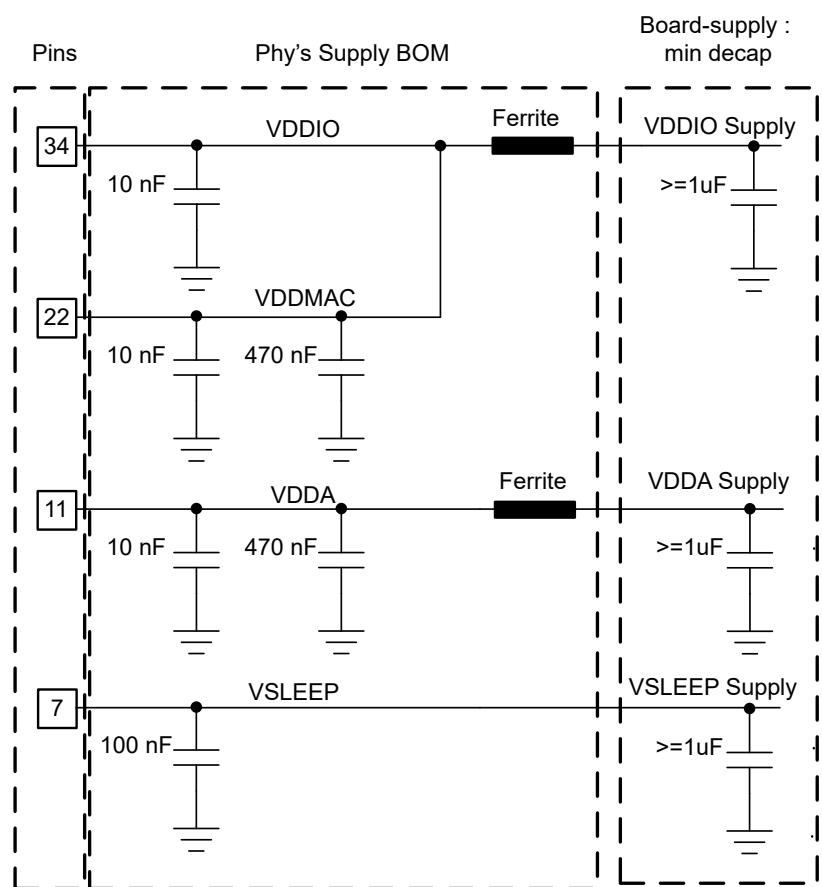

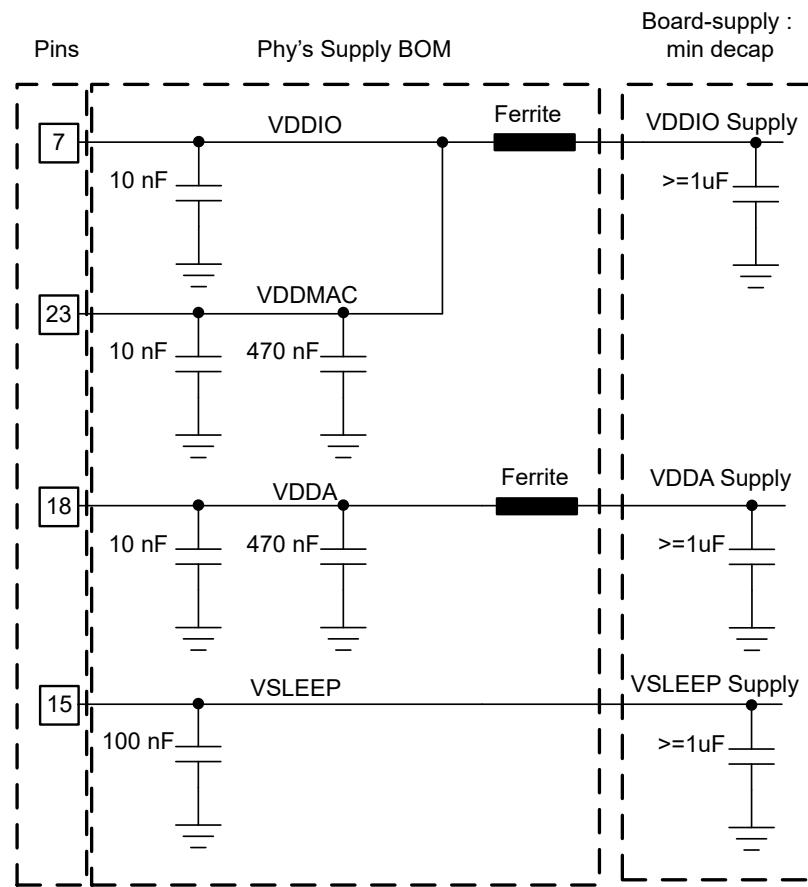

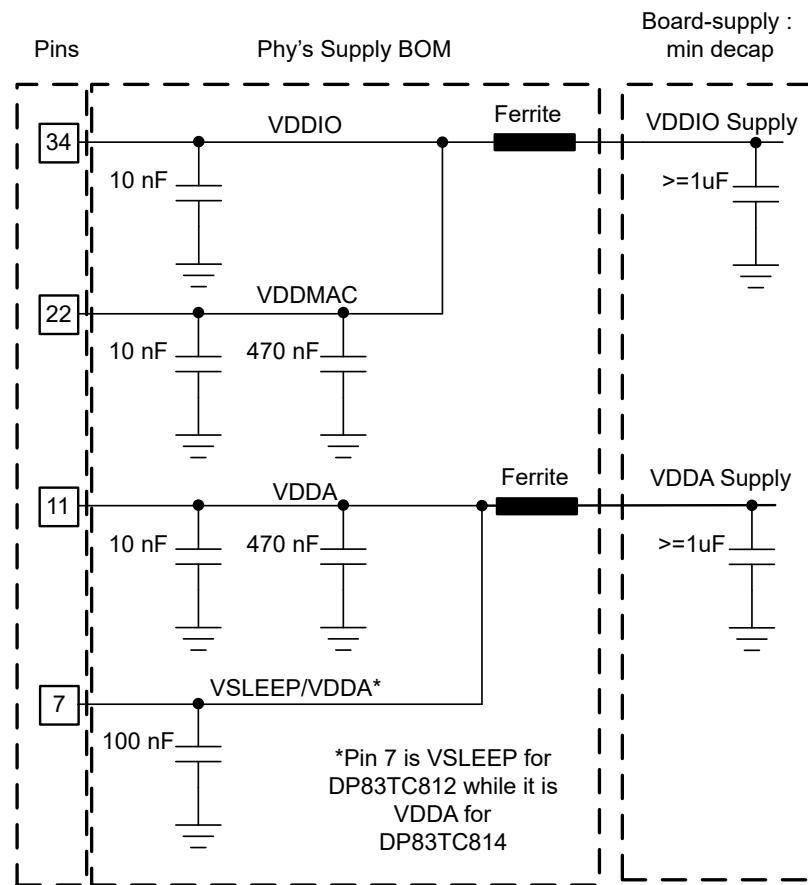

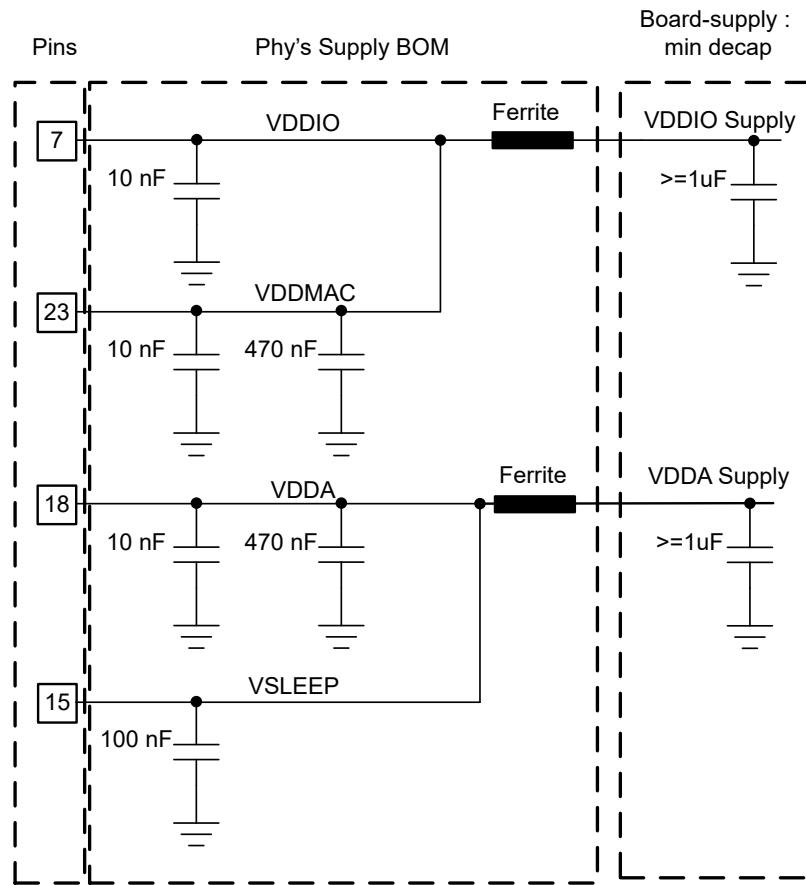

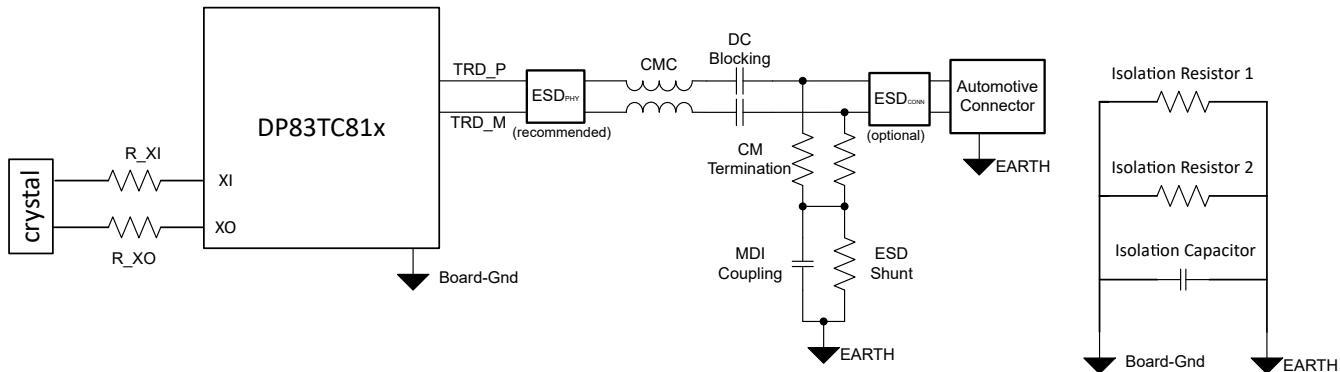

100Base-T1 PHY の性能には、MDI、リファレンス クロック、電源ネットワーク向けの回路図と適切な部品が重要です。このセクションでは、OA TC-1 のテストで使用する推奨回路図と部品の値を示します。

図 2-1. 電源ネットワーク: スリープ モード要件を持つアプリケーションの場合 (DP83TC812)

図 2-2. 電源ネットワーク:スリープ モード要件を持つアプリケーションの場合 (DP83TC813)

図 2-3. 電源ネットワーク:スリープ モード要件なしアプリケーション用 (DP83TC812 および DP83TC814)

図 2-4. 電源ネットワーク:スリープ モード要件なしアプリケーション用 (DP83TC813)

図 2-5. MDI と水晶振動子の回路図

表 2-1. パラメーター、構成要素、および値

| パラメータ   コンポーネント                                  | 値                   |

|--------------------------------------------------|---------------------|

| $V_{DDIO}   V_{DDMAC}$                           | 1.8V, 2.5V、または 3.3V |

| デカップリングコンデンサ $V_{DDIO}$                          | 10nF                |

| デカップリングコンデンサ $V_{DDMAC}$                         | 10nF, 470nF         |

| $V_{DDIO}   V_{DDMAC}$ <sup>1</sup> 用一体型フェライトビーズ | BLM18KG601SH1       |

| $V_{DDA}$                                        | 3.3V                |

| デカップリングコンデンサ $V_{DDA}$                           | 10nF, 470nF         |

| (選択可能): $V_{DDA}$ 用フェライトビーズ                      | BLM18KG601SH1       |

| $V_{sleep}$                                      | 3.3V                |

**表 2-1. パラメーター、構成要素、および値 (続き)**

| パラメータ   コンポーネント                  | 値                                                                                                                        |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| デカップリング コンデンサ $V_{sleep}$        | $0.1\mu F$                                                                                                               |

| DC ブロッキング コンデンサ (精度 1%、100V)     | $0.1\mu F$                                                                                                               |

| コモン モード チョーク                     | DLW43MH201XK2L, DLW32MH201XK2, AE2002, ACT1210L-201                                                                      |

| 同相終端抵抗 (精度 1%、0.75W、サイズ:2010)    | $1k\Omega$                                                                                                               |

| MDI カップリング コンデンサ                 | $4.7nF$                                                                                                                  |

| ESD シャント (5% 精度、0.125W、サイズ:0805) | $100k\Omega$                                                                                                             |

| 絶縁抵抗 1 (0.25W、サイズ:1206)          | $0 \Omega$                                                                                                               |

| 絶縁抵抗 2 (0.25W、サイズ:1206)          | $0 \Omega$                                                                                                               |

| 絶縁型コンデンサ                         | 未実装                                                                                                                      |

| R_XI                             | $100 \Omega$                                                                                                             |

| R_XO                             | 水晶のワット数仕様に必要な最小値                                                                                                         |

| ESD <sub>CONN</sub> (オプション)      | 100V を上回るクランプ電圧と負荷容量が 5pF 未満の ESD 抑制デバイス向けに、Open Alliance 100BASE-T1 EMC テスト仕様で認定済みの ESD デバイス。<br>PESD1ETH1GLS-Q を例にします。 |

| ESD <sub>PHY</sub> (推奨)          | PESD2ETHX-Q。V <sub>CC</sub> ピンを 3.3V レールに接続します。これにより、イーサネットケーブルがバッテリに短絡した場合や、100V 未満のその他の過渡事象から保護できます。                   |

- (1) V<sub>PDIO</sub> が V<sub>DDMAC</sub> から分離している場合、V<sub>DDIO</sub> にフェライトビーズと  $0.47\mu F$  コンデンサを追加する必要があります。このフェライトビーズの部品番号は、BLM18KG601SH1。

### 3 ソフトウェアの設定

このセクションでは、さまざまな OA コンプライアンス テスト ハウスでのテスト中に使用される DP83TC81x のレジスタ設定について説明します。これらの設定は、最小要件として推奨されます。システム レベルまたはボード レベルの制約によって必要に応じて、さらにパラメータをプログラムできます。記載されているデフォルト値は、デバイスの電源投入時またはハードリセット時に読み取られます。

PHY は、自律モードまたは管理モードに構成するためのブート ストラップ オプションをサポートしており、デフォルトでは自律モードになっています。[表 3-1](#) および [表 3-2](#) のソフトウェア設定の実行中にリンクアップ プロセスが開始されないように、管理モード ストラップ オプションを推奨します。ソフトウェア構成が完了したら、ビット 0x18B[6] を 1 に設定することで、PHY を管理モードから削除できます。

**表 3-1. マスタ モード構成**

| MMD | レジスタ  | 値     | 説明                            |

|-----|-------|-------|-------------------------------|

| 1f  | x001F | x8000 | ハードリセット                       |

| 1f  | x0523 | x0001 | 設定が完了するまでリンクアップの開始をディセーブルにします |

| 01  | x0834 | xC000 | PHY をマスタ モードで設定します            |

| 1f  | x081C | x0FE2 | 相互運用性のための設定                   |

| 1f  | x0873 | x0021 | 相互運用性のための設定                   |

| 1f  | x089E | x0010 | 相互運用性のための設定                   |

| 1f  | x0874 | x6866 | 相互運用性のための設定                   |

| 1f  | x0875 | x6868 | 相互運用性のための設定                   |

| 1f  | x0812 | x00EE | 相互運用性のための設定                   |

| 1f  | x0816 | x0300 | 相互運用性のための設定                   |

| 1f  | x0806 | x293A | 相互運用性のための設定                   |

| 1f  | x0807 | x3348 | 相互運用性のための設定                   |

| 1f  | x0808 | x3D56 | 相互運用性のための設定                   |

| 1f  | x083E | x045F | 相互運用性のための設定                   |

| 1f  | x0834 | x8000 | 相互運用性のための設定                   |

| 1f  | x0862 | x0330 | 相互運用性のための設定                   |

| 1f  | x0896 | x32CB | 相互運用性のための設定                   |

| 1f  | x003E | x0009 | 相互運用性のための設定                   |

| 1f  | x0848 | x0030 | 相互運用性のための設定                   |

| 1f  | x0830 | x0143 | 相互運用性のための設定                   |

| 1f  | x080A | x0015 | 相互運用性のための設定                   |

| 1f  | x0820 | x03AA | 相互運用性のための設定                   |

| 1f  | x0826 | x1407 | 相互運用性のための設定                   |

| 1f  | x083D | x0047 | 相互運用性のための設定                   |

| 1f  | x086C | x1336 | 相互運用性のための設定                   |

| 1f  | x0856 | x1000 | 相互運用性のための設定                   |

| 1f  | x0842 | xBAB8 | 相互運用性のための設定                   |

| 1f  | x08F3 | x0015 | 相互運用性のための設定                   |

| 1f  | x08AD | x0019 | 相互運用性のための設定                   |

| 1f  | x08ED | x001D | 相互運用性のための設定                   |

| 1f  | x08EF | x0021 | 相互運用性のための設定                   |

| 1f  | x08F0 | x0025 | 相互運用性のための設定                   |

| 1f  | x08F1 | x0029 | 相互運用性のための設定                   |

| 1f  | x08F2 | x002D | 相互運用性のための設定                   |

**表 3-1. マスタ モード構成 (続き)**

| MMD | レジスタ  | 値     | 説明                                           |

|-----|-------|-------|----------------------------------------------|

| 1f  | x0456 | x0021 | MAC インターフェイス IO ドライバのスルーレートを低減します            |

| 1f  | x0452 | x0303 |                                              |

| 1f  | x0453 | x0003 | (選択可能): CLKOUT および LED 出力をディセーブルにして、放射を低減します |

| 1f  | x045F | x000F |                                              |

| 1f  | x085A | x3000 | RF 耐性性能を向上させる構成                              |

| 1f  | x085B | x3000 |                                              |

| 1f  | x0189 | x0018 | TC10 相互運用性の設定                                |

| 1f  | x018B | x144B |                                              |

| 1f  | x0154 | x0220 | 相互運用性のための設定                                  |

| 1f  | x001F | x4000 | ソフトリセット                                      |

| 1f  | x0523 | x0000 | 設定終了後にリンクアップ開始をイネーブルにします                     |

**表 3-2. スレーブ モード構成**

| MMD | レジスタ  | 値     | 説明                                           |

|-----|-------|-------|----------------------------------------------|

| 1f  | x001F | x8000 | ハードリセット                                      |

| 1f  | x0523 | x0001 | 設定が完了するまでリンクアップの開始をディセーブルにします                |

| 01  | x0834 | x8000 | PHY をスレーブ モードに構成します                          |

| 1f  | x0862 | x0330 | 相互運用性のための設定                                  |

| 1f  | x086E | x1868 | 相互運用性のための設定                                  |

| 1f  | x0812 | x00F4 | 相互運用性のための設定                                  |

| 1f  | x0816 | x0300 | 相互運用性のための設定                                  |

| 1f  | x0873 | x0021 | 相互運用性のための設定                                  |

| 1f  | x0896 | x22FF | 相互運用性のための設定                                  |

| 1f  | x089E | x0000 | 相互運用性のための設定                                  |

| 1f  | x08F3 | x0015 | 相互運用性のための設定                                  |

| 1f  | x08AD | x0019 | 相互運用性のための設定                                  |

| 1f  | x08ED | x001D | 相互運用性のための設定                                  |

| 1f  | x08EF | x0021 | 相互運用性のための設定                                  |

| 1f  | x08F0 | x0025 | 相互運用性のための設定                                  |

| 1f  | x08F1 | x0029 | 相互運用性のための設定                                  |

| 1f  | x08F2 | x002D | 相互運用性のための設定                                  |

| 1f  | x0456 | x0021 | MAC インターフェイス IO ドライバのスルーレートを低減します            |

| 1f  | x0452 | x0303 | (選択可能): CLKOUT および LED 出力をディセーブルにして、放射を低減します |

| 1f  | x0453 | x0003 |                                              |

| 1f  | x045F | x000F |                                              |

| 1f  | x085A | x3000 | RF 耐性性能を向上させる構成                              |

| 1f  | x085B | x3000 |                                              |

| 1f  | x0189 | x0018 | TC10 相互運用性の設定                                |

| 1f  | x018B | x144B |                                              |

| 1f  | x0154 | x0220 | 相互運用性のための設定                                  |

| 1f  | x001F | x4000 | ソフトリセット                                      |

| 1f  | x0523 | x0000 | 設定終了後にリンクアップ開始をイネーブルにします                     |

## 4 PMA テスト

OA TC-1 は、100Base-T1 PHY のフロント エンドに対するさまざまな電気的テストを規定しています。標準文書には、各種テスト モードが記載されています。各テスト モードでは、PHY は MDI ライン上でパターンを生成するか、異なる電気的 パラメータを測定するためにピンに内部クロック信号を露出することを想定しています。

DP83TC81x は、これらすべてのテスト モードをサポートしています。このセクションでは、各テスト モードに移行するため に必要な構成について詳しく説明します。

ご要望に応じて、UNH (OA 準拠テストハウス) から OA と IEEE に準拠した結果を記載した PMA テストレポートの詳細 を入手できます。

### 4.1 PMA テスト手順

---

#### 注

- いずれかのテスト モードをプログラムする前に、DP83TC81x にそれぞれの初期化レジスタ構成 (マスクまたはスレーブ) をロードする必要があります (を参照) [セクション 3](#)。

**表 4-1. PMA テスト モードのプログラミング**

| テスト モード                                     | MMD        | レジスタ             | 値                                                         |

|---------------------------------------------|------------|------------------|-----------------------------------------------------------|

| テスト モード 1                                   | x01        | 0x0836           | 0x2000                                                    |

| テスト モード 2                                   | x01        | 0x0836           | 0x4000                                                    |

| テスト モード 4:CLKOUT<br>ピン上の Tx_Tclk 25<br>MHz。 | x01<br>x1F | 0x0836<br>0x045F | 0x8000<br>0x000D<br>(DP83TC812/814)<br>0x0007 (DP83TC813) |

| テスト モード 5                                   | x01        | 0x0836           | 0xA000                                                    |

## 5 IOP テスト:リンクアップとリンクダウン

OA TC-1 は、リンクアップ時間、リンクダウン時間、リンクの安定性をテストするためのさまざまな PHY レベル テストを規定しています。このセクションでは、PHY レベルのテストに使用されるこれらの IOP テストに使用されるテスト シーケンスを強調し、ECU レベルのテストにも同じものを移植できます。

TC-1 の相互運用性テストは、OA コンプライアンス テスト ハウス C&S によって実施されています。DP83TC81x の相互運用性をテストするため、C&S は、DP83TC81x と他の 100Base-T1 認証済み PHY をリンク パートナーとして使用して、これらの各パラメータをテストします。これらのパラメータは、さまざまな温度やケーブル長について多数の反復テストを行います。

ご要望に応じて、C&S (米国と欧州、中東、アフリカ) に準拠した結果を記載した IOP テスト レポートを入手できます。

### 5.1 IOP テスト手順

次の IOP テスト手順を使用します。

- 測定開始:

電源投入後またはハードウェアリセット後どちらかでリンクアップ時間を測定する IOP テストでは、初期化構成が DP83TC81x にロードされた後でリンクアップ時間の測定を開始することが重要です。構成がコントローラによって PHY にロードされるため、最後の構成レジスタに書き込まれた後、表示 (ソフトウェアビットまたは IO 状態) をコントローラに行なうことを推奨します。このインジケータが **high** になることは、リンクアップ時間の測定開始です。

- ポーリングするステータス:

リンクステータスはレジスタ 0x1 のビット 2 で示されます。1 = リンクアップ、0 = リンクダウン。これらのテスト中、リンクアップまたはリンクダウンのイベントを示すために、この状態をポーリングする必要があります。

#### 注

- 電源投入後に自動リンクアップが必要ない場合 (初期化スクリプトの書き込み後にのみリンクを発生させる)、DP83TC81x の管理モードを使用するために、ピン LED\_1 のストラップを使用する必要があります。

- PHY は、自律モードまたは管理モードに構成するためのブートストラップ オプションをサポートしており、デフォルトでは自律モードになっています。ソフトウェア設定の実行中にリンクアップ プロセスが開始されないように、管理モード ストラップ オプションを推奨します。ソフトウェア構成が完了したら、ビット 0x18B[6] を 1 に設定することで、PHY を管理モードから削除できます。

## 6 SQI テスト

SQI は、銅ケーブルの信号品質を示します。

OA TC-1 は、ノイズ レベルの増加に伴って SQI 値が単調に減少することを示しています。

ご要望に応じて、C&S (米国と欧州、中東、アフリカ) に準拠した結果を記載した SQI テスト レポートを入手できます。

### 6.1 SQI 値の解釈

レジスタ ビット 0x871[3:1] には SQI の値が含まれます。このレジスタをポーリングして、各 SQI 値に対する適切な MSE 値の範囲を理解できます。

**表 6-1. レジスタ ビット 0x871[3:1] の SQI 値**

| 0x871 [3:1] | OPEN ALLIANCE SQI | MSE 値          |

|-------------|-------------------|----------------|

| 0x0         | SQI = 0 (ワースト)    | MSE > 133      |

| 0x1         | SQI = 1           | 11 < MSE ≤ 133 |

| 0x2         | SQI = 2           | 7 < MSE ≤ 11   |

| 0x3         | SQI = 3           | 5 < MSE ≤ 7    |

| 0x4         | SQI = 4           | 4 < MSE ≤ 5    |

| 0x5         | SQI = 5           | 3 < MSE ≤ 4    |

| 0x6         | SQI = 6           | 2 < MSE ≤ 3    |

| 0x7         | SQI = 7 (ベスト)     | MSE ≤ 2        |

## 7 TDR テスト

このセクションでは、ケーブルの断線または短絡の障害をテストする手順について説明します。

ご要望に応じて、C&S から OA に準拠した結果を含む詳細な TDR テストレポート入手できます。

### 注

C&S テストで実施された OA TC-1 テストは、開路および短絡ケーブルフォルトのテストケース用です。また、TDR はリンクがない場合に根本原因を見つけるために通常実行されます。[セクション 7.1](#) に記載されているテスト手順には、コンプライアンス テストの手順に追加のステップがあります。つまり、可能な場合はリンクダウン 状態を強制することです(必要に応じて使用)。

### 7.1 TDR テスト手順

**表 7-1. TDR の実行手順**

| シーケンス                           | 説明                                                                                                                                                                                           | レジスタの読み取り/書き込み                                                                                                                                                                                                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ステップ 1:<br>DP83TC81x をマスターとして使用 | レジスタを書き込んでリンクダウンを強制的に行い、リンク パートナーがサイレントになるようにします。<br>有効なオープンおよび短絡ケーブルフォルトが発生した場合でも、TDR はステップ 1 なしでも正常に動作します。<br>良好なケーブル ケースを得るために、TDR レジスタ 0x001E では、このステップをバイパスすると「Fail」(故障) と表示される場合があります。 | 書き込み<br>Reg[0x1834] = 0x8001<br>マスターを黙らせるために。                                                                                                                                                                                             |

| ステップ 1:<br>DP83TC81x をスレーブとして使用 | レジスタを書き込んでリンクダウンを強制的に行い、リンク パートナーがサイレントになるようにします。<br>有効なオープンおよび短絡ケーブルフォルトが発生した場合でも、TDR はステップ 1 なしでも正常に動作します。<br>良好なケーブル ケースを得るために、TDR レジスタ 0x001E では、このステップをバイパスすると「Fail」(故障) と表示される場合があります。 | DP83TC81x がリンク パートナーの場合、リンク パートナーに reg[0x1834] = 0x8001 を書き込み、サイレントにします。他の PHY を使用する場合は、ベンダにレジスタ書き込みを問い合わせてリンク パートナーをサイレントにします                                                                                                            |

| ステップ 2                          | TDR の構成: プレラン                                                                                                                                                                                | Reg[0x0523] = 0x0001 //送信ディセーブル<br>Reg[0x0827] = 0x4800<br>Reg[0x0301] = 0x1701<br>Reg[0x0303] = 0x023D<br>Reg[0x0305] = 0x0015<br>Reg[0x0831] = 0x3003<br>Reg[0x001F] = 0x4000<br>Reg[0x0523] = 0x0000 //送信イネーブル<br>Reg[0x001F] = 0x0000 |

| ステップ 3                          | Start TDR                                                                                                                                                                                    | Reg[0x001E(15)] = 1                                                                                                                                                                                                                       |

| ステップ 4                          | 100ms 待ちます (TDR が最大ケーブル長に収束するのに十分です)                                                                                                                                                         |                                                                                                                                                                                                                                           |

| ステップ 5                          | 0x001E[1:0] = [TDR 完了:TDR フェイル]。<br>値は [1,0] にする必要があります。故障タイプと位置は、この正しい値が読み出された場合にのみ有効です。<br>[1,0] 以外の値は、回線上にノイズが発生して TDR が失敗していることを意味します。                                                   |                                                                                                                                                                                                                                           |

**表 7-1. TDR の実行手順 (続き)**

| シーケンス                                                                                        | 説明                | レジスタの読み取り/書き込み                                             |  |

|----------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------|--|

| ステップ 6                                                                                       | 障害の種類と場所が読み取られます。 | フォルト ステータスとフォルト タイプについては、レジスタ 0x0310 を読み出します。<br>障害タイプの場合: |  |

| <b>TDR_TC-1 Reg 0x0310[7] = peak_detect</b>                                                  |                   |                                                            |  |

|                                                                                              | 0b                | フォルトが検出されない                                                |  |

|                                                                                              | 1b                | 故障検出                                                       |  |

| <b>TDR_TC-1 Reg 0x0310[6] = peak_sign</b>                                                    |                   |                                                            |  |

|                                                                                              | 0b                | 短絡                                                         |  |

|                                                                                              | 1b                | オープン                                                       |  |

| ** peak_sign ケーブルで障害が検出された場合にのみ有効です<br>有効なフォルトが検出された場合:レジスタ 0x0310[5:0] = フォルト位置で、単位はメートルです。 |                   |                                                            |  |

## 8 EMC と EMI のテスト

OA TC-1 は伝導 EMC および EMI テストを規定しています。DP83TC81x の場合、これらのテストは OA 準拠テスト ハウス FTZ で実施され、MDI の放射、各電源ピンの放射、RF 信号への耐性はテスト スイートの一部です。このボードは FTZ の OA 仕様に準拠して設計されています。

本書で説明しているハードウェアとソフトウェアの構成を、これらの伝導型 EMC および EMI テストに使用しました。アプリケーションに TC-1 仕様よりもさらに強化が必要な場合は、構成を使用できます。

ご要望に応じて、FTZ からの詳細なテストレポートと手順および OA 準拠の結果が提供されます。

伝導エミッション テスト (OA TC-1 準拠のため) 以外に、DP83TC81x (前述のハードウェアおよびソフトウェアの構成を使用) はさまざまな OEM のさまざまな放射エミッションおよび放射耐性要件に対するテストされています。放射エミッションと耐性テスト結果の詳細は、ご要望に応じて提供しています。設定は、アプリケーションでさらにマージンを強化する必要がある場合に使用できます。

## 9 改訂履歴

| Changes from Revision F (August 2025) to Revision G (December 2025) | Page              |

|---------------------------------------------------------------------|-------------------|

| • 相互運用性のためマスタとスレーブの構成を更新.....                                       | <a href="#">7</a> |

---

| Changes from Revision E (February 2025) to Revision F (August 2025) | Page              |

|---------------------------------------------------------------------|-------------------|

| • MDI ピンのオプションの ESD ダイオードの推奨事項を追加。.....                             | <a href="#">2</a> |

| • RGMII シフトおよび RMII モードで RX_CLK を確実にオンにするためのレジスタ 0x431 書き込みを追加..... | <a href="#">7</a> |

---

| Changes from Revision D (January 2025) to Revision E (February 2025) | Page              |

|----------------------------------------------------------------------|-------------------|

| • レジスタ 0x41C への書き込み後の遅延を追加.....                                      | <a href="#">7</a> |

---

| Changes from Revision C (July 2024) to Revision D (January 2025)                           | Page               |

|--------------------------------------------------------------------------------------------|--------------------|

| • 相互運用性のためマスタとスレーブの構成を更新.....                                                              | <a href="#">7</a>  |

| • TDR 事前実行から 0x0306 の書き込みを削除。0x310[8] 表示を削除。レジスタ 0x0831 の値を 0x3003 に変更。 <a href="#">13</a> | <a href="#">13</a> |

---

| Changes from Revision B (April 2024) to Revision C (July 2024) | Page              |

|----------------------------------------------------------------|-------------------|

| • マスタおよびスレーブ構成を追加のレジスタで更新.....                                 | <a href="#">7</a> |

---

| Changes from Revision A (May 2022) to Revision B (April 2024) | Page               |

|---------------------------------------------------------------|--------------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                          | <a href="#">1</a>  |

| • 0x18B[6] を更新.....                                           | <a href="#">7</a>  |

| • テスト モード 1 の注のコメントを削除.....                                   | <a href="#">10</a> |

| • 0x18B[6] ~ 0 から 0x18B[6] ~ 1 に変更.....                       | <a href="#">11</a> |

| • TDR プリラン構成に 0x0831 = 0x0903 書き込みを追加.....                    | <a href="#">13</a> |

---

| Changes from Revision * (December 2021) to Revision A (May 2022)                                                                                                                   | Page               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| • ドキュメント全体を通して DP83TC813 および DP83TC814 デバイスのサポートを追加.....                                                                                                                           | <a href="#">1</a>  |

| • 「パラメータ、部品、値」に ESD 部品の説明を追加。VDDA デカップリング コンデンサに関するオプションの通知を追加。VDDIO または VDDMAC のフェライトビーズの推奨事項を更新。VDDIO および VDDMAC フェライトビーズの脚注を追加。DP83TC813 および DP83TC814 に関する関連情報を含むように図を変更。..... | <a href="#">2</a>  |

| • 「電源ネットワーク」を追加:スリープ モード要件を持つアプリケーション(DP83TC813)の場合、電源ネットワーク:スリープ モードの要件を持たないアプリケーションでは、ペリフェラルの図を持つ代表的な DP83TC814 アプリケーションを紹介します。.....                                             | <a href="#">2</a>  |

| • DP83TC813 のテスト モード 4 コマンドを更新.....                                                                                                                                                | <a href="#">10</a> |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月