# AWR6843AOP シングルチップ 60~64GHz ミリ波センサ アンテナ搭載パッケージ (AOP)

## 1 特長

- FMCW トランシーバ

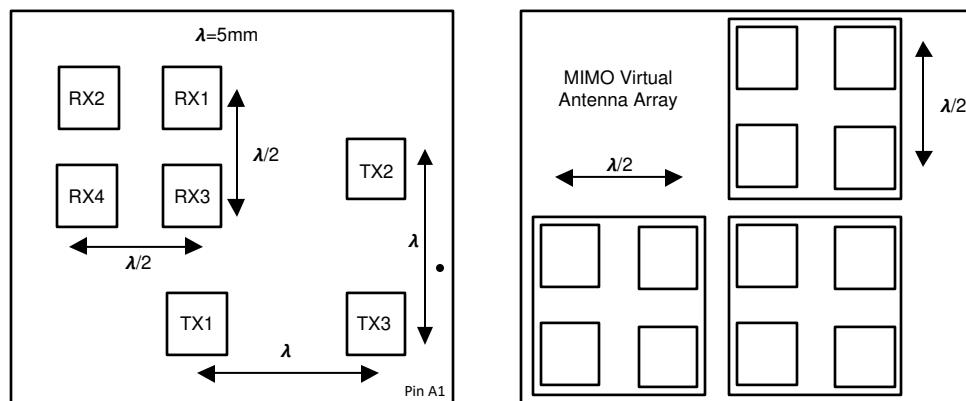

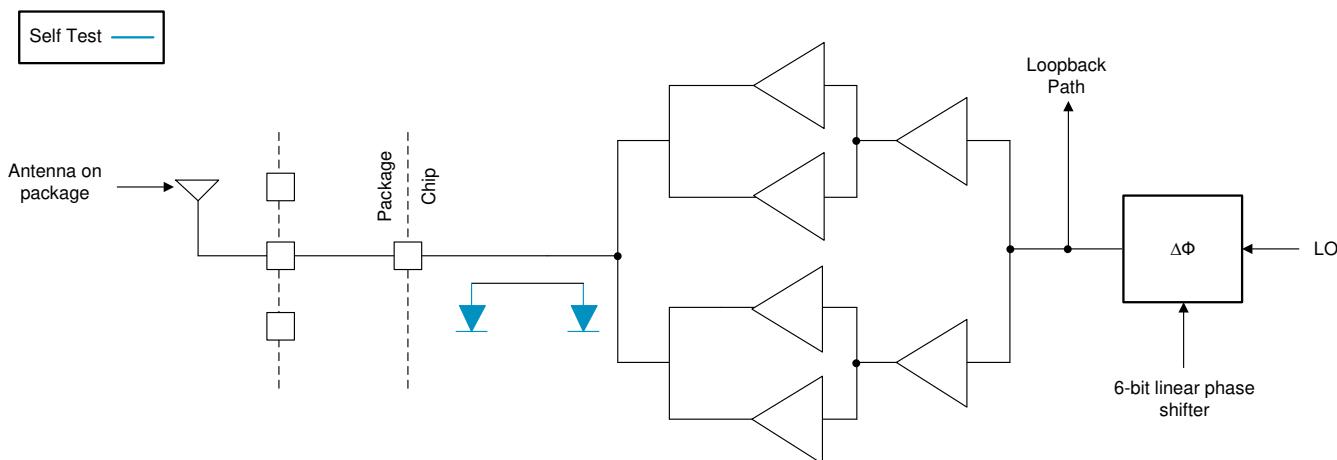

- 4 つのレシーバと 3 つのトランスマッタを内蔵したアンテナ オン パッケージ (AOP)

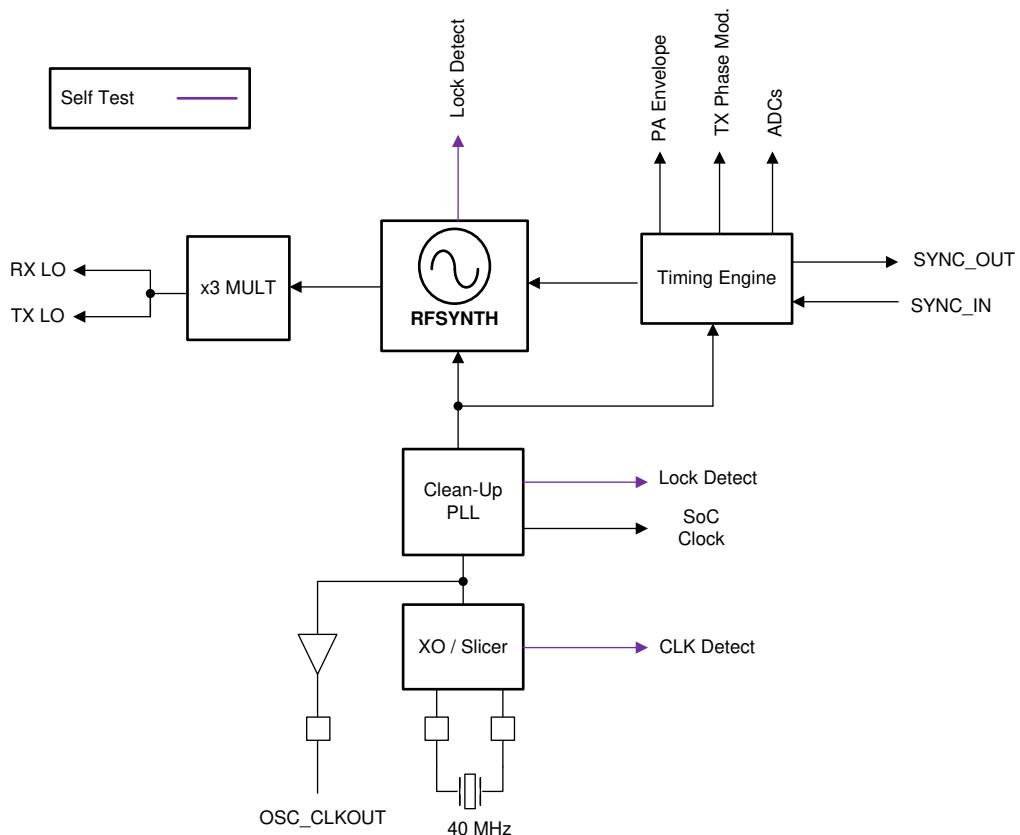

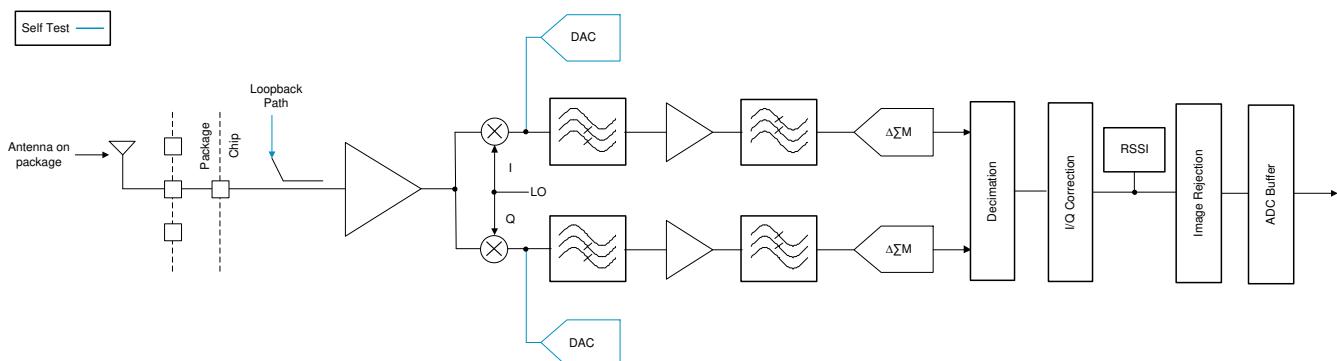

- PLL、トランスマッタ、レシーバ、ベースバンド、ADC を内蔵

- 60~64GHz 帯で、連続帯域幅 4GHz

- 6 ビット位相シフタをサポート

- フラクショナル N PLL を使用した超高精度のチャップ エンジン

- 較正および自己テストを内蔵

- Arm® Cortex®-R4F ベースの無線制御システム

- 内蔵ファームウェア (ROM)

- プロセスおよび温度の自己較正システム

- ホスト プロセッサの関与を必要としない自己監視機能を内蔵 (機能安全準拠デバイス)

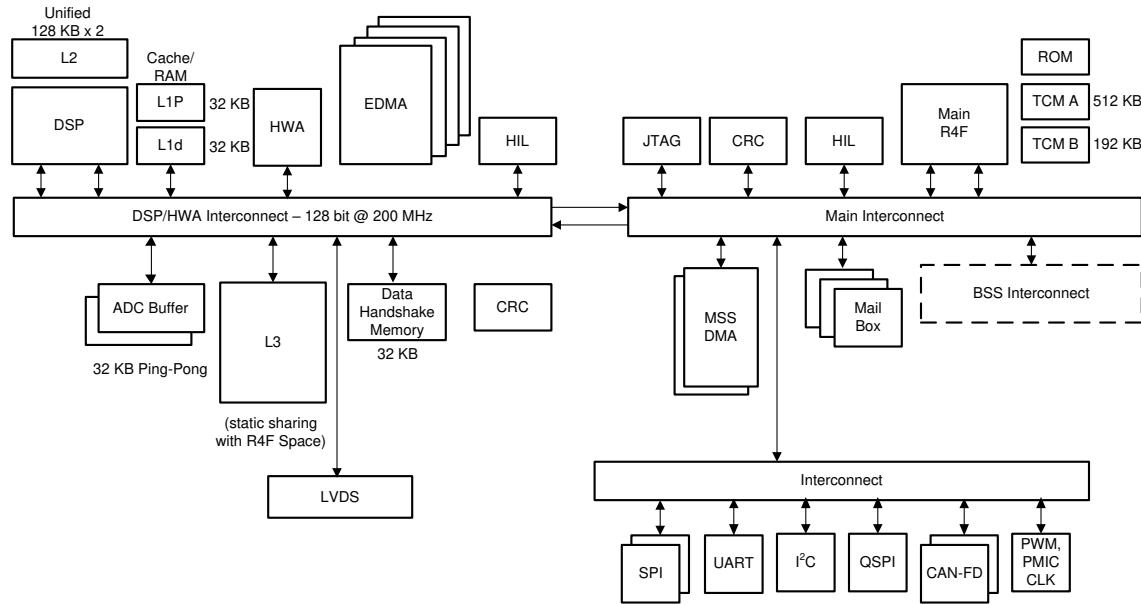

- C674x DSP による高度な信号処理 (AWR6843 のみ)

- FFT、フィルタリング、CFAR 処理用のハードウェア アクセラレータ

- メモリ圧縮

- 物体検出およびインターフェイス制御用の Arm® Cortex®-R4F マイクロコントローラ

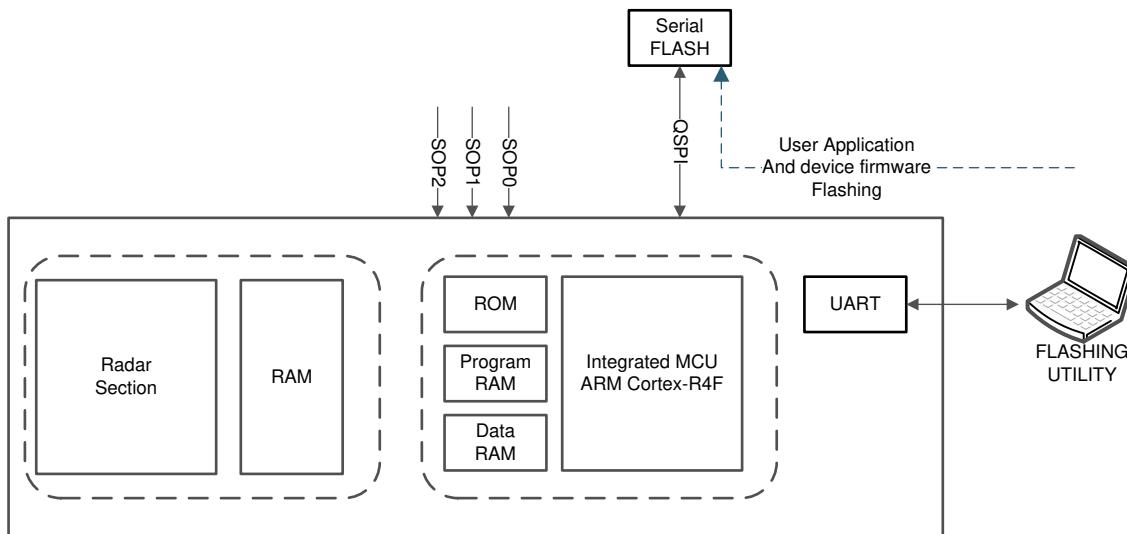

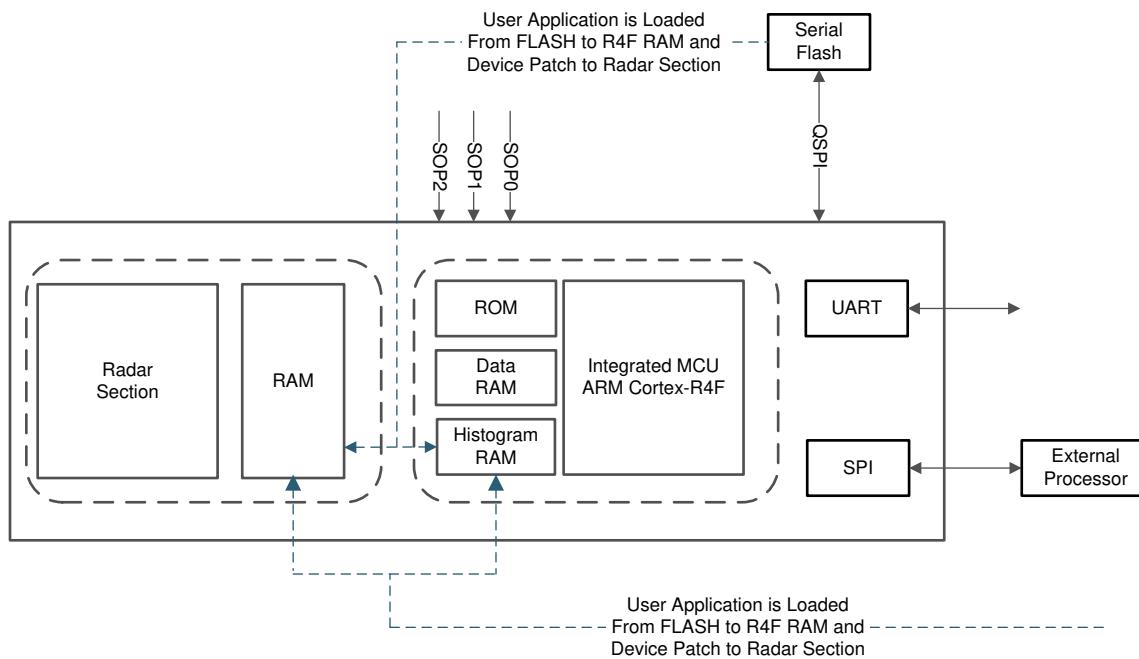

- 自律モード (QSPI フラッシュ メモリからのユーザー アプリケーションのロード) をサポート

- ECC 付き内部メモリ

- AWR6843: 1.75MB を以下に分割: MSS プログラム RAM (512KB)、MSS データ RAM (192KB)、DSP L1 RAM (64KB)、DSP L2 RAM (256KB)、L3 レーダー データ キューブ RAM (768KB)

- AWR6443: 1.4MB を以下に分割: MSS プログラム RAM (512KB)、MSS データ RAM (192KB)、L3 レーダー データ キューブ RAM (768KB)

- 許容されるサイズ変更をテクニカル リファレンスマニュアルに記載

- ユーザー アプリケーションで利用可能な他のインターフェイス

- 最大 6 つの ADC チャネル (低サンプル レートの監視)

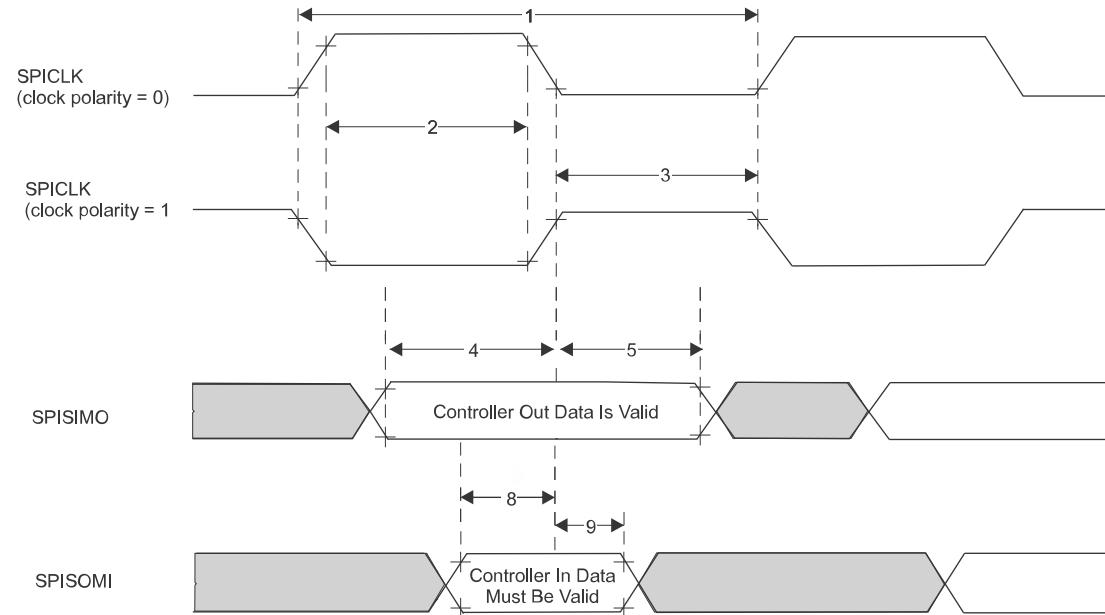

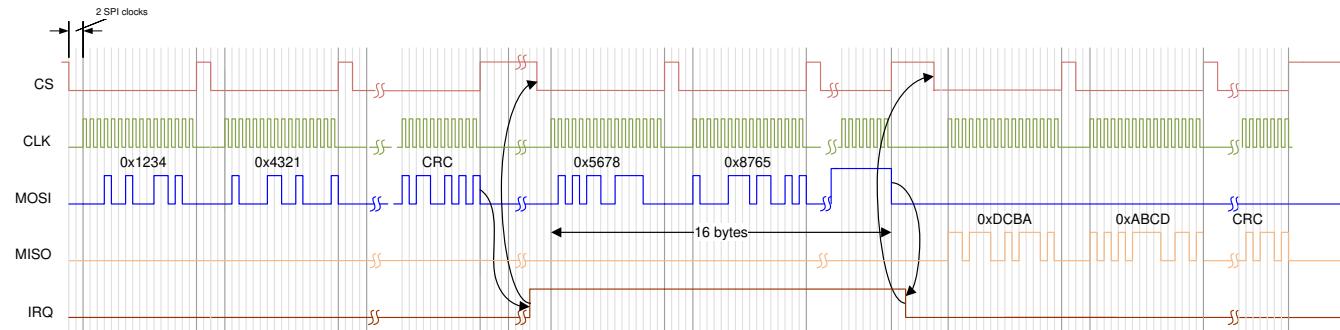

- 最大 2 つの SPI ポート

- 最大 2 つの UART

- 2 つの CAN-FD インターフェイス

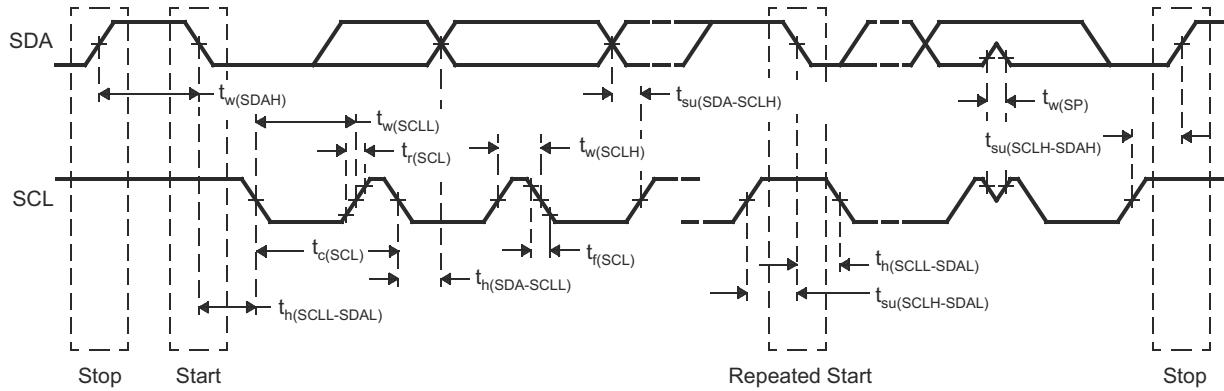

- I2C

- GPIO

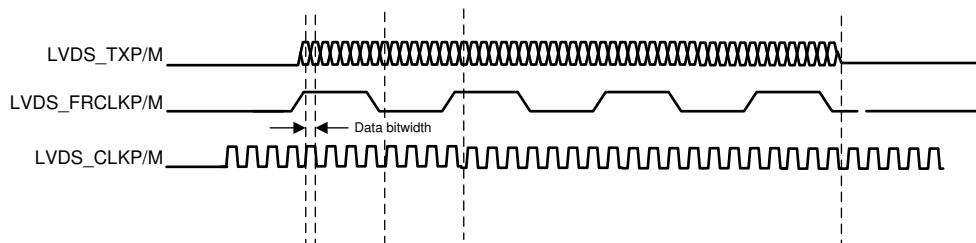

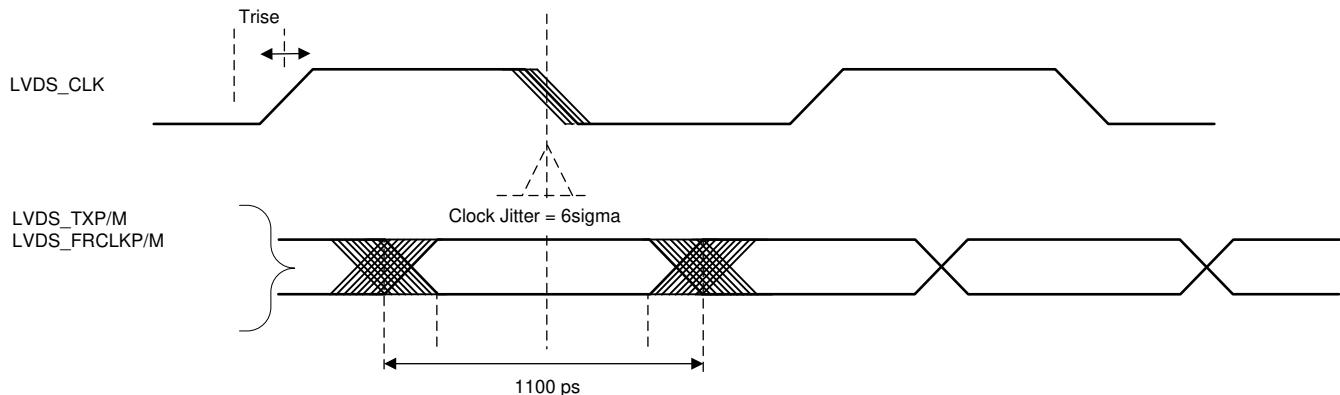

- 未加工 ADC データおよびデバッグ計測用の 2 レーンの LVDS インターフェイス

- デバイスのセキュリティ (一部の型番のみ)

- セキュア認証および暗号化ブートのサポート

- 顧客がプログラム可能なルートキー、対称キー (256 ビット)、非対称キー (RSA-2K まで)、キー失効機能付き

- 暗号化ソフトウェア アクセラレータ - PKA、AES (最大 256 ビット)、SHA (最大 256 ビット)、TRNG/DRGB

- 機能安全準拠

- 機能安全アプリケーション向けに開発

- ASIL-D までの ISO 26262 機能安全システム設計に役立つ資料を入手可能

- ASIL-B までのハードウェア インテグリティ

- 安全関連の認証

- TUV SUD により ISO 26262 認証済み (ASIL B まで)

- AEC-Q100 認定済み

- パワー マネージメント

- 内蔵 LDO ネットワークにより PSRR の向上を実現

- I/O は 3.3V/1.8V のデュアル電圧に対応

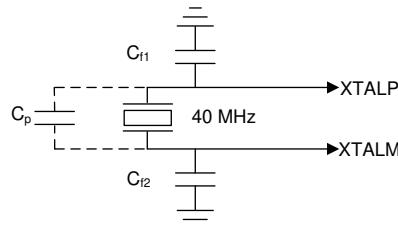

- クロック ソース

- 40.0MHz の水晶振動子と内部発振器

- 40MHz の外部発振器をサポート

- 40MHz の外部駆動クロック (方形波 / 正弦波) をサポート

- ハードウェア設計が簡単

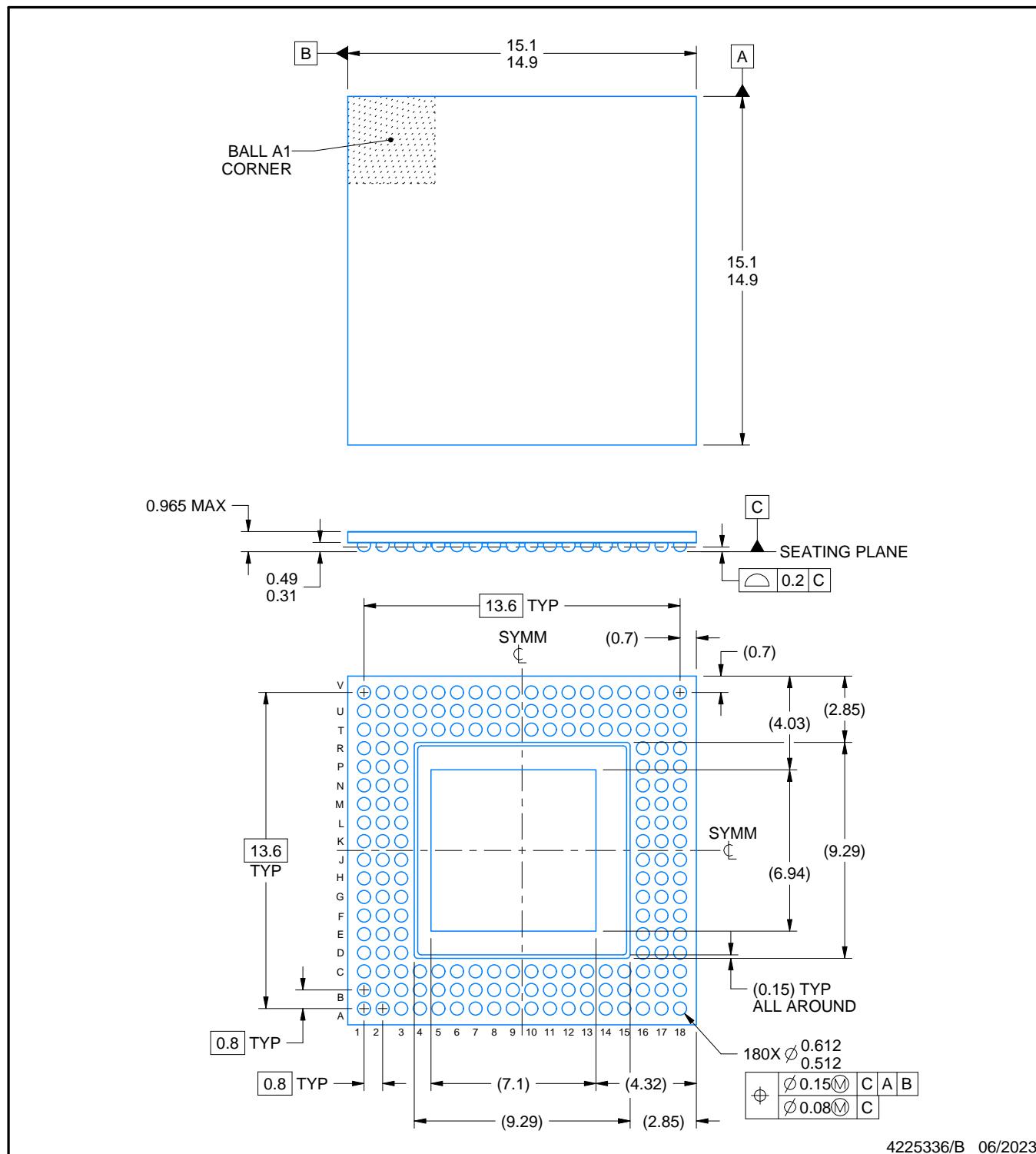

- 組み立てが簡単で低コストの PCB を設計できる 0.8mm ピッチ、180 ピン、15mm × 15mm のフリップ チップ BGA パッケージ (ALP)

- 小型ソリューション サイズ

- 動作条件:

- 接合部温度範囲: -40°C ~ 125°C

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 2 アプリケーション

- 車室内センシング

- 子供の存在検知

- 物体検出

- シートベルト警報

- ドライバーのバイタルサイン監視

- キックセンサ / アクセスセンサ

- 侵入者検出

- ジェスチャ制御の HMI

- ジェスチャ認識

## 3 説明

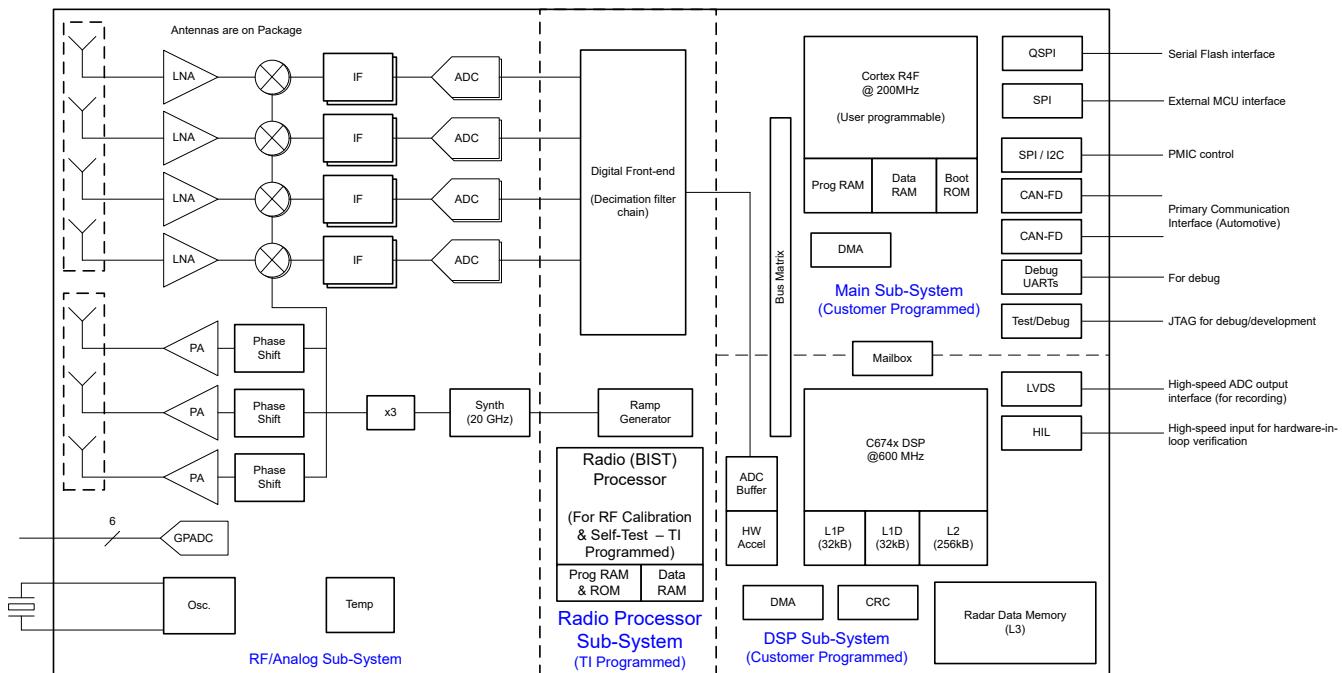

AWR6843AOP は、テキサス・インストルメンツ (TI) のシングルチップレーダー デバイス ファミリの先進のアンテナ搭載パッケージ (AOP) デバイスです。超小型フォーム ファクタで、これまでにないレベルの統合を実現しており、低消費電力で自己監視機能を備えた超高精度の車載用レーダー システムに最適なソリューションです。現在、機能安全準拠デバイス (ASIL-B) と機能安全非準拠デバイスを含む複数の車載認定済みバリエントを提供しています。

また、TI の高性能 C674x DSP を含む DSP サブシステムをレーダー信号処理のために統合しています。無線の構成、制御、較正用に BIST プロセッサ サブシステムも内蔵されています。さらに、このデバイスには車載用インターフェイスとして使用される Arm Cortex-R4F が搭載されており、ユーザーがプログラム可能です。ハードウェア アクセラレータ ブロック (HWA) はレーダー処理を実行でき、DSP がより高いレベルのアルゴリズムを実行できるように DSP の負荷を解放できます。プログラミング モデルを変更するだけで、さまざまなセンサに応用でき、マルチモード センサの実装においては動的再構成にも対応します。また本デバイスは、リファレンス ハードウェア デザイン、ソフトウェア ドライバ、構成例、API ガイド、ユーザー マニュアルを含む完全なプラットフォーム ソリューションとして提供しています。

### デバイス情報

| 部品番号              | パッケージ <sup>(1)</sup> | 本体サイズ <sup>(2)</sup> | トレイ / テープ アンド リール |

|-------------------|----------------------|----------------------|-------------------|

| AWR6843ARBGALPQ1  | FCBGA (180)          | 15mm × 15mm          | トレイ               |

| AWR6843ARBGALPRQ1 | FCBGA (180)          | 15mm × 15mm          | テープ アンド リール       |

| AWR6843ARBSALPQ1  | FCBGA (180)          | 15mm × 15mm          | トレイ               |

| AWR6843ARBSALPRQ1 | FCBGA (180)          | 15mm × 15mm          | テープ アンド リール       |

(1) 詳細については、[セクション 13、「メカニカル、パッケージ、および注文情報」](#)を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

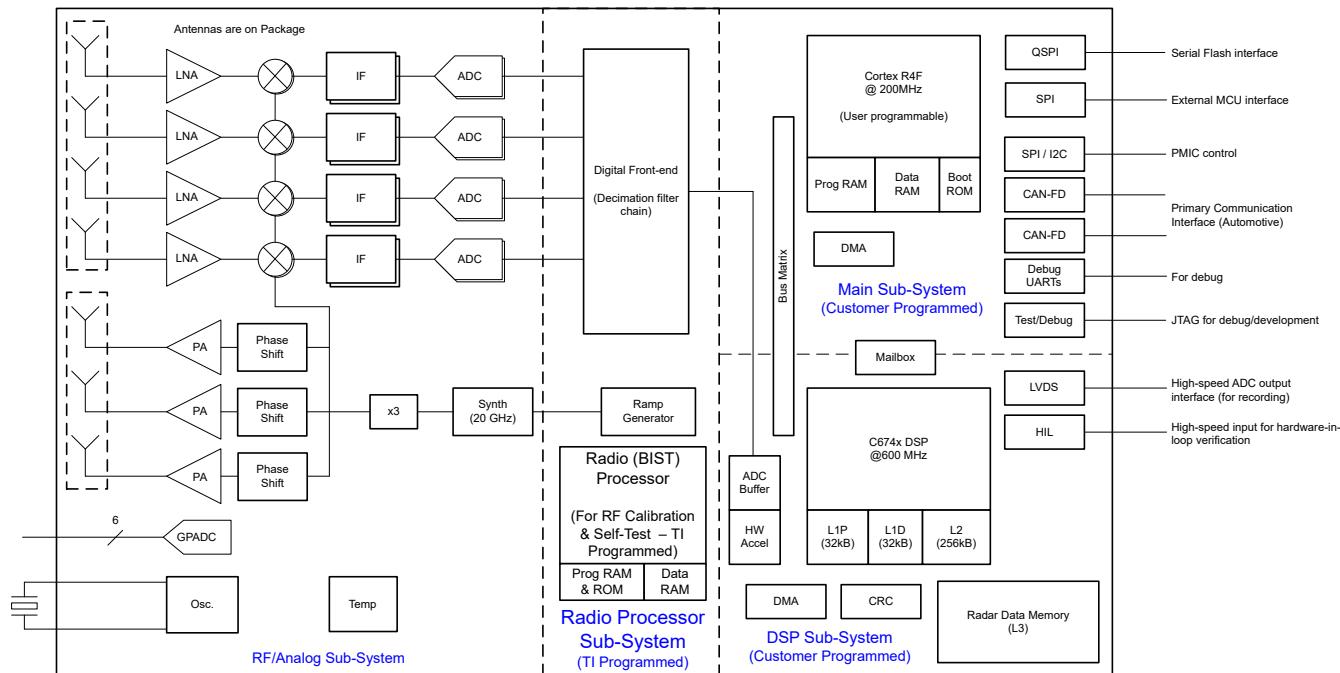

## 4 機能ブロック図

デバイスの機能ブロック図を図 4-1 に示します。

図 4-1. 機能ブロック図

## 目次

|                                       |    |                                    |    |

|---------------------------------------|----|------------------------------------|----|

| <b>1 特長</b>                           | 1  | <b>8 詳細説明</b>                      | 68 |

| <b>2 アプリケーション</b>                     | 2  | <b>8.1 概要</b>                      | 68 |

| <b>3 説明</b>                           | 2  | <b>8.2 機能ブロック図</b>                 | 68 |

| <b>4 機能ブロック図</b>                      | 3  | <b>8.3 サブシステム</b>                  | 69 |

| <b>5 デバイスの比較</b>                      | 5  | <b>8.4 その他のサブシステム</b>              | 73 |

| 5.1 関連製品                              | 7  | <b>8.5 ブートモード</b>                  | 74 |

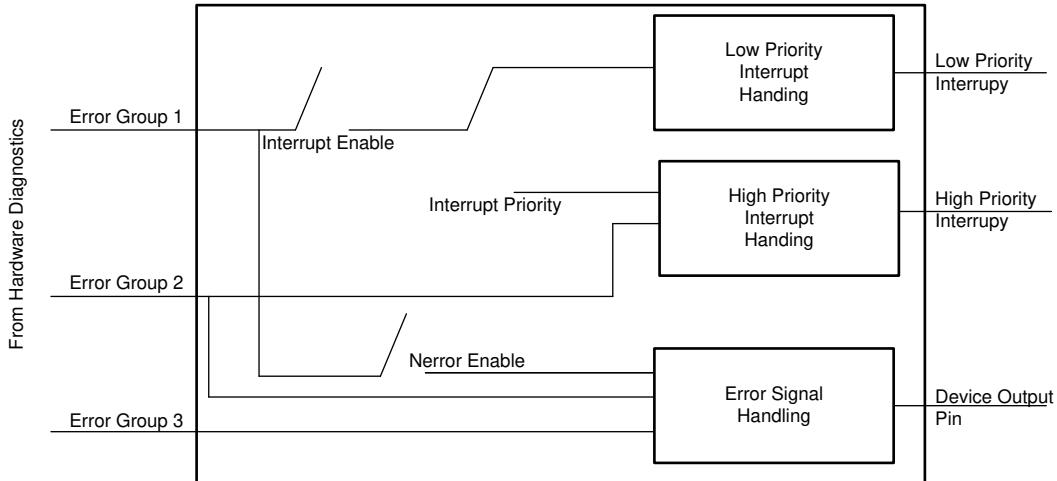

| <b>6 端子構成および機能</b>                    | 8  | <b>9 監視と診断</b>                     | 78 |

| 6.1 ピン配置図                             | 8  | <b>9.1 監視と診断のメカニズム</b>             | 78 |

| 6.2 信号の説明                             | 9  | <b>10 アプリケーション、実装、およびレイアウト</b>     | 83 |

| 6.3 ピン属性                              | 15 | <b>10.1 アプリケーション情報</b>             | 83 |

| <b>7 仕様</b>                           | 29 | <b>10.2 リファレンス回路図</b>              | 83 |

| 7.1 絶対最大定格                            | 29 | <b>11 デバイスおよびドキュメントのサポート</b>       | 84 |

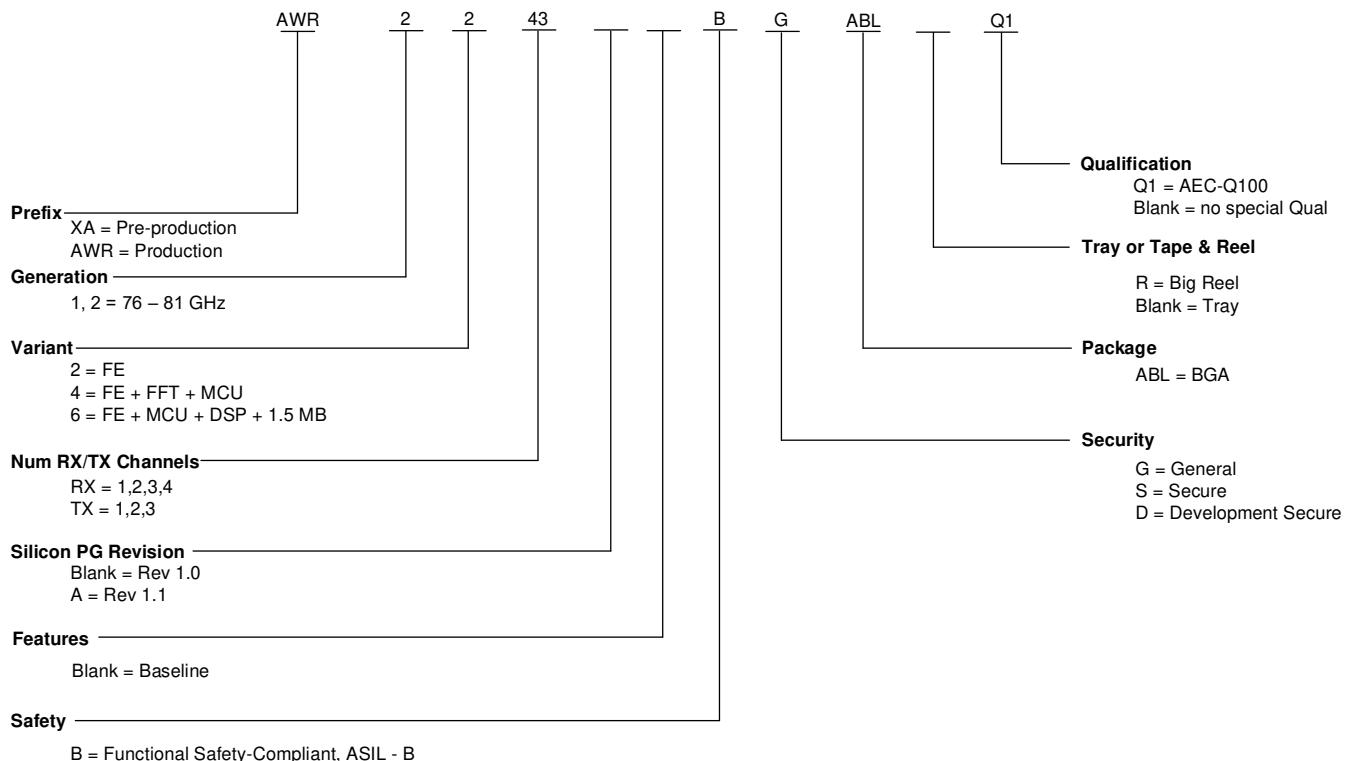

| 7.2 ESD 定格                            | 29 | <b>11.1 デバイスの命名規則</b>              | 84 |

| 7.3 電源投入時間 (POH)                      | 30 | <b>11.2 ツールとソフトウェア</b>             | 86 |

| 7.4 推奨動作条件                            | 31 | <b>11.3 ドキュメントのサポート</b>            | 86 |

| 7.5 ワンタイムプログラマブル (OTP) eFuse の VPP 仕様 | 32 | <b>11.4 サポート・リソース</b>              | 86 |

| 7.6 電源仕様                              | 32 | <b>11.5 商標</b>                     | 86 |

| 7.7 消費電力の概略                           | 33 | <b>11.6 静電気放電に関する注意事項</b>          | 86 |

| 7.8 パワー セーブ モード                       | 34 | <b>11.7 用語集</b>                    | 86 |

| 7.9 RF 仕様                             | 36 | <b>12 改訂履歴</b>                     | 87 |

| 7.10 CPU の仕様                          | 36 | <b>13 メカニカル、パッケージ、および注文情報</b>      | 89 |

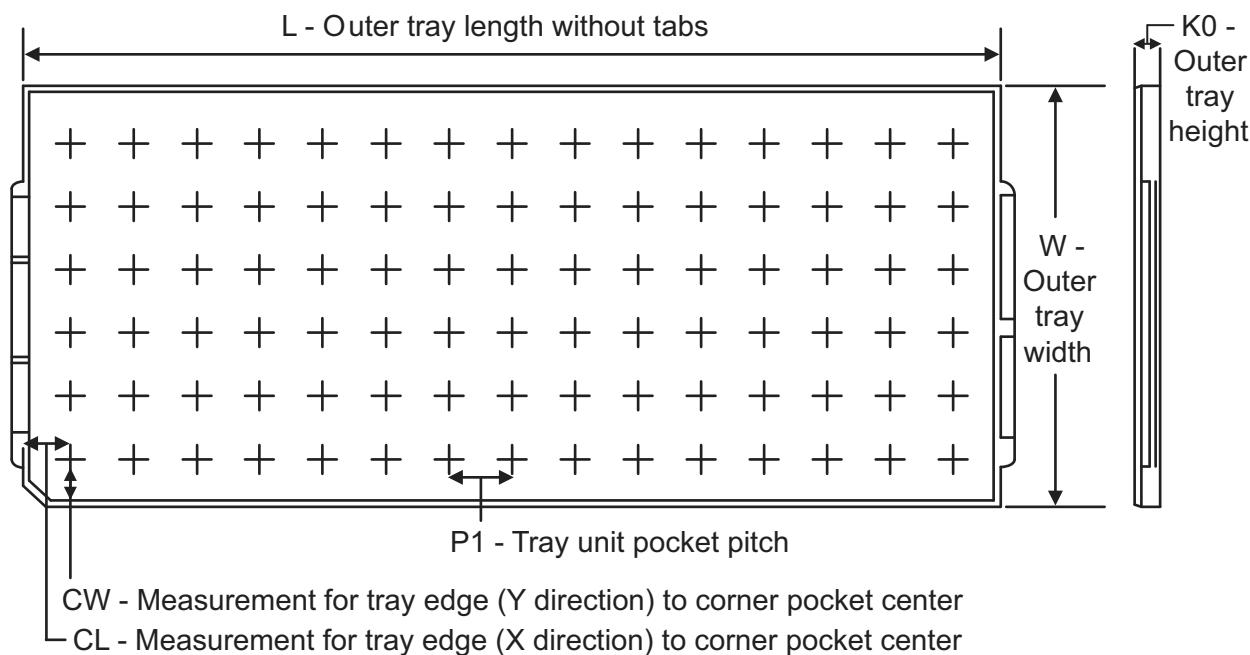

| 7.11 FCBGA パッケージの熱抵抗特性 [ALP0180A]     | 37 | <b>13.1 パッケージ情報</b>                | 89 |

| 7.12 タイミングおよびスイッチング特性                 | 38 | <b>13.2 ALP, 15 × 15 mm のトレイ情報</b> | 89 |

## 5 デバイスの比較

**表 5-1. デバイスの機能の比較**

| 機能                                           | AWR6843AOP <sup>(1)</sup> | AWR1843AOP       | AWR6843          | AWR6443          | AWR1843          | AWR1642  | AWR1443  | AWRL6432 | AWRL1432 |

|----------------------------------------------|---------------------------|------------------|------------------|------------------|------------------|----------|----------|----------|----------|

| アンテナオンパッケージ(AOP)                             | あり                        | あり               | —                | —                | —                | —        | —        | —        | —        |

| レシーバの数                                       | 4                         | 4                | 4                | 4                | 4                | 4        | 4        | 3        | 3        |

| トランシミッタの数                                    | 3 <sup>(2)</sup>          | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 2        | 3        | 2        | 2        |

| RF周波数範囲                                      | 60~64GHz                  | 76~81GHz         | 60~64GHz         | 60~64GHz         | 76~81GHz         | 76~81GHz | 76~81GHz | 57~64GHz | 57~64GHz |

| オンチップメモリ                                     | 1.75MB                    | 2MB              | 1.75MB           | 1.4MB            | 2MB              | 1.5MB    | 576KB    | 1MB      | 1MB      |

| 最大I/F(中間周波数)(MHz)                            | 10                        | 10               | 10               | 10               | 10               | 5        | 5        | 5        | 5        |

| 最大実数サンプリングレート(MspS)                          | 25                        | 25               | 25               | 25               | 25               | 12.5     | 12.5     | 12.5     | 12.5     |

| 最大複素サンプリングレート(MspS)                          | 12.5                      | 12.5             | 12.5             | 12.5             | 12.5             | 6.25     | 6.25     | —        | —        |

| デバイスのセキュリティ <sup>(3)</sup>                   | あり                        | あり               | あり               | —                | あり               | あり       | —        | —        | —        |

| プロセッサ                                        |                           |                  |                  |                  |                  |          |          |          |          |

| MCU                                          | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | あり       | あり       |

| DSP(C674x)                                   | あり                        | あり               | あり               | あり               | —                | あり       | あり       | —        | —        |

| ペリフェラル                                       |                           |                  |                  |                  |                  |          |          |          |          |

| シリアルペリフェラルインターフェイス(SPI)ポート                   | 2                         | 2                | 2                | 2                | 2                | 2        | 1        | 2        | 2        |

| クワッドシリアルペリフェラルインターフェイス(QSPI)                 | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | あり       | あり       |

| I <sup>2</sup> C(Integrated Circuit)インターフェイス | 1                         | 1                | 1                | 1                | 1                | 1        | 1        | 1        | 1        |

| コントローラエリアネットワーク(DCAN)インターフェイス                | —                         | 1                | —                | —                | 1                | 1        | 1        | —        | —        |

| コントローラエリアネットワーク(CAN-FD)インターフェイス              | 2                         | 1                | 2                | 2                | 1                | —        | —        | 1        | 1        |

| トレース                                         | あり                        | あり               | あり               | あり               | あり               | あり       | —        | —        | —        |

| PWM                                          | あり                        | あり               | あり               | あり               | あり               | あり       | —        | あり       | あり       |

| ハードウェアインループ(HIL/DMM)                         | あり                        | あり               | あり               | あり               | あり               | あり       | —        | —        | —        |

| GPADC                                        | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | あり       | あり       |

| LVDS / デバッグ <sup>(4)</sup>                   | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | —        | —        |

| CSI2                                         | —                         | —                | —                | —                | —                | —        | —        | —        | —        |

| ハードウェアアクセラレータ                                | あり                        | あり               | あり               | あり               | あり               | あり       | —        | あり       | あり       |

| 1Vバイパスモード                                    | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | 該当なし     | 該当なし     |

| JTAG                                         | あり                        | あり               | あり               | あり               | あり               | あり       | あり       | あり       | あり       |

表 5-1. デバイスの機能の比較 (続き)

| 機能       | AWR6843AOP (1)                    | AWR1843AOP | AWR6843 | AWR6443 | AWR1843 | AWR1642 | AWR1443 | AWRL6432 | AWRL1432 |

|----------|-----------------------------------|------------|---------|---------|---------|---------|---------|----------|----------|

| 製品のステータス | 製品プレビュー (PP)、事前情報 (AI)、量産データ (PD) | PD (5)     | PD (5)  | PD (5)  | PD (5)  | PD (5)  | PD (5)  | PD (5)   | PD (5)   |

- (1) 機能安全アプリケーション用に開発された本デバイスは、ASIL-Bまでのハードウェア安全度をサポートしています。詳細については、関連資料を参照してください。

- (2) 3 Tx 同時動作は、1V LDO バイパスおよび PA LDO 無効化モードのみでサポートしています。このモードでは、1V 電源を VOUT PA ピンに供給する必要があります。

- (3) セキュア ブートとカスタマー プログラマブル キーを含むデバイス セキュリティ機能は、「製品情報」表のセクション 3 のデバイス タイプ識別子で示された一部の製品バリアントでのみ利用できます。

- (4) LVDS インターフェイスは、製品インターフェイスではなく、デバッグ目的でのみ使用されます。

- (5) 量産データの情報は、公開日の時点での最新のものです。製品は、テキサス・インスツルメンツの標準保証条件に基づく仕様に準拠しています。量産開始前の製品の事前情報。予告なく変更される場合があります。

## 5.1 関連製品

この製品ファミリまたは関連製品の他のデバイスの詳細については、以下のリンクを参照してください。

### ミリ波センサ

テキサスインスツルメンツの車載最もフットプリントが小さい車載アプリケーション向けミリ波センサは、小さい電力で、距離、角度、速度を迅速かつ正確に検出します。

### 車載ミリ波センサ

テキサス・インスツルメンツの車載ミリ波センサ製品ラインアップは、超高分解能、小型、低消費電力のシングルチップ レーダー ソリューションに高性能レーダー フロント エンドを提供します。テキサス・インスツルメンツのスケーラブルなセンサ製品ラインアップは、すべての自動車の快適性機能から安全性機能に至るまで、あらゆる性能、アプリケーション、センサ構成に対応する ADAS システム ソリューションの設計と開発を可能にします。

### コンパニオン製品 (AWR6843)

この製品と組み合わせて購入または使用されることが多い製品を確認してください。

### リファレンス デザイン (AWR6843)

TI Designs リファレンス デザインライブラリは、アナログ、組み込みプロセッサ、コネクティビティの各分野にわたる堅牢なリファレンス デザイン ライブラリです。すべての TI Designs は、システム設計を迅速に開始できるようにテキサス・インスツルメンツの専門家により作成されたもので、回路図またはブロック図、BOM、設計ファイルが含まれており、製品の開発期間短縮に役立ちます。[ti.com/tidesigns](http://ti.com/tidesigns) でリファレンス デザインを検索、ダウンロードしてください。

### 車両乗員検出のリファレンス デザイン

このリファレンス デザインは、AWR6843 の使用方法を示します。この製品は、DSP を搭載した 60GHz シングルチップ ミリ波センサであり、車両の乗員検出 (VOD) や子供の占有検出 (CPD) センサとして使用すると、車両内の乗員や生体を検出できます。このデザインは、C674x DSP 上で動作するリファレンス ソフトウェアの処理チェーンを実現し、ヒート マップを生成して、±60 度の視野角 (FOV) で乗員を検出できるようにします。

## 6 端子構成および機能

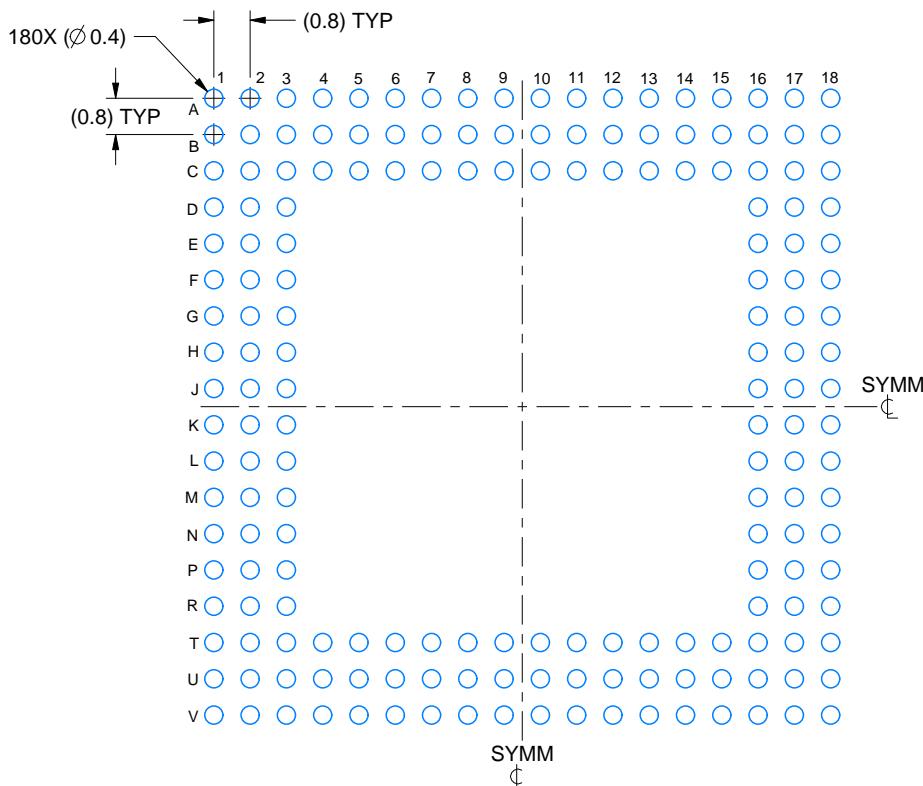

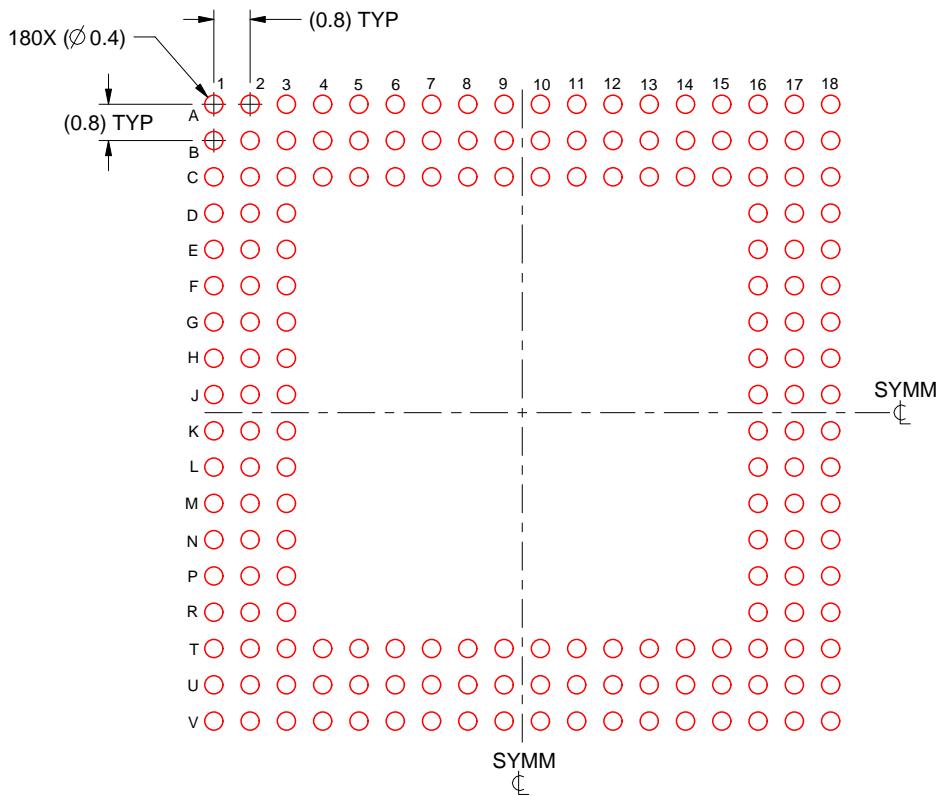

### 6.1 ピン配置図

図 6-1 は、180 ピン 15 × 15 mm FCBGA パッケージと

|   | 18         | 17         | 16         | 15         | 14          | 13          | 12         | 11           | 10            | 9       | 8     | 7     | 6         | 5    | 4           | 3            | 2             | 1            |           |

|---|------------|------------|------------|------------|-------------|-------------|------------|--------------|---------------|---------|-------|-------|-----------|------|-------------|--------------|---------------|--------------|-----------|

| V | VSSA       | VSSA       | RS232C_RX  | VDDIN      | VNW_A       | MCU_CL_KOUT | VIN_SRA_M  | VIOIN_18     | PMIC_CL_KOUT  | VIOIN   | VDDIN | VNW_A | VIN_SRA_M | DP2  | VDDIN       | DP4          | VPP           | VSS          | V         |

| U | VSSA       | VSSA       | RS232C_TX  | NERROR_OUT | NERROR_IN   | WARM_RESET  | SYNC_IN    | NRESET       | TDO           | TDI     | TMS   | DP0   | DP1       | DP3  | DMMLSYNC    | DMMCL_K      | VIOIN_18_DIFF | VSS          | U         |

| T | GPADC_4    | VSSA       | VSS        | VSS        | VSS         | VSS         | VSS        | VSS          | VSS           | VSS     | VSS   | VSS   | VSS       | VSS  | TCK         | LVDS_F_RCLKM | LVDS_F_RCLKP  | T            |           |

| R | GPADC_3    | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      |             | VSS          | LVDS_C_LKM    | LVDS_C_LKP   | R         |

| P | GPADC_1    | GPADC_2    | VSSA       |            |             |             |            |              |               |         |       |       |           |      |             | VSS          | LVDS_T_XP[1]  | LVDS_T_XM[1] | P         |

| N | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      |             | VSS          | LVDS_T_XP[0]  | LVDS_T_XM[0] | N         |

| M | VIN_18B_B  | VIN_18B_B  | VIN_18B_B  |            |             |             |            |              |               |         |       |       |           |      | SYNC_OUTPUT | GPIO_0       | DP5           |              | M         |

| L | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      | GPIO_1      | DP6          | DP7           |              | L         |

| K | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      | GPIO_2      | QSPI[3]      | VIOIN_18      |              | K         |

| J | VIN_13R_F1 | VIN_13R_F1 | VIN_13R_F1 |            |             |             |            |              |               |         |       |       |           |      | QSPI[2]     | QSPILCS_N    | VDDIN         |              | J         |

| H | VIN_13R_F2 | VIN_13R_F2 | VIN_13R_F2 |            |             |             |            |              |               |         |       |       |           |      | QSPI[0]     | QSPILCLK     | VIOIN         |              | H         |

| G | VOUT_P_A   | VOUT_P_A   | VOUT_P_A   |            |             |             |            |              |               |         |       |       |           |      | SPIB_MISO   | QSPI[1]      | SPIB_MOSI     |              | G         |

| F | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      | VSS         | SPIA_MOSI    | VIOIN_18      |              | F         |

| E | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      | VSS         | SPIB_CLK     | VDDIN         |              | E         |

| D | VSSA       | VSSA       | VSSA       |            |             |             |            |              |               |         |       |       |           |      | SPIB_CS_N   | SPIA_CLK     | SPIA_MISO     |              | D         |

| C | VIN_18C_LK | VSSA       | VSSA       | VIN_18C_LK | VSSA        | VSSA        | VSSA       | VIN_18V_CD   | GPADC_6       | GPADC_5 | VSSA  | VSSA  | VSSA      | DP14 | DP10        | DP8          | SPIA_CS_N     | VNW_A        | C         |

| B | VSSA       | VSSA       | VSSA       | VSSA       | VSSA        | VSSA        | VSSA       | VSSA         | VSSA          | VSSA    | VSSA  | VSSA  | VSSA      | CLKM | VSSA        | DP15         | DP12          | DP9          | SPIA_CS_N |

| A | VSSA       | VSSA       | VBGAP      | VSSA       | DSC_CL_KOUT | VSSA        | VIN_18V_CD | VOUT_1_4APLL | VOUT_1_4SYNTH | VSSA    | CLKP  | VSSA  | VIN_SRA_M | DP13 | DP11        | VSS          | VSS           | VIOIN_18     | A         |

図 6-1. ピン配置図 (上面図)

## 6.2 信号の説明

---

### 注

本デバイスのすべての IO ピン (NERROR\_IN、NERROR\_OUT、WARM\_RESET を除く) はフェイルセーフではないので、VIO 電源が本デバイスに供給されていない状態において、これらの IO ピンが外部から駆動されないように注意する必要があります。

---

### 注

電源ランプ時の GPIO 状態は保証されません。GPIO の状態が重要なアプリケーションで GPIO を使用する場合には、NRESET が Low であるときにも、トライステートバッファを使用して GPIO 出力をレーダー デバイスから分離し、プル抵抗を使って、アプリケーションで必要な状態を確定する必要があります。レーダー デバイスへの NRESET 信号は、トライステートバッファの出力イネーブル (OE) を制御するために使用できます。

### 6.2.1 ピンの機能 - デジタルおよびアナログ [ALP パッケージ]

| 名称          | I/O | 説明                                                                 | 番号                         |

|-------------|-----|--------------------------------------------------------------------|----------------------------|

| デジタル        |     |                                                                    |                            |

| BSS_UART_TX | O   | デバッグ UART 送信 [レーダー ブロック]                                           | D3、E2、K3、L2、U8、U10、U16、V16 |

| CAN1_FD_RX  | I   | CAN1 FD (MCAN) 受信信号                                                | A4、B3、E2、F2、K2、U8、V16      |

| CAN1_FD_TX  | O   | CAN1 FD (MCAN) 送信信号                                                | C2、C3、D1、D3、J3、T3、U16      |

| CAN2_FD_RX  | I   | CAN2 FD (MCAN) 受信信号                                                | D2                         |

| CAN2_FD_TX  | O   | CAN2 FD (MCAN) 送信信号                                                | B4                         |

| DMM0        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | U7                         |

| DMM1        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | U6                         |

| DMM2        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | V5                         |

| DMM3        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | U5                         |

| DMM4        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | V3                         |

| DMM5        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | M1                         |

| DMM6        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | L2                         |

| DMM7        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | L1                         |

| DMM8        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | C3                         |

| DMM9        | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | B3                         |

| DMM10       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | C4                         |

| DMM11       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | A3                         |

| DMM12       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | B4                         |

| DMM13       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | A4                         |

| DMM14       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | C5                         |

| DMM15       | I   | デバッグ インターフェイス (ハードウェア イン ループ) - データライン                             | B5                         |

| DMM_CLK     | I   | デバッグ インターフェイス (ハードウェア イン ループ) - クロック                               | U3                         |

| DMM_MUX_IN  | I   | デバッグ インターフェイス (ハードウェア イン ループ) DMM1 と DMM2 の間でのマルチプレクサ選択 (2 インスタンス) | L3、M3、U12                  |

| DMM_SYNC    | I   | デバッグ インターフェイス (ハードウェア イン ループ) - 同期                                 | U4                         |

| DSS_UART_TX | O   | デバッグ UART 送信 [DSP]                                                 | D2、F2、G3、H2、L1             |

| 名称         | I/O | 説明                 | 番号                |

|------------|-----|--------------------|-------------------|

| EPWM1A     | O   | PWM モジュール 1 - 出力 A | B4、U16、V13        |

| EPWM1B     | O   | PWM モジュール 1 - 出力 B | A4、M2、U16、V10     |

| EPWM1SYNCI | I   | PWM モジュール 1 - 同期入力 | C3、L3             |

| EPWM1SYNCO | I   | PWM モジュール 1 - 同期出力 | B3                |

| EPWM2A     | O   | PWM モジュール 2 - 出力 A | C5、M2、U16、V10、V16 |

| EPWM2B     | O   | PWM モジュール 2 - 出力 B | B5、V16            |

| EPWM2SYNCO | O   | PWM モジュール 2 - 同期出力 | V3                |

| EPWM3A     | O   | PWM モジュール 3 - 出力 A | C4、V16            |

| EPWM3B     | O   | PWM モジュール 3 - 出力 A | A3                |

| EPWM3SYNCO | O   | PWM モジュール 3 - 同期出力 | U5                |

| GPIO_0     | IO  | 汎用 I/O             | M2                |

| GPIO_1     | IO  | 汎用 I/O             | L3                |

| GPIO_2     | IO  | 汎用 I/O             | K3                |

| GPIO_3     | IO  | 汎用 I/O             | D2                |

| GPIO_4     | IO  | 汎用 I/O             | D3                |

| GPIO_5     | IO  | 汎用 I/O             | E2                |

| GPIO_6     | IO  | 汎用 I/O             | J2                |

| GPIO_7     | IO  | 汎用 I/O             | H2                |

| GPIO_8     | IO  | 汎用 I/O             | H3                |

| GPIO_9     | IO  | 汎用 I/O             | G2                |

| GPIO_10    | IO  | 汎用 I/O             | J3                |

| GPIO_11    | IO  | 汎用 I/O             | K2                |

| GPIO_12    | IO  | 汎用 I/O             | B2                |

| GPIO_13    | IO  | 汎用 I/O             | M2                |

| GPIO_14    | IO  | 汎用 I/O             | U16               |

| GPIO_15    | IO  | 汎用 I/O             | V16               |

| GPIO_16    | IO  | 汎用 I/O             | L3                |

| GPIO_17    | IO  | 汎用 I/O             | T3                |

| GPIO_18    | IO  | 汎用 I/O             | U8                |

| GPIO_19    | IO  | 汎用 I/O             | F2                |

| GPIO_20    | IO  | 汎用 I/O             | D1                |

| GPIO_21    | IO  | 汎用 I/O             | G1                |

| GPIO_22    | IO  | 汎用 I/O             | G3                |

| GPIO_23    | IO  | 汎用 I/O             | U9                |

| GPIO_24    | IO  | 汎用 I/O             | U10               |

| GPIO_25    | IO  | 汎用 I/O             | V13               |

| GPIO_26    | IO  | 汎用 I/O             | K3                |

| GPIO_27    | IO  | 汎用 I/O             | V10               |

| GPIO_28    | IO  | 汎用 I/O             | U12               |

| GPIO_29    | IO  | 汎用 I/O             | M3                |

| GPIO_30    | IO  | 汎用 I/O             | C2、D2             |

| GPIO_31    | IO  | 汎用 I/O             | U7                |

| GPIO_32    | IO  | 汎用 I/O             | U6                |

| 名称           | I/O | 説明                                                                                               | 番号                     |

|--------------|-----|--------------------------------------------------------------------------------------------------|------------------------|

| GPIO_33      | IO  | 汎用 I/O                                                                                           | V5                     |

| GPIO_34      | IO  | 汎用 I/O                                                                                           | U5                     |

| GPIO_35      | IO  | 汎用 I/O                                                                                           | V3                     |

| GPIO_36      | IO  | 汎用 I/O                                                                                           | M1                     |

| GPIO_37      | IO  | 汎用 I/O                                                                                           | L2                     |

| GPIO_38      | IO  | 汎用 I/O                                                                                           | L1                     |

| GPIO_39      | IO  | 汎用 I/O                                                                                           | C3                     |

| GPIO_40      | IO  | 汎用 I/O                                                                                           | B3                     |

| GPIO_41      | IO  | 汎用 I/O                                                                                           | C4                     |

| GPIO_42      | IO  | 汎用 I/O                                                                                           | A3                     |

| GPIO_43      | IO  | 汎用 I/O                                                                                           | B4                     |

| GPIO_44      | IO  | 汎用 I/O                                                                                           | A4                     |

| GPIO_45      | IO  | 汎用 I/O                                                                                           | C5                     |

| GPIO_46      | IO  | 汎用 I/O                                                                                           | B5                     |

| GPIO_47      | IO  | 汎用 I/O                                                                                           | U3                     |

| I2C_SCL      | IO  | I2C クロック                                                                                         | G3、V16                 |

| I2C_SDA      | IO  | I2C データ                                                                                          | G1、U16                 |

| LVDS_TXP[0]  | O   | 差動データ出力 - レーン 0                                                                                  | N2                     |

| LVDS_TXM[0]  | O   | 差動データ出力 - レーン 0                                                                                  | N1                     |

| LVDS_TXP[1]  | O   | 差動データ出力 - レーン 1                                                                                  | P2                     |

| LVDS_TXM[1]  | O   | 差動データ出力 - レーン 1                                                                                  | P1                     |

| LVDS_CLKP    | O   | 差動クロック出力                                                                                         | R1                     |

| LVDS_CLKM    | O   | 差動クロック出力                                                                                         | R2                     |

| LVDS_FRCLKP  | O   | 差動フレーム クロック                                                                                      | T1                     |

| LVDS_FRCLKM  | O   | 差動フレーム クロック                                                                                      | T2                     |

| MCU_CLKOUT   | O   | 外部 MCU またはプロセッサに供給されるプログラマブル クロック                                                                | V13                    |

| MSS_UARTA_RX | I   | メイン サブシステム - UART A 受信                                                                           | E2、U9、V16              |

| MSS_UARTA_TX | O   | メイン サブシステム - UART A 送信                                                                           | D3、U7、U10、U16          |

| MSS_UARTB_RX | IO  | メイン サブシステム - UART B 受信                                                                           | U12、V16                |

| MSS_UARTB_TX | O   | メイン サブシステム - UART B 送信                                                                           | D3、E2、K3、M1、T3、U10、U16 |

| NDMM_EN      | I   | デバッグ インターフェイス (ハードウェア イン ループ) イネーブル - アクティブ Low 信号                                               | U10、U16                |

| NERROR_IN    | I   | デバイスへのフェイルセーフ入力。他のデバイスからの NERROR 出力は、デバイス内のエラー信号モニタ モジュールに集約させることができ、ファームウェアによって適切なアクションを実行できます。 | U14                    |

| NERROR_OUT   | O   | オープンドレインのフェイルセーフ出力信号。非常に重大なフォルトが発生していることを示すために、PMIC / プロセッサ / MCU に接続されています。復帰にはリセットが必要です。       | U15                    |

| PMIC_CLKOUT  | O   | PMIC 用 AWR6843AOP デバイスからの出力クロック                                                                  | K3、M2、V10              |

| QSPI[0]      | IO  | QSPI データライン #0 (シリアル データ フラッシュと使用)                                                               | H3                     |

| QSPI[1]      | I   | QSPI データライン #1 (シリアル データ フラッシュと使用)                                                               | G2                     |

| QSPI[2]      | I   | QSPI データライン #2 (シリアル データ フラッシュと使用)                                                               | J3                     |

| QSPI[3]      | I   | QSPI データライン #3 (シリアル データ フラッシュと使用)                                                               | K2                     |

| QSPI_CLK     | O   | QSPI クロック (シリアル データ フラッシュと使用)                                                                    | H2                     |

| 名称            | I/O | 説明                                | 番号              |

|---------------|-----|-----------------------------------|-----------------|

| QSPI_CLK_EXT  | I   | QSPI クロック (シリアル データ フラッシュと使用)     | D3              |

| QSPI_CS_N     | O   | QSPI チップ セレクト (シリアル データ フラッシュと使用) | J2              |

| RS232_RX      | I   | デバッグ UART (バス マスタとして動作) - 受信信号    | V16             |

| RS232_TX      | O   | デバッグ UART (バス マスタとして動作) - 送信信号    | U16             |

| SOP[0]        | I   | センス オン パワー - ライン #0               | U10             |

| SOP[1]        | I   | センス オン パワー - ライン #1               | M3              |

| SOP[2]        | I   | センス オン パワー - ライン #2               | V10             |

| SPIA_CLK      | IO  | SPI チャネル A - クロック                 | D2              |

| SPIA_CS_N     | IO  | SPI チャネル A - チップ セレクト             | C2              |

| SPIA_MISO     | IO  | SPI チャネル A - マスタ入力 / スレーブ出力       | D1              |

| SPIA_MOSI     | IO  | SPI チャネル A - マスタ出力 / スレーブ入力       | F2              |

| SPIB_CLK      | IO  | SPI チャネル B - クロック                 | E2, H2          |

| SPIB_CS_N     | IO  | SPI チャネル B チップ セレクト (インスタンス ID 0) | D3, J2          |

| SPIB_CS_N_1   | IO  | SPI チャネル B チップ セレクト (インスタンス ID 1) | B2, L3, M3      |

| SPIB_CS_N_2   | IO  | SPI チャネル B チップ セレクト (インスタンス ID 2) | G2, L3, M3      |

| SPIB_MISO     | IO  | SPI チャネル B - マスタ入力 / スレーブ出力       | G3, H3          |

| SPIB_MOSI     | IO  | SPI チャネル B - マスタ出力 / スレーブ入力       | G1, G2          |

| SPI_HOST_INTR | O   | SPI 経由で通信中の外部ホストへの帯域外割り込み         | B2              |

| SYNC_IN       | I   | 低周波数同期信号入力                        | U12             |

| SYNC_OUT      | O   | 低周波数同期信号出力                        | K3, L3, M3, U12 |

| TCK           | I   | JTAG テスト クロック                     | T3              |

| TDI           | I   | JTAG テスト データ入力                    | U9              |

| TDO           | O   | JTAG テスト データ出力                    | U10             |

| TMS           | I   | JTAG テスト モード信号                    | U8              |

| TRACE_CLK     | O   | デバッグ トレース出力 - クロック                | U3              |

| TRACE_CTL     | O   | デバッグ トレース出力 - 制御                  | U4              |

| TRACE_DATA_0  | O   | デバッグ トレース出力 - データ ライン             | U7              |

| TRACE_DATA_1  | O   | デバッグ トレース出力 - データ ライン             | U6              |

| TRACE_DATA_2  | O   | デバッグ トレース出力 - データ ライン             | V5              |

| TRACE_DATA_3  | O   | デバッグ トレース出力 - データ ライン             | U5              |

| TRACE_DATA_4  | O   | デバッグ トレース出力 - データ ライン             | V3              |

| TRACE_DATA_5  | O   | デバッグ トレース出力 - データ ライン             | M1              |

| TRACE_DATA_6  | O   | デバッグ トレース出力 - データ ライン             | L2              |

| TRACE_DATA_7  | O   | デバッグ トレース出力 - データ ライン             | L1              |

| TRACE_DATA_8  | O   | デバッグ トレース出力 - データ ライン             | C3              |

| TRACE_DATA_9  | O   | デバッグ トレース出力 - データ ライン             | B3              |

| TRACE_DATA_10 | O   | デバッグ トレース出力 - データ ライン             | C4              |

| TRACE_DATA_11 | O   | デバッグ トレース出力 - データ ライン             | A3              |

| TRACE_DATA_12 | O   | デバッグ トレース出力 - データ ライン             | B4              |

| TRACE_DATA_13 | O   | デバッグ トレース出力 - データ ライン             | A4              |

| TRACE_DATA_14 | O   | デバッグ トレース出力 - データ ライン             | C5              |

| TRACE_DATA_15 | O   | デバッグ トレース出力 - データ ライン             | B5              |

| FRAME_START   | O   | 各フレームの開始を示すパルス信号                  | K3, V10, V13    |

| 名称                | I/O  | 説明                                                                                      | 番号                                                                                                                                                                                                          |

|-------------------|------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIRP_START       | O    | 各チャーブの開始を示すパルス信号                                                                        | K3、V10、V13                                                                                                                                                                                                  |

| CHIRP_END         | O    | 各チャーブの終了を示すパルス信号                                                                        | K3、V10、V13                                                                                                                                                                                                  |

| ADC_VALID         | O    | High のとき、有効な ADC サンプルを示します                                                              | B2、L3、M2                                                                                                                                                                                                    |

| WARM_RESET        | IO   | オープンドレインのフェイルセーフ ウォームリセット信号。診断用として PMIC から駆動するか、または、デバイスがリセット中であることを示すステータス信号として使用できます。 | U13                                                                                                                                                                                                         |

| <b>アナログ</b>       |      |                                                                                         |                                                                                                                                                                                                             |

| NRESET            | I    | チップのパワーON リセット。アクティブ Low                                                                | U11                                                                                                                                                                                                         |

| CLKP              | I    | XTAL モード: 外部クロック モードのリファレンス水晶振動子用差動ポート: シングルエンド入力リファレンス クロック ポート                        | A7                                                                                                                                                                                                          |

| CLKM              | I    | XTAL モード: 外部クロック モードのリファレンス水晶振動子用差動ポート: このポートはグランドに接続します。                               | B7                                                                                                                                                                                                          |

| OSC_CLKOUT        | O    | PLL のクリーンアップ後に、クロック サブシステムから出力されるリファレンス クロック (1.4V 出力電圧スイング)。                           | A14、K3                                                                                                                                                                                                      |

| VBGAP             | O    | デバイスのバンドギャップ リファレンス出力                                                                   | A16                                                                                                                                                                                                         |

| VDDIN             | 電源   | 1.2V デジタル電源                                                                             | E1、J1、V4、V8、V15                                                                                                                                                                                             |

| VIN_SRAM          | 電源   | 内部 SRAM 用 1.2V 電源レール                                                                    | A5、V6、V12                                                                                                                                                                                                   |

| VNWA              | 電源   | SRAM アレイのバック バイアス用 1.2V 電源レール                                                           | C1、V7、V14                                                                                                                                                                                                   |

| VIOIN             | 電源   | I/O 電源 (3.3V または 1.8V): すべての CMOS I/O はこの電源で動作します。                                      | H1、V9                                                                                                                                                                                                       |

| VIOIN_18          | 電源   | CMOS IO 用 1.8V 電源                                                                       | B1、F1、K1、V11                                                                                                                                                                                                |

| VIN_18CLK         | 電源   | クロック モジュール用 1.8V 電源                                                                     | C15、C18                                                                                                                                                                                                     |

| VIOIN_18DIFF      | 電源   | LVDS ポート用 1.8V 電源                                                                       | U2                                                                                                                                                                                                          |

| VPP               | 電源   | ヒューズ チェーン用電源電圧                                                                          | V2                                                                                                                                                                                                          |

| VIN_13RF1         | 電源   | 1.3V アナログおよび RF 電源、VIN_13RF1 と VIN_13RF2 が基板上で短絡されている可能性があります。                          | J16、J17、J18                                                                                                                                                                                                 |

| VIN_13RF2         | 電源   | 1.3V アナログおよび RF 電源                                                                      | H16、H17、H18                                                                                                                                                                                                 |

| VIN_18BB          | 電源   | 1.8V アナログ ベース バンド電源                                                                     | M16、M17、M18                                                                                                                                                                                                 |

| VIN_18VCO         | 電源   | 1.8V RF VCO 電源                                                                          | A12、C11                                                                                                                                                                                                     |

| VSS               | グランド | デジタル グランド                                                                               | A1、A2、E3、F3、N3、P3、R3、T4、T5、T6、T7、T8、T9、T10、T11、T12、T13、T14、T15、T16、U1、V1                                                                                                                                    |

| VSSA              | グランド | アナログ グランド                                                                               | A6、A8、A11、A13、A15、A17、A18、B6、B8、B9、B10、B11、B12、B13、B14、B15、B16、B17、B18、C6、C7、C8、C12、C13、C14、C16、C17、D16、D17、D18、E16、E17、E18、F16、F17、F18、K16、K17、K18、L16、L17、L18、N16、N17、N18、P16、R16、R17、T17、U17、U18、V17、V18 |

| VOUT_14APLL       | O    | 内部 LDO 出力                                                                               | A10                                                                                                                                                                                                         |

| VOUT_14SYNTH      | O    | 内部 LDO 出力                                                                               | A9                                                                                                                                                                                                          |

| VOUT_PA           | IO   | 内部 LDO 出力                                                                               | G16、G17、G18                                                                                                                                                                                                 |

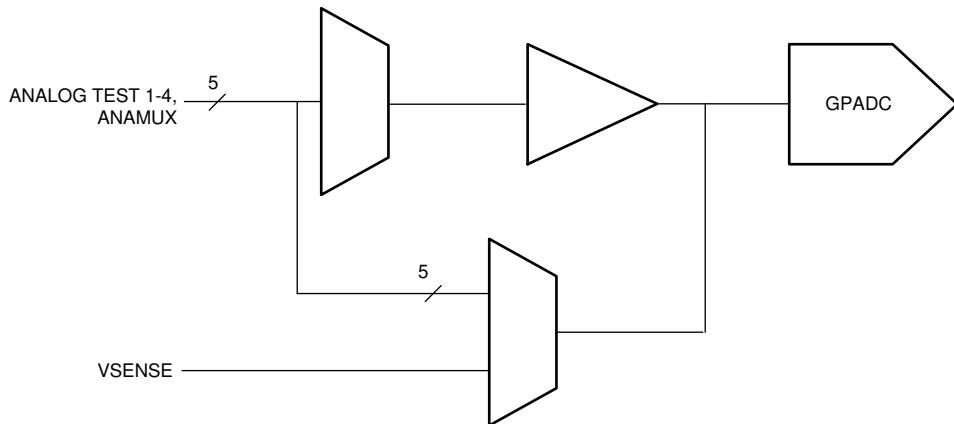

| アナログ テスト 1/GPADC1 | IO   | ADC サービス専用のアナログ IO                                                                      | P18                                                                                                                                                                                                         |

| 名称                | I/O | 説明                 | 番号  |

|-------------------|-----|--------------------|-----|

| アナログ テスト 2/GPADC2 | IO  | ADC サービス専用のアナログ IO | P17 |

| アナログ テスト 3/GPADC3 | IO  | ADC サービス専用のアナログ IO | R18 |

| アナログ テスト 4/GPADC4 | IO  | ADC サービス専用のアナログ IO | T18 |

| ANAMUX/GPADC5     | IO  | ADC サービス専用のアナログ IO | C9  |

| VSENSE/GPADC6     | IO  | ADC サービス専用のアナログ IO | C10 |

## 6.3 ピン属性

**表 6-1. ピン属性 (ALP180A パッケージ)**

| ポール番号 [1] | ポール名 [2]      | 信号名 [3]      | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7] | プルアップ / ダウン タイプ [8] |

|-----------|---------------|--------------|------------------|-------------|---------|---------------|---------------------|

| M2        | GPIO_0        | GPIO_13      | 0xFFFFEA04       | 0           | IO      | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_0       |                  | 1           | IO      |               |                     |

|           |               | PMIC_CLKOUT  |                  | 2           | O       |               |                     |

|           |               | EPWM1B       |                  | 10          | O       |               |                     |

|           |               | ePWM2A       |                  | 11          | O       |               |                     |

| L3        | GPIO_1        | GPIO_16      | 0xFFFFEA08       | 0           | IO      | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_1       |                  | 1           | IO      |               |                     |

|           |               | SYNC_OUT     |                  | 2           | O       |               |                     |

|           |               | DMM_MUX_IN   |                  | 12          | I       |               |                     |

|           |               | SPIB_CS_N_1  |                  | 13          | IO      |               |                     |

|           |               | SPIB_CS_N_2  |                  | 14          | IO      |               |                     |

|           |               | EPWM1SYNCI   |                  | 15          | I       |               |                     |

| K3        | GPIO_2        | GPIO_26      | 0xFFFFEA64       | 0           | IO      | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_2       |                  | 1           | IO      |               |                     |

|           |               | OSC_CLKOUT   |                  | 2           | O       |               |                     |

|           |               | MSS_UARTB_TX |                  | 7           | O       |               |                     |

|           |               | BSS_UART_TX  |                  | 8           | O       |               |                     |

|           |               | SYNC_OUT     |                  | 9           | O       |               |                     |

|           |               | PMIC_CLKOUT  |                  | 10          | O       |               |                     |

|           |               | CHIRP_START  |                  | 11          | O       |               |                     |

|           |               | CHIRP_END    |                  | 12          | O       |               |                     |

|           |               | FRAME_START  |                  | 13          | O       |               |                     |

|           |               | TRACE_DATA_0 | 0xFFFFEA7C       | 0           | O       | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_31      |                  | 1           | IO      |               |                     |

|           |               | DMM0         |                  | 2           | I       |               |                     |

|           |               | MSS_UARTA_TX |                  | 4           | IO      |               |                     |

| U6        | GPIO_32 (DP1) | TRACE_DATA_1 | 0xFFFFEA80       | 0           | O       | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_32      |                  | 1           | IO      |               |                     |

|           |               | DMM1         |                  | 2           | I       |               |                     |

| V5        | GPIO_33 (DP2) | TRACE_DATA_2 | 0xFFFFEA84       | 0           | O       | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_33      |                  | 1           | IO      |               |                     |

|           |               | DMM2         |                  | 2           | I       |               |                     |

| U5        | GPIO_34 (DP3) | TRACE_DATA_3 | 0xFFFFEA88       | 0           | O       | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_34      |                  | 1           | IO      |               |                     |

|           |               | DMM3         |                  | 2           | I       |               |                     |

|           |               | EPWM3SYNCO   |                  | 4           | O       |               |                     |

表 6-1. ピン属性 (ALP180A パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]       | 信号名 [3]       | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7] | プルアップ / ダウン タイプ [8] |

|-----------|----------------|---------------|------------------|-------------|---------|---------------|---------------------|

| V3        | GPIO_35 (DP4)  | TRACE_DATA_4  | 0xFFFFEA8C       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_35       |                  | 1           | IO      |               |                     |

|           |                | DMM4          |                  | 2           | I       |               |                     |

|           |                | EPWM2SYNCO    |                  | 4           | O       |               |                     |

| M1        | GPIO_36 (DP5)  | TRACE_DATA_5  | 0xFFFFEA90       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_36       |                  | 1           | IO      |               |                     |

|           |                | DMM5          |                  | 2           | I       |               |                     |

|           |                | MSS_UARTB_TX  |                  | 5           | O       |               |                     |

| L2        | GPIO_37 (DP6)  | TRACE_DATA_6  | 0xFFFFEA94       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_37       |                  | 1           | IO      |               |                     |

|           |                | DMM6          |                  | 2           | I       |               |                     |

|           |                | BSS_UART_TX   |                  | 5           | O       |               |                     |

| L1        | GPIO_38 (DP7)  | TRACE_DATA_7  | 0xFFFFEA98       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_38       |                  | 1           | IO      |               |                     |

|           |                | DMM7          |                  | 2           | I       |               |                     |

|           |                | DSS_UART_TX   |                  | 5           | O       |               |                     |

| C3        | GPIO_39 (DP8)  | TRACE_DATA_8  | 0xFFFFEA9C       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_39       |                  | 1           | IO      |               |                     |

|           |                | DMM8          |                  | 2           | I       |               |                     |

|           |                | CAN1_FD_TX    |                  | 4           | O       |               |                     |

|           |                | EPWM1SYNCI    |                  | 5           | I       |               |                     |

| B3        | GPIO_40 (DP9)  | TRACE_DATA_9  | 0xFFFFEAA0       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_40       |                  | 1           | IO      |               |                     |

|           |                | DMM9          |                  | 2           | I       |               |                     |

|           |                | CAN1_FD_RX    |                  | 4           | I       |               |                     |

|           |                | EPWM1SYNCO    |                  | 5           | O       |               |                     |

| C4        | GPIO_41 (DP10) | TRACE_DATA_10 | 0xFFFFEAA4       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_41       |                  | 1           | IO      |               |                     |

|           |                | DMM10         |                  | 2           | I       |               |                     |

|           |                | EPWM3A        |                  | 4           | O       |               |                     |

| A3        | GPIO_42 (DP11) | TRACE_DATA_11 | 0xFFFFEAA8       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_42       |                  | 1           | IO      |               |                     |

|           |                | DMM11         |                  | 2           | I       |               |                     |

|           |                | EPWM3B        |                  | 4           | O       |               |                     |

| B4        | GPIO_43 (DP12) | TRACE_DATA_12 | 0xFFFFEAAC       | 0           | O       | 出力ディセーブル      | プルダウン               |

|           |                | GPIO_43       |                  | 1           | IO      |               |                     |

|           |                | DMM12         |                  | 2           | I       |               |                     |

|           |                | EPWM1A        |                  | 4           | O       |               |                     |

**表 6-1. ピン属性 (ALP180A パッケージ) (続き)**

| ポール番号 [1] | ポール名 [2]          | 信号名 [3]       | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7]   | プルアップ / ダウントップ [8] |

|-----------|-------------------|---------------|------------------|-------------|---------|-----------------|--------------------|

|           |                   | CAN2_FD_TX    |                  | 5           | O       |                 |                    |

| A4        | GPIO_44 (DP13)    | TRACE_DATA_13 | 0xFFFFEAB0       | 0           | O       | 出力ディセーブル        | プルダウン              |

|           |                   | GPIO_44       |                  | 1           | IO      |                 |                    |

|           |                   | DMM13         |                  | 2           | I       |                 |                    |

|           |                   | EPWM1B        |                  | 4           | O       |                 |                    |

|           |                   | CAN1_FD_RX    |                  | 5           | I       |                 |                    |

| C5        | GPIO_45 (DP14)    | TRACE_DATA_14 | 0xFFFFEAB4       | 0           | O       | 出力ディセーブル        | プルダウン              |

|           |                   | GPIO_45       |                  | 1           | IO      |                 |                    |

|           |                   | DMM14         |                  | 2           | I       |                 |                    |

|           |                   | EPWM2A        |                  | 4           | O       |                 |                    |

| B5        | GPIO_46 (DP15)    | TRACE_DATA_15 | 0xFFFFEAB8       | 0           | O       | 出力ディセーブル        | プルダウン              |

|           |                   | GPIO_46       |                  | 1           | IO      |                 |                    |

|           |                   | DMM15         |                  | 2           | I       |                 |                    |

|           |                   | EPWM2B        |                  | 4           | O       |                 |                    |

| U3        | GPIO_47 (DMM_CLK) | TRACE_CLK     | 0xFFFFEABC       | 0           | O       | 出力ディセーブル        | プルダウン              |

|           |                   | GPIO_47       |                  | 1           | IO      |                 |                    |

|           |                   | DMM_CLK       |                  | 2           | I       |                 |                    |

| U4        | DMM_SYNC          | TRACE_CTL     | 0xFFFFEAC0       | 0           | O       | 出力ディセーブル        | プルダウン              |

|           |                   | DMM_SYNC      |                  | 2           | I       |                 |                    |

| V13       | MCU_CLKOUT        | GPIO_25       | 0xFFFFEA60       | 0           | IO      | 出力ディセーブル        | プルダウン              |

|           |                   | MCU_CLKOUT    |                  | 1           | O       |                 |                    |

|           |                   | CHIRP_START   |                  | 2           | O       |                 |                    |

|           |                   | CHIRP_END     |                  | 6           | O       |                 |                    |

|           |                   | FRAME_START   |                  | 7           | O       |                 |                    |

|           |                   | EPWM1A        |                  | 12          | O       |                 |                    |

|           |                   |               |                  |             |         |                 |                    |

| U14       | NERROR_IN         | NERROR_IN     | 0xFFFFEA44       | 0           | I       | 入力              |                    |

| U15       | NERROR_OUT        | NERROR_OUT    | 0xFFFFEA4C       | 0           | O       | Hi-Z (オープンドレイン) |                    |

| V10       | PMIC_CLKOUT       | SOP[2]        | 0xFFFFEA68       | パワーアップ時     | I       | 出力ディセーブル        | プルダウン              |

|           |                   | GPIO_27       |                  | 0           | IO      |                 |                    |

|           |                   | PMIC_CLKOUT   |                  | 1           | O       |                 |                    |

|           |                   | CHIRP_START   |                  | 6           | O       |                 |                    |

|           |                   | CHIRP_END     |                  | 7           | O       |                 |                    |

|           |                   | FRAME_START   |                  | 8           | O       |                 |                    |

|           |                   | EPWM1B        |                  | 11          | O       |                 |                    |

|           |                   | EPWM2A        |                  | 12          | O       |                 |                    |

|           |                   |               |                  |             |         |                 |                    |

表 6-1. ピン属性 (ALP180A パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]  | 信号名 [3]      | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7] | プルアップ / ダウン タイプ [8] |

|-----------|-----------|--------------|------------------|-------------|---------|---------------|---------------------|

| H3        | QSPI[0]   | GPIO_8       | 0xFFFFEA2C       | 0           | IO      | 出力ディセーブル      | プルダウン               |

|           |           | QSPI[0]      |                  | 1           | IO      |               |                     |

|           |           | SPIB_MISO    |                  | 2           | IO      |               |                     |

| G2        | QSPI[1]   | GPIO_9       | 0xFFFFEA30       | 0           | IO      | 出力ディセーブル      | プルダウン               |

|           |           | QSPI[1]      |                  | 1           | I       |               |                     |

|           |           | SPIB_MOSI    |                  | 2           | IO      |               |                     |

|           |           | SPIB_CS_N_2  |                  | 8           | IO      |               |                     |

| J3        | QSPI[2]   | GPIO_10      | 0xFFFFEA34       | 0           | IO      | 出力ディセーブル      | プルダウン               |

|           |           | QSPI[2]      |                  | 1           | I       |               |                     |

|           |           | CAN1_FD_TX   |                  | 8           | O       |               |                     |

| K2        | QSPI[3]   | GPIO_11      | 0xFFFFEA38       | 0           | IO      | 出力ディセーブル      | プルダウン               |

|           |           | QSPI[3]      |                  | 1           | I       |               |                     |

|           |           | CAN1_FD_RX   |                  | 8           | I       |               |                     |

| H2        | QSPI_CLK  | GPIO_7       | 0xFFFFEA3C       | 0           | IO      | 出力ディセーブル      | プルダウン               |

|           |           | QSPI_CLK     |                  | 1           | O       |               |                     |

|           |           | SPIB_CLK     |                  | 2           | IO      |               |                     |

|           |           | DSS_UART_TX  |                  | 6           | O       |               |                     |

| J2        | QSPI_CS_N | GPIO_6       | 0xFFFFEA40       | 0           | IO      | 出力ディセーブル      | プルアップ               |

|           |           | QSPI_CS_N    |                  | 1           | O       |               |                     |

|           |           | SPIB_CS_N    |                  | 2           | IO      |               |                     |

| V16       | RS232_RX  | GPIO_15      | 0xFFFFEA74       | 0           | IO      | 入力イネーブル       | プルアップ               |

|           |           | RS232_RX     |                  | 1           | I       |               |                     |

|           |           | MSS_UARTA_RX |                  | 2           | I       |               |                     |

|           |           | BSS_UART_TX  |                  | 6           | IO      |               |                     |

|           |           | MSS_UARTB_RX |                  | 7           | IO      |               |                     |

|           |           | CAN1_FD_RX   |                  | 8           | I       |               |                     |

|           |           | I2C_SCL      |                  | 9           | IO      |               |                     |

|           |           | EPWM2A       |                  | 10          | O       |               |                     |

|           |           | EPWM2B       |                  | 11          | O       |               |                     |

|           |           | EPWM3A       |                  | 12          | O       |               |                     |

**表 6-1. ピン属性 (ALP180A パッケージ) (続き)**

| ポール番号 [1] | ポール名 [2]  | 信号名 [3]      | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7] | プルアップ/ダウンタイプ [8] |

|-----------|-----------|--------------|------------------|-------------|---------|---------------|------------------|

| U16       | RS232_TX  | GPIO_14      | 0xFFFFEA78       | 0           | IO      | 出力イネーブル       |                  |

|           |           | RS232_TX     |                  | 1           | O       |               |                  |

|           |           | MSS_UARTA_TX |                  | 5           | IO      |               |                  |

|           |           | MSS_UARTB_TX |                  | 6           | IO      |               |                  |

|           |           | BSS_UART_TX  |                  | 7           | IO      |               |                  |

|           |           | CAN1_FD_TX   |                  | 10          | O       |               |                  |

|           |           | I2C_SDA      |                  | 11          | IO      |               |                  |

|           |           | EPWM1A       |                  | 12          | O       |               |                  |

|           |           | EPWM1B       |                  | 13          | O       |               |                  |

|           |           | NDMM_EN      |                  | 14          | I       |               |                  |

|           |           | EPWM2A       |                  | 15          | O       |               |                  |

| D2        | SPIA_CLK  | GPIO_3       | 0xFFFFEA14       | 0           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | SPIA_CLK     |                  | 1           | IO      |               |                  |

|           |           | CAN2_FD_RX   |                  | 6           | I       |               |                  |

|           |           | DSS_UART_TX  |                  | 7           | O       |               |                  |

| C2        | SPIA_CS_N | GPIO_30      | 0xFFFFEA18       | 0           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | SPIA_CS_N    |                  | 1           | IO      |               |                  |

|           |           | CAN1_FD_TX   |                  | 6           | O       |               |                  |

| D1        | SPIA_MISO | GPIO_20      | 0xFFFFEA10       | 0           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | SPIA_MISO    |                  | 1           | IO      |               |                  |

|           |           | CAN1_FD_RX   |                  | 2           | O       |               |                  |

| F2        | SPIA_MOSI | GPIO_19      | 0xFFFFEA0C       | 0           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | SPIA_MOSI    |                  | 1           | IO      |               |                  |

|           |           | CAN1_FD_RX   |                  | 2           | I       |               |                  |

|           |           | DSS_UART_TX  |                  | 8           | O       |               |                  |

| E2        | SPIB_CLK  | GPIO_5       | 0xFFFFEA24       | 0           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | SPIB_CLK     |                  | 1           | IO      |               |                  |

|           |           | MSS_UARTA_RX |                  | 2           | I       |               |                  |

|           |           | MSS_UARTB_TX |                  | 6           | O       |               |                  |

|           |           | BSS_UART_TX  |                  | 7           | O       |               |                  |

|           |           | CAN1_FD_RX   |                  | 8           | I       |               |                  |

|           |           | GPIO_4       |                  | 0           | IO      |               |                  |

| D3        | SPIB_CS_N | SPIB_CS_N    | 0xFFFFEA28       | 1           | IO      | 出力ディセーブル      | プルアップ            |

|           |           | MSS_UARTA_TX |                  | 2           | O       |               |                  |

|           |           | MSS_UARTB_TX |                  | 6           | O       |               |                  |

|           |           | BSS_UART_TX  |                  | 7           | IO      |               |                  |

|           |           | QSPI_CLK_EXT |                  | 8           | I       |               |                  |

|           |           | CAN1_FD_TX   |                  | 9           | O       |               |                  |

表 6-1. ピン属性 (ALP180A パッケージ) (続き)

| ポール番号 [1] | ポール名 [2]      | 信号名 [3]       | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7] | プルアップ / ダウントラップ [8] |

|-----------|---------------|---------------|------------------|-------------|---------|---------------|---------------------|

| G3        | SPIB_MISO     | GPIO_22       | 0xFFFFEA20       | 0           | IO      | 出力ディセーブル      | ブルアップ               |

|           |               | SPIB_MISO     |                  | 1           | IO      |               |                     |

|           |               | I2C_SCL       |                  | 2           | IO      |               |                     |

|           |               | DSS_UART_TX   |                  | 6           | O       |               |                     |

| G1        | SPIB_MOSI     | GPIO_21       | 0xFFFFEA1C       | 0           | IO      | 出力ディセーブル      | ブルアップ               |

|           |               | SPIB_MOSI     |                  | 1           | IO      |               |                     |

|           |               | I2C_SDA       |                  | 2           | IO      |               |                     |

| B2        | SPI_HOST_INTR | GPIO_12       | 0xFFFFEA00       | 0           | IO      | 出力ディセーブル      | ブルダウン               |

|           |               | SPI_HOST_INTR |                  | 1           | O       |               |                     |

|           |               | SPIB_CS_N_1   |                  | 6           | IO      |               |                     |

| U12       | SYNC_IN       | GPIO_28       | 0xFFFFEA6C       | 0           | IO      | 出力ディセーブル      | ブルダウン               |

|           |               | SYNC_IN       |                  | 1           | I       |               |                     |

|           |               | MSS_UARTB_RX  |                  | 6           | IO      |               |                     |

|           |               | DMM_MUX_IN    |                  | 7           | I       |               |                     |

|           |               | SYNC_OUT      |                  | 9           | O       |               |                     |

| M3        | SYNC_OUT      | SOP[1]        | 0xFFFFEA70       | パワーアップ時     | I       | 出力ディセーブル      | ブルダウン               |

|           |               | GPIO_29       |                  | 0           | IO      |               |                     |

|           |               | SYNC_OUT      |                  | 1           | O       |               |                     |

|           |               | DMM_MUX_IN    |                  | 9           | I       |               |                     |

|           |               | SPIB_CS_N_1   |                  | 10          | IO      |               |                     |

|           |               | SPIB_CS_N_2   |                  | 11          | IO      |               |                     |

| T3        | TCK           | GPIO_17       | 0xFFFFEA50       | 0           | IO      | 入力イネーブル       | ブルダウン               |

|           |               | TCK           |                  | 1           | I       |               |                     |

|           |               | MSS_UARTB_TX  |                  | 2           | O       |               |                     |

|           |               | CAN1_FD_TX    |                  | 8           | O       |               |                     |

| U9        | TDI           | GPIO_23       | 0xFFFFEA58       | 0           | IO      | 入力イネーブル       | ブルアップ               |

|           |               | TDI           |                  | 1           | I       |               |                     |

|           |               | MSS_UARTA_RX  |                  | 2           | I       |               |                     |

| U10       | TDO           | SOP[0]        | 0xFFFFEA5C       | パワーアップ時     | I       | 出力イネーブル       |                     |

|           |               | GPIO_24       |                  | 0           | IO      |               |                     |

|           |               | TDO           |                  | 1           | O       |               |                     |

|           |               | MSS_UARTA_TX  |                  | 2           | O       |               |                     |

|           |               | MSS_UARTB_TX  |                  | 6           | O       |               |                     |

|           |               | BSS_UART_TX   |                  | 7           | O       |               |                     |

|           |               | NDMM_EN       |                  | 9           | I       |               |                     |

**表 6-1. ピン属性 (ALP180A パッケージ) (続き)**

| ポール番号 [1] | ポール名 [2]    | 信号名 [3]     | PINCNTL アドレス [4] | モード [5] [9] | タイプ [6] | ポールリセット状態 [7]      | プルアップ / ダウントップ [8] |

|-----------|-------------|-------------|------------------|-------------|---------|--------------------|--------------------|

| U8        | TMS         | GPIO_18     | 0xFFFFEA54       | 0           | IO      | 入力イネーブル            | プルダウン              |

|           |             | TMS         |                  | 1           | I       |                    |                    |

|           |             | BSS_UART_TX |                  | 2           | O       |                    |                    |

|           |             | CAN1_FD_RX  |                  | 6           | I       |                    |                    |

| U13       | WARM_RESET  | WARM_RESET  | 0xFFFFEA48       | 0           | IO      | Hi-Z 入力 (オープンドレイン) |                    |

| R2        | LVDS_CLKM   | LVDS_CLKM   |                  |             | O       |                    |                    |

| R1        | LVDS_CLKP   | LVDS_CLKP   |                  |             | O       |                    |                    |

| N2        | LVDS_TXP[0] | LVDS_TXP[0] |                  |             | O       |                    |                    |

| N1        | LVDS_TXM[0] | LVDS_TXM[0] |                  |             | O       |                    |                    |

| P2        | LVDS_TXP[1] | LVDS_TXP[1] |                  |             | O       |                    |                    |

| P1        | LVDS_TXM[1] | LVDS_TXM[1] |                  |             | O       |                    |                    |

| T1        | LVDS_FRCLKP | LVDS_FRCLKP |                  |             | O       |                    |                    |

| T2        | LVDS_FRCLKM | LVDS_FRCLKM |                  |             | O       |                    |                    |

| U11       | NRESET      | NRESET      |                  |             | I       |                    |                    |

| A7        | CLKP        | CLKP        |                  |             | I       |                    |                    |

| B7        | CLKM        | CLKM        |                  |             | I       |                    |                    |

| A14       | OSC_CLKOUT  | OSC_CLKOUT  |                  |             | O       |                    |                    |

| A16       | VBGAP       | VBGAP       |                  |             | O       |                    |                    |

| E1        | VDDIN       | VDDIN       |                  |             | PWR     |                    |                    |

| J1        | VDDIN       | VDDIN       |                  |             | PWR     |                    |                    |

| V4        | VDDIN       | VDDIN       |                  |             | PWR     |                    |                    |

| V8        | VDDIN       | VDDIN       |                  |             | PWR     |                    |                    |

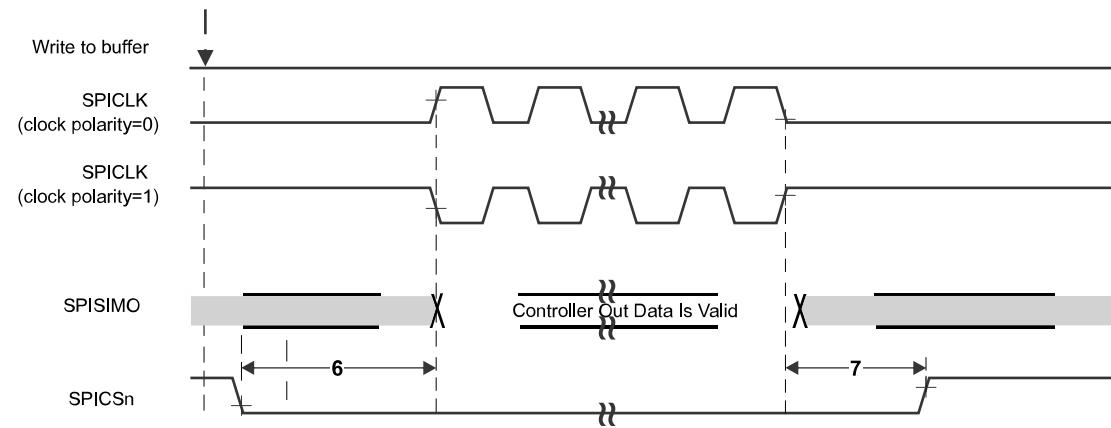

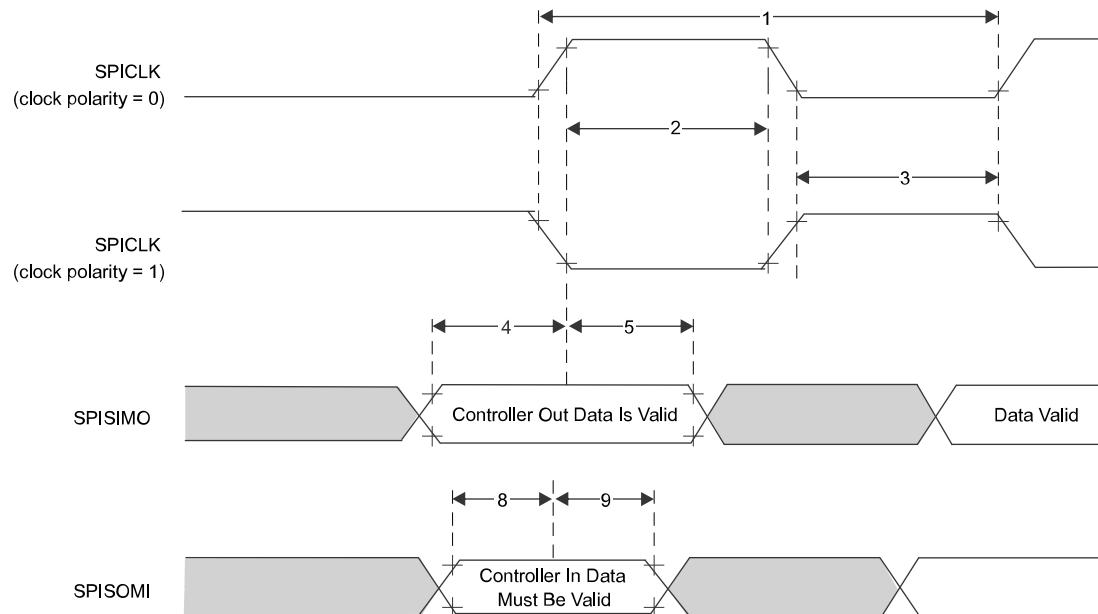

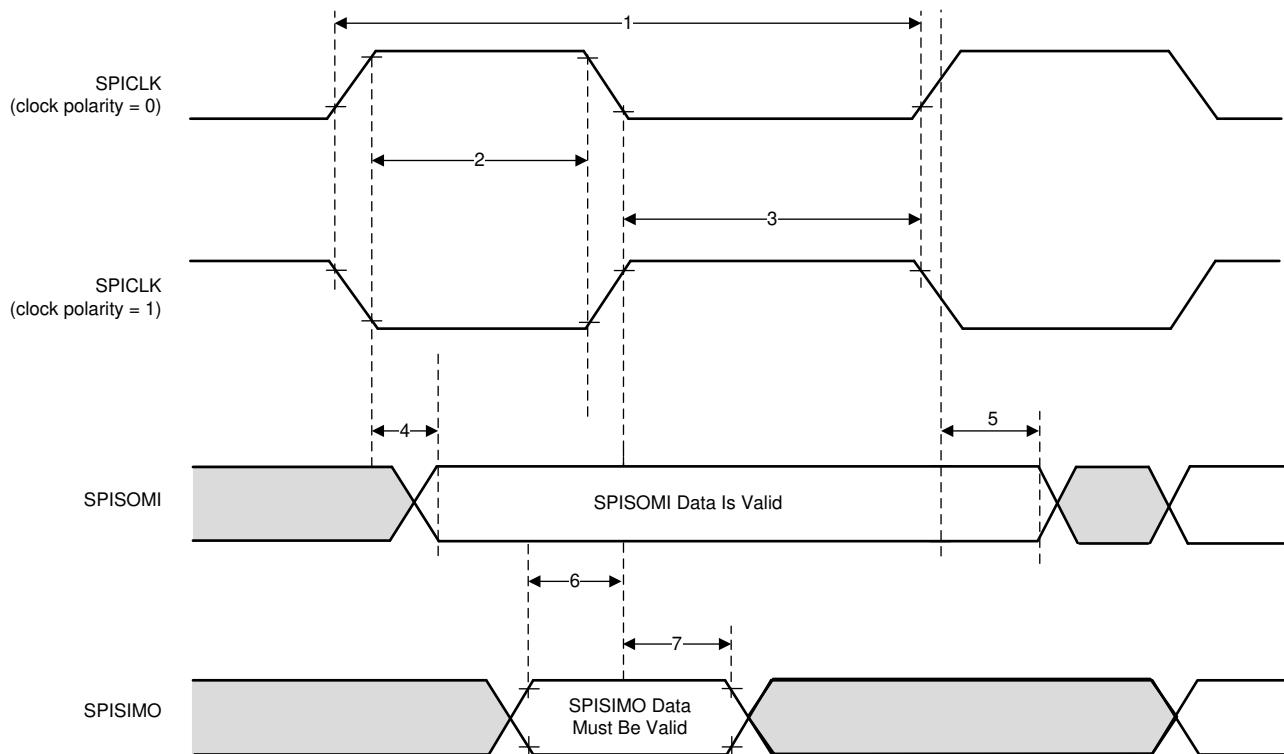

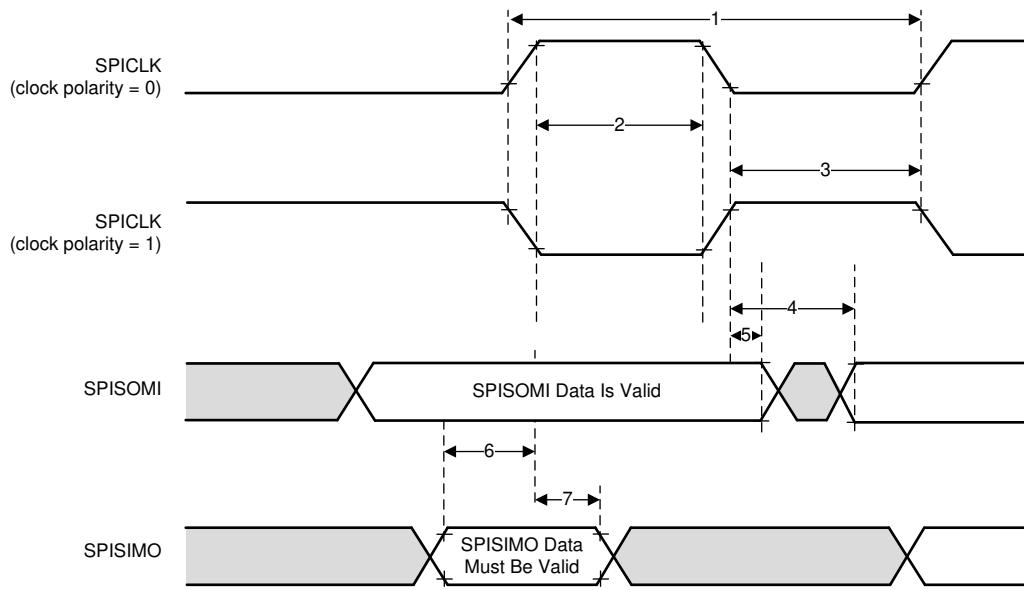

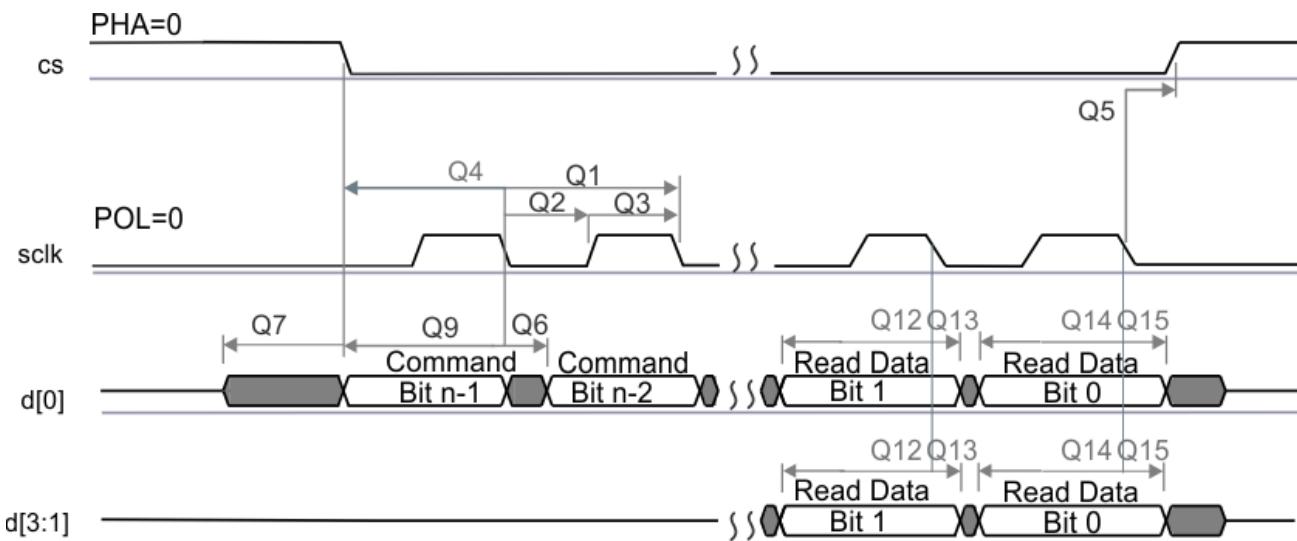

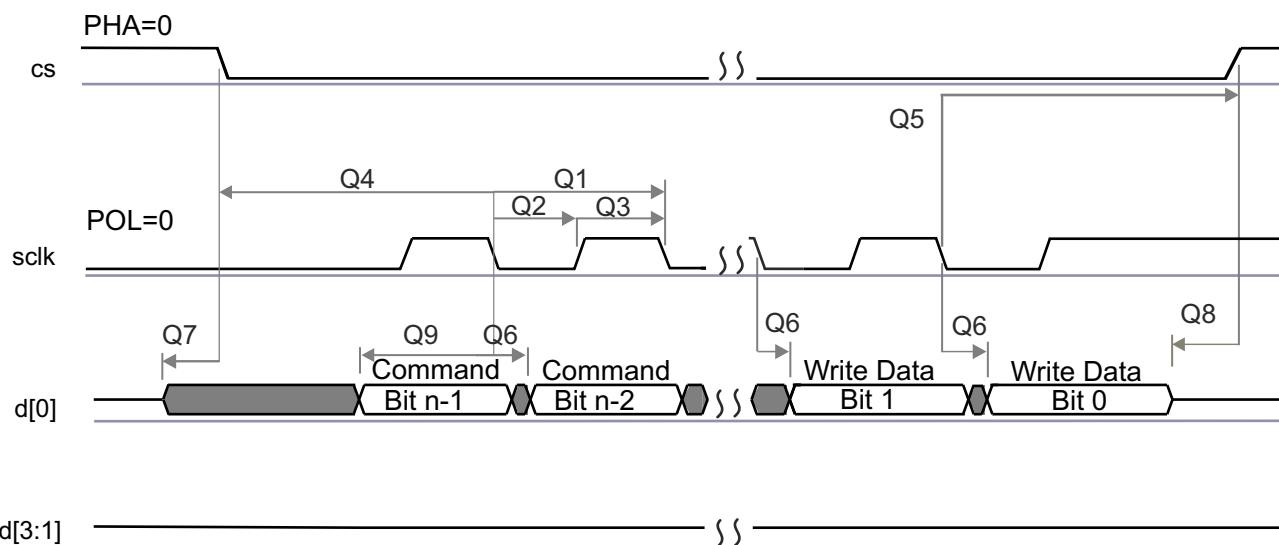

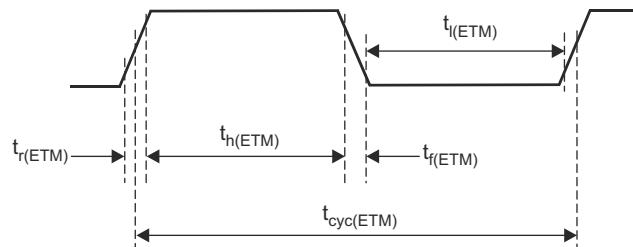

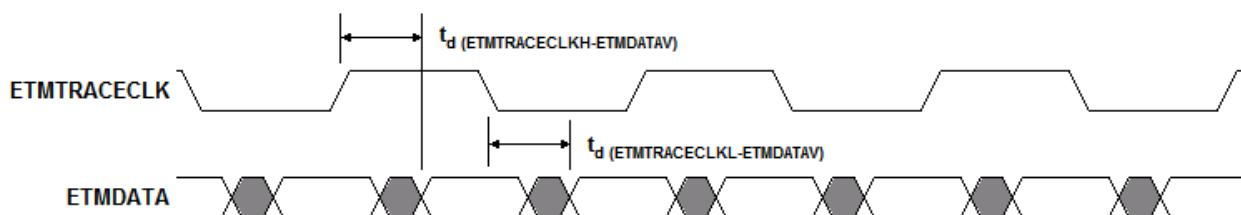

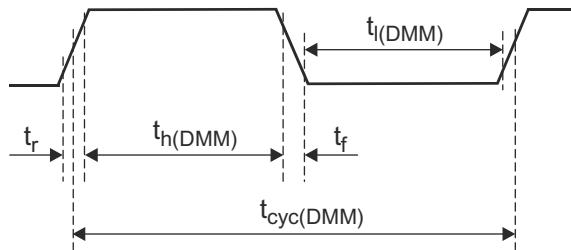

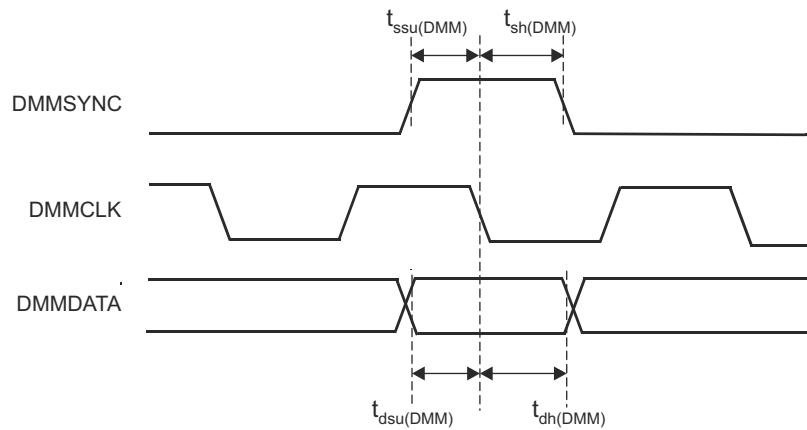

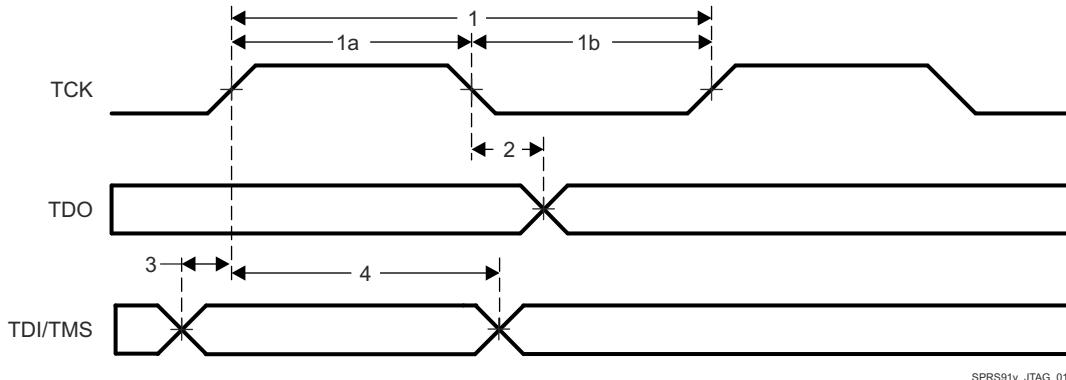

| V15       | VDDIN       | VDDIN       |                  |             | PWR     |                    |                    |