## Technical Article

# 高スイッチング周波数での整流器向けアクティブ クランプ回路の設計

Daniel Gao

### はじめに

車載電気システムにおいて、高電圧から低電圧への DC/DC コンバータは反転可能な電子デバイスであり、高電圧 (400V または 800V) 車載バッテリの DC をそれより低い DC 電圧 (12V) に変化させます。これらのコンバータは、単方向または双方向にすることができます。一般的な電力レベルは 1kW ~ 3kW で、システムには、コンバータの高電圧パワー ネット (1 次側) に対する定格が 650V ~ 1,200V で、12V のパワー ネット (2 次側) に対して定格が 60V 以上である部品が必要です。

電力密度の向上とパワートレインの小型化に対するニーズにより、磁気部品のサイズを縮小するために電源部品のスイッチング周波数が数百キロヘルツに引き上げられました。高電圧から低電圧への DC/DC コンバータの小型化により、スイッチング周波数が低い場合に、電磁適合性 (EMC)、放熱、金属酸化膜半導体電界効果トランジスタ (MOSFET) 向けのアクティブ クランプなど、それほど重要ではない問題が多発します。この Power Tip では、高いスイッチング周波数での同期整流 MOSFET 向けクランプ回路の設計について説明します。

### 従来型のアクティブ クランプ

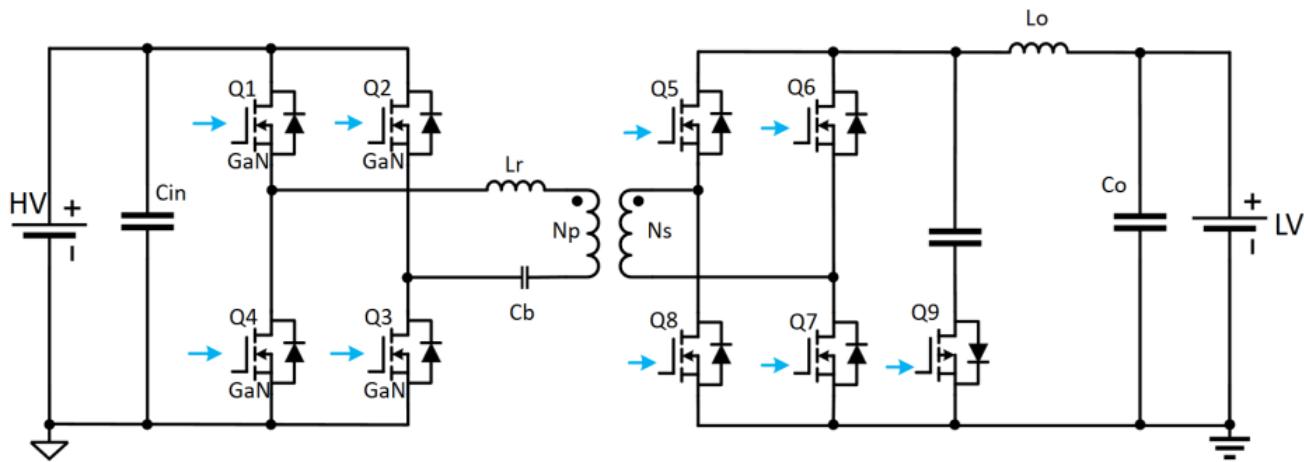

図 1 に示す位相シフトフルブリッジ (PSFB) は、コンバータ効率を上げるためにスイッチでソフト スイッチングを実現できるため、高電圧から低電圧への DC/DC 用途で人気の高いトポロジです。しかし、同期整流器の寄生容量がトランスのリーケージ インダクタンスで共振するため、同期整流器では高電圧ストレスの発生が予想されます。整流器の電圧ストレスは、式 1 と同じ高さになる可能性があります。

$$V_{ds\_max} = 2V_{IN}x(N_s/N_p) \quad (1)$$

N<sub>p</sub> と N<sub>s</sub> はそれぞれトランスの 1 次巻線と 2 次巻線です。

設計者は多くの場合、高電圧から低電圧への DC/DC コンバータの電力レベルと、抵抗容量結合形ダイオードスナバの電力損失 [1] を考慮して、同期整流 MOSFET にアクティブ クランプ回路を使用します。代表的な回路を 図 1 に示します。

図 1. PSFB 同期整流 MOSFET の従来型のアクティブ クランプ回路出典: [テキサス・インスツルメンツ](#)

この回路図には、アクティブ クランプ回路の主要な部品である P チャネル金属酸化膜半導体 (PMOS) Q9 とスナバ コンデンサが示されています。スナバコンデンサの 1 つの端子を出力チョークに接続し、PMOS のソースを接地します。PSFB の従来型アクティブ クランプ回路では、同期整流 MOSFET Q5 と Q7 の方式が同じであるため、Q6 と Q8 も同じです。同期整流 MOSFET がシャットダウンするたびに、PMOS は適切な遅延時間でオンになります。

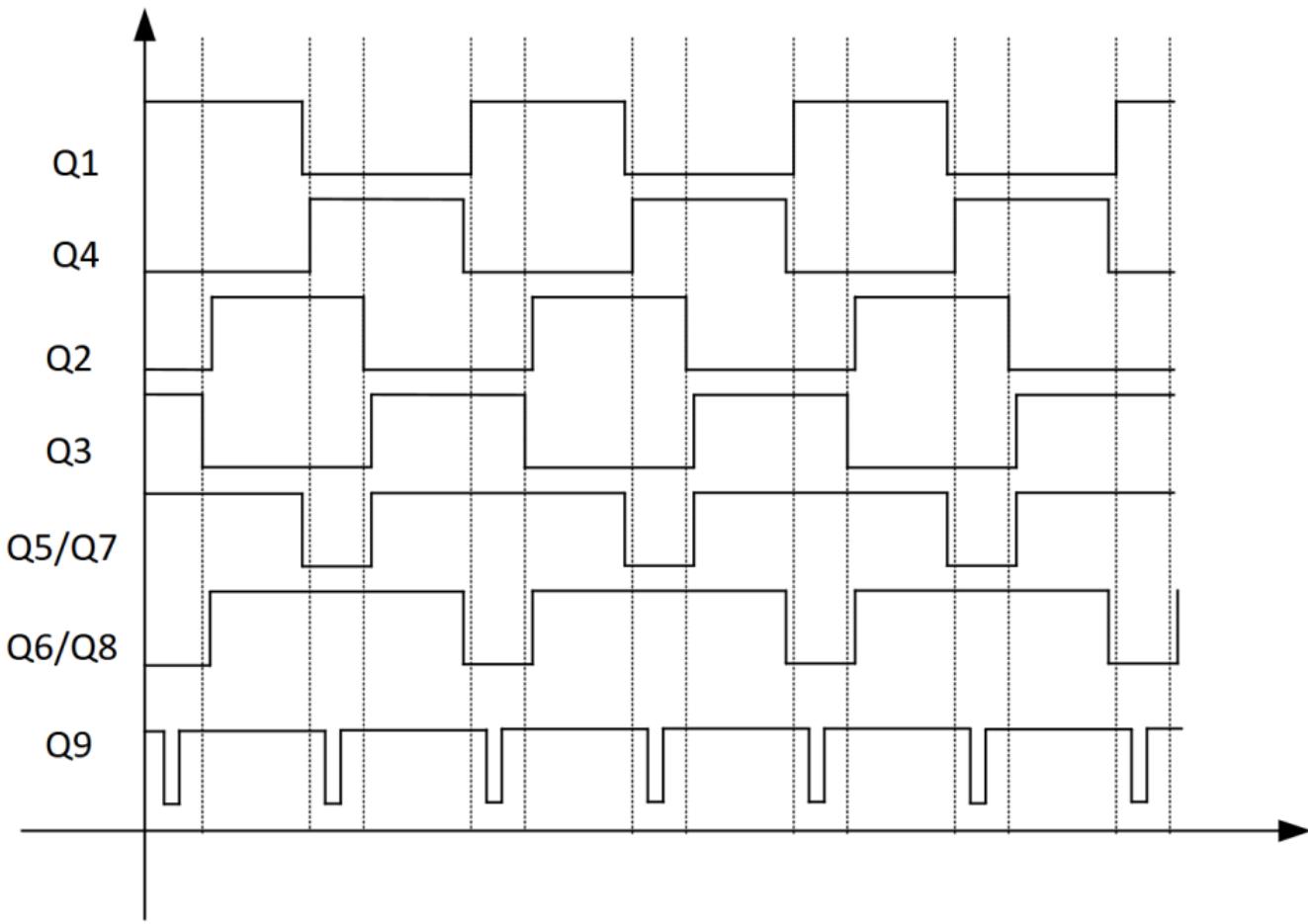

図 2 に PSFB とアクティブ クランプの制御方式を示します。PMOS のスイッチング周波数が  $f_{sw}$  の 2 倍になることは容易に理解できます。

図 2. アクティブ クランプ PMOS Q9 の制御方式 (PMOS のスイッチング周波数が  $f_{sw}$  の 2 倍) 出典: テキサス・インスツルメンツ

### アクティブ クランプ損失の評価

式 2、式 3、式 4、式 5、式 6 を使用して、アクティブ クランプ PMOS の損失を評価できます。 $P_{on\_state}$  以外のすべての損失は  $f_{sw}$  に比例します。PMOS のスイッチング周波数が 2 倍になると損失は 2 倍になります。そのため、PMOS の熱関連問題を解決しなければならなくなります。また、小型化のニーズを満たすために  $f_{sw}$  を高くすると、実際の熱問題がさらに悪化することが判明しています。

$$P_{on\_state} = I_{rms}^2 \times R_{ds(on)} \quad (2)$$

$$P_{turn\_on} = 0.5 \times V_{ds} \times I_{on} \times t_{on} \times f_{sw} \quad (3)$$

$$P_{turn\_off} = 0.5 \times V_{ds} \times I_{off} \times t_{off} \times f_{sw} \quad (4)$$

$$P_{drive} = V_{drv} \times Q_g \times f_{sw} \quad (5)$$

$$P_{diode} = I_{snubber} \times V_{sd} \times t_d \times f_{sw} \quad (6)$$

## アクティブ クランプの提案

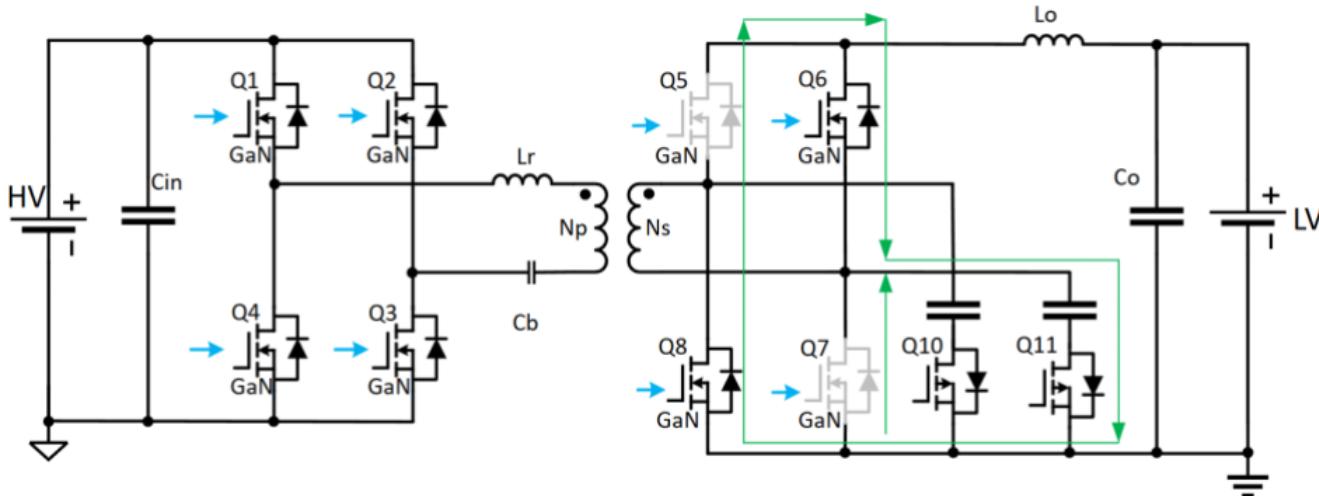

この問題を解決するにはどうすればよいのでしょうか。性能指数 (FOM) に優れた PMOS を選択すべきか、それとも導電率係数が高い熱グリースを選択すべきでしょうか？どちらでも構わないのですが、アクティブ クランプによる熱問題は依然として 1 つの部分に集中して発生します。このことがこの問題の解決を困難にしているのです。熱を複数の部分に分散させることはできないのでしょうか？実行可能な方法は、図 3 に示すように、2 つのアクティブ クランプ回路を使用し、スナバコンデンサの端子を 2 次側レッグのスイッチング ノードに接続することです。Q11 をオンにできるのは Q5 と Q7 がオフになった後のみで、Q10 をオンにできるのは Q6 と Q8 がオフになった後のみです。PSFB と提案するアクティブ クランプの制御方式を 図 4 に示します。

図 3. PSFB 同期整流 MOSFET 用アクティブ クランプ回路の提案出典:テキサス・インスツルメンツ

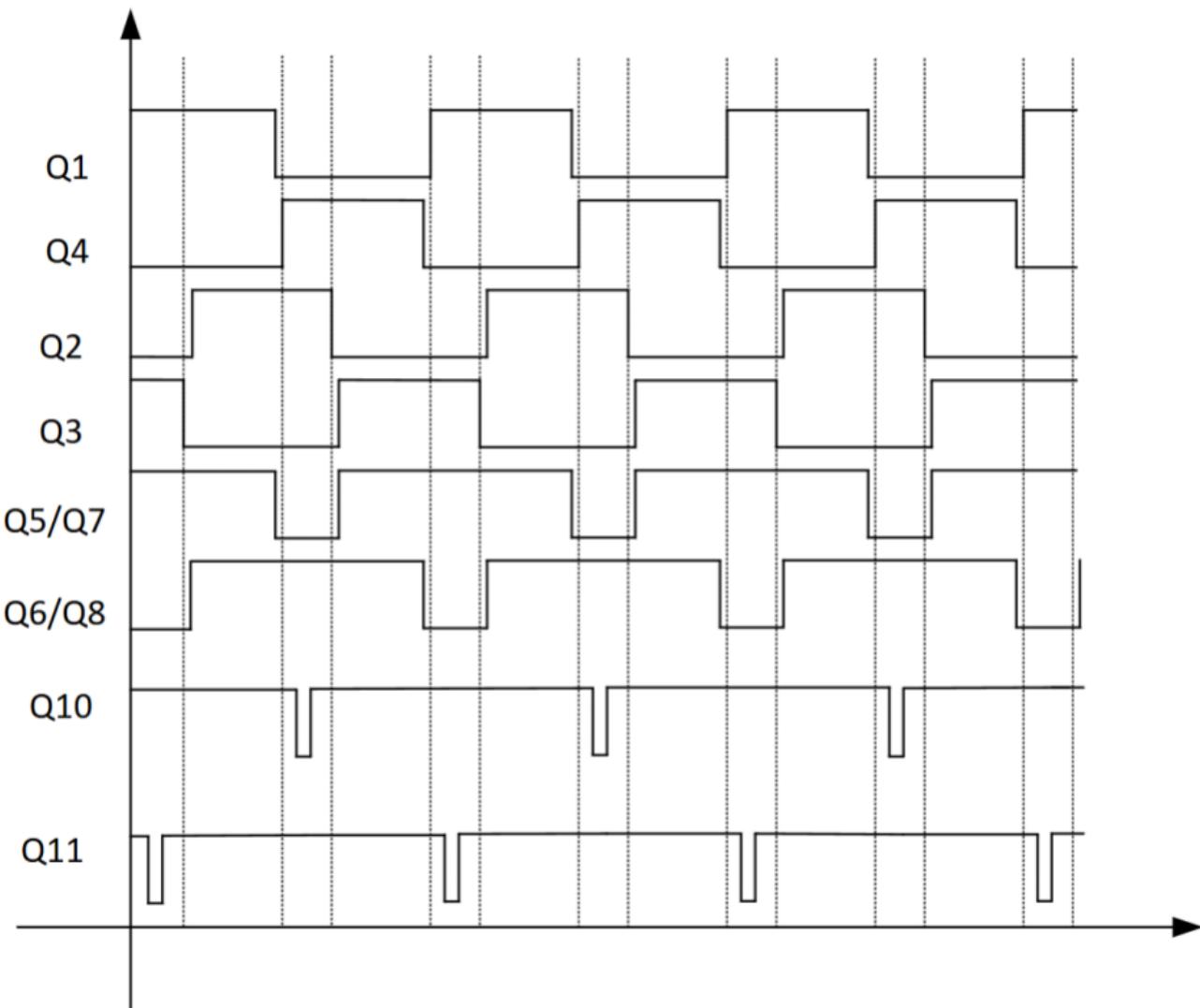

図 4. PSFB と提案するアクティブクランプの制御方式出典:テキサス・インスツルメンツ

Q5 と Q7 がオフになっても Q6 と Q8 は引き続きオンのままで。そのため、図 3 で緑色の矢印で示されているように、Q5 と Q7 のクランプ ループを見つけることができます。Q10 と Q11 のスイッチング周波数はどちらも  $f_{sw}$  であり、 $f_{sw}$  の 2 倍ではありません。

式 2、式 3、式 4、式 5、式 6 によれば、各 PMOS の  $P_{on\_state}$  は元の 4 分の 1 になり、 $P_{turn\_on}$ 、 $P_{turn\_off}$ 、 $P_{drive}$ 、 $P_{diode}$  は元の半分になります。提案している方法ではクランプ回路の損失を 2 つの部に分散させるので、熱問題への対応が明らかに容易になります。

ここでクランプ ループに話を戻します。Q5 のループは Q7 よりも大きく、Q6 と Q8 と同様です。Q5 と Q6 の最小クランプ ループを得るには、同期整流器のレイアウトに注意する必要があります。

## アクティブ クランプ性能の提案

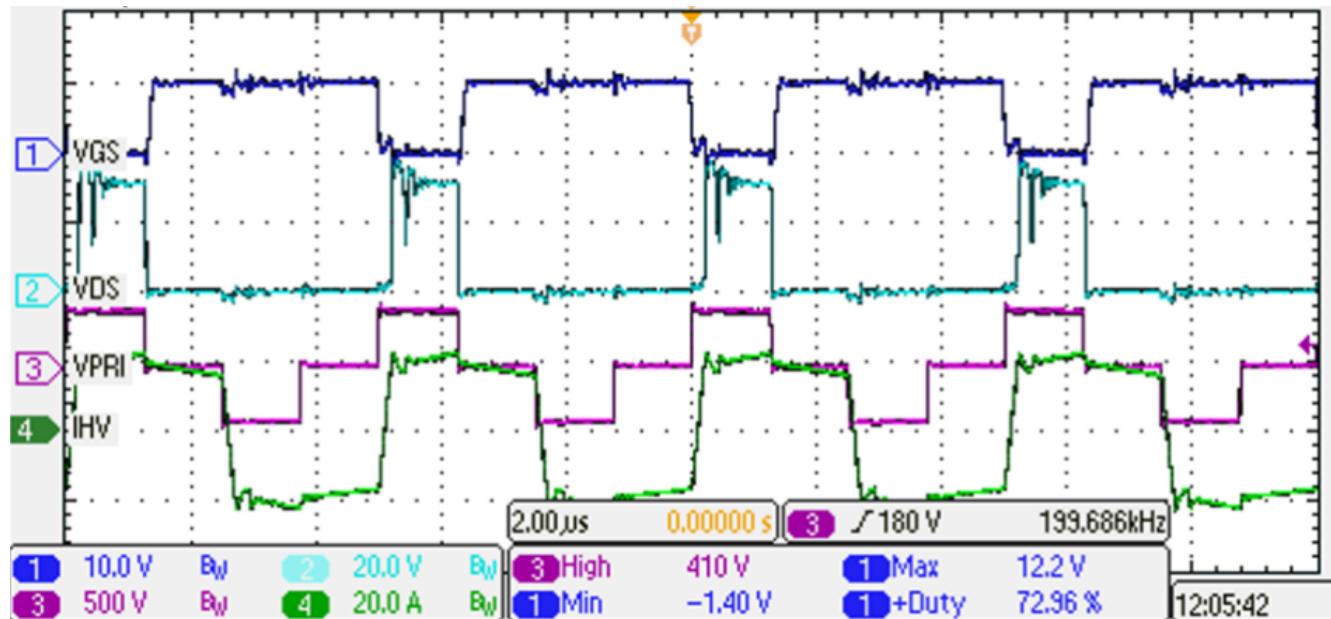

図 5 と図 6 に、テキサス インスツルメンツの「GaN HEMT を搭載した高電圧から低電圧への DC/DC コンバータのリファレンス設計」から関連するテストを示します。この設計では、200kHz のスイッチング周波数で動作するアクティブクランプ回路案を採用しています。図 5 に整流器の電圧ストレスを示します。

図 5. 整流器の電圧ストレス (CH1 は整流器の  $V_{gs}$ 、CH2 は整流器の  $V_{ds}$ 、CH3 は 1 次側トランス巻線の電圧、CH4 は 1 次側トランス巻線の電流)出典:テキサス・インスツルメンツ

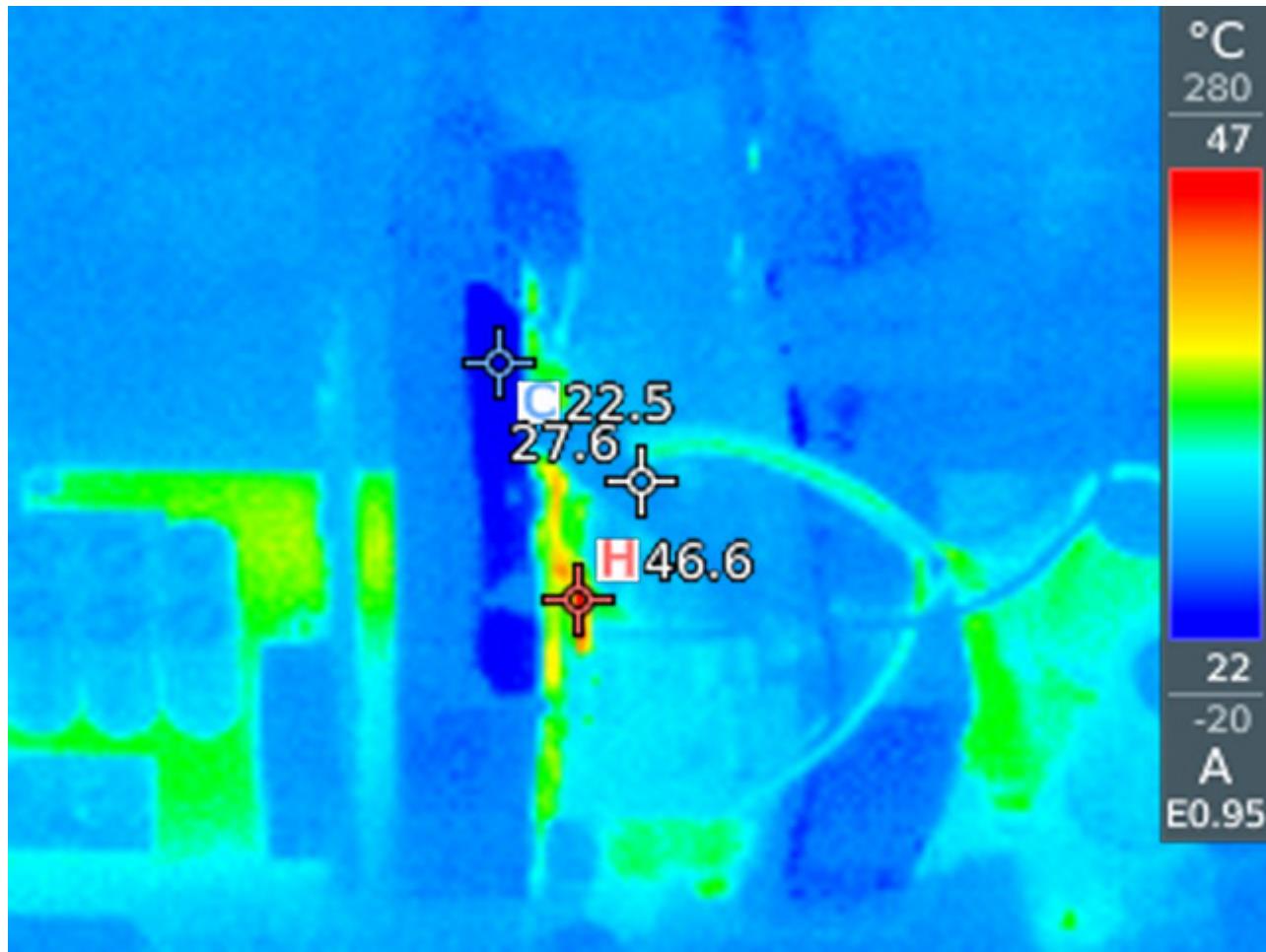

CH1 は整流器の  $V_{gs}$ 、CH2 は整流器の  $V_{ds}$ 、CH3 は 1 次側トランス巻線の電圧、CH4 は 1 次側トランス巻線の電流です。整流器の最大電圧ストレスは、 $400V_{IN}$ 、 $13.5V_{OUT}$ 、 $250A I_{OUT}$  で 45V 未満です。図 6 に示すように、アクティブ クランプ回路の最高温度は  $400V_{IN}$ 、 $13.5V_{OUT}$ 、 $180A I_{OUT}$  [2] で  $46.6^{\circ}C$  です。そのため、この制御方式案は、クランプ MOSFET に対して非常に優れた放熱性能を達成します。

図 6. アクティブ クランプ回路の放熱性能 (アクティブ クランプの最大温度は  $400V_{IN}$ 、 $13.5V_{OUT}$ 、 $180A I_{OUT}$  で  $46.6^{\circ}C$ )

出典:テキサス・インスツルメンツ

### 熱問題が発生しない 500kHz アクティブ クランプ

スイッチング周波数を 200kHz から 500kHz に上げると、トランジスタの体積が約 45% 縮小し [2]、高電圧から低電圧への DC/DC コンバータの電力密度の向上に役立ちます。この方法案では BOM コストが多少増加しますが、設計者は熱問題がなく 500kHz のスイッチング周波数でアクティブ クランプを動作させることができ、これが性能の向上につながります。PMOS のパルス ドレイン電流が NMOS よりもはるかに小さいことを考慮すると、設計者は、必要に応じて、絶縁ドライバとバイアス電源を搭載したアクティブ クランプで NMOS を使用することもできます。

### 関連コンテンツ

- [Power Tips #135: ESS 内の双方向 CLLLC 共振コンバータの制御方式](#)

- [Power Tips #134: ハードなスイッチングを行わない — PWM フルブリッジで ZVS を実現](#)

- [Power Tips #133: TLVR で合計リーケージ インダクタンスを測定し性能を最適化](#)

- [高精度クランプによるデータロガーの保護](#)

- [反転バイポーラ トランジスタは信号クランプとしても機能](#)

- [高速クランプはパルス形成回路として機能](#)

### 参考資料

1. Betten, John. 2016.『[Power Tips: 7 つの R-C スナップ計算ステップ](#)』TI E2E™ 設計サポートフォーラム技術記事 (2016 年 5 月)

**商標**

2. 「[GaN HEMT を搭載した高電圧から低電圧への DC/DC コンバータのリファレンス設計](#)」2024.テキサス・インスツルメンツのリファレンス設計テストレポート (No. PMP41078、文献番号 TIDT403A)2024 年 12 月 16 日アクセス。

この記事は、以前 EDN.com で公開された記事です。

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated