## Design Guide: TIDA-050051

## 車載対応、PMIC と FPD-Link III 搭載、8.3MP の POC カメラ モジュールのリファレンス デザイン

## 説明

カメラ モジュールを提示するこのリファレンス デザインは、8.3 メガピクセルのイメージャと、4.16Gbps の TI の FPD-Link III シリアライザを組み合わせ、ADAS (先進運転支援システム) 向けの小型で低コストというカメラの需要に対応しています。また、電源管理集積回路 (PMIC) により、超小型のフォームファクタで 2 つのデバイスに電力を供給できます。このデザインが採用している高速シリアルインターフェイスは、車載リモート カメラ モジュールを、ディスプレイまたはマシン ビジョン処理システムに接続するほか、1 本の同軸ケーブルで 8.3MP (メガピクセル) の RAW12 HDR ビデオ データと電力の両方を伝送することができます。

## リソース

|              |            |

|--------------|------------|

| TIDA-050051  | デザイン フォルダ  |

| TPS650330-Q1 | プロダクト フォルダ |

| DS90UB953-Q1 | プロダクト フォルダ |

テキサス・インスツルメンツの™ E2E サポート エキスパートにお問い合わせください。

## 特長

- 1 枚の 20mm × 20mm PCB に統合型電源を搭載した省スペース設計

- 統合型 TPS650330-Q1 電源に 3 つの降圧コンバータと LDO を内蔵し、高効率と低ノイズの電源生成を実現

- P2P 互換電源により機能安全アプリケーションを実現

- DS90UB953-Q1 を使用して最大 8MP / 27fps のカメラ アプリケーションを実現

- Onsemi 製 8.3 MP の AR0820 イメージ センサは、12 ビット AD、MIPI 4 レーン、HDR RAW12、RAW14、RAW16、RAW20、RAW24 を実現

- デジタルビデオ、電力供給、制御、診断用に Rosenberger 製 FAKRA 同軸コネクタを 1 個実装

## アプリケーション

- 処理機能なしのカメラ モジュール

- フロント カメラ

- リア カメラ

- サラウンド ビュー システム

## 1 システムの説明

多くの車載アプリケーションでは、システムをコンパクトかつモジュール化できるよう、回路面積を抑えた小型フォーム フィクタが求められます。そのため、ADAS 用カメラを設計する際には、カメラ本体および電子部品のほとんどが厳しいスペース制約を満たす必要があります。このリファレンス デザインは、8.3 メガピクセルのイメージャ、4.16 Gbps のシリアルライザ、1 個の電源管理 IC を含み、すべての部品を 20mm × 20mm の基板上に収めることで、この課題に対応しています。このシステムに必要な接続は、50Ω の同軸ケーブル 1 本だけです。

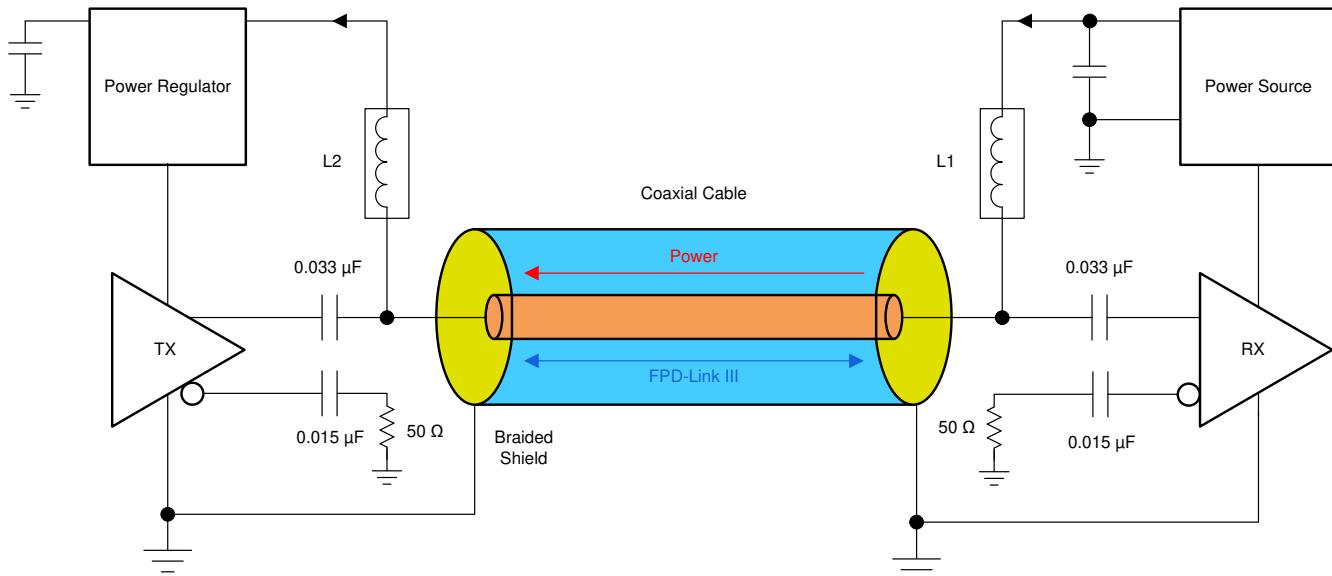

DC 電力、FPD-Link フロントチャネル、FPD-Link バックチャネルなどが FAKRA 同軸コネクタ経由でボードに接続されます。図 1-1 のフィルタは、信号の DC (電力) 部分がインダクタ L5 を通過できるようにしながら、信号の高速成分 (大幅な減衰なし) をすべてブロックします。

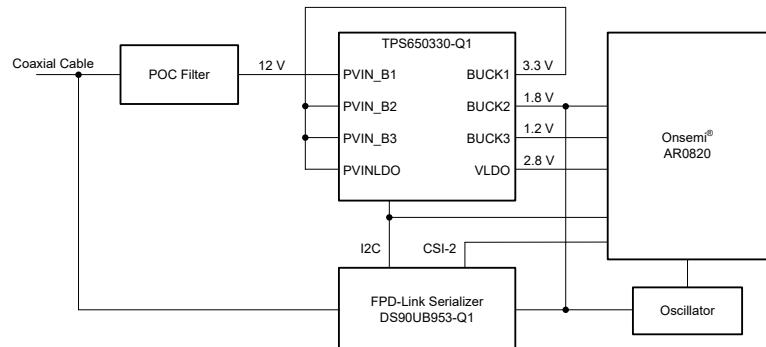

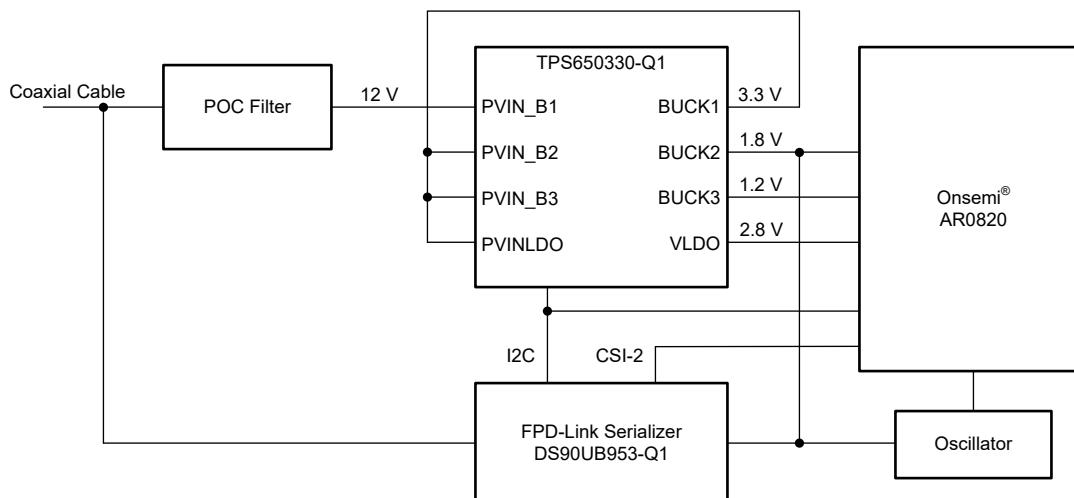

図 1-1. FPD-Link III 信号路

DC 部分は、TPS650330-Q1 パワー マネージメント IC の降圧 1 入力に接続されています。この電圧は、デバイスの降圧 2 と降圧 3 に電力を供給します。これらの電圧は、イメージャとシリアルライザへの電源レールを作成します。LDO 入力ピンは 3.3V に供給され、イメージャに低ノイズの 2.8-V アナログ電源を供給します。降圧 3 はイメージャ専用の 1.1V を出力し、降圧 2 はイメージャとシリアルライザの両方で共有される汎用の 1.8V デジタル電源を生成します。信号の高周波部分はシリアルライザに直接接続されます。これは、シリアルライザとデシリアルライザの間で、映像データおよび制御用バックチャネルが通る経路です。

イメージャの出力は、4 レーンの MIPI CSI-2 インターフェイスを経由してシリアルライザに接続されています。シリアルライザは、このビデオ データを、単一の LVDS ペアを介して、同軸ケーブルのもう一方の端にあるデシリアルライザに送信します。

さらに、同じ同軸ケーブル上に、独立した低レイテンシの双方向制御チャネルがあり、I<sup>2</sup>C ポートから制御情報を送信する追加の機能を提供します。この制御チャネルは、ビデオ ブランкиング期間には依存しません。イメージャを設定および制御するために、システム マイクロプロセッサによって使用されます。

### 1.1 主なシステム仕様

表 1-1. 主なシステム仕様

| パラメータ              | 備考     | 最小値                    | 標準値 | 最大値 | 単位              |

|--------------------|--------|------------------------|-----|-----|-----------------|

| V <sub>IN</sub>    | 電源電圧   | Power over coax (POC)  | 5   | 12  | 18.3            |

| P <sub>TOTAL</sub> | 総消費電力  | V <sub>POC</sub> = 12V | —   | 1   | 1.5             |

| A <sub>PCB</sub>   | PCB 面積 |                        | —   | —   | mm <sup>2</sup> |

## 2 システム概要

## 2.1 ブロック図

図 2-1. カメラのブロック図

## 2.2 設計上の考慮事項

以下のサブセクションでは、システムの各サブセクションの設計について説明します。

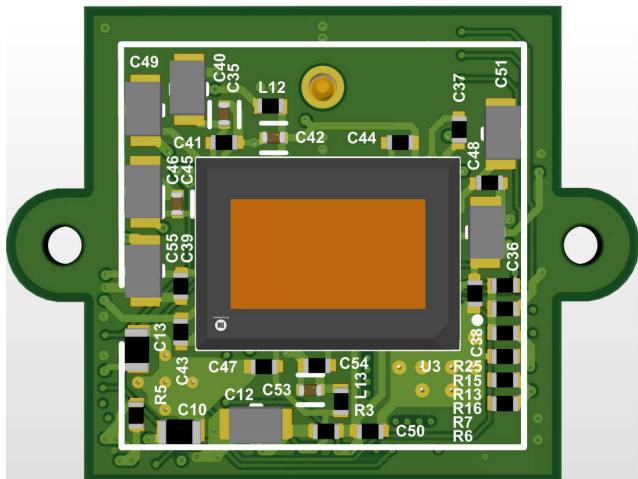

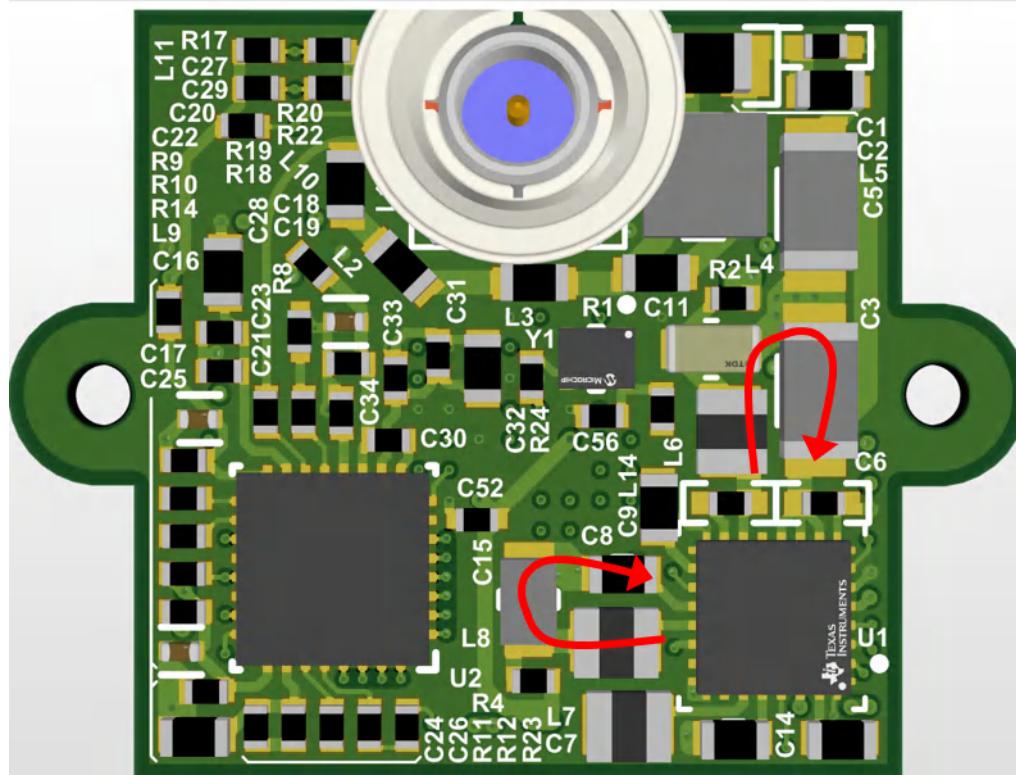

### 2.2.1 PCB とフォーム ファクタ

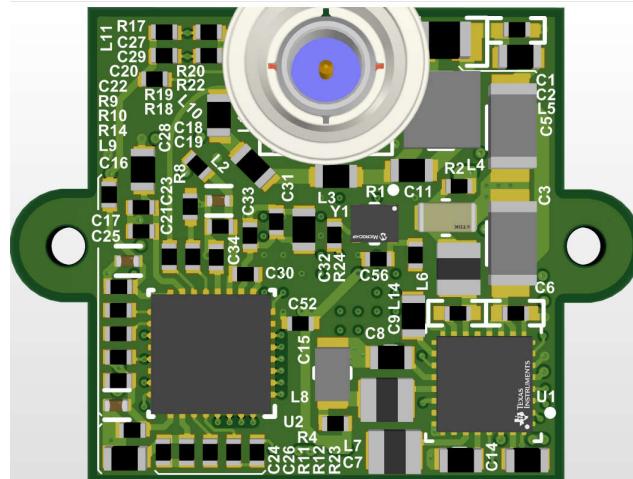

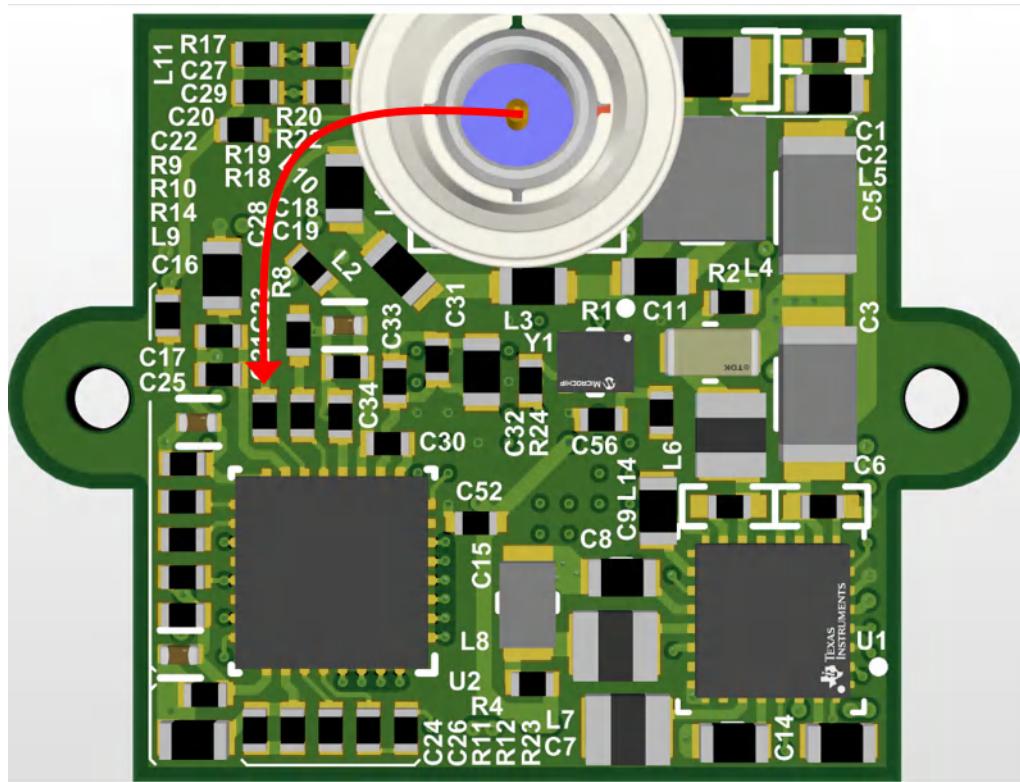

このリファレンス デザインは、特定のフォーム フактаに適合させることを目的としたものではありません。しかし、設計の目的は、PCB 面積を最小限に抑えたコンパクトなソリューションを示すことにあります。基板の面積はおよそ 20mm×20mm の寸法に相当します。図 2-2 の基板端付近の領域は、レンズを保持する光学系ハウジングを取り付けるために予約されています。

図 2-2. 3D PCB 上面図

図 2-3. 3D PCB 底面図

## 2.2.2 電源の設計

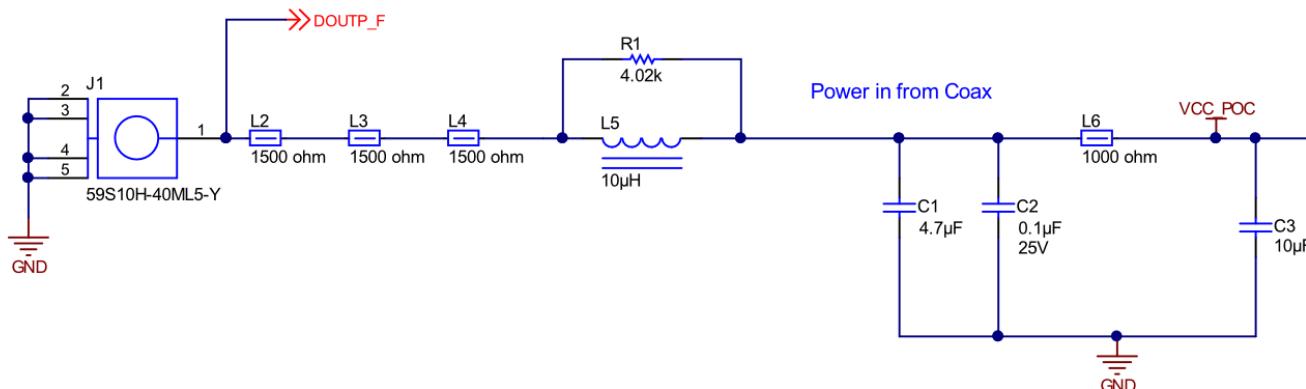

### 2.2.2.1 POC フィルタ

POC を使用する設計の最も重要な部分の 1 つはフィルタ回路です。目標は 2 つあります。

1. スイッチング レギュレータの入力にクリーンな DC 電源を供給する。

2. システムの他の部分から、ノイズ結合された逆方向から FPD-Link 通信チャネルを保護する。

このシステムで使用されている DS90UB953-Q1 および DS90UB960-Q1 SerDes デバイスは、2 つのキャリア周波数、2GHz でフルスピード（「フォワード チャネル」）、およびデシリアライザ デバイスによって決定される低い周波数の 50MHz（「バック チャネル」）を介して通信を行います。フィルタは DC のみを通過するように、両方のキャリアにこのかなり大きな帯域を減衰させる必要があります。同軸ケーブル上でフォワード チャネルおよびバック チャネルの信号を途切れなく通すためには、25MHz~2GHz の帯域において  $2k\Omega$  以上のインピーダンスが必要です。この目標を達成するために、通常は 25MHz~1GHz の範囲をフィルタリングするためにインダクタを選択し、1~2GHz の周波数帯域をフィルタリングするためにフェライトビーズを選択します。このフィルタ全体を、図 2-4 に L2 で示します。L1 は同じですが、そ POC フィルタは FPD-Link III 送信のデシリアライザ側用です。このカメラ設計では、POC フィルタのフットプリントをできるだけ小さくすることが非常に重要です。これを実現するために、10MHz ~ 1GHz までフィルタリングする広帯域インピーダンスを備えた LQH3NPZ100MJRL  $10\mu\text{H}$  インダクタを選択しています。これにより、低周波数用と高周波数用の 2 つのインダクタを通常必要とするソリューションは不要です。

高周波順方向チャネル フィルタリングを実現するために、このリファレンス デザインでは、3 個のフェライトビーズを  $10\mu\text{H}$  インダクタと直列に接続し、 $1.5k\Omega$  より上のインピーダンスを、1GHz ~ 2GHz の範囲全体で  $2k\Omega$  より上のインピーダンスにしています。このデザインは 3 個の  $1.5k\Omega$  フェライトビーズを使用しています。これは、動作時に、これらのデバイスを流れる電流が実効インピーダンスを小さくするためです。そのため、2 個ではなく 3 個のフェライトビーズを使用すると、周波数帯域全体にわたってヘッドルームが大きくなります。適切な測定を行うために、このデザインでは  $4-k\Omega$  抵抗を  $10-\mu\text{H}$  インダクタと並列に使用し、周波数帯域全体にわたって一定のインピーダンスを確保して、インピーダンスを平滑化します。この手法を使用すると、PoC インダクタのフィルタリング用に、オンボードのソリューション サイズを最小化できます。詳細については、[DS90UB953-Q1 用 Power-over-Coax 設計ガイドライン アプリケーション レポート](#)を参照してください。

最後に、フィルタリングに関しては、クリーンでノイズのない DC 電源をシステムに供給する場合と同様に、FPD-Link 信号が中断されないようにすることも重要です。これを実現するために、 $0.033\mu\text{F}$  および  $0.015\mu\text{F}$  の AC 結合コンデンサを使用しています。これにより、高速な AC データ信号は通過しますが、DC がデータ ラインに流れ込むのを防ぎます。バック チャネル速度の向上により、DS90UB953-Q1 および DS90UB954-Q1 デバイスでは、従来世代よりも小さい容量のコンデンサを使用することが可能になりました。

図 2-4. PoC (Power Over Coax: 同軸ケーブルを介した電源供給)

### 2.2.2.2 電源に関する考慮事項

このリファレンス デザインは車載を対象としているため、設計上の選択肢を制限するいくつかの要件があります。また、以下に示すシステム レベルの仕様を示すことで、最終的な設計全体の形成に役立ちました：

- この設計では、20mm × 20mm というサイズ要件を満たすために、ソリューション全体のサイズを最小化する必要があります。つまり、外付け回路を不要にするため、FET、ダイオード、補償ネットワーク、帰還抵抗分圧器などを統合した部品を選定する必要があります。

- AM ラジオ帯への干渉を避けるため、すべてのスイッチング周波数は 1700 kHz より高いか、540 kHz より低く設定する必要があります。この場合、低いスイッチング周波数は好ましくありません。大きなインダクタが必要になるうえ、依然として AM 帯に高調波ノイズを発生させるおそれがあるためです。このリファレンス デザインでは高い周波数のスイッチャに注目します。

- すべてのデバイスは AEC-Q100 (-Q1) 認定を受けている必要があります。

部品を選定する前に、入力電圧範囲、必要な電圧レール、および各レールに必要な電流を把握しておく必要があります。この場合、入力電圧は同軸ケーブル経由で供給される事前調整済みの 12V 電源です。このシステムには、イメージ ヤとシリアル アイザという 2 つの主要なデバイスがあり、これらが動作中の電力消費を担当します。表 2-1 に、電源の要件を示します：

表 2-1. システム電力バジェット

| パラメータ            | 電圧 (V) | 電流 (mA) | 電力 (mW) |

|------------------|--------|---------|---------|

| <b>DS90UB953</b> |        |         |         |

| VDD              | 1.8    | 225     | 405     |

| <b>AR0820</b>    |        |         |         |

| VDD -D           | 1.2    | 217     | 260     |

| VDD-IO           | 1.8    | 4       | 7       |

| VDD-A            | 2.8    | 141     | 395     |

| <b>発振器</b>       |        |         |         |

| VDD              | 1.8    | 3       | 5       |

| <b>合計</b>        |        |         |         |

| VDD -D           | 1.2    | 217     | 260     |

| VDD-IO           | 1.8    | 232     | 418     |

| VDD-A            | 2.8    | 141     | 395     |

同軸ケーブルを通して供給される 12V 電源は、まず 3.3V に降圧され、その後カメラ モジュール内の他の回路に電力を供給します。この設計では、1.8V レールが DS90UB953 の電源および AR0820 イメージャのインターフェイス電源の両方に供給されています。AR0820 の 2.8V アナログ レールには 141 mA、DS90UB953 シリアル アイザの 1.8 V レールには 225mA、そして AR0820 の 1.2V デジタル レールには 217mA が必要です。

計算を簡略化するため効率を 85% と仮定すると、1.2V、1.8V、および 2.8V の各レールを適切に動作させるために、3.3V 電源では約 124mA が必要と算出されます。入力および出力電圧、出力電流の要件、総ワット数が判明しているため、式 1 を使用して入力電流を計算します。

$$\begin{aligned}

P_{IN} &= V_{IN} \times I_{IN} = \frac{P_{OUT}}{\eta_{SYSTEM}} = \frac{\frac{P_{OUT2}}{\eta_2} + \frac{P_{OUT3}}{\eta_3} + \frac{P_{LDO}}{\eta_{LDO}}}{\eta_1} \\

\therefore I_{IN} &= \frac{\frac{260 \text{ mW}}{85\%} + \frac{418 \text{ mW}}{85\%} + \frac{395 \text{ mW}}{85\%}}{12 \text{ V} \times 85\%} = 124 \text{ mA}

\end{aligned} \tag{1}$$

この情報は、後の章で説明される電源トポロジおよびインダクタ系受動部品の選定において、重要な基礎となります。

Q100 認定の要件により、スイッチング周波数は AM 帯域外で設定されることが義務づけられており、さらに前述の電圧および電流要件を満たす必要があります。入力電圧は常に生成される各電圧レールより高い安定化電圧であるため、選択すべき電源トポロジーは降圧コンバータ (降圧) または LDO のいずれかになります。降圧コンバータは一般に、スイッチング ノイズが大きな懸念とならない電源に採用され、消費電力削減が最も重要な関心事です。一方で、LDO は低ノイ

ズのアナログ電源を構築する際に有効で、内部ノイズを低減し、EMI に対してもより強固になります。ただし、その分電流消費が大きくなるという欠点があります。

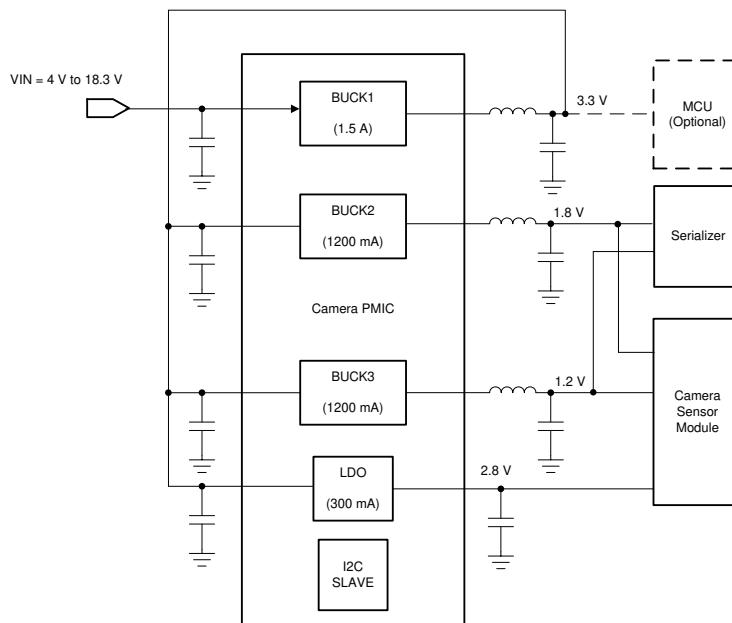

この設計では、1 つのパワー マネージメント IC が電源レールへの電力供給を行います。このデバイス TPS650330-Q1 は、3 つの降圧コンバータ (BUCKS) と 1 つの LDO を、4.0mm × 4.0mm の VQFN パッケージに統合しているため選定されました。設計の電流要件もデバイス選定において重要な役割を果たしました。セカンダリの降圧コンバータ (BUCKS) は 1200 mA の供給が可能であり、一方 LDO は最大 300 mA の出力電流を供給できます。BUCK1 は 12V の POC 入力を 3.3V に降圧します。3.3V レールはその後、BUCK2、BUCK3、および LDO の入力に電力を供給します。BUCK2 は、AR0820 イメージャおよび DS90UB953 シリアライザのインターフェイス電源およびデジタル電源を供給します。一方、LDO 出力は AR0820 用の 2.8V アナログ電源として、クリーンで低ノイズな電源を生成します。

### 2.2.2.2.1 外付け部品の選択

単純化するため、これらの動作条件における降圧レギュレータの効率は 85% と仮定し、LDO の効率は 式 2 によって示されます。

$$\eta_{LDO} = \frac{V_{OUT}}{V_{IN}} \quad (2)$$

スイッチング レギュレータの効率を 85% と仮定して計算されたシステムおよび降圧 1 の電流を 式 1 に示します。

表 2-2 に、カメラ モジュールの要件と比較した各レギュレータの負荷能力を示します。TPS650330-Q1 デバイスは、標準値および最大値変動との変動に対応するため、十分なマージンを確保してシステム電力を供給することができます。

表 2-2. レギュレータの負荷能力

| 規制     | 出力電圧 (V) | 最大電流 (mA) | 必要な電流 (mA) |

|--------|----------|-----------|------------|

| Buck 1 | 3.3      | 1500      | 383        |

| Buck 2 | 1.8      | 1200      | 232        |

| Buck3  | 1.2      | 1200      | 217        |

| LDO    | 2.8      | 300       | 141        |

電力要件に基づいて TPS650330-Q1 デバイスが適切であることを判定すると、データシートの推奨事項に基づいて外付け部品を素早く選択し、設計プロセスを簡素化できます。これらの推奨事項は、図 2-5 および 表 2-3 で参照できます。

図 2-5. TPS650330-Q1 の代表的なアプリケーション回路

**表 2-3. TPS650330-Q1 の推奨部品**

| 部品                       | 説明                                              | 値   | 単位 |

|--------------------------|-------------------------------------------------|-----|----|

| C <sub>VSYS,VSYS_S</sub> | V <sub>SYS</sub> および V <sub>SYS_S</sub> デカップリング | 10  | μF |

| C <sub>PVIN_B1</sub>     | 降圧 1 入力コンデンサ                                    | 10  | μF |

| L <sub>SW_B1</sub>       | 降圧 1 インダクタ                                      | 1.5 | μH |

| C <sub>OUT_B1</sub>      | 降圧 1 出力コンデンサ                                    | 10  | μF |

| C <sub>PVIN_B2</sub>     | 降圧 2 入力コンデンサ                                    | 10  | μF |

| L <sub>SW_B2</sub>       | 降圧 2 インダクタ                                      | 1.0 | μH |

| C <sub>OUT_B2</sub>      | 降圧 2 出力コンデンサ                                    | 10  | μF |

| C <sub>PVIN_B3</sub>     | 降圧 3 入力コンデンサ                                    | 10  | μF |

| L <sub>SW_B3</sub>       | 降圧 3 インダクタ                                      | 1.0 | μH |

| C <sub>OUT_B3</sub>      | 降圧 3 出力コンデンサ                                    | 10  | μF |

| C <sub>PVIN_LDO</sub>    | LDO 入力コンデンサ                                     | 1.0 | μF |

| C <sub>OUT_LDO</sub>     | LDO 出力コンデンサ                                     | 2.2 | μF |

### 2.2.2.2.2 降圧 1 インダクタの選択

インダクタンス値 1.5μH を選択した場合、設計に適切なインダクタを選択するために、最小インダクタ飽和電流を求めなければなりません。これは、定常状態の電源電流とインダクタのリップル電流の組み合わせです。大電力のイメージセンサに対して、電源とシリアルライザのベースボードの柔軟性を確保できるように、レギュレータの各最大定格出力電流に基づいてインダクタを選択します。式 3 はインダクタのリップル電流を計算します：

$$\Delta I_{L(max)} = V_{OUT} \times \left( 1 - \frac{V_{OUT}}{V_{IN(max)}} \right) \times \frac{1}{L_{(min)} \times f_{sw}} \quad (3)$$

ここで、

- $\Delta I_{L(max)}$  は、ピークツーピーク インダクタリップル電流の最大値

- $L_{(min)}$  は実効インダクタ値の最小値

- $f_{sw}$  は実際の PWM スイッチング周波数

このリファレンス デザインの降圧 1 のパラメータは次のとおりです。

- $V_{OUT} = 3.3V$

- $V_{IN(max)} = 18.3V$

- $L_{(min)} = 1.5\mu H$

- $f_{sw} = 2.3MHz$

これらのパラメータから、 $\Delta I_L = 784mA$  のインダクタリップル電流が得られます。最大負荷電流が 1500mA と仮定すると、式 4 を使用して 1900mA の最小飽和電流を計算します。

$$L_{SAT} \geq I_{OUT, (MAX)} + \frac{\Delta I_L(MAX)}{2} \quad (4)$$

この設計では TPS650330-Q1 デバイスを使用している TDK® TFM201610ALMA1R5MTAA は、定格電流が 2A、最大 DC 抵抗が 152mΩ です。また、このインダクタは 55°C から 150°C までの範囲の動作温度を 2.0mm × 1.6mm の超小型パッケージで実現します。

### 2.2.2.2.3 降圧 2 および降圧 3 インダクタの選択

降圧 2 および降圧 3 の推奨インダクタ値は 1.0μH です。部品を選択する際は、DC 抵抗と飽和電流を検証することが重要です。インダクタンスの DC 抵抗はコンバータの効率に直接影響を及ぼします。DC 抵抗の低い値は効率に正比例します。インダクタの飽和要件は、定常状態の電源電流とインダクタリップル電流を組み合わせることで決定されます。インダ

クタの物理的なサイズを小さくするために、電流定格は十分に高くしていますが、できるだけ小さくする必要があります。インダクタのリップル電流は、式 3 を使って計算されます。

降圧 2 1.8V レールのパラメータは次のとおりです：

- $V_{OUT} = 1.8V$

- $V_{IN(max)} = 3.3V$

- $L_{(min)} = 1.0\mu H$

- $f_{sw} = 2.3MHz$

これらのパラメータから、 $\Delta I_L = 356mA$  のインダクタリップル電流が得られます。最大負荷電流が 1200mA と仮定すると、式 4 を使用でき 1400mA の最小飽和電流を計算します。

降圧 3 1.2V レールのパラメータは次のとおりです：

- $V_{OUT} = 1.2V$

- $V_{IN(max)} = 3.3V$

- $L_{(min)} = 1.0\mu H$

- $f_{sw} = 2.3MHz$

これらのパラメータから、 $\Delta I_L = 332mA$  のインダクタリップル電流が得られます。最大負荷電流が 1200mA と仮定すると、式 4 を使用でき 1400mA の最小飽和電流を計算します。

このリファレンス デザインの降圧 2 と降圧 3 では、定格電流が 3.1A、DC 抵抗が 60mΩ の TDK® TFM201610ALMA1R0MTAA を使用しています。また、このインダクタは 55°C から 150°C までの範囲の動作温度を 2.0mm × 1.6mm の超小型パッケージで実現します。

### 2.2.2.3 機能安全

TPS650330-Q1 デバイスには、温度および電流監視に加えてスーパーバイザが内蔵されています。このデバイスは、TPS650331-Q1、TPS650332-Q1、および TPS650333-Q1 ともピン互換性があります。TPS650331-Q1、TPS650332-Q1、TPS650333-Q1 の各デバイスは、ASIL-B 安全性要素 (SEooC) としての追加の安全機能を備えているため、機能安全要件を持つカメラ アプリケーションに対してこのデザインを拡張できます。

## 2.3 主な使用製品

このリファレンス デザインは、次の TI 製品を使用しています。

- DS90UB953-Q1: チップセットのシリアルアイザ部分で、FPD-Link III インターフェイスを搭載しており、1 本の同軸ケーブルまたは差動ペア ケーブルで、高速順方向チャネルおよび双方向制御用チャネルのデータを転送します。このチップセットには高速の順方向チャネルと、双方向制御チャネル データ パスの両方の差動信号処理回路が組み込まれています。シリアルアイザとデシリアルアイザのペアは、電子制御ユニット(ECU)内のイメージャとビデオ プロセッサ間の接続を目的としています。

- TPS650330-Q1: 車載認証済み、カメラ アプリケーション用に最適化された 4 チャネル PMIC です。このデバイスは、3 つの降圧コンバータと 1 つの LDO を内蔵し、各電圧レールに過電圧保護および低電圧監視機能を備えています。PWM 2.3MHz の高い固定スイッチング周波数により、小型のインダクタを使用でき、高速過渡応答を実現できます。低ノイズ、高 PSRR LDO は、敏感なアナログ回路用に出力電圧オプションを備えています。幅広い出力電圧やシーケンス設定に加え、その他の動作設定もプログラム可能で、追加の部品を必要とせず、さまざまなイメージ センサとの互換性を実現します。

### 2.3.1 AR0820 イメージャ

Onsemi® AR0820 は、対角 9.25 mm、1/2 型の CMOS イメージ センサで、有効画素数は 8.3 メガピクセルです。このセンサは 12 ビット ADC を内蔵しており、MIPI 4 レーン接続に対応しています。RAW12 から RAW24 までの HDR 出力をサポートします。その他の機能：

- 最大 40fps で 3840 × 2160 (8.3MP) の解像度をサポート

- ASIL-B 準拠をサポートする故障検出

- 複数のカメラの同期のサポート

- 3 つの電圧レール (2.8V、1.8V、1.2V) が必要

- I<sup>2</sup>C 互換の 2 線式シリアル インターフェイスを使用して構成可能

8 車載対応、PMIC と FPD-Link III 搭載、8.3MP の POC カメラ モジュールのリファレンス デザイン

JAJU859 – AUGUST 2022

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 2.3.2 DS90UB953-Q1

シリアルアイザを使用して、12 ビットビデオと双方向制御信号を 1 本の同軸またはツイストペア上に結合することで、システムの複雑さ、コスト、ケーブル配線の要件を大幅に簡素化できます。DS90UB953-Q1 の CSI-2 入力は、AR0820 イメージャの MIPI CSI-2 ビデオ出力と適切に接続できます。PoC 用のフィルタと組み合わせることで、映像、I2C 制御、診断信号、電力をすべて、1 本の安価な同軸ケーブルで最大 15 メートルまで伝送できます。

### 2.3.3 TPS650330-Q1

TPS650330-Q1 デバイスは、車載カメラ モジュール向けの高集積パワー マネージメント IC です。このデバイスは、3 つの降圧コンバータと 1 つの低ドロップアウト (LDO) レギュレータを組み合わせたものです。BUCK1 降圧コンバータは最大 18.3V の入力電圧に対応し、Power Over Coax (POC) と接続できます。すべてのコンバータは、強制固定周波数 PWM モードで動作します。この LDO は 300mA を供給することができ、3.0V ~ 5.5V の入力電圧範囲で動作します。これらの降圧コンバータと LDO は個別の電圧入力を使用しており、設計とシーケンシングで最大のフレキシビリティを実現できます。さらに、内蔵の高度な拡散スペクトラム クロック (SSC) により、堅牢な EMI 性能が可能です。小型フォーム ファクタに加え、電源レール監視機能やプログラマビリティが追加されたことで、このデバイスは、迅速な設計や将来のアプリケーションへの拡張が求められる用途に非常に適した候補となっています。

## 2.4 システム設計理論

車載カメラに関して設計時に考慮する必要のある主な課題は、サイズ、使いやすさ、熱効率です。車載カメラは多くの場合、面積が限られている自動車の遠隔領域に配置するので、全体的な小型ソリューションが必要になります。そのため、システムは部品点数を最小限に抑えながら、完全統合型 PMIC 電源ソリューションを実現するように設計されています。PMIC ソリューションがもたらす使いやすさと設計の柔軟性も、単一プラットフォーム設計を実現し、ADAS アプリケーションの拡大に伴う開発時間を短縮するうえで重要な要素です。DS90UB953-Q1 と TPS650330-Q1 は、さらに多様なイメージャとの互換性も備えています。最後に、これらのカメラはサイズが小さく、離れた場所に配置できることから、熱に対する感受性が高くなります。こうした条件下で画質を維持するには、電力効率の優れたシステムが不可欠です。TPS650330-Q1 デバイスは、3 つの降圧および 1 つの LDO レギュレータトポロジで効率を重視して最適化されており、熱性能を犠牲にせずに中品質から高品質のイメージャをサポートできます。熱はシステム性能に影響するため、設計プロセスの一環としてシステム全体の効率を計算することが重要です。表 2-2 の降圧 1 出力電源から、TPS650330-Q1 の効率は約 90% です。この値を用いて、式 5 ではシステムの入力電力がおよそ 1.4W と算出されています。次に、式 5 を使用して Buck 2、Buck 3、および LDO の出力電力から、システム全体の効率を算出できます。

$$\eta_{SYSTEM} = \frac{P_{OUT}}{P_{IN}} = \frac{(P_{OUT,2} + P_{OUT,3} + P_{OUT,LDO})}{P_{IN,1}} = 75\% \quad (5)$$

### 3 ハードウェア、テスト要件、およびテスト結果

#### 3.1 ハードウェア要件

図 3-1 に示すように、このリファレンス デザインでは、FAKRA コネクタを介して互換性のあるデシリアルライザを使用してシステムを 1 つ接続するだけで済みます。

図 3-1. ボードの使用を開始

##### 3.1.1 ハードウェア設定

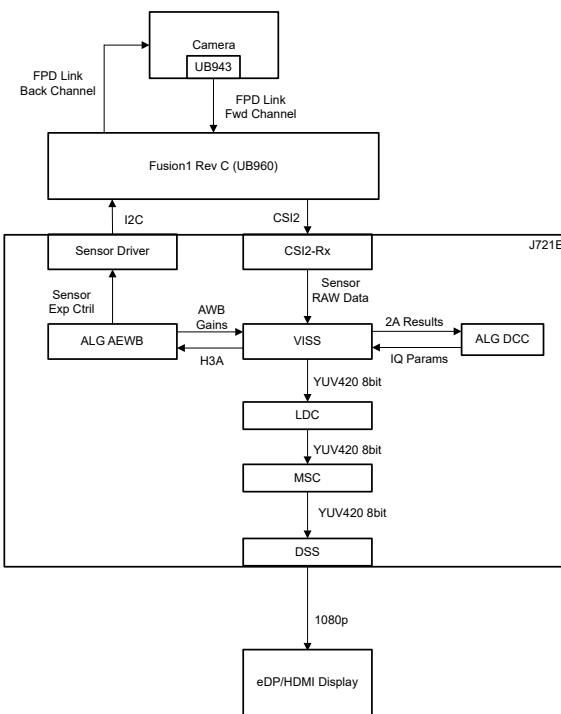

図 3-2 に、カメラ モジュールのリファレンス デザインをテストするための構成を示します。このデザインは、CSI-2 と I<sup>2</sup>C の各インターフェイスを経由して DS90UB953-Q1 シリアライザに接続する AR0820 イメージ センサを搭載しています。次に、DS90UB953-Q1 シリアライザは、POC 経由で DS90UB960-Q1 デシリアルライザに接続します。テストの設定では、DS90UB960-Q1 デバイスから 1 つのチャネルのみを使用することに注意します。

DS90UB960-Q1 デバイスからビデオ出力を行うために、デシリアルライザである Fusion1 Rev C アプリケーション ボードを Jacinto 7 EVM に接続します。この EVM を使用すると、AR0820、DS90UB953-Q1、DS90UB960-Q1 デバイスのすべてのバック チャネル I<sup>2</sup>C 設定構成を書き込み、ビデオ出力を可能にします。これらの書き込みが完了すると、Vision SDK ソフトウェアは DisplayPort 接続モニタへのビデオ出力を有効にします。

図 3-2. テスト設定

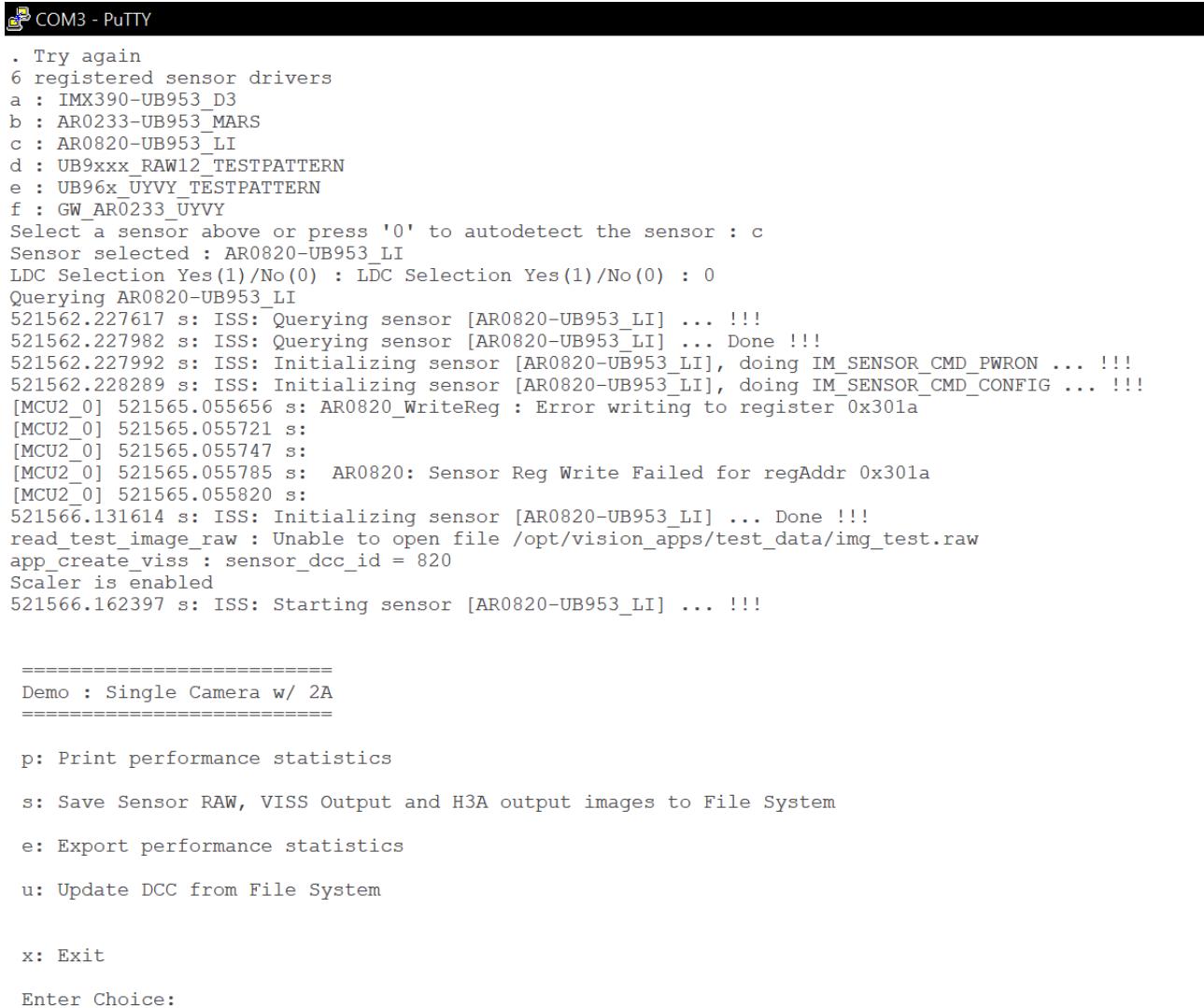

### 3.1.2 FPD-Link III I<sup>2</sup>C の初期化

図 3-2 の構成を接続した状態では、DS90UB960-Q1 デシリアライザを搭載した Fusion1 ボードに 12V の入力電源が供給されます。この電力は POC を介して伝送され、TIDA-050051 カメラ モジュールに電力を供給します。すべてのレベルが確立されると、初期化のための I<sup>2</sup>C 書き込みを開始できます。これらの書き込みは、Jacinto 7 プロセッサ ソフトウェア開発キット (SDK) で利用できる単一のカメラ アプリケーションの使用事例で実行されます。詳細については、[EVM](#) および [SDK ツール ページ](#)をご覧ください。

```

COM3 - PuTTY

. Try again

6 registered sensor drivers

a : IMX390-UB953_D3

b : AR0233-UB953_MARS

c : AR0820-UB953_LI

d : UB9xxx_RAW12_TESTPATTERN

e : UB96x_UYVY_TESTPATTERN

f : GW_AR0233_UYVY

Select a sensor above or press '0' to autodetect the sensor : c

Sensor selected : AR0820-UB953_LI

LDC Selection Yes(1)/No(0) : LDC Selection Yes(1)/No(0) : 0

Querying AR0820-UB953_LI

521562.227617 s: ISS: Querying sensor [AR0820-UB953_LI] ... !!!

521562.227982 s: ISS: Querying sensor [AR0820-UB953_LI] ... Done !!!

521562.227992 s: ISS: Initializing sensor [AR0820-UB953_LI], doing IM_SENSOR_CMD_PWRON ... !!!

521562.228289 s: ISS: Initializing sensor [AR0820-UB953_LI], doing IM_SENSOR_CMD_CONFIG ... !!!

[MCU2_0] 521565.055656 s: AR0820_WriteReg : Error writing to register 0x301a

[MCU2_0] 521565.055721 s:

[MCU2_0] 521565.055747 s:

[MCU2_0] 521565.055785 s: AR0820: Sensor Reg Write Failed for regAddr 0x301a

[MCU2_0] 521565.055820 s:

521566.131614 s: ISS: Initializing sensor [AR0820-UB953_LI] ... Done !!!

read_test_image_raw : Unable to open file /opt/vision_apps/test_data/img_test.raw

app_create_viss : sensor_dcc_id = 820

Scaler is enabled

521566.162397 s: ISS: Starting sensor [AR0820-UB953_LI] ... !!!

=====

Demo : Single Camera w/ 2A

=====

p: Print performance statistics

s: Save Sensor RAW, VISS Output and H3A output images to File System

e: Export performance statistics

u: Update DCC from File System

x: Exit

Enter Choice:

```

図 3-3. シングル カメラ アプリケーションの初期化

### 3.1.3 AR0820 の初期化

DS90UB953-Q1 と DS90UB960-Q1 デバイスの FPD-Link III 設定が完了したら、AR0820 上で I<sup>2</sup>C 初期化を行うことができます。これらの書き込みについては、レジスタ設定について AR0820 のデータシートを参照してください。イメージやおよび ISP を構成するための多数のレジスタ設定が一覧に示されていますが、DS90UB953-Q1 と DS90UB960-Q1 の FPD-Link III が設定されていれば、I<sup>2</sup>C バックチャネルを介してアドレス 0x10 の AR0820 にアクセスできます。このテストでは、AR0820 を 3840 × 2160 解像度の RAW12 HDR 出力に設定しています。

## 3.2 テスト設定

電源と I<sup>2</sup>C 通信を検証するための以下のテストでは、図 3-2 に示すように、カメラを Fusion アプリケーション拡張カードと Jacinto 7 EVM に接続しています。

### 3.2.1 電源の起動

電源のシーケンシングと起動動作を確認するために、TPS650320-Q1 デバイスからの各電圧レール出力を、同軸ケーブルを介してシステムに電力を供給した後で測定しました。

この設計では、DS90UB953-Q1 デバイスの PDB リセット信号が、TPS650330-Q1 デバイスの nRSTOUT ピンに直接接続されています。PMIC の内蔵シーケンシング機能により、1.8-V 電源が安定した後に PDB リセットラインが確実に High になるため、外部 RC ネットワークが不要になります。

### 3.2.2 カメラの機能

バック チャネル I2C 通信は、Jacinto 7 EVM ヘシリアル接続で検証済みです。DisplayPort 互換モニタを使用して、ビデオ ストリームと画質を検証します。

## 3.3 テスト結果

以下のセクションでは、カメラ設計の機能を検証したテスト データを示します。

### 3.3.1 電源の起動

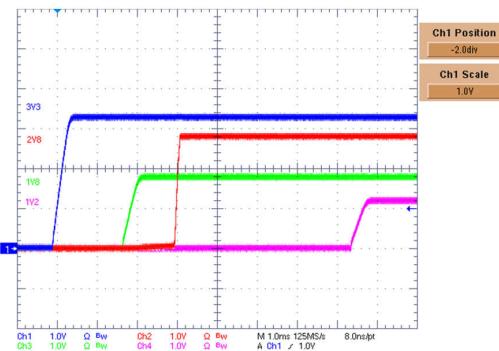

図 3-4 は、3.3 V、1.8 V、1.2 V、および 2.8 V レールの起動動作を示しています。

(チャネル 1):3.3V 電源、(チャネル 2):2.8V 電源、(チャネル 3):1.8V 電源、(チャネル 4):1.2V 電源

図 3-4. ポイントオブ ロード電源の起動

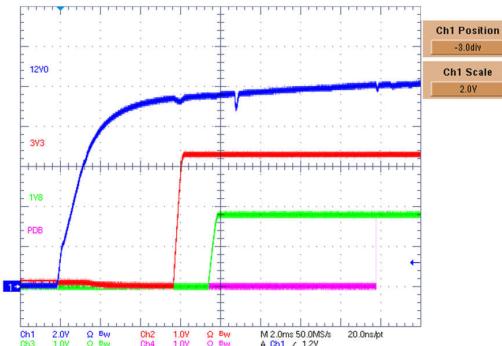

### 3.3.2 電源の起動—1.8V レールおよび PDB

適切に初期化するには、すべての電源が最終的な電圧まで安定するまで、シリアルアイザの PDB ピンは low に維持されます。図 3-5 に、電源の起動を示します。TPS650320-Q1 デバイスの RSTOUT に PDB ピンを直接接続し、すべてのレールが確立された後で PDB を適切に同期できるようにすることに注意します。

(チャネル 1):12V 電源、(チャネル 2):3.3V 電源、(チャネル 3):1.8V 電源、(チャネル 4):PDB

図 3-5. シリアライザ パワーアップ シーケンス

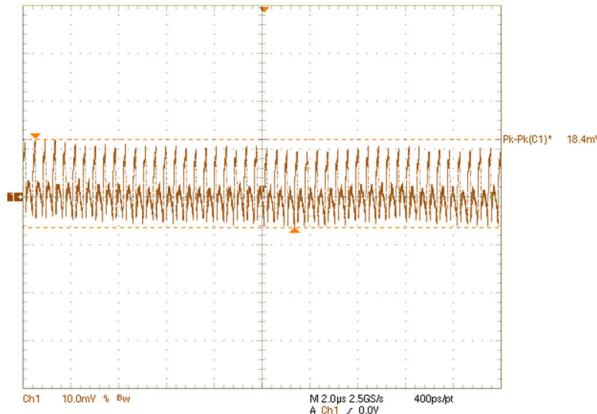

### 3.3.3 電源電圧リップル

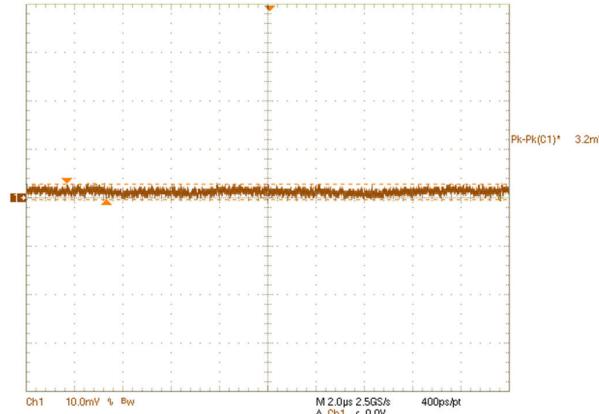

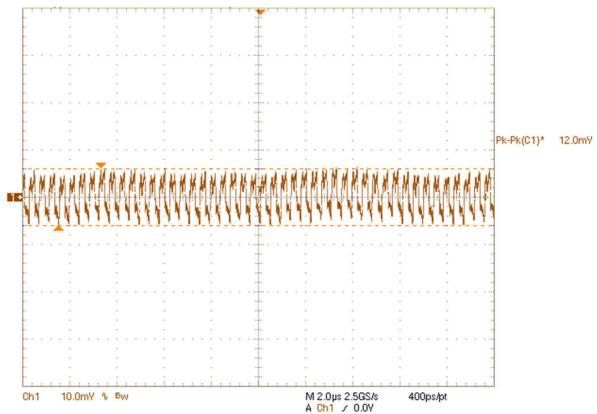

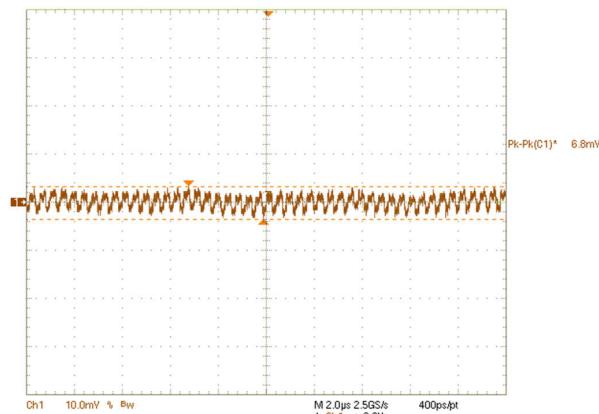

高品質の出力ビデオストリームを実現するには、AR0820 および DS90UB953-Q1 電源の出力電圧リップルが高速データおよび内部 PLL クロックの整合性に影響を与えないように Low にする必要があります。3.3V、2.8V、1.8V、1.2V レールの測定値を、図 3-6、図 3-7、図 3-8 にそれぞれ示します。イメージャの性能に影響を与えるのは、2.8V レールと 1.2V レールです。これらはそれぞれ、クリーンなアナログ電源とデジタル電源を供給する役割を担っています。3.3V レールは、システム全体に電力を供給するとともに、0.5% の優れたリップル性能も備えています。測定によると、2.8V レールと 1.2V レールのリップル性能はそれぞれ 0.1% と 0.6% です。1.8V レールは VDD および VDD\_PLL レールに電力を供給するため、シリアルライザにとって重要です。1.8V レールは、0.7% という優れた電圧リップル性能を備えています。すべてのレールの電圧リップルは、ビデオ出力が正常に送信されるには十分に低い値です。

図 3-6. 出力電圧リップル - 3.3V

図 3-7. 出力電圧リップル - 2.8V

図 3-8. 出力電圧リップル - 1.8V

図 3-9. 出力電圧リップル - 1.2V

### 3.3.4 電源負荷電流

カメラモジュールの電源に関して最後に測定すべき項目は、システム全体の電源レールに対する負荷電流と、AR0820イメージャの各レールにかかる負荷電流です。これらの測定により、AR0820イメージャ上のカメラモジュールの合計消費電力と各レールの負荷電流を確認できます。以下の試験データでは、各電源レールがシリアルアイザおよびイメージャに指定された負荷電流をそれぞれ消費しています。すべての負荷電流測定は、ビデオ出力ストリームが存在している間に行われます。

このリファレンスデザインの [表 3-1](#) には、各電源電圧における電流の測定結果が示されています。12V レールの負荷電流は、カメラモジュール全体の総入力電流であり、測定値は 107 mA です。総消費電力から算出されるシステム全体の効率は 70% であり、[セクション 2.4](#) で得られた 75% という値に近い結果となっています。この差は、想定よりも動作電流が小さかったことに加え、POC ケーブルおよびフィルタ内での伝導損失によるものと考えられます。

**表 3-1. 消費電流の測定結果**

| 電圧レール | 測定電流( |

|-------|-------|

| 12V   | 103mA |

| 3.3V  | 320mA |

| 2.8V  | 120mA |

| 1.8V  | 193mA |

| 1.2V  | 155mA |

### 3.3.5 D ビデオ出力

3840 x 2160 の解像度と 27fps で動作しているときのカメラモジュールからの出力フレームを示します。出力フォーマットは 8 ビット YUV420 です。

**図 3-10. TIDA-050051 ビデオ出力**

## 4 設計とドキュメントのサポート

### 4.1 デザインファイル

#### 4.1.1 回路図

回路図をダウンロードするには、[TIDA-050050](#) のデザインファイルを参照してください。

#### 4.1.2 部品表

部品表 (BOM) をダウンロードするには、[TIDA-050050](#) のデザインファイルを参照してください。

#### 4.1.3 PCB レイアウトに関する推奨事項

##### 4.1.3.1 レイアウトプリント

レイヤープロットをダウンロードするには、[TIDA-050050](#) のデザインファイルを参照してください。

##### 4.1.3.2 PMIC レイアウトに関する推奨事項

レイアウトの PMIC 部分では、PCB の面積とノイズの両方を最小限に抑えるため、慎重に考慮する必要があります。車載用システムで EMI は重要な問題であり、TPS650330-Q1 デバイスには拡散スペクトラム機能があり伝導および放射妨害波を低減できるため、スペースに制約のあるアプリケーション向けに配置およびレイアウトに関する柔軟性が向上します。ただし、できるだけ多くのベストプラクティスに従うことをお勧めします。これには、降圧レギュレータの入力コンデンサ、インダクタ、出力コンデンサの間のスイッチング電流に起因する面積を最小限に抑える機能が含まれ、厳密な部品配置と、PMIC サーマルパッドへのリターンパスを最小限に抑えることが含まれます。図 4-1 は、降圧 1 および降圧 3 の例を示しています。

LDO の場合、入力コンデンサと出力コンデンサのグランドプレーンを分離すると、スイッチングレールからノイズ結合がノイズの影響を受けやすい 2.8V アナログレールへ低減されます。ノイズ結合をさらに低減するために、PMIC の専用 AGND ピンを、最上層のノイズの多いサーマルパッドに直接接続するのではなく、ビアを使用して内部層のグランドプレーンに接続しています。

図 4-1. PMIC PCB レイアウト

#### 4.1.3.3 シリアライザレイアウトに関する推奨事項

デカップリング コンデンサは、シリアルアイザの電源ピンのすぐ近くに配置する必要があります。ここでも、電源電流とリターン電流の経路を慎重に考慮する必要があります。この接続のループ面積を小さく保つことで、コンデンサの接続に関連する寄生インダクタンスを低減できます。スペースの制約があるため、理想的な配置が必ずしも可能とは限りません。シリアルアイザの反対面に配置されたデカップリング コンデンサについては、帰路をシリアルアイザのサーマル パッドまでできるだけ短くするようにします。高周波デカップリングを担う容量の小さいコンデンサは、デバイスのすぐ近くに配置します。

このアプリケーションでは、同軸相互接続に  $50\Omega$  のシングルエンド インピーダンスが必要です。DOUT の AC 結合コンデンサなど、重要な部品の下にあるグランド プレーンにはアンチパッドを設け、インピーダンスの不整合を最小限に抑えています。シリアルライザへの同軸接続は短くします。図 4-1 には、高速シリアル ラインの配線経路が赤線で示されています。赤色の線の全長は約  $1/2$  インチです。

高速データライン間のクロストークを最小限に抑えるため、隣接する層での高速データ配線が重ならないように設計します。スペースの制約でどうしても配線が重なる場合は、2つの配線層の間にグランド層を挟み、バッファとして配置します。高速信号のビアパターンを最小限に抑えます。理想的には、反射の原因となるタップを減らすため、ビアの数は2個以下に抑える必要があります。

図 4-2. 高速パターン配線

#### 4.1.3.4 イメージャレイアウトに関する推奨事項

高速データ配線は、先に示したシリアルライザのレイアウトに関するガイドラインと同じ規則に従う必要があります。同様に、デカッピング コンデンサは電源ピンのできるだけ近くに配置し、容量の小さいコンデンサを優先的にピンに近づけます。ピアと広いパターンで、グランド プレーンへの寄生抵抗およびインダクタンスを最小化します。一部のイメージでは、画像ノイズを低減するために、個別のアナログ グランド (AGND) プレーンを推奨します。イメージの AGND ピン、AVDD のデカッピング コンデンサ、および LDO 出力コンデンサを、この AGND プレーンに接続します。そして、このプレーンをメインのグランドに 1 点のみで接続します。

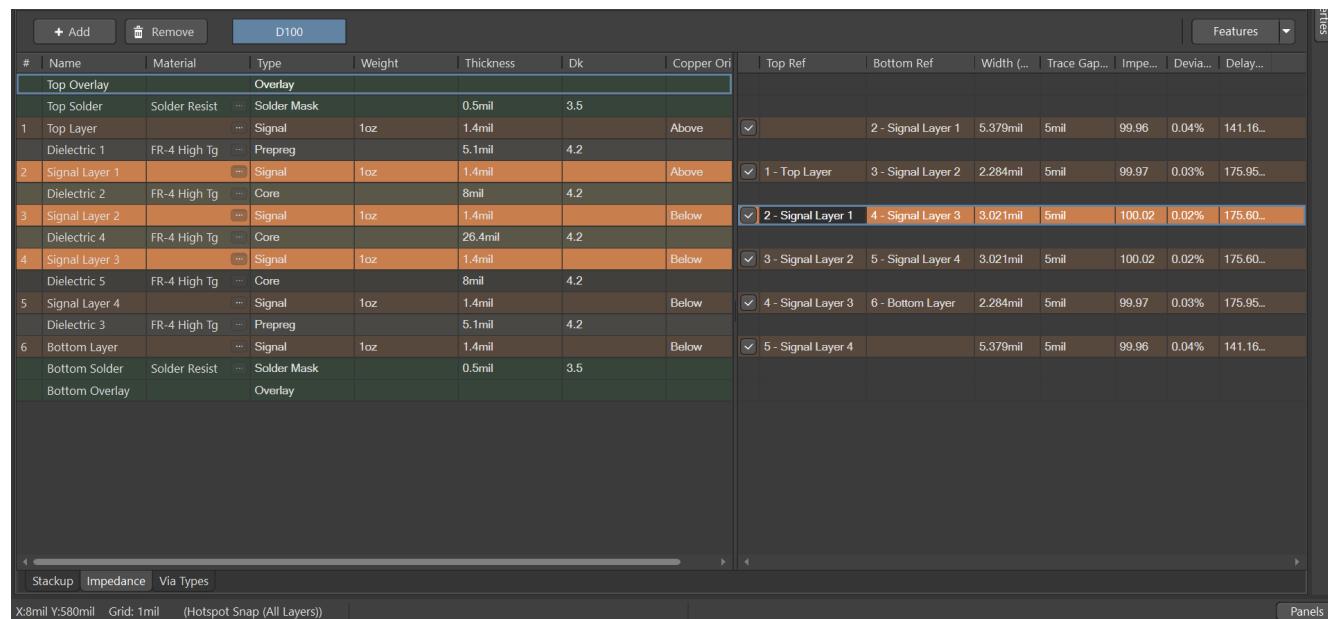

#### 4.1.3.5 PCB レイヤの積層に関する推奨事項

図 4-3 に、PMIC およびシリアルライザ基板で使用する 8 層のスタックアップを示します。この PCB は小型であるため、I2C、ロジック IO、クロック信号、PMIC、シリアルライザ、イメージヤ間の制御信号を含む複雑な配線が必要となり、その結果、2 層の信号層が必要になります。外部層の分離は、シングルエンド特性インピーダンスが  $50\Omega$ 、差動特性インピーダンスが  $100\Omega$  となるように選択されます。

この設計では、高電流部品が基板の表面層と裏面層の両方に配置されているため、スタックアップ内のレイヤ 2 およびレイヤ 7 をグラウドプレーン専用とし、高電流の帰路を最小限に抑えています。

図 4-3. 層のスタックアップ

#### 4.1.4 Altium プロジェクト

Altium プロジェクトファイルをダウンロードするには、[TIDA-050051](#) のデザインファイルを参照してください。

#### 4.1.5 ガーバーファイル

ガーバーファイルをダウンロードするには、[TIDA-050051](#) のデザインファイルを参照してください。

## 5 ドキュメントのサポート

1. テキサス インスツルメンツ、[TPS650330-Q1 EVM ユーザー ガイド](#)

2. テキサス インスツルメンツ、[DS90UB95x-Q1EVM デシリアライザユーザー ガイド](#)

3. テキサス インスツルメンツ、[DS90UB953-Q1 FPD-Link III シリアライザ、1MP / 60fps カメラ、10 / 12 ビット、100MHz 用データシート](#)

4. テキサス インスツルメンツ、[DS90UB953-Q1 用 Power-over-Coax 設計ガイドラインアプリケーション ノート](#)

5. テキサス インスツルメンツ、[カメラ PMIC スピニ選択ガイドアプリケーション ノート](#)

6. テキサス インスツルメンツ、[Jacinto7 J721E/DRA829/TDA4VM 評価基板ユーザー ガイド](#)

7. テキサス インスツルメンツ、[DRA829 および TDA4VM Jacinto™ プロセッサ向けソフトウェア開発キット](#)

## 6 サポート・リソース

[TI E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の [使用条件](#)を参照してください。

## 7 商標

テキサス・インスツルメンツの™ and TI E2E™ are trademarks of Texas Instruments.

TDK® is a registered trademark of TDK Electronics AG.

Onsemi® is a registered trademark of Omnipower Technologies Inc..

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月