## EVM User's Guide: TPSM828502QEVM-159

# TPSM82850x-Q1 車載用降圧コンバータ、評価基板

## 説明

TPSM82850x-Q1 デバイスは、ピン互換で 1A および 2A の、インダクタ内蔵の車載高効率同期整流降圧型 DC/DC パワー モジュールのファミリです。これらのデバイスは、固定周波数のピーク電流モード制御トポロジを使用します。これらのモジュールは、高電力密度と使いやすさが求められる車載アプリケーションで動作します。低抵抗スイッチにより、高い周囲温度でも最大 2A の連続出力電流を供給できます。

スイッチング周波数は、ピン ストラップにより 2.25MHz に固定、または設定抵抗により 1.8MHz ~ 4MHz の範囲で選択できます。このモジュールは、1.8MHz ~ 4MHz の範囲の外部クロックに同期させることもできます。PFM および PWM モードでは、TPSM82850x-Q1 は負荷が軽いときに自動的にパワーセーブ モードへ移行するため、負荷範囲全体にわたって高い効率が維持されます。

## 設計を開始

1. [ti.com](http://ti.com) で評価基板を注文します。

2. [TPSM82851x 2.7V ~ 6V 入力、0.5A/1A/2A インダクタ内蔵降圧パワー モジュールのデータシート](#)をダウンロードしてください。

3. データシートを使用して、目的の出力電圧に応じてデバイスの部品表 (BOM) を調整してください。

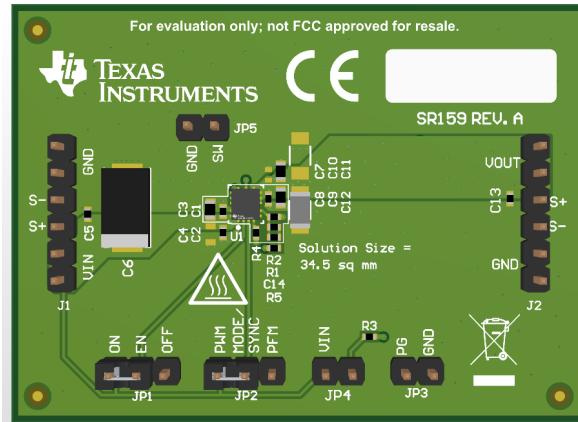

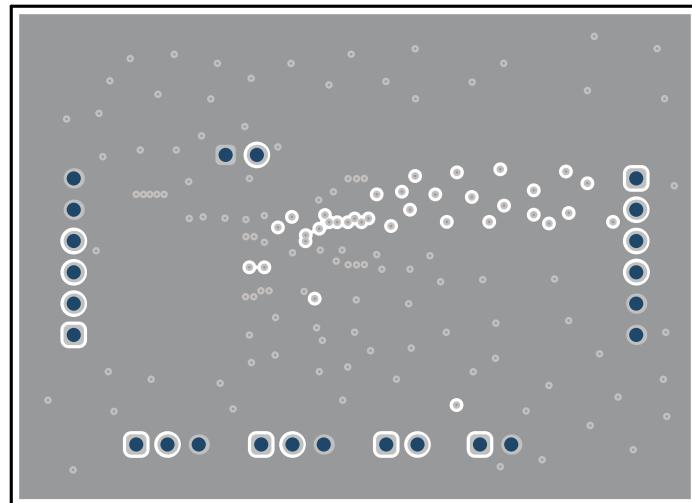

TPSM828502QEVM-159 (上面図)

## 1 評価基板の概要

### 1.1 はじめに

この評価基板は、インダクタ内蔵の TPSM82850x-Q1 降圧コンバータ モジュールの動作と機能を、ユーザーが容易に評価およびテストできる設計を採用しています。この評価基板は、2.7V ~ 6V の入力電圧を、最大 2A を供給可能な 1.8V の安定化出力電圧に変換します。このユーザー ガイドでは、TI の TPSM82850x-Q1 評価基板 (EVM) の特性、動作、使用方法を掲載しています。このドキュメントには、以下のセットアップ手順が含まれています。

- ハードウェア

- プリント基板 (PCB) レイアウト

- 回路図

- 部品表 (BOM)

### 1.2 キットの内容

表 1-1. TPSM828502QEVM-159 キットの内容

| 項目                 | 説明  | 数量 |

|--------------------|-----|----|

| TPSM828502QEVM-159 | PCB | 1  |

### 1.3 仕様

表 1-2. 性能仕様の概要

| 仕様   | テスト条件              | 最小値 | 標準値 | 最大値 | 単位 |

|------|--------------------|-----|-----|-----|----|

| 入力電圧 |                    | 2.7 |     | 6   | V  |

| 出力電圧 |                    |     | 1.8 |     | V  |

| 出力電流 | TPSM828502QEVM-159 | 0   |     | 2   | A  |

### 1.4 製品情報

この評価基板の PCB は、この IC の可変電圧バージョンに対応するよう設計されています。評価基板上では、フィードバックピンに接続された 抵抗デバイダ分岐を調整することで、目的の出力電圧を設定できます。他の入力コンデンサおよび出力コンデンサを追加することもできます。

## 2 ハードウェア

### 2.1 構成

このセクションでは、TPSM828502QEVM-159 の適切な使用方法について説明します。

#### 2.1.1 コネクタの説明

|                       |                                                                                                                                                             |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1、ピン 1 および 2 – VIN   | 評価基板の入力電源からの正の入力電圧接続                                                                                                                                        |

| J1、ピン 3 および 4 – S+/S- | 入力電圧センス接続。このポイントで入力電圧を測定します。                                                                                                                                |

| J1、ピン 5 および 6 – GND   | 評価基板の入力電源からの入力リターン接続                                                                                                                                        |

| J2、ピン 1 および 2 – VOUT  | 正の出力電圧接続                                                                                                                                                    |

| J2、ピン 3 および 4 – S+/S- | 出力電圧センス接続。このポイントで出力電圧を測定します。                                                                                                                                |

| J2、ピン 5 および 6 – GND   | 出力リターン接続                                                                                                                                                    |

| JP1 - EN              | EN ピン ジャンパ。ON と EN の間に付属のジャンパを配置すると、IC をオンにします。OFF と EN の間にジャンパを配置すると、IC がオフになります。                                                                          |

| JP2 – MODE/SYNC       | MODE/SYNC ピン ジャンパ。デバイスを強制 PWM モードで動作させるには、PWM と MODE/SYNC の間に付属のジャンパを配置します。デバイスを PFM/PWM モードで動作させるには、PFM と MODE/SYNC の間にジャンパを配置します。                         |

| JP3 – PG/GND          | このヘッダーのピン 1 に PG 出力が現れ、ピン 2 に便利なグラウンドが配置されています。                                                                                                             |

| JP4 – PG プルアップ電圧      | PG ピン プルアップ電圧ジャンパ。付属のジャンパを JP4 に配置し、PG ピン プルアップ抵抗を入力電圧に接続します。また、ジャンパを取り外し、ピン 1 に別の電圧を供給することで、PG ピンを異なるレベルにプルアップできます。この外部印加電圧は $V_{in} + 0.3V$ 未満である必要があります。 |

| JP5 – SW テスト ポイント     | このテスト ポイントは SW ノードのテスト ポイントです。必要な場合にのみ使用してください。フローティングのままにしてもかまいません。                                                                                        |

#### 2.1.2 ハードウェア設定

この評価基板を動作させるには、[コネクタの説明](#)に従ってジャンパ JP1 を目的の位置に設定してください。入力電源を J1 に接続し、負荷を J2 に接続します。

### 2.2 変更点

この評価基板のプリント基板 (PCB) は、ユーザによる一部の変更に対応できるよう設計されています。出力電圧に応じて、他の入力コンデンサ、出力コンデンサ、またはフィードフォワードコンデンサを追加できます。また、出力電圧は抵抗デバイダにより変更できます。ループ安定性測定のためにノイズを注入する際は、付属の抵抗 R5 を使用してください。

#### 2.2.1 入力と出力の各コンデンサ

C4 は、追加の入力コンデンサとして提供されています。このコンデンサは適切な動作に必須ではありませんが、入力電圧リップルを低減するために使用できます。

C7 と C11 は、追加の出力コンデンサとして提供されています。これらのコンデンサは適切な動作に必須ではありませんが、出力電圧リップルの低減および負荷過渡応答の改善に使用できます。適切に動作させるため、出力キャパシタンスをデバイスのデータシートの推奨範囲内にする必要があります。

#### 2.2.2 フィードフォワードコンデンサ

C14 はフィードフォワードコンデンサです。この評価基板は 10pF のフィードフォワードコンデンサを備えています。過渡応答を改善するため、TI は R1 と並列にフィードフォワードコンデンサ (CFF) を配置することを推奨しています。FB 抵抗値に関係なく、CFF の値は常に 10pF でなければなりません。

### 3 ハードウェア設計ファイル

#### 3.1 回路図

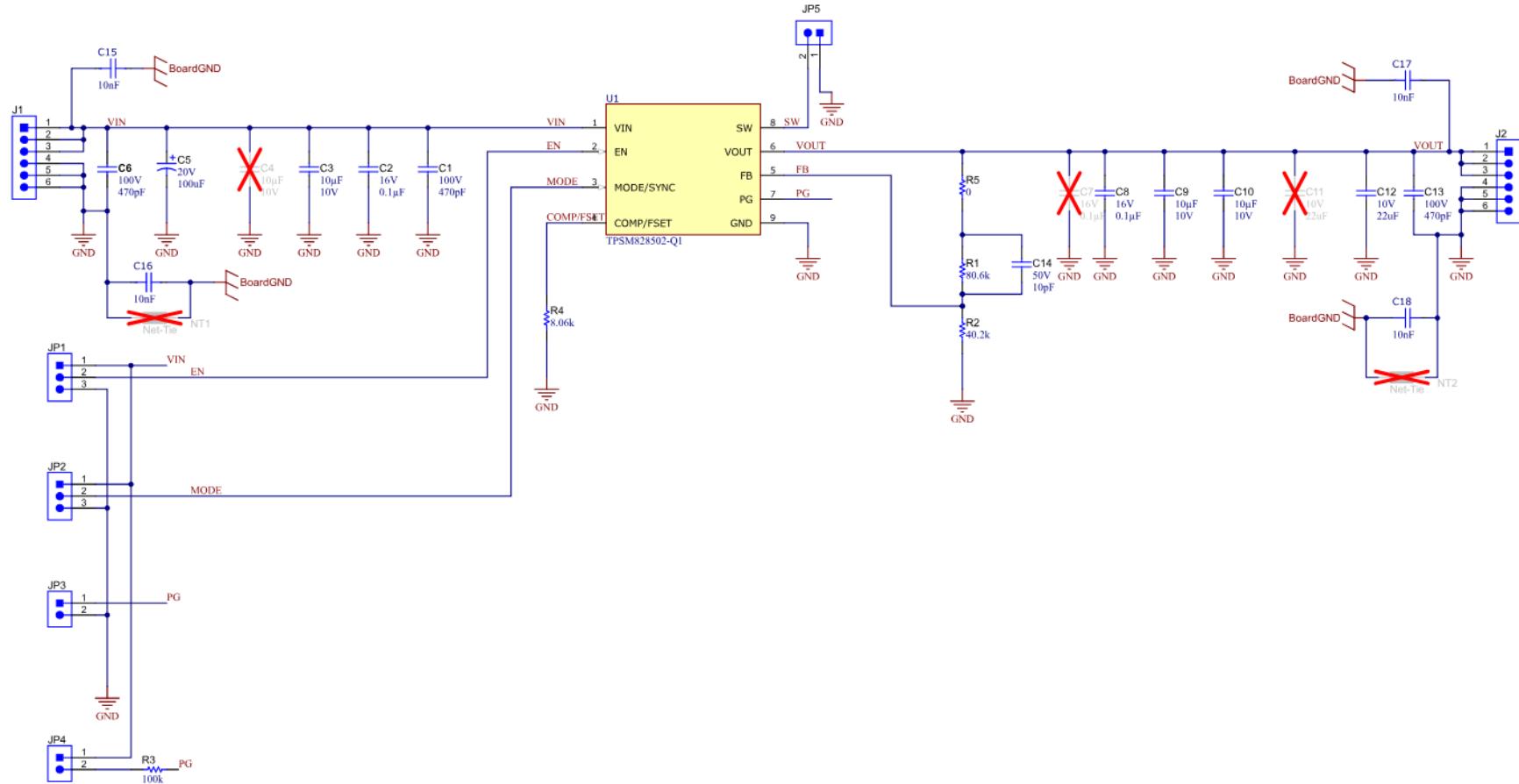

図 3-1 に、TPSM828502QEVM-159 の回路図を示します。

図 3-1. TPSM828502QEVM-159 の回路図

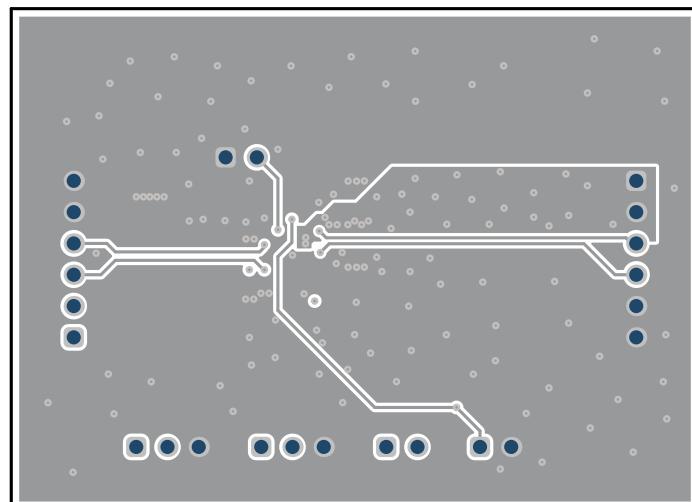

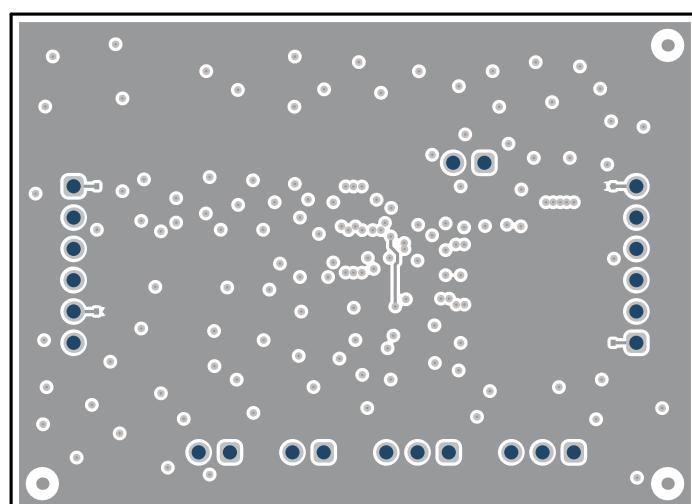

### 3.2 PCB のレイアウト

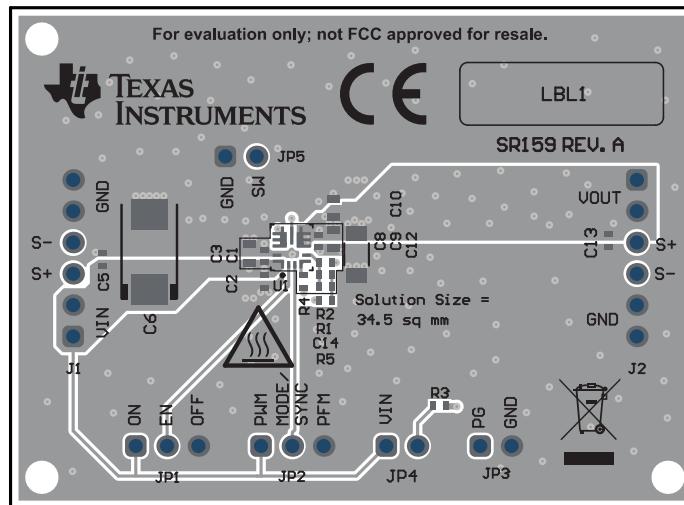

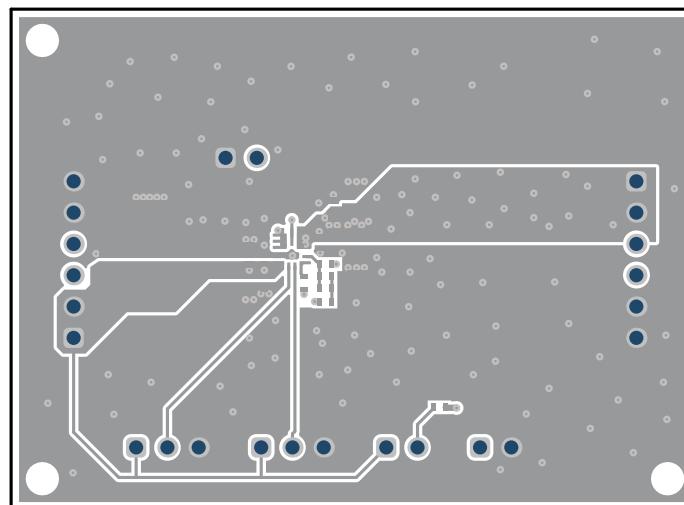

このセクションでは、TPSM828502QEVM-159 の基板レイアウトと図を示します。TPSM828502QEVM-159 は 4 層 PCB です。

図 3-2. 上面図

図 3-3. 上層

図 3-4. 信号層 1

図 3-5. 信号層 2

図 3-6. 下層

### 3.3 部品表 (BOM)

表 3-1 は TPSM828502QEVM-159 の部品表を示しています。

**表 3-1. TPSM828502QEVM-159 部品表**

| 数量 | 参照の記号                     | 値             | 説明                          | サイズ           | 部品番号               | メーカー                                  |

|----|---------------------------|---------------|-----------------------------|---------------|--------------------|---------------------------------------|

|    | <b>TPSM828502QEVM-159</b> |               |                             |               |                    |                                       |

| 3  | C1、<br>C6、C13             | 470pF         | コンデンサ、セラミック、100V、±10%、X7R   | 0402          | GRM155R72A471KA01D | Murata (村田製作所)                        |

| 2  | C2、<br>C8                 | 0.1μF         | コンデンサ、セラミック、16V、±10%、X7R    | 0402          | CL05B104KO5NNNC    | Walsin                                |

| 3  | C3、C9、<br>C10             | 10uF          | コンデンサ、セラミック、10V、±20%、X7R    | 0603          | GRM188Z71A106MA73D | Murata (村田製作所)                        |

| 1  | C12                       | 22uF          | コンデンサ、セラミック、10V、±10%、X7R    | 1206          | GRM31CR71A226KE15L | Murata (村田製作所)                        |

| 1  | C14                       | 10pF          | コンデンサ、セラミック、50V、C0G/NP0、±5% | 0402          | GRM1555C1H100JA01D | Murata (村田製作所)                        |

| 1  | C5                        | 100uF         | コンデンサ、タンタル ポリマー、20V、±20%    | 7.3x4.3mm     | 20TQC100MYF        | Panasonic<br>Electronic<br>Components |

| 4  | C15、C16、C17、<br>C18       | 10nF          | コンデンサ、セラミック、50V、±10%、X7R    | 0402          | GCM155R71H103KA55D | Murata (村田製作所)                        |

| 1  | R1                        | 80.6k         | 抵抗、チップ、0.063W、1%            | 0402          | 標準                 | 標準                                    |

| 1  | R2                        | 40.2k         | 抵抗、チップ、0.063W、1%            | 0402          | 標準                 | 標準                                    |

| 1  | R3                        | 100k          | 抵抗、チップ、0.0625W、1%           | 0402          | 標準                 | 標準                                    |

| 1  | R4                        | 8.06k         | 抵抗、チップ、0.063W、1%            | 0402          | 標準                 | 標準                                    |

| 1  | R5                        | 0             | 抵抗、チップ、0.063W、5%            | 0402          | 標準                 | 標準                                    |

| 1  | U1                        | TPSM828502-Q1 | IC、6V、2A 降圧パワー モジュール        | 2.7mm × 3.0mm | TPSM828502-Q1      | TI                                    |

## 4 追加情報

### 4.1 商標

すべての商標は、それぞれの所有者に帰属します。

### 5 関連資料

デバイスのデータシートおよびその他のドキュメントは、[TPSM828502-Q1](#) プロダクトフォルダで入手できます。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月