# EVM User's Guide: SK-AM62-SIP

## AM62x-SIP SK 評価基板

### 説明

SK-AM62-SIP スタータ キット (SK) 評価基板 (EVM) は、512MB の LPDDR4 SDRAM を単一のパッケージに統合した AM6254 システム オン チップ (SoC) を土台として製作した、スタンドアロンのテスト / 開発プラットフォームです。AM625SIP プロセッサは、クワッドコアの 64 ビット Arm®-Cortex®-A53 マイクロプロセッサと、シングルコアの Arm Cortex-M4F マイコンで構成されています。

SK-AM62-SIP を使用すると、3D GPU を活用し、ドット密度 (DPI) の高い HDMI™ (高品位マルチメディア インターフェイス) や LVDS (低電圧差動信号伝送) を経由するデュアル ディスプレイ機能、またシリアル、イーサネット、USB、その他のインターフェイスを使用した産業用通信アプリケーションの実験を実施できます。

### 設計を開始

1. [SK-AM62-SIP](#) で評価基板を注文します。

2. EVM の[設計ファイル](#)をダウンロードします。

3. [AM62x 開発ポータル](#)から、多くのアプリケーション向けのリファレンス ソフトウェアをダウンロードできます。

4. 操作の前に、この評価基板のユーザー ガイドをよくお読みください。

### 特長

- USB-C 電源を使用するスタンド アロン動作モード

- 電力最適化済み、ディスクリート DC/DC パワー マネージメント

- コード開発とデバッグに適した USB 接続機能付きオンボード、XDS110 JTAG インターフェイス

- オンボードの 32GB eMMC メモリと 512Mb OSPI NOR フラッシュ

- RGMII RJ45 コネクタ x 2

- Type-A と Type-C のコネクタを搭載した USB 2.0 x 2

- XDS110 を介した テスト オートメーション インターフェイス

- インターフェイスにアクセスするための拡張コネクタ

- Wi-Fi/BT モジュール用 M.2 コネクタ

このリファレンスデザインは HDMI®技術を採用しています。

| 目次                            |           |

|-------------------------------|-----------|

| 説明                            | 1         |

| 設計を開始                         | 1         |

| 特長                            | 1         |

| <b>1 評価基板の概要</b>              | <b>3</b>  |

| 1.1 はじめに                      | 3         |

| 1.2 キットの内容                    | 3         |

| 1.3 製品情報                      | 3         |

| 1.4 評価基板のリビジョンおよびアセンブリバリエーション | 3         |

| 1.5 仕様                        | 3         |

| <b>2 ハードウェア</b>               | <b>5</b>  |

| 2.1 補足画像                      | 5         |

| 2.2 主な特長                      | 6         |

| 2.3 電源                        | 7         |

| 2.4 電源オン/オフの手順                | 15        |

| 2.5 インターフェイス マッピング            | 17        |

| 2.6 クロック処理                    | 17        |

| 2.7 リセット                      | 20        |

| 2.8 CSI インターフェイス              | 21        |

| 2.9 オーディオ コーデック インターフェイス      | 22        |

| 2.10 HDMI ディスプレイ インターフェイス     | 23        |

| 2.11 JTAG インターフェイス            | 24        |

| 2.12 テスト オートメーション ヘッダー        | 26        |

| 2.13 UART インターフェイス            | 28        |

| 2.14 USB インターフェイス             | 29        |

| 2.15 メモリ インターフェイス             | 32        |

| 2.16 イーサネット インターフェイス          | 37        |

| 2.17 GPIO ポート エクスパンダ          | 39        |

| 2.18 GPIO へのマッピング             | 40        |

| 2.19 OLDI ディスプレイ インターフェイス     | 41        |

| 2.20 評価基板のユーザー設定/構成           | 41        |

| 2.21 拡張ヘッダ                    | 47        |

| 2.22 割り込み                     | 56        |

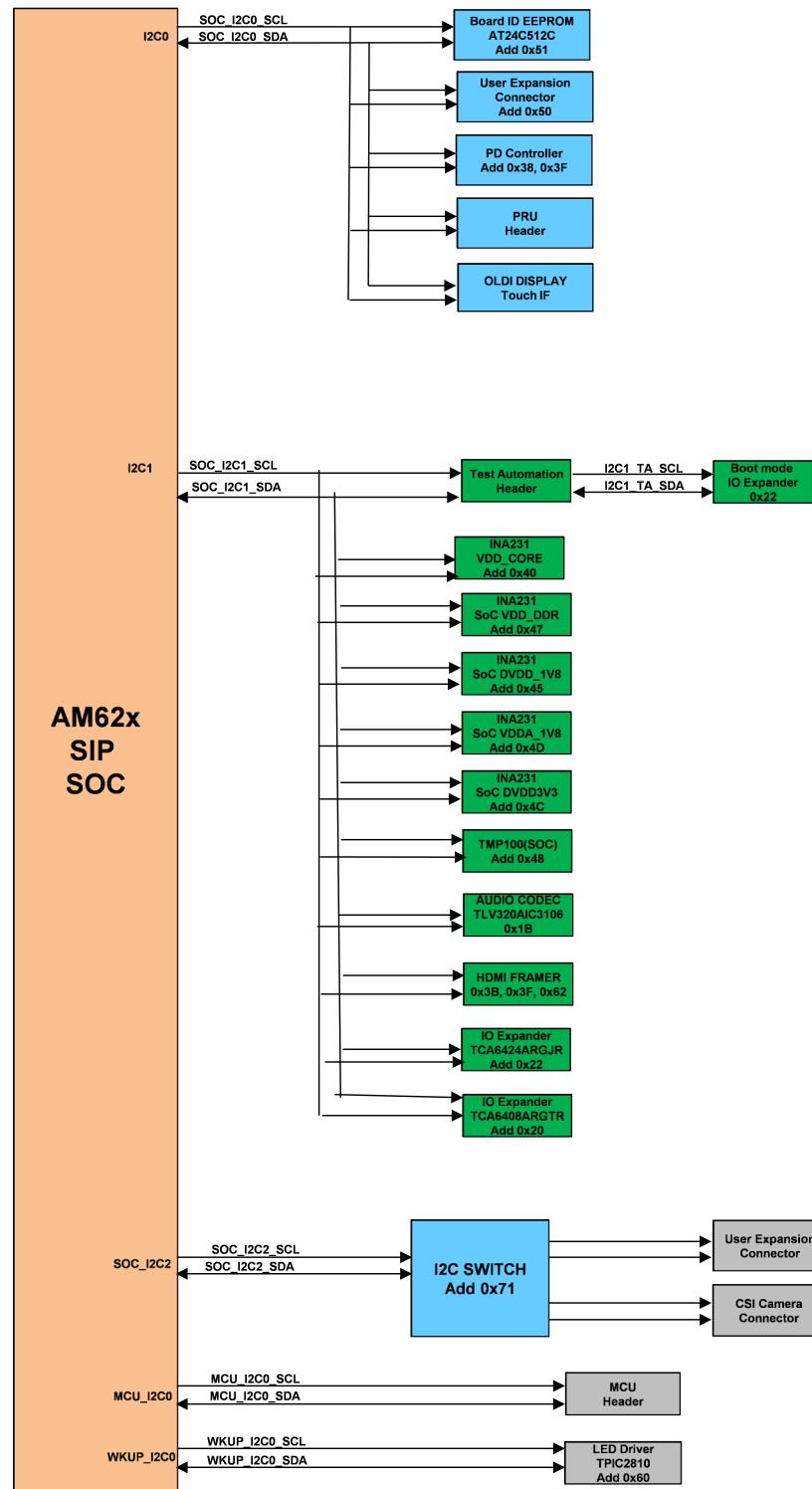

| 2.23 I2C アドレス マッピング           | 57        |

| <b>3 ハードウェア設計ファイル</b>         | <b>59</b> |

| <b>4 準拠に関する情報</b>             | <b>59</b> |

| 4.1 準拠および認証                   | 59        |

| <b>5 追加情報</b>                 | <b>59</b> |

| 5.1 ハードウェアまたはソフトウェアに関する既知の問題  | 59        |

| 5.2 商標                        | 60        |

| <b>6 改訂履歴</b>                 | <b>60</b> |

## 1 評価基板の概要

### 1.1 はじめに

本テクニカル ユーザー ガイドでは、AM62x SIP SoC を実装した低コストのスタータ キットである SK-AM62-SIP 評価基板のハードウェア アーキテクチャについて説明します。AM62x SIP プロセッサは、クワッドコアの 64 ビット Arm®-Cortex® A53 マイクロプロセッサ、シングルコアの Arm Cortex-R5F マイコン、および Arm Cortex-M4F マイコンで構成されています。

SK-AM62-SIP は、HS-FS (high-security field-securable: 高度セキュリティ対応、フィールドでのセキュア化可能) シリコンを採用しているため、セキュリティ アプリケーションの場合、オプションで鍵と暗号化をカスタマイズできます。

SK-AM62-SIP は、HDMI ディスプレイまたは外部 LVDS パネルを使用する HMI (ヒューマン マシン インターフェイス) やコントロール パネルなど、最大 2K 60fps の解像度の各種ディスプレイ アプリケーションで使用できます。産業用の豊富なインターフェイスを搭載し、1.4GHz のクワッド A53 を使用できる Arm の強力な性能は、PLC (プログラマブル ロジック コントローラ)、オートメーション制御、ゲートウェイ、EV (電気自動車) 充電、医療、ビル オートメーション システムなどの幅広いアプリケーション向けに優れた制御機能と通信機能を実現するのに役立ちます。

### 1.2 キットの内容

- SK-AM62-SIP EVM

- 『評価基板ユーザー ガイド』冊子

- EVM の免責事項と標準約款

### 1.3 製品情報

加えて、SK-AM62-SIP は他のプロセッサまたはシステムと通信できるほか、通信ゲートウェイとして動作することも可能です。また、標準リモート I/O システムとして直接動作することや、産業用通信ネットワークに接続したシンプルなセンサとして動作することもできます。

Code Composer Studio™ (CCSTUDIO) 統合開発環境 (IDE) のような標準的な開発ツールを使用し、組込み済みエミュレーション ロジックを通じてエミュレーションとデバッグを実施することもできます。多くのアプリケーションに適したリファレンス ソフトウェアは [AM62x 開発ポータル](#) からダウンロードできます。

### 1.4 評価基板のリビジョンおよびアセンブリ バリエーション

SK-AM62-SIP 評価基板のさまざまな PCB 設計リビジョンとアセンブリ バリエーションを、表 1-1 に示します。特定の PCB リビジョンは PCB 上にシルクスクリーンで示され、特定のアセンブリ バリエーションは追加のステッカー ラベルで示されています

表 1-1. 評価基板の PCB 設計リビジョンおよびアセンブリ バリエーション

| OPN         | PCB リビジョン | アセンブリ バリエーション | リビジョンとアセンブリ バリエーションの説明                                                                 |

|-------------|-----------|---------------|----------------------------------------------------------------------------------------|

| SK-AM62-SIP | PROC162E1 | 該当なし          | AM62X SIP 評価基板の最初のプロトタイプ、初期リリース リビジョン。PMIC 電源ソリューションを使用して Sitara AM62X SIP MPU を実装します。 |

### 1.5 仕様

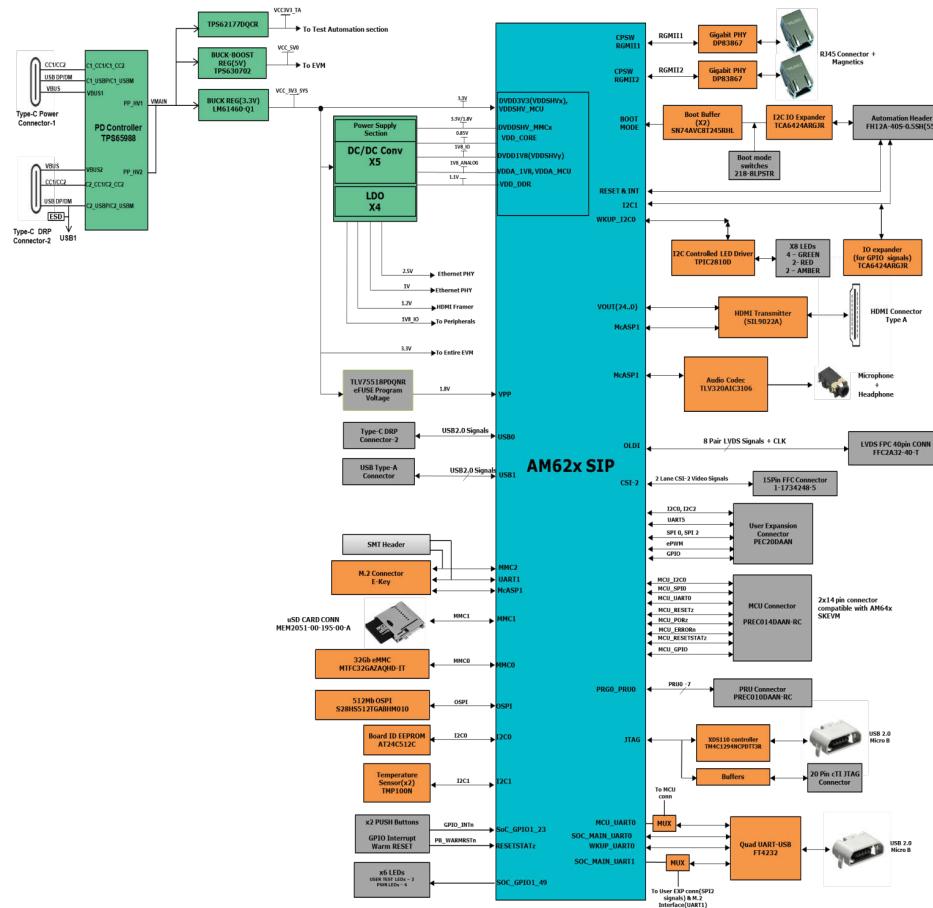

次の図は、AM62x SIP SK 評価基板の機能ブロック図を示しています。

Main Block Diagram

## 2 ハードウェア

### 2.1 補足画像

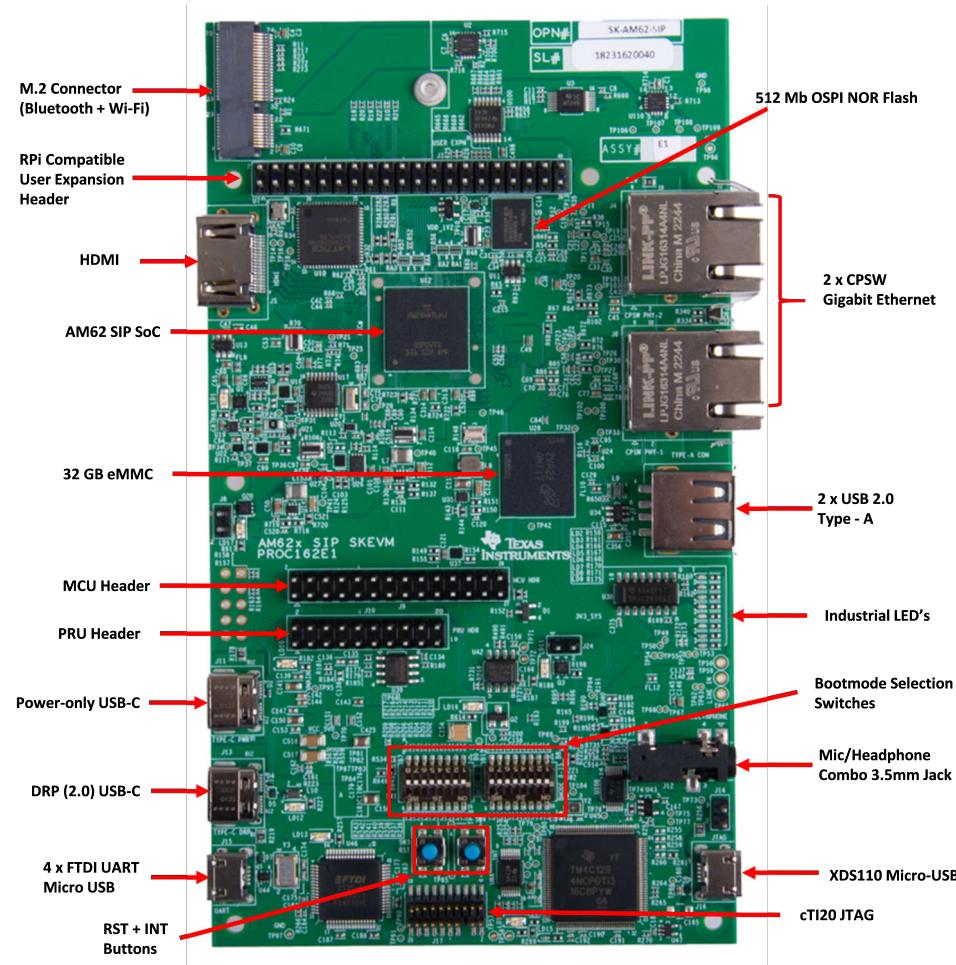

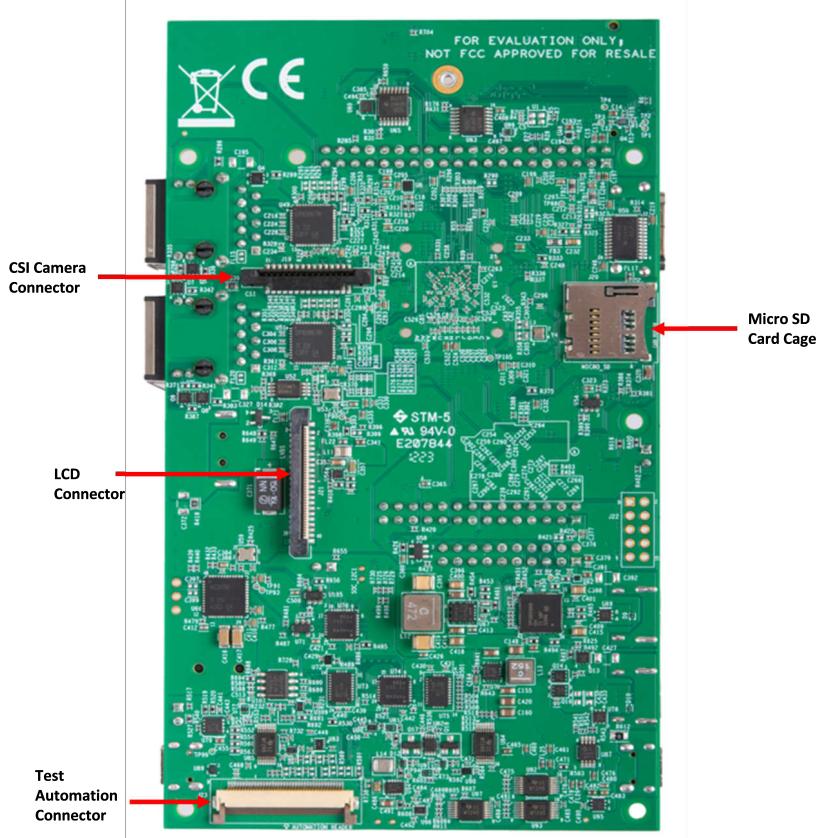

このセクションでは、評価基板の画像および基板上のさまざまなブロックの位置を示します。

図 2-1. 評価基板の上面

図 2-2. 評価基板の底面

## 2.2 主な特長

AM62x SIP SK 評価基板は、高性能のスタンダードアロン開発プラットフォームです。これを用いることによって、テキサス インスツルメンツの AM62x SIP システム オン チップ (SoC) 用の産業用アプリケーションの評価と開発を行うことができます。

以下のセクションでは、SK 評価基板の主な特長について説明します。

### 2.2.1 プロセッサ

- AM62x SIPSOC、13mm × 13mm、0.5mm ピッチ、425 ピン VCA FBGA

### 2.2.2 電源

- USB Type-C® ポート (入力範囲 5V ~ 15V) × 2

- プロセッサとペリフェラル用のディスクリート レギュレータ、LDO を使用して電源設計を最適化

### 2.2.3 メモリ

- UHS-1 対応の MicroSD カード スロット

- 512MbitOctal SPI フラッシュ メモリ

- 512Kbit I2C (Inter-Integrated Circuit) 基板 ID EEPROM

- HS-400 対応の 32GBeMMC フラッシュ

### 2.2.4 JTAG / エミュレータ

- XDS110 オンボード エミュレータ

- 外付けエミュレータからの 20 ピン JTAG 接続に対応

## 2.2.5 サポートされるインターフェイスおよびペリフェラル

- USB2.0 type C インターフェイス x 1、DFP、UFP の役割をサポート

- USB2.0 ホストインターフェイス x 1、Type A

- 1xHDMI インターフェイス

- オーディオ ライン入力およびマイク + ヘッドフォン出力

- M.2 Key E インターフェイスは、Wi-Fi と Bluetooth の両方のモジュールをサポート

- 2 つの RJ45 コネクタで 10/100/1000Mbps のデータレートをサポートするギガビットイーサネット ポート x 2

- microB USB コネクタ経由のクワッド ポート UART to USB 回路

- 産業用イーサネット LED

- 電流監視用 INA デバイス

- SoC 付近に温度監視用温度センサ x 1

## 2.2.6 拡張コネクタ/ヘッダー

- CSI カメラ ヘッダー

- LVDS ディスプレイコネクタ

- ユーザー拡張コネクタ

- PRU ヘッダー

- MCU ヘッダー

## 2.3 電源

### 2.3.1 電源要件

AM62x SIP SK 評価基板は、2 つの USB Type-C コネクタのいずれかを通じて電力を供給できます：

- コネクタ 1 (J11) - 電源ロール - SINK、データロールなし

- コネクタ 2 (J13) - 電源ロール - DRP、データロール - USB2.0 DFP または UFP

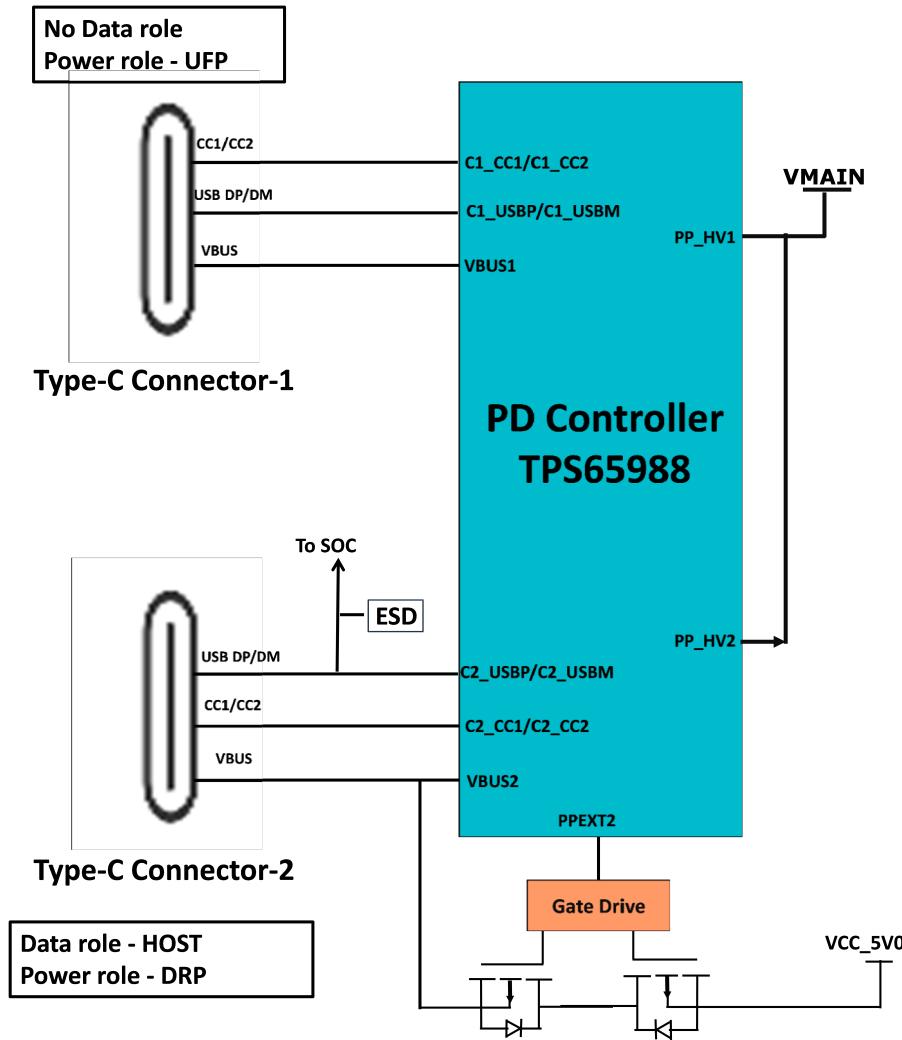

AM62x SIP SK 評価基板は、5V ~ 15V の電圧入力範囲と、3A の電流に対応しています。USB PD コントローラ (メーカー型番 TPS65988DHRSHR) は、ケーブル検出時の PD ネゴシエーションに使用され、基板に必要な電力を取得します。コネクタ 1 は UFP ポートとして構成され、データロールはありません。コネクタ 2 は DRP ポートとして構成され、コネクタ 1 によって基板に電力が供給されている場合にのみ DFP として動作します。両方のコネクタが外部電源に接続されている場合、PD の電力供給能力が最も高いポートが基板の電源として選択されます。

表 2-1. Type-C ポートの電源ロール

| J11(UFP) | J13(DRP) | 基板電源             | 注記                                                              |

|----------|----------|------------------|-----------------------------------------------------------------|

| 接続済み     | NC       | ON-J11           | J11 は UFP で、電力のシンクのみを行います。J13 は、ペリフェラルが接続されている場合に DFP として動作します。 |

| NC       | 接続済み     | ON - J13         | J13 は UFP で、電力のシンクのみを行います。                                      |

| 接続済み     | 接続済み     | ON - J11 または J13 | 基板は、PD の電力供給能力が最も高いポートから電力を供給されます                               |

PD IC は、パワーアップ時に SPI EEPROM を使用して必要な構成をロードすることで、互換性のある電源と電力供給能力をネゴシエートできます。

構成ファイルは、ヘッダー J22 を使用して EEPROM にロードされます。EEPROM がプログラムされると、PD は SPI 通信を介して構成ファイルを取得します。構成ファイルがロードされると、PD は必要な電源要件を満たすために電源とネゴシエートします。

---

**注**

EEPROM には、PD コントローラの動作に必要な構成ファイルがあらかじめプログラムされています。

---

SK 評価基板に電力を供給しているコネクタを識別するために、両方の Type-C コネクタには電源表示 LED が搭載されています。

外部電源 (Type-C 出力) は 評価基板 の電源として使用可能ですが、SK 評価基板キットには含まれていません。

外部電源の要件 (Type-C) は次のとおりです。

最小電圧: 5VDC、推奨最小電流: 3000mA

最大電圧: 15VDC、最大電流: 5000mA

**表 2-2. 推奨外部電源**

| DigiKey 部品番号 | メーカー          | メーカー部品番号             |

|--------------|---------------|----------------------|

| 1939-1794-ND | GlobTek, Inc. | TR9CZ3000USBCG2R6BF2 |

| Q1251-ND     | Qualtek       | QADC-65-20-08CB      |

---

**注**

SK-AM62 SIP は電源用に USB PD を実装しているため、デバイスと電源アダプタの両方がサポートする最大電圧 / 電流の組み合わせをネゴシエートすることができます。電源が上記の最大電圧を上回り、かつ電流要件を満たしている場合、電源アダプタは USB-C PD 仕様に準拠しています。

---

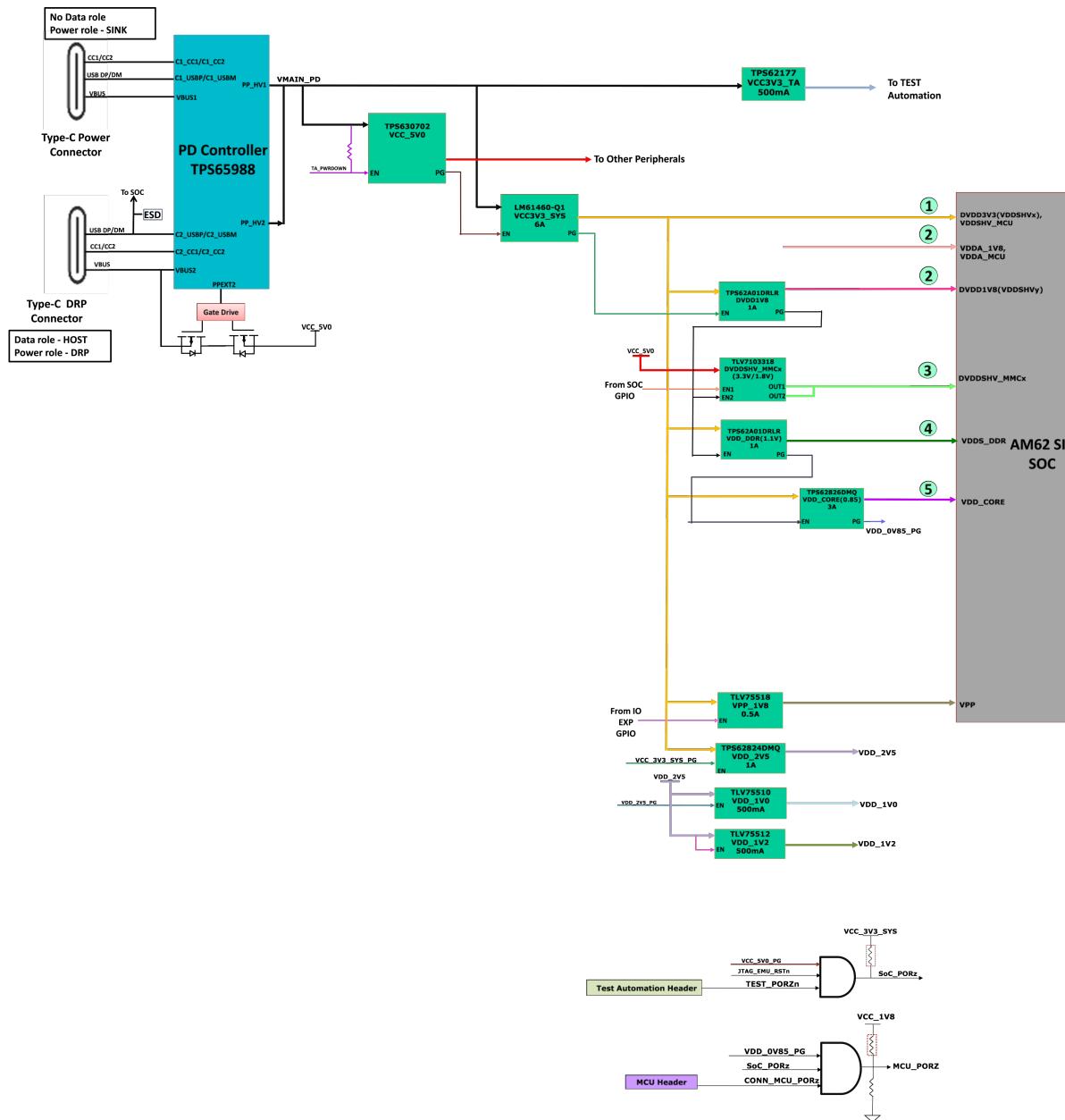

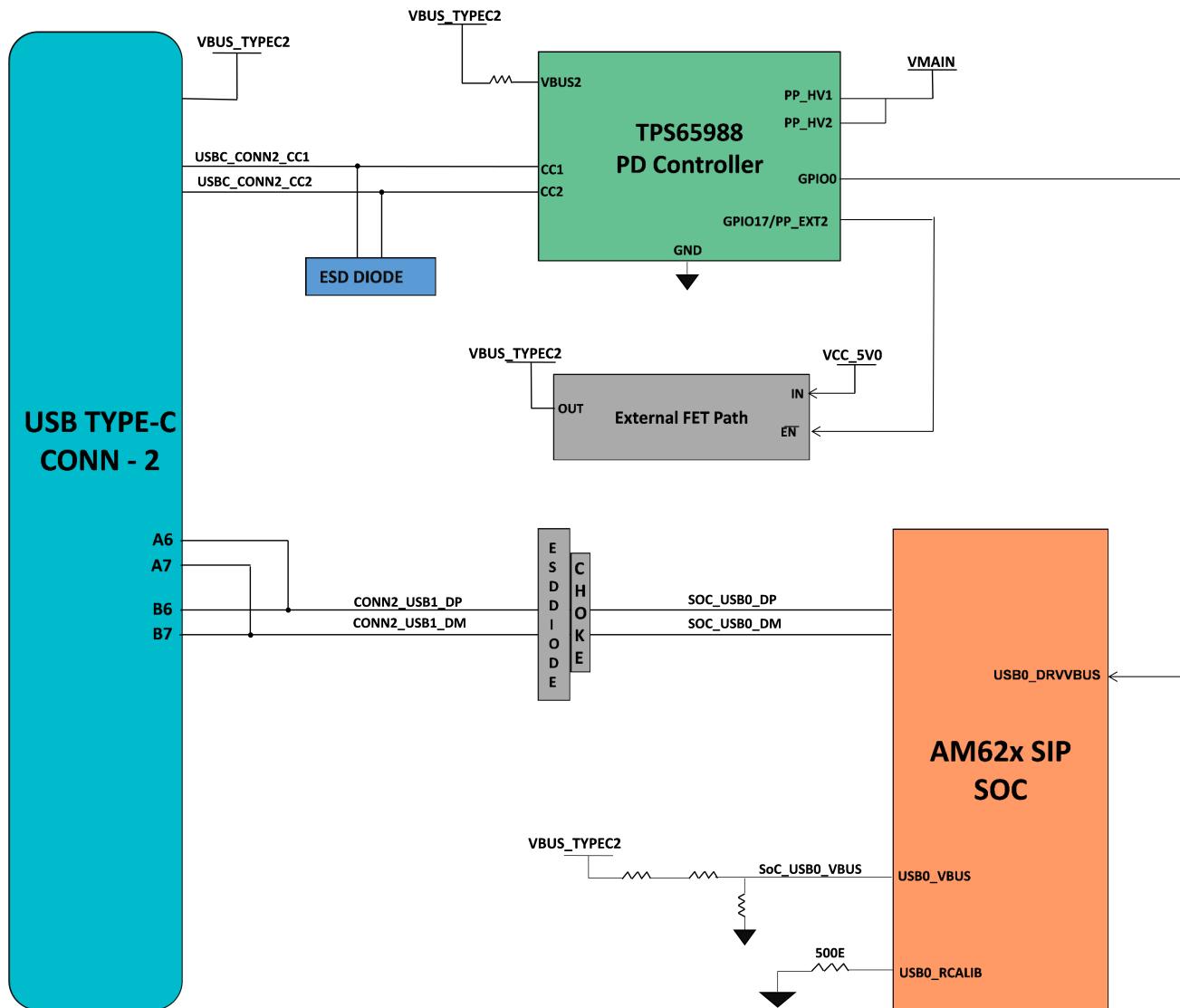

### 2.3.2 電源入力

USB Type-C コネクタ (VBUS ラインと CC ライン) はどちらも、デュアル PD コントローラ (メーカー型番 TPS65988) に接続されています。TPS65988 は、スタンドアロンの USB Type-C およびパワー デリバリ (PD) コントローラであり、2 つの USB Type-C コネクタのケーブルのプラグと向きを検出します。ケーブルを検出すると、TPS65988 は USB PD プロトコルを使用して CC ワイヤで通信を行います。ケーブルの検出と USB PD ネゴシエーションが完了すると、TPS65988 は適切な電力パスを有効にします。TPS65988 の 2 つの内部電力パスは、2 つの Type-C ポートのシンク パスとして構成され、DFP として動作する場合には Type-C CONN 2 から 5V を供給するための外部 FET パスが提供されています。外部 FET パスは、PD コントローラの GPIO17/PP\_EXT2 によって制御されています。

TPS65988 PD コントローラは、CC ネゴシエーションにより、3A (最大 15V) の出力を供給できます。両方の Type-C コネクタからの VBUS ピンは、PD コントローラの VBUS ピンに接続されています。PD の出力は VMAIN です。この VMAIN は、オンボードの昇降圧レギュレータと降圧レギュレータに供給され、SK 評価基板用の 5V と 3.3V の固定電源を生成します。

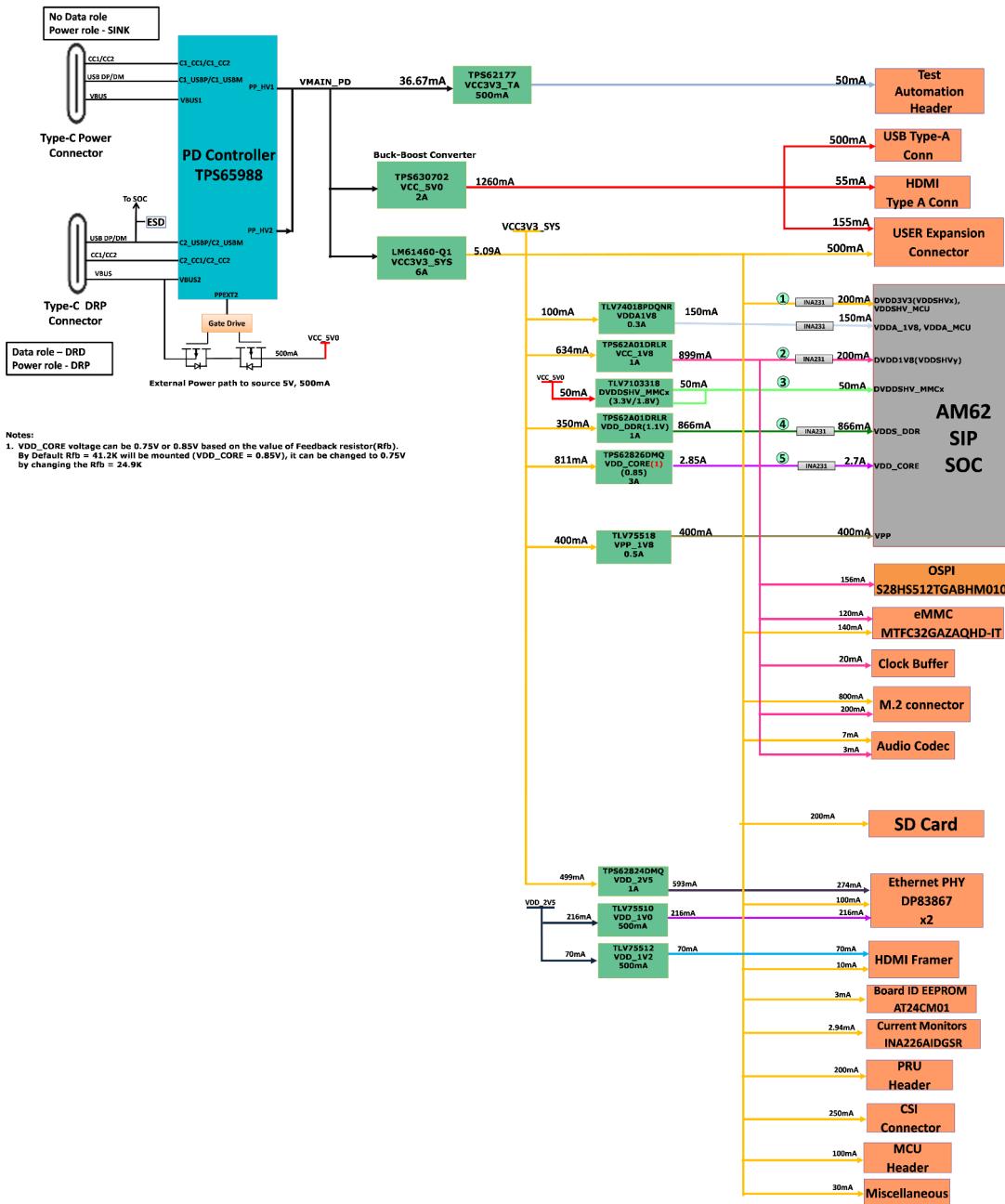

図 2-3. PD コントローラ

以下のセクションでは、SKEVM ボード、サポートコンポーネント、リファレンス電圧に電力を供給する電源分配ネットワークのトポロジについて説明します。

AM62x SIP SK 評価基板には、ディスクリート電源コンポーネントに基づく電源デザインが採用されています。電源供給の初期段は、2 つの USB Type-C コネクタ J11 と J13 のいずれかからの VBUS 電圧になります。USB Type-C デュアル PD コントローラ (メーカー型番 TPS65988DHRSHR) は、システムに必要な電力のネゴシエーションに使用されます。

昇降圧コントローラ TPS630702RNMR と降圧コンバータ LM61460-Q1 は、それぞれ 5V と 3.3V の生成に使用され、レギュレータへの入力は PD 出力です。これらの 3.3V と 5V の電圧は、AM62x SIP SK 評価基板の電源リソースの主要な電圧です。

降圧レギュレータ LM61460-Q1 から生成された 3.3V 電源は、各種 SoC レギュレータおよび LDO への入力電源です。昇降圧レギュレータ TPS630702RNMR から生成された 5V 電源は、オンボードのペリフェラルの電源に使用されます。

基板上で使用されるディスクリートレギュレータと LDO は次のとおりです。

- TPS62824DMQR — イーサネット PHY 用の VDD\_2V5 レールを生成

- TLV75510PDQNR — イーサネット PHY 用の VDD\_1V0 を生成

- TLV75512PDQNR — HDMI トランシミッタ用の VDD\_1V2 を生成

- TLV74018PDQNR — SoC 用の 1.8V アナログ電源を生成

- TPS62A01DRLR — SoC およびペリフェラル (OSPI、eMMC、オーディオ コーデック、M.2 コネクタ、クロック バッファ) 用の 1.8V IO 電源を生成

- TLV7103318QDSERQ1 — SoC 用の VDDSHV5\_MMC1 (SD インターフェイス) 電源を生成

- TPS62A01DRLR — SoC 用の DDR 電源を生成

- TPS62826DMQR — SoC 用のコア電源を生成

基板には、以下の用途向けに専用レギュレータも搭載されています：

- TPS62177 レギュレータ — テスト オートメーション セクションの常時オン回路に電力を供給

- TLV75518LDO — SoC の e-Fuse プログラミング用

- TPS79601LDO - XDS110 オンボード エミュレータ用

- TPS73533LDO — FT4232 UART-to-USB ブリッジ用

さらに、テスト オートメーション ヘッダーからの GPIO も TPS630702RNMR イネーブル ピンに接続されており、テスト オートメーション ボード経由で SK 評価基板のオン / オフを制御します。このテスト オートメーション ボードは、すべての他の電源が派生する TPS630702RNMR の VCC\_5V0 出力だけを無効化します。SoC には異なる IO グループがあります。各 IO グループには、次のセクションで示す特定の電源から電力が供給されます。

### 2.3.3 電源

AM62x SIP SK 評価基板は、DC/DC コンバータのアレイを使用して、ボード上のさまざまなメモリ、クロック、SoC、その他の部品に必要な電圧と電力を供給します。

以下の図に、電源レールの生成に使用される各種のディスクリートレギュレータおよび LDO と、AM62x SIP SK 評価基板上の各ペリフェラルの消費電流を示します。

図 2-4. 電力アーキテクチャ

### 2.3.4 電源シーケンス

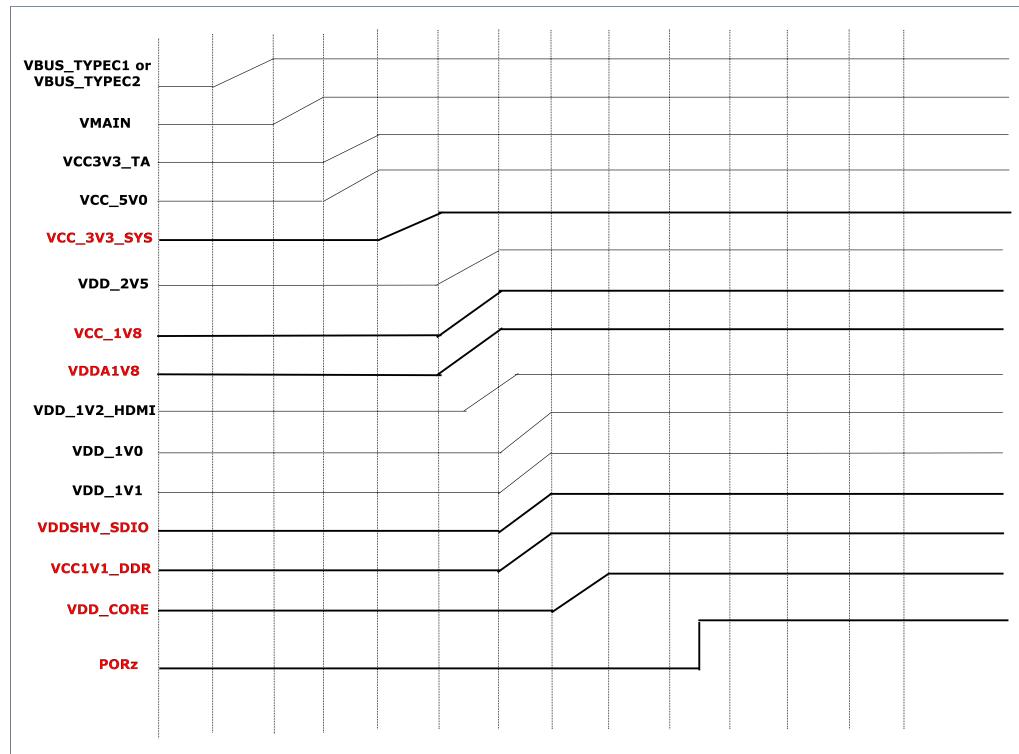

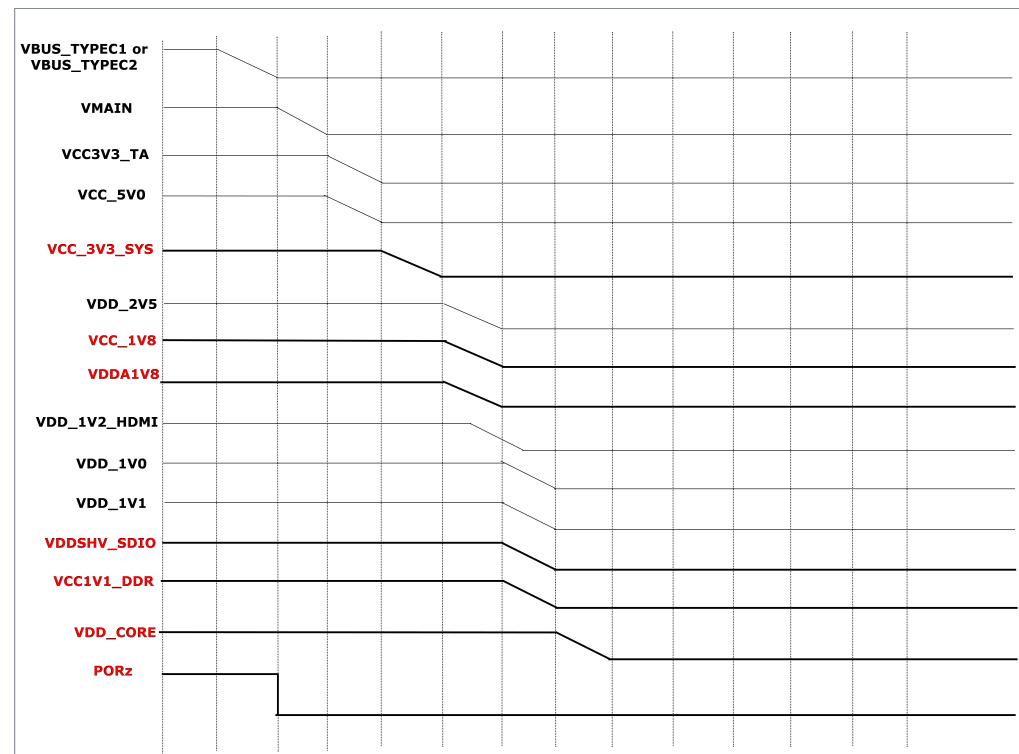

下の図は、AM62x SIP SK 評価基板の全電源のパワーアップおよびパワーダウン シーケンスを示しています。AM62x SIP SoC の電源レールは赤色で示されています。

図 2-5. パワーアップ シーケンス

図 2-6. パワーダウン シーケンス

図 2-7. 電源シーケンス

### 2.3.5 AM62x SIP SoC 電源

AM62x SIP のコア電圧は、Rfb (R150) 抵抗の値と電力最適化要件に基づいて、0.75V または 0.85V に設定できます。デフォルトでは、Rfb = 41.2K が搭載されており (VDD\_CORE = 0.85V)、Rfb を 24.9K に変更することで 0.75V に変更できます。電流モニタは、SoC 電源レールのすべてに搭載されています。

SoC には異なる IO グループがあります。各 IO グループには、以下の表に示すように、特定の電源から電力が供給されます。

**表 2-3. SoC 電源**

| シリアル番号 | 電源               | SoC 電源レール                       | IO 電源グループ | 電圧   |

|--------|------------------|---------------------------------|-----------|------|

| 1      | VDD_CORE         | VDDA_CORE_USB                   |           | 0.85 |

|        |                  | VDDA_CORE_CSI                   |           |      |

|        |                  | VDD_CANUART                     | CANUART   |      |

|        |                  | VDD_CORE                        | CORE      |      |

|        |                  | VDDR_CORE                       | CORE      |      |

| 2      | VDDA_1V8         | VDDA_1V8_CSIRX の詳細を示します。        | CSI       | 1.8  |

|        |                  | VDDA_1V8_USB                    | USB       |      |

|        |                  | VDDA_1V8 MCU                    |           |      |

|        |                  | VDDA_1V8_OLDI                   | OLDI      |      |

|        |                  | VDDA_1V8_OSCO                   | OSCO      |      |

|        |                  | VDDS_MEM_1P8                    | DDR       |      |

|        |                  | VDDA_PLL0, VDDA_PLL1 &VDDA_PLL2 |           |      |

| 3      | VDD_DDR          | VDDS_DDR                        | DDR0      | 1.1  |

|        |                  | VDDS_DDR_MEM                    |           |      |

| 5      | VPP_1V8          | VPP_1V8                         |           | 1.8  |

| 6      | SoC_VDDSHV5_SDIO | VDDSHV5                         | MMC1      |      |

| 7      | SoC_DVDD1V8      | VDDSHV0                         | 総則        | 1.8  |

|        |                  | VDDSHV1                         | OSPI      |      |

|        |                  | VDDSHV4                         | MMC0      |      |

|        |                  | VDDSHV6                         | MMC2      |      |

|        |                  | VMON_1P8_SOC                    |           |      |

| 8      | SoC_DVDD3V3      | VDDSHV0                         | 総則        | 3.3  |

|        |                  | VDDSHV2                         | RGMII     |      |

|        |                  | VDDSHV3                         | GPMC      |      |

|        |                  | VDDSHV_MCU                      | MCU 全般    |      |

|        |                  | VMON_3P3_SOC                    |           |      |

|        |                  | VDDA_3P3_USB                    | USB       |      |

### 2.3.6 電流監視

INA231 電力監視デバイスは、AM62x SIP プロセッサの各種電源レールの電流と電圧を監視するために使用されます。INA231 は、I2C インターフェイス (SoC\_I2C1) で AM62x SIP と接続されています。負荷電流測定用に、4 端子の高精度シャント抵抗が実装されています。

**表 2-4. INA I2C デバイス アドレス**

| ソース         | 電源ネット       | デバイス アドレス | 電源レールに接続されているシャントの値 |

|-------------|-------------|-----------|---------------------|

| VCC_CORE    | VDD_CORE    | 0x40      | 1mΩ± 1%             |

| VCC_3V3_SYS | SoC_DVDD3V3 | 0x4C      | 10mΩ± 1%            |

| VCC_1V8     | SoC_DVDD1V8 | 0x45      | 10mΩ± 1%            |

| VDDA1V8     | VDDA_1V8    | 0x4D      | 10mΩ± 1%            |

| VCC1V1_DDR  | VDD_DDR     | 0x47      | 10mΩ± 1%            |

## 2.4 電源オン/オフの手順

評価基板への電力供給は、2 つの USB Type-C ポートのいずれかに PD 電圧と電流を供給する外部電源を通じて供給されます。

**注**

IO ケーブルの最大長が 3m を超えないことを推奨します。

### 2.4.1 電源オンの手順

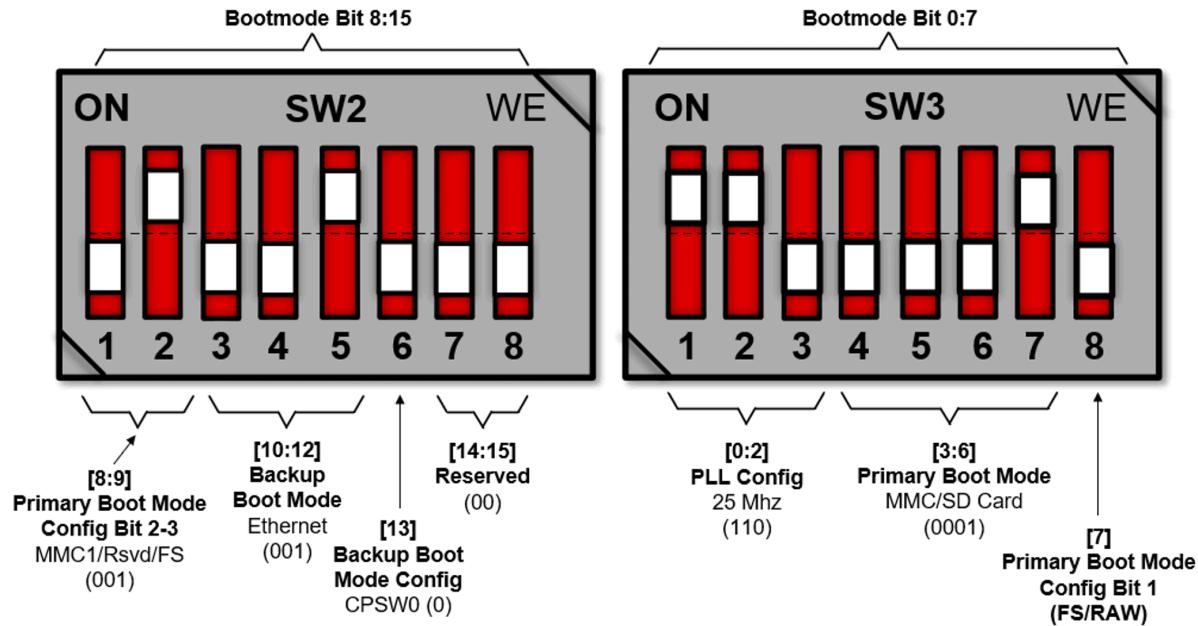

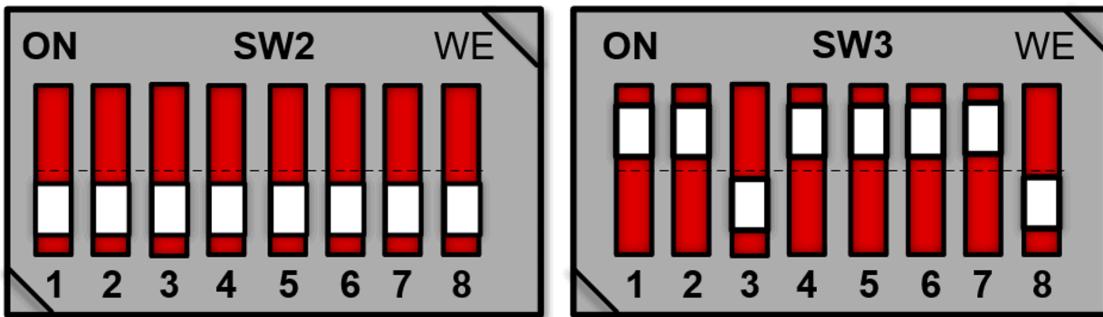

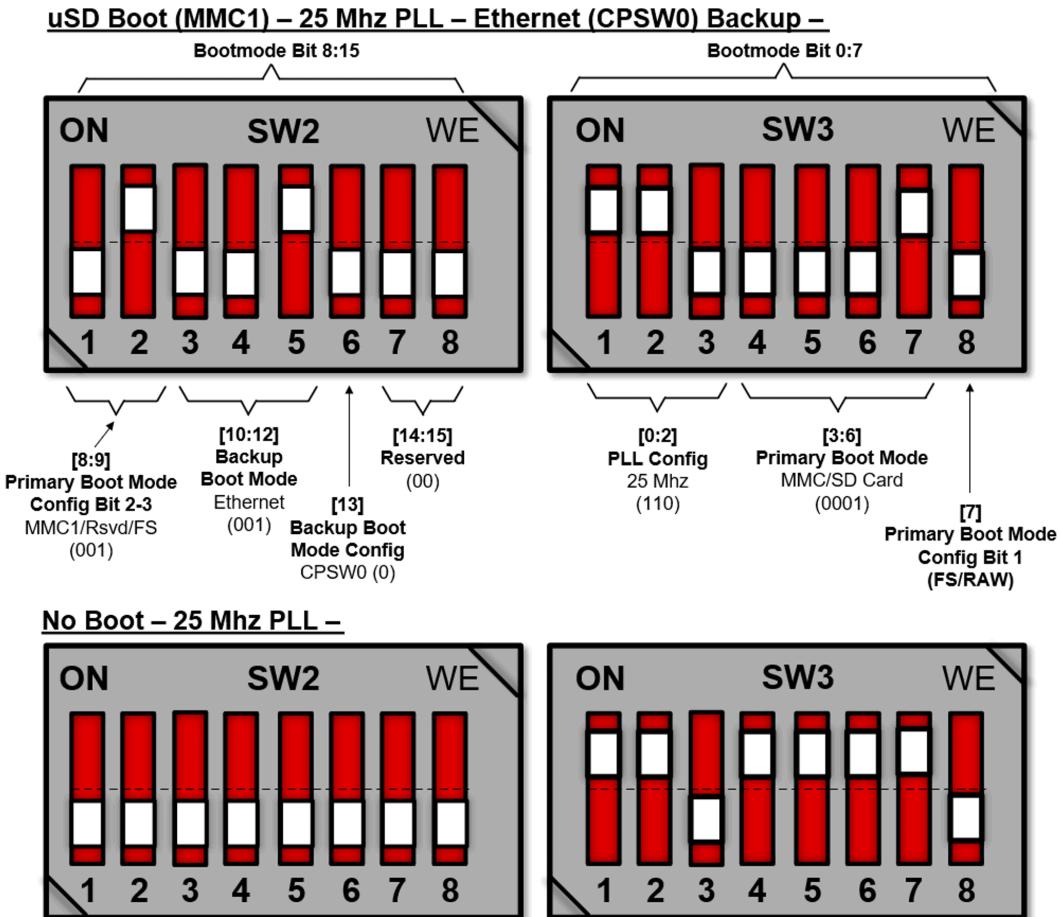

1. SK 評価基板ブートスイッチ セレクタ (SW1、SW2) を選択したブート モードに設定します。以下に、SD カードのブート モードおよびブートなしの例を示します。

2. ブート メディアを接続します (該当する場合)。

3. PD 対応の USB Type-C ケーブルを、SK 評価基板の Type-C (J11 または J13) コネクタに取り付けます。

4. Type-C ケーブルのもう一方の端を AC 電源アダプタまたは Type C ソース デバイス (ノートコンピュータなど) に接続します。

5. LD10 または LD12 の LED が点灯していることを目視で確認します。

6. XDS110JTAG と UART のデバッグ コンソール出力は、それぞれ micro-USB ポート J16 と J15 に接続されています。

uSD Boot (MMC1) – 25 Mhz PLL – Ethernet (CPSW0) Backup –

No Boot – 25 Mhz PLL –

図 2-8. SD ブート モードおよびブート スイッチなしの設定例

#### 2.4.2 電源オフの手順

1. AC/DC コンバータから AC 電源を切り離します。

2. SK 評価基板から USB Type-C ケーブルを取り外します。

#### 2.4.3 電力テスト ポイント

基板上の各電力出力のテスト ポイントを、以下の表に示します。

表 2-5. 電力テスト ポイント

| S 番号 | 電源          | テスト ポイント | 電圧     |

|------|-------------|----------|--------|

| 1    | VBUS_TYPEC1 | C398.1   | 5V-15V |

| 2    | VBUS_TYPEC2 | C415.1   | 5V-15V |

| 3    | VMAIN       | TP95     | 5V-15V |

| 4    | VCC_5V0     | TP70     | 5V     |

| 5    | VCC_3V3_SYS | TP51     | 3.3V   |

| 6    | VDD_2V5     | TP42     | 2.5V   |

| 7    | VPP_1V8     | TP31     | 1.8V   |

| 8    | VDD_1V0     | TP33     | 1.0V   |

| 9    | VDD_1V2     | TP10     | 1.2V   |

| 10   | VDDA1V8     | TP36     | 1.8V   |

**表 2-5. 電力テスト ポイント (続き)**

| S 番号 | 電源             | テスト ポイント | 電圧        |

|------|----------------|----------|-----------|

| 11   | VCC_1V8        | TP41     | 1.8V      |

| 12   | VDDSHV_SDIO    | TP29     | 1.8V/3.3V |

| 13   | VCC1V1_DDR     | TP40     | 1.1V      |

| 14   | VCC_CORE       | TP45     | 0.85V     |

| 15   | VDD_CORE       | TP46     | 0.85V     |

| 16   | VCC3V3_TA      | TP87     | 3.3V      |

| 17   | VCC3V3_XDS     | TP77     | 3.3V      |

| 18   | VCC_3V3_FT4232 | C482.1   | 3.3V      |

## 2.5 インターフェイス マッピング

**表 2-6. インターフェイス マッピング**

| インターフェイス名              | SoC 上のポート                                          | デバイス部品番号                                     |

|------------------------|----------------------------------------------------|----------------------------------------------|

| メモリ – OSPI             | OSPI0                                              | S28HS512TGABHM010                            |

| メモリ – Micro SD ソケット    | MMC1                                               | MEM2051-00-195-00-A                          |

| メモリ – eMMC             | MMC0                                               | MTFC32GAZAQHD-IT                             |

| メモリ – 基板 ID EEPROM     | SoC_I2C0                                           | AT24C512C-MAHM-T                             |

| イーサネット 1 – RGMII       | SoC_RGMII1                                         | DP83867IRRGZ                                 |

| イーサネット 2 – RGMII       | SoC_RGMII2                                         | DP83867IRRGZ                                 |

| LED ドライバー – 通信 LED 8 個 | WKUP_I2C0                                          | TPIC2810D                                    |

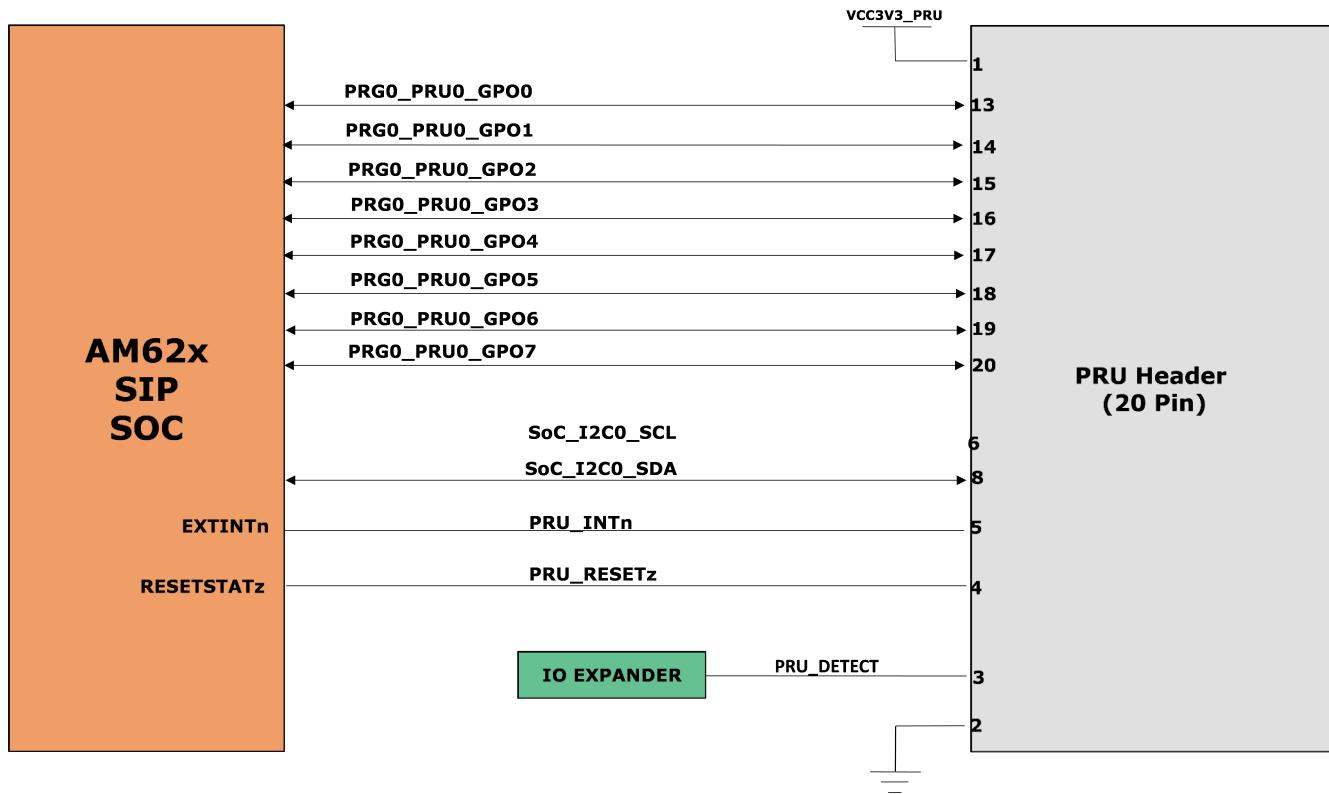

| PRU ヘッダー – 2x10 HDR    | PR0_PRU0_GPO, SoC_I2C0                             | PREC010DAAN-RC                               |

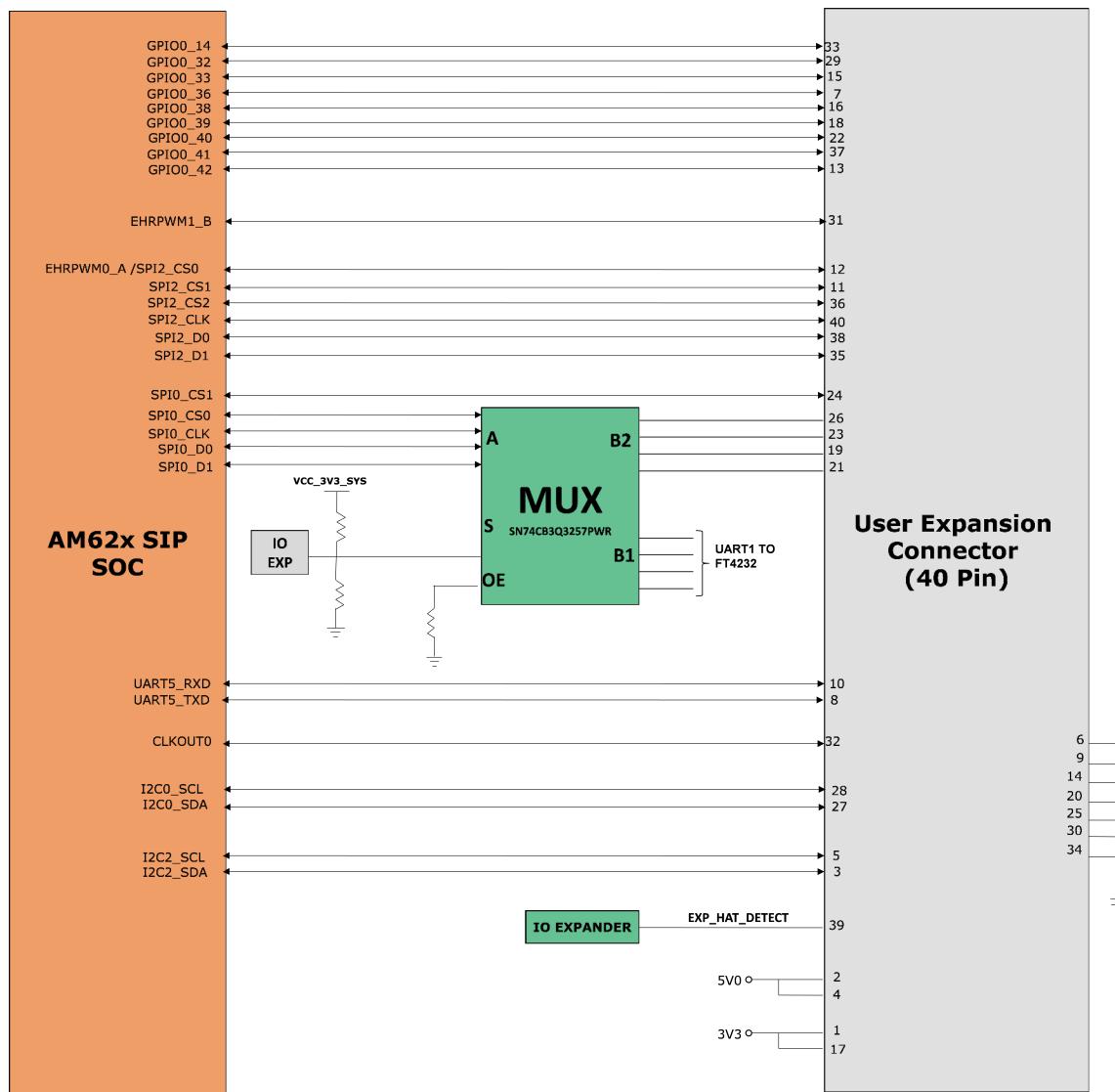

| ユーザー拡張コネクタ – 2x20 HDR  | SPI0, SPI2, UART5, SoC_I2C0, SoC_I2C2, GPIO        | PEC20DAAN                                    |

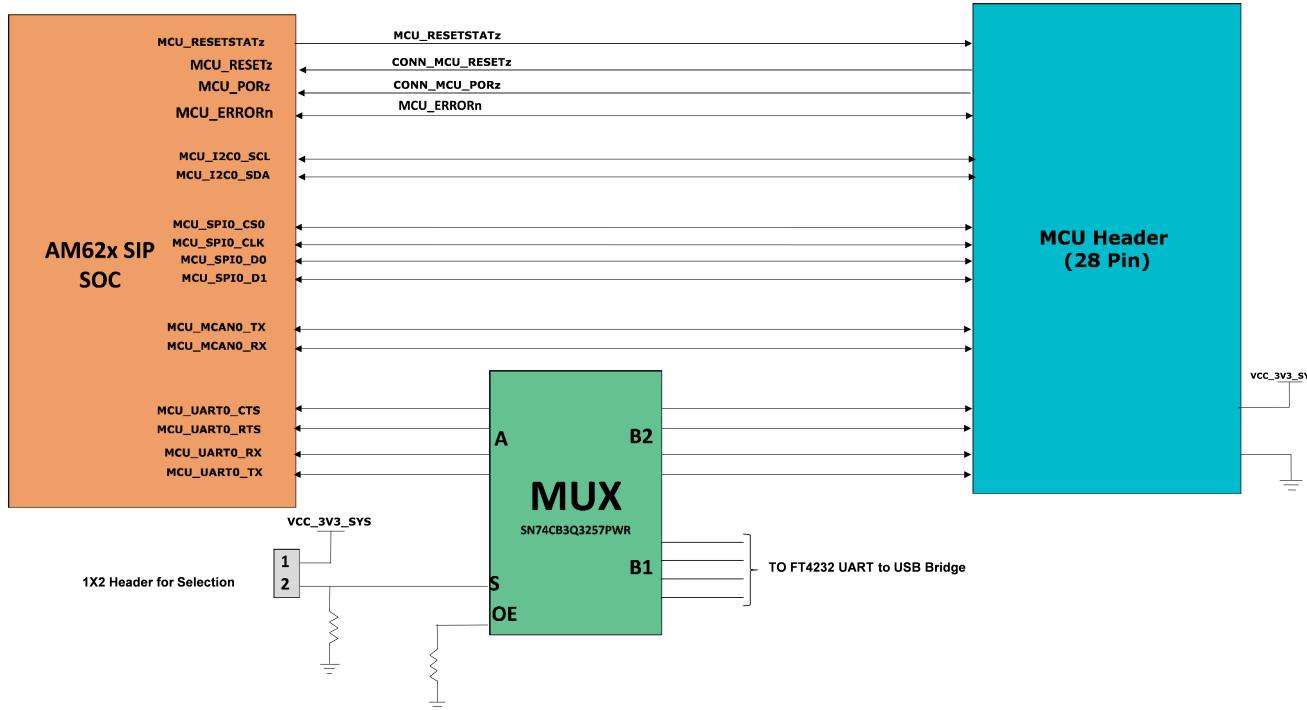

| MCU ヘッダー – 2x14 HDR    | MCU_UART0, MCU_MCAN0, MCU_SPI0, MCU_I2C0, MCU GPIO | PREC014DAAN-RC                               |

| USB-2.0 タイプ C          | USB0                                               | 2012670005                                   |

| USB-2.0 タイプ A          | USB1                                               | 629104151021                                 |

| LVDS ディスプレイ コネクタ       | OLDI0                                              | FFC2A32-40-T                                 |

| CSI インターフェイス           | CSI0                                               | 1-1734248-5                                  |

| HDMI                   | VOUT0                                              | Sil9022ACNU + TPD12S016PWR + 10029449-001RLF |

| オーディオ コーデック            | McASP2and SoC_I2C1                                 | TLV320AIC3106IRGZT+ SJ-43514-SMT             |

| GPIO ポート エクスパンダ        | SoC_I2C1                                           | TCA6424ARGJR                                 |

| UART 端子 (UART-to-USB)  | SoC_UART[1:0], WKUP_UART0, MCU_UART0               | FT4232HL+ 629105150521                       |

| テスト オートメーション ヘッダー      | SoC_I2C1                                           | FH12A-40S-0.5SH                              |

| 温度センサ                  | SoC_I2C1                                           | TMP100NA/3K                                  |

| 電流モニタ                  | SoC_I2C1                                           | INA231AIYFDR                                 |

| コネクティビティ – M.2 Key E   | MMC2, McASP1 および SoC_UART1                         | 2199119-4                                    |

## 2.6 クロック処理

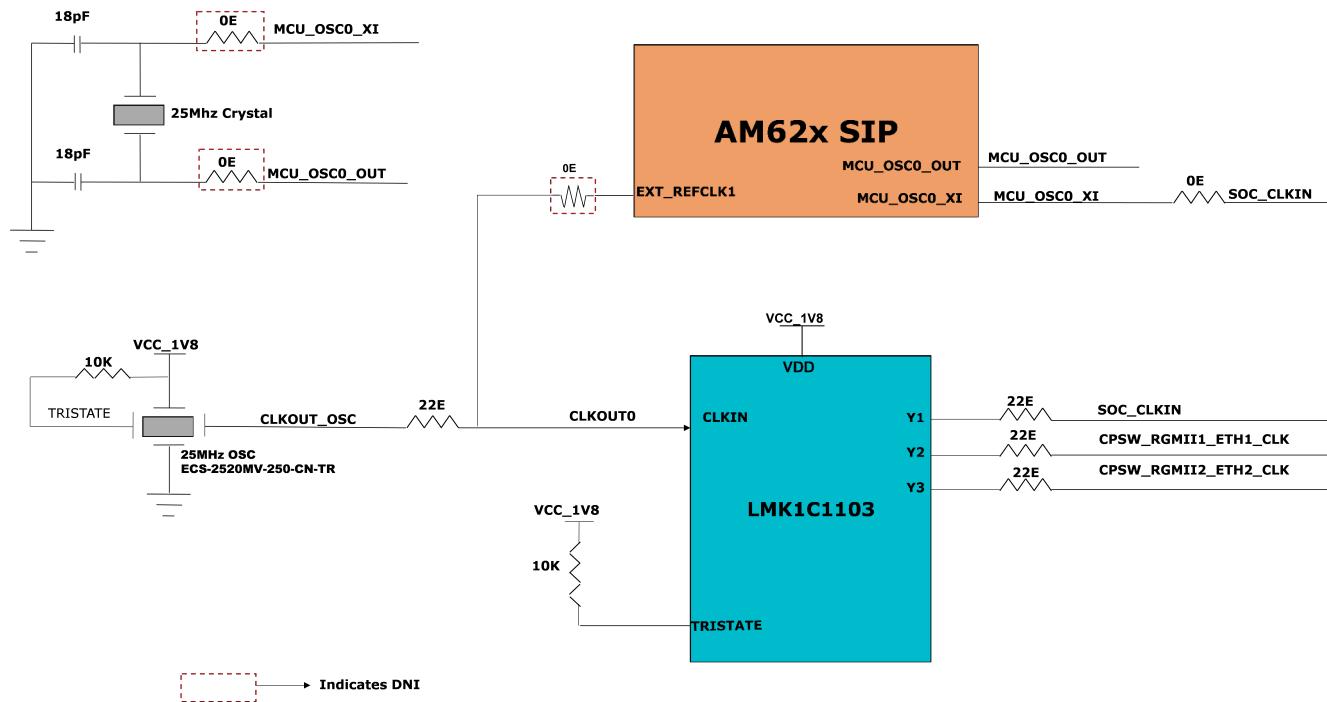

下の図は、AM62x SIP SK 評価基板のクロック アーキテクチャを示しています。

図 2-9. クロック アーキテクチャ

クロック ジェネレータ (型番 LMK1C1103PWR) は、SoC と 2 つのイーサネット PHY に 25MHz クロックを供給するためには使用されます。LMK1C1103PWR は 1:3 の LVCMS クロック バッファで、25MHz 水晶振動子 / LVCMS リファレンス入力を取り込み、3 つの 25MHz LVCMS クロックを出力します。クロック バッファのソースは、SoC からの CLKOUT0 ピンまたは 25MHz 発振器のいずれかであり、抵抗セットを使用して選択します。デフォルトでは、AM62x SIP SK 評価基板のクロック バッファへの入力として発振器が使用されます。クロック バッファの出力 Y2 と Y3 は、2 つのギガビットイーサネット PHY のリファレンス クロック入力として使用されます。

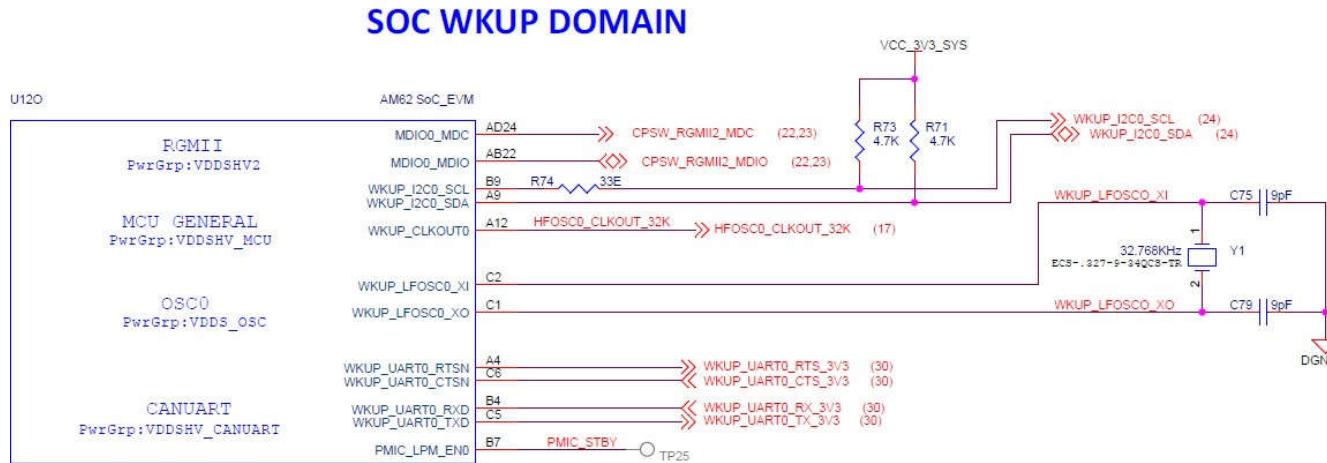

AM62x SIP SoC には、SoC (32.768KHz) の WKUP ドメインにクロックを供給するために、1 つの外部水晶振動子が取り付けられています。

図 2-10. SoC WKUP ドメイン

### 2.6.1 ペリフェラル リファレンス クロック

XDS110、FT4232、HDMI トランスミッタ、オーディオ コーデックなどのペリフェラルに必要なクロック入力は、個別の水晶振動子または発振器を使用してローカルで生成されます。評価基板のペリフェラルにリファレンス クロックを供給するために使用される水晶振動子または発振器を、下の表に示します。

表 2-7. クロック表

| ペリフェラル        | メーカー部品番号              | 説明                     | 周波数       |

|---------------|-----------------------|------------------------|-----------|

| XDS110 エミュレータ | XRCGB16M000FXN01R0    | CRY 16.000MHz 8pF SMD  | 16.000MHz |

| FT4232 ブリッジ   | ECS-120-18-30B-AGN-TR | CRY 12.000MHz 18pF SMD | 12.000MHz |

| オーディオ コーデック   | KC2520Z12.2880C1KX00  | OSC 12.288MHz CMOS SMD | 12.288MHz |

| HDMI トランスミッタ  | KC2520Z12.2880C1KX00  | OSC 12.288MHz CMOS SMD | 12.288MHz |

HDMI トランスミッタが必要とするクロックは、オンボード発振器 または SoC の AUDIO\_EXT\_REFCLK1 のいずれかから供給できます。これらは、抵抗マルチプレクサで選択できます。SoC の EXT\_REFCLK1 は、SK 評価基板のユーザー拡張コネクタにクロックを供給するために使用されます。M.2 モジュールへの 32.768KHz クロックは、電圧変換バッファを介して AM62x SIP SoC の WKUP\_CLKOUT0 によって供給されます。

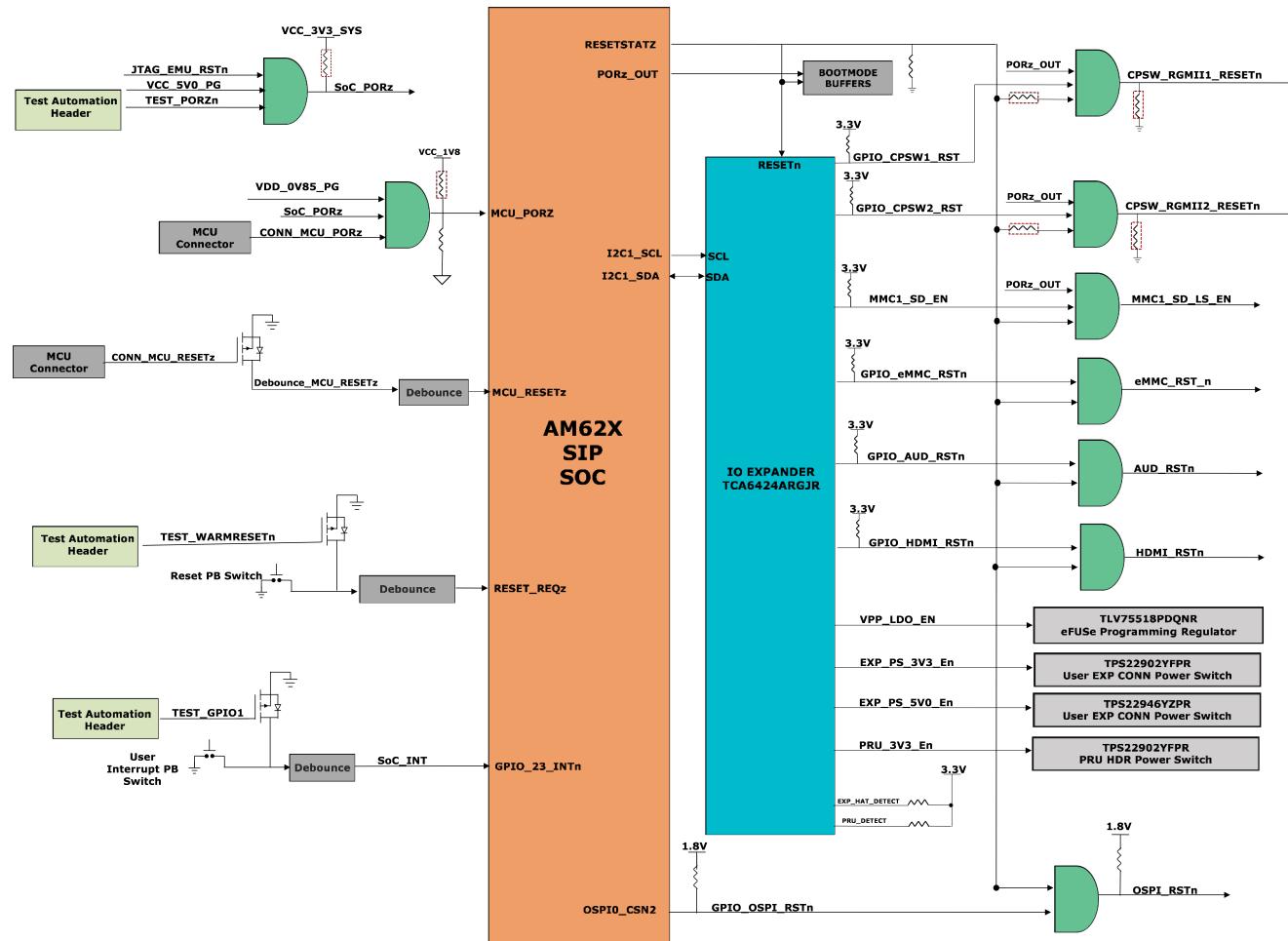

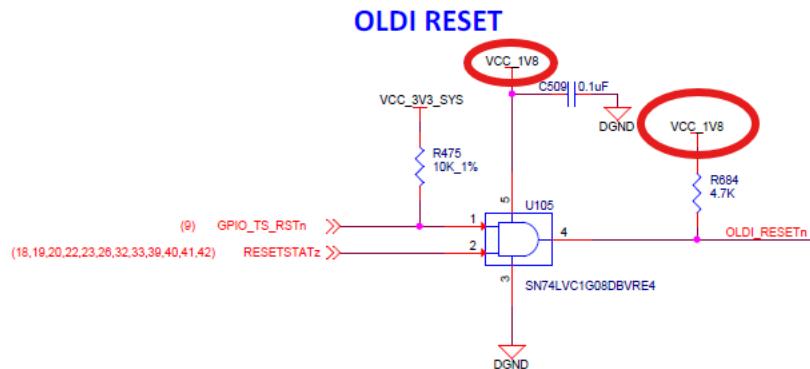

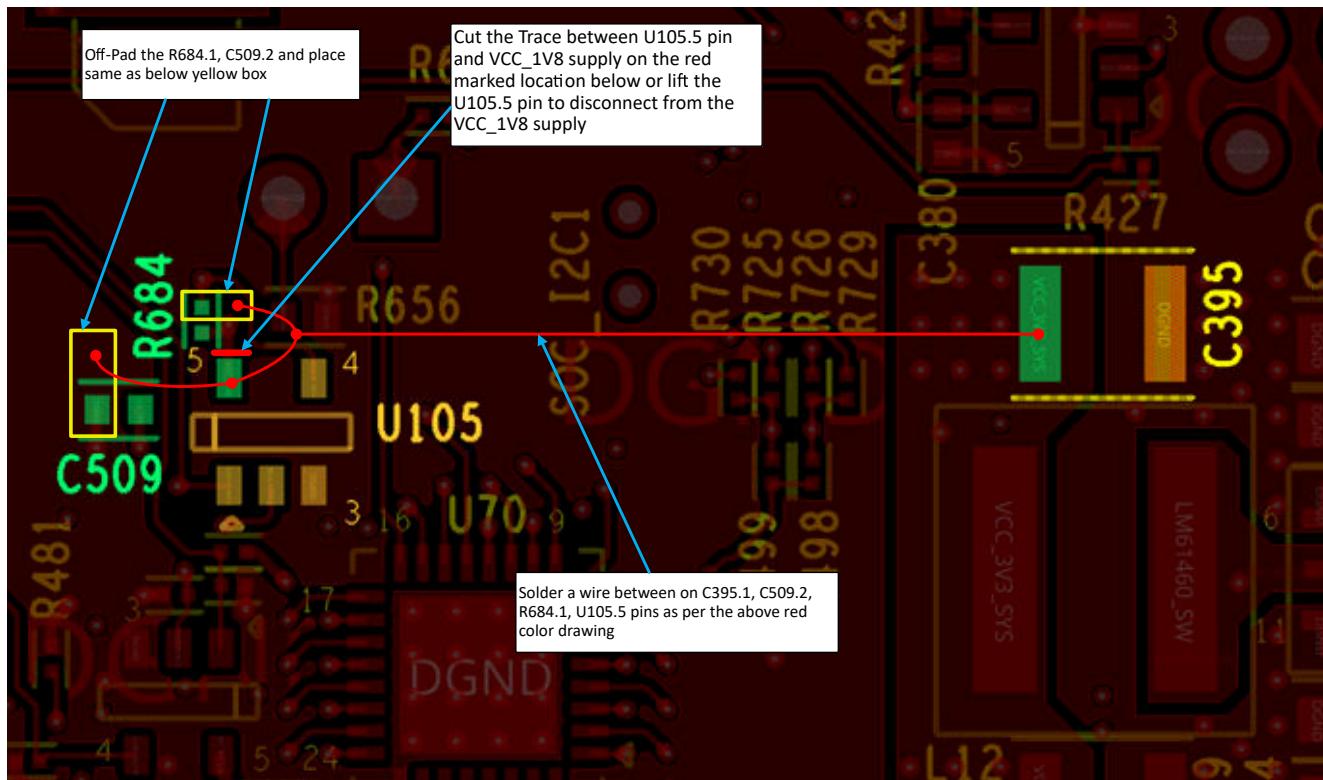

## 2.7 リセット

AM62x SIP SK 評価基板のリセットアーキテクチャを以下に示します。

SoC には次のリセット機能があります:

- **RESETSTATZ** は、マインドメインのウォームリセットステータス出力です

- **PORz\_OUT** は、マインドメインのパワーオンリセットステータス出力です

- **RESET\_REQZ** は、マインドメインのウォームリセット入力です

- **MCU\_PORz** は、MCU ドメインのパワーオン / コールドリセット入力です。

- **MCU\_RESETZ** は、MCU ドメインのウォームリセット入力です

- **MCU\_RESETSTATZ** は、MCU ドメインのウォームリセットステータス出力です。

パワーオンリセット時に、マインドメインに接続されているすべてのペリフェラル デバイスは **RESETSTATZ** によってリセットされます。

図 2-11. リセットアーキテクチャ

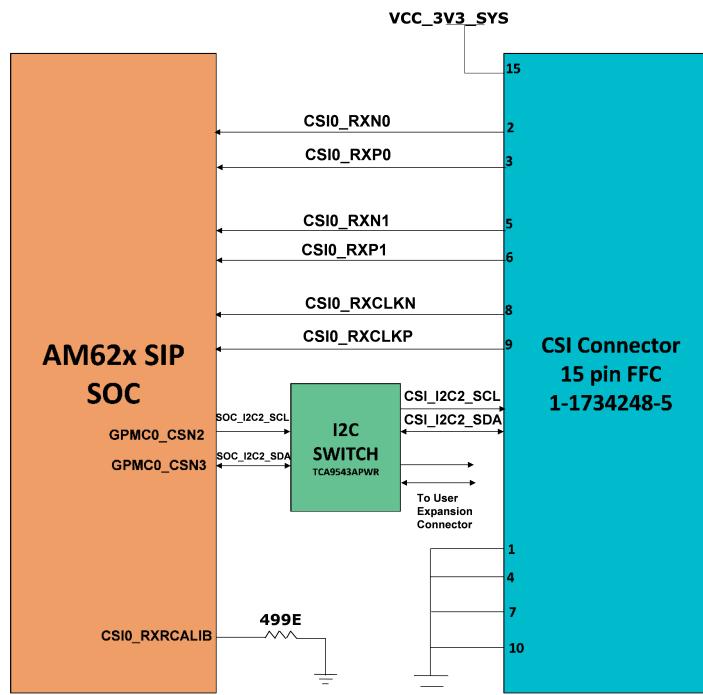

## 2.8 CSI インターフェイス

AM62x SIP SoC の CSI-2 インターフェイスは、RPi カメラ モジュールに対応した 15 ピンカメラ FPC コネクタ 1-1734248-5 に終端されています。これらのモジュールは、2 レーンの CSI RX 信号をサポートしています。SoC は 4 つの CSI RX レーンをサポートしていますが、SK 評価基板では 2 つのみがピンアウトされています。

CSI コネクタのピン配置は、RPi カメラコネクタと互換性があります。以下の表には、15 ピン CSI コネクタのピン配置が示されています。SoC I2C2 信号も CSI ヘッダーに接続されています。IO エクスパンダの GPIO 信号は、カメラ GPIO のものに接続されています。

図 2-12. CSI インターフェイス

表 2-8. CSI カメラコネクタ J19 のピン配置

| ピン番号。 | ピン構成         |

|-------|--------------|

| 1     | GND          |

| 2     | CSI0_RXN0    |

| 3     | CSI0_RXP0    |

| 4     | GND          |

| 5     | CSI0_RXN1    |

| 6     | CSI0_RXP1    |

| 7     | GND          |

| 8     | CSI0_RXCLKN  |

| 9     | CSI0_RXCLKP  |

| 10    | GND          |

| 11    | CSI_GPIO1    |

| 12    | CSI_GPIO2    |

| 13    | CSI_I2C2_SCL |

| 14    | CSI_I2C2_SDA |

| 15    | VCC_3V3_SYS  |

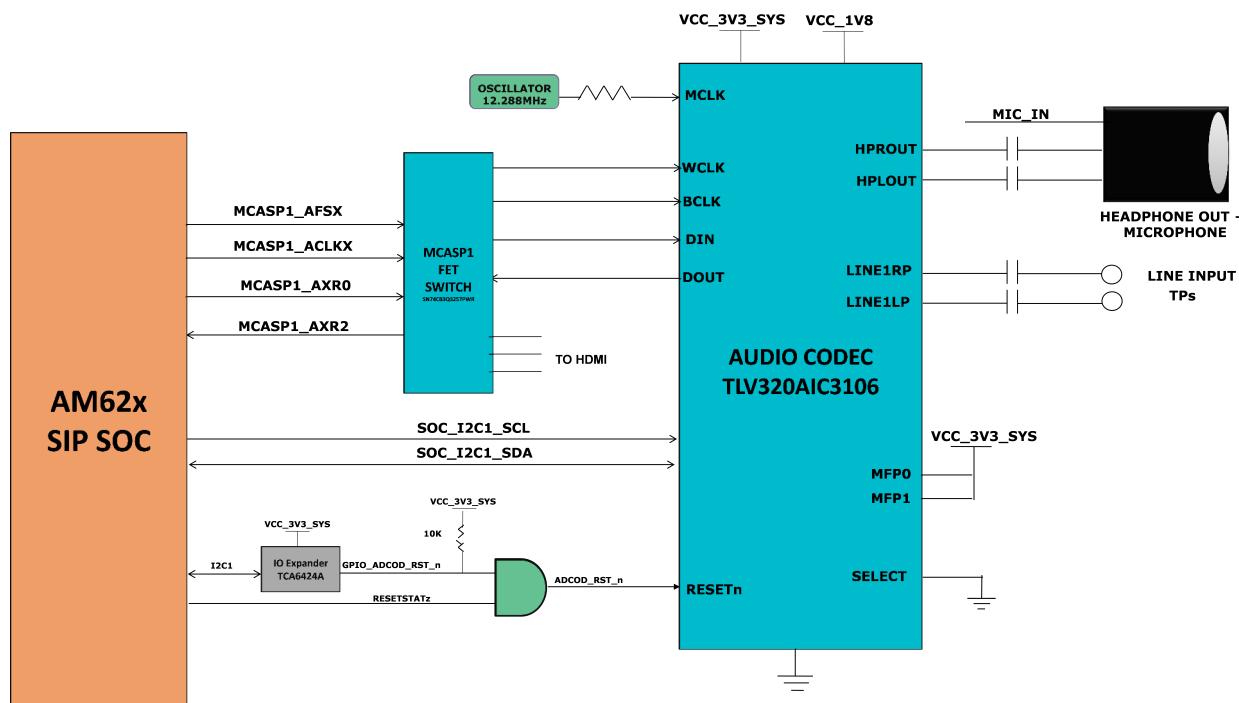

## 2.9 オーディオ コーデック インターフェイス

AM62x SIP SK 評価基板には、TI の低消費電力 TLV320AIC3106 ステレオ オーディオ コーデックが搭載されており、McASP 経由で AM62x SIP とのインターフェイスを確立しています。

TLV320AIC3106 は、ステレオ ヘッドフォン アンプを内蔵した低消費電力ステレオ オーディオ コーデックであり、シングル エンドまたは完全差動構成でプログラマブルな複数の入力と出力を備えています。TLV320AIC3106 の録音パスには、内蔵マイクロフォン バイアス、デジタル制御のステレオ マイク ブリアンプ、自動ゲイン制御 (AGC) が含まれており、複数のアナログ入力の間にミックス / マルチプレクサ 機能があります。ステレオ オーディオ DAC は、8kHz ~ 96kHz のサンプリング レートをサポートします。

MIC およびヘッドフォン出力用に、標準 3.5mm TRRS オーディオ ジャック コネクタ (メーカー型番 SJ-43514) が 1 つ提供されています。オーディオ コーデックのライン入力は、テスト ポイントで終端されています。

I2C を制御インターフェイスとして選択するには、選択ピンを "LOW" に保持する必要があります。コーデックは I2C インターフェイス経由で構成できます。この場合、ピン MFP0 と MFP1 ピンを High または Low に駆動することにより I2C アドレスを設定できます。これらのピンはどちらも High に設定されているため、デバイス アドレスは 0x1B に設定されています。オーディオ コーデックの未使用の入出力は、グランドに接続されています。

オーディオ コーデックへのコントローラ クロック入力である MCLK は、12.288MHz の発振器から供給されます。コーデックのオーディオ シリアル データ バス ビット クロック BCLK は、バッファを介して AM62x SIP SoC によって駆動されます。オーディオ シリアル データ バス入出力 DIN、DOUT は、バッファ経由で SoC の MCASP1\_AXR0 と MCASP1\_AXR2 に接続されます。RESETSTATz の AND 出力と、IO エクスパンダ 経由で供給される GPIO は、オーディオ コーデックをリセットするために使用されます。

TLV320AIC3106 は、3.3V のアナログ電源、1.8V のデジタル コア電源、3.3V のデジタル I/O 電源で動作します。

図 2-13. オーディオ コーデック インターフェイス

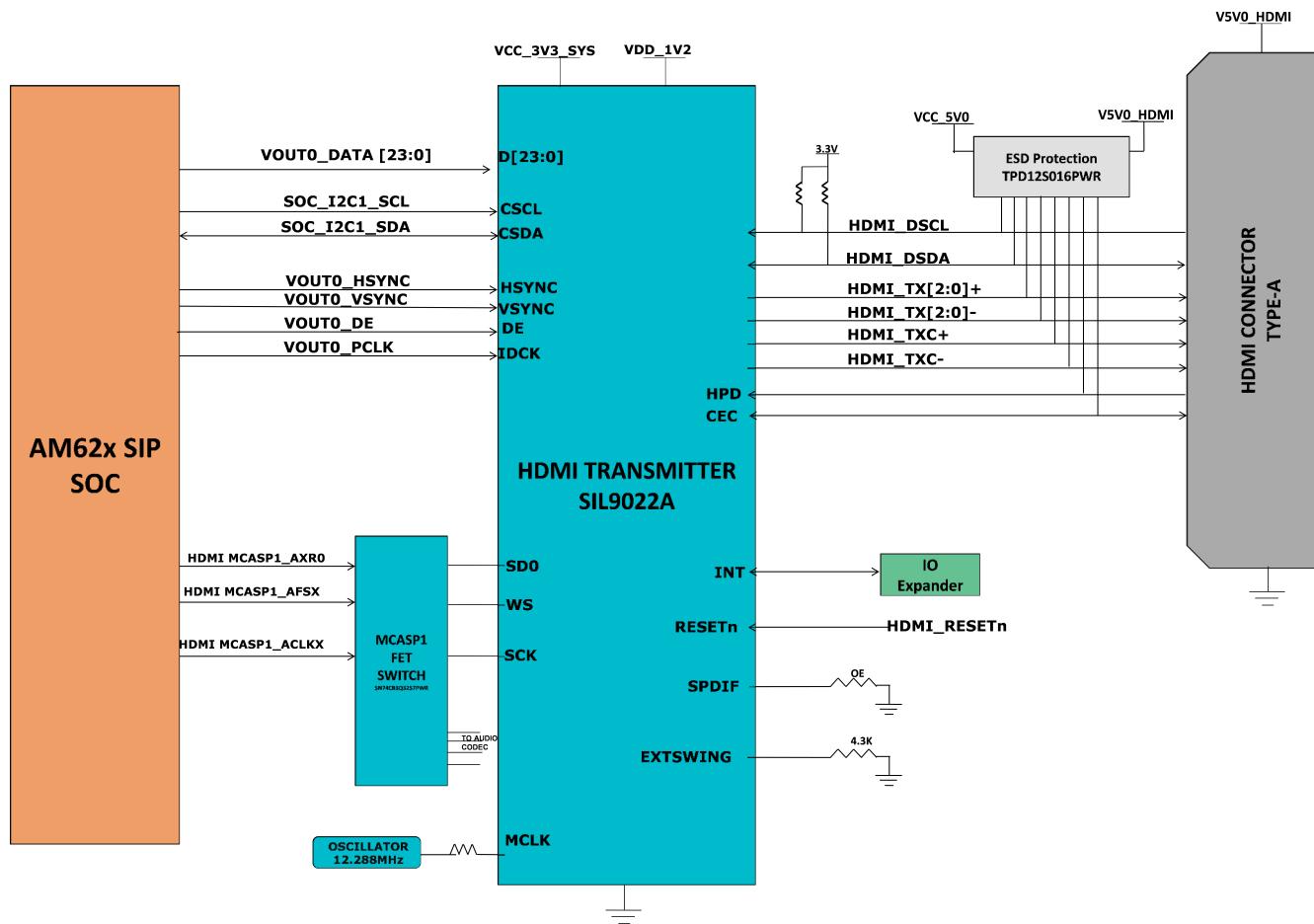

## 2.10 HDMI ディスプレイ インターフェイス

AM62x SIP SoC の DSS (ディスプレイサブシステム) は、SK 評価基板上で使用され、標準的な Type-A コネクタ経由で HDMI インターフェイスを実現します。この SK 評価基板は、Lattice Semiconductor の SiL9022A HDMI トランシッタを搭載しており、24 ビットのパラレル RGB DSS 出力ストリームおよび McASP を HDMI 準拠のデジタルオーディオ / ビデオ信号に変換します。

使用されるデータマッピング フォーマットは RGB888 です。データバス幅は 24 ビットです。

SoC\_I2C1 は、互換モードレジスタ、TPI レジスタ、CPI レジスタへアクセスするために、HDMI トランシッタに接続されています。SiL9022A を使用するには、SoC が I2C インターフェイスを介して SiL9022A を設定する必要があります。オーディオデータは、McASP1 インスタンスを介して SoC から HDMI トランシッタに送信されます。HDMI\_I2C バスは、接続されたシンクデバイスの EDID と HDCP データにアクセスします。

TMDS 差動データペアとトランシッタからの差動クロック信号は、HDMI ESD デバイス (メーカー型番 TPD12S016PWR) 経由で HDMI コネクタに接続されています。このデータは、オンボードの 5V 電源から HDMI コネクタに供給される電流を制限するロードスイッチとしても機能します。

HDMI フレーマには、3.3V ボード IO 電源と専用 LDO (メーカー型番 TLV75512PDQNR) から供給される 1.2V で給電されます。

図 2-14. HDMI インターフェイス

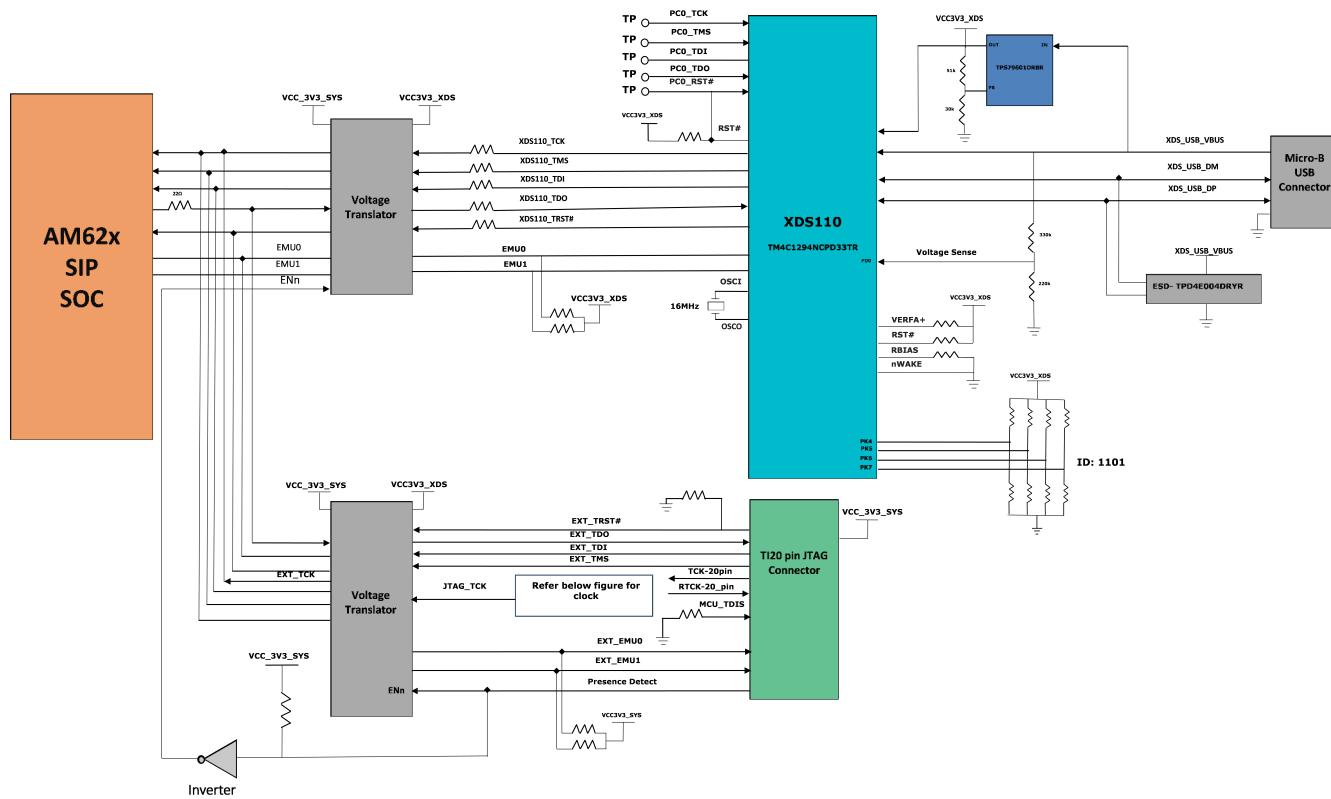

## 2.11 JTAG インターフェイス

AM62x SIP SK 評価基板には、XDS110 クラスのオンボード エミュレーションが搭載されています。このエミュレータの接続には USB 2.0 micro-B コネクタが使用され、回路はバス電源供給方式の USB デバイスとして機能します。コネクタからの VBUS 電源はエミュレーション回路に電源として使用されているため、SK 評価基板の電源が切り離されてもエミュレータへの接続が失われることはありません。電圧変換バッファは、XDS110 回路を SK 評価基板の他の部分から分離するために使用されます。

オプションとして、SK 評価基板の JTAG インターフェイスは、20 ピンの標準 JTAG cTI ヘッダ J17 を通じても提供されます。これにより、外部 JTAG エミュレータケーブルを接続することができます。電圧変換バッファは、cTI ヘッダの JTAG 信号を SK 評価基板の他の部分から分離するために使用されます。XDS110 セクションと cTI ヘッダー セクションの電圧トランスレータの出力はマルチプレクサによって切り替えられ、AM62x SIP の JTAG インターフェイスに接続されています。存在検出回路を使用して cTI 20 ピン JTAG コネクタへの接続が検出されると、マルチプレクサはオンボードのエミュレーション回路の代わりに cTI コネクタからの 20 ピン信号を AM62x SIP SoC にルーティングします。

図 2-15. JTAG インターフェイス

以下の表に、cTI 20 ピン JTAG コネクタのピン配列を示します。USB 信号には、ESD 電流パルスを VCC または GND に誘導する ESD 保護デバイス (型番 TPD4E004) が搭載されています。TPD4E004 は、IEC 61000-4-2 で規定されている最大  $\pm 15\text{kV}$  の人体モデル (HBM) の ESD パルスから保護し、 $\pm 8\text{kV}$  の接触放電と  $\pm 12\text{kV}$  のエアギャップ放電を提供します。

**表 2-9. JTAG コネクタ (J17) のピン配置**

| ピン番号。 | 信号             |

|-------|----------------|

| 1     | JTAG_TMS       |

| 2     | JTAG_TRST#     |

| 3     | JTAG_TDI       |

| 4     | JTAG_TDIS      |

| 5     | VCC3V3_SYS     |

| 6     | NC             |

| 7     | JTAG_TDO       |

| 8     | SEL_XDS110_INV |

| 9     | JTAG_cTI_RTCK  |

| 10    | DGND           |

| 11    | JTAG_cTI_TCK   |

| 12    | DGND           |

| 13    | JTAG_EMU0      |

| 14    | JTAG_EMU1      |

| 15    | JTAG_EMU_RSTn  |

| 16    | DGND           |

| 17    | NC             |

| 18    | NC             |

| 19    | NC             |

| 20    | DGND           |

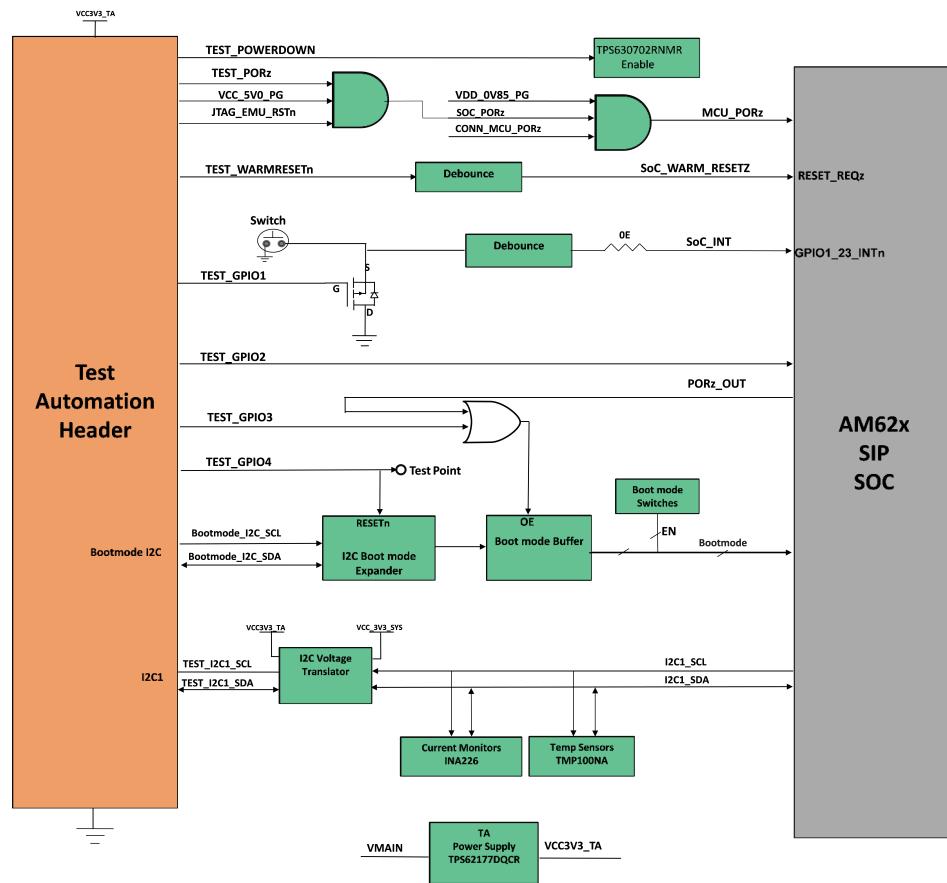

## 2.12 テストオートメーション ヘッダー

AM62x SIP SK 評価基板は、40 ピンのテストオートメーション ヘッダー (FH12A-40S-0.5SH) を搭載しており、パワーダウン、POR、ウォームリセット、ブートモード制御などの基本動作を外部コントローラで操作できます。

テストオートメーション回路は、専用レギュレータ (メーカー型番: TPS62177DQCR) から生成された 3.3V 電源によって駆動されます。SoC の I2C1 は、テストオートメーション ヘッダーに接続されています。テストオートメーション ヘッダーのもう一つの I2C インスタンス (BOOTMODE\_I2C) は、24 ビット I2C ブートモード IO エクスパンダ (メーカー型番 TCA6424ARGJR) に接続されており、AM62x SIP SoC のブートモードを制御できます。

テストオートメーション回路には電圧変換回路があり、コントローラは AM62x SIP で使用される IO 電圧から絶縁されています。AM62x SIP のブートモードは、ユーザーが DIP スイッチ、または I2C IO エクスパンダ経由のテストオートメーション ヘッダーを使用して制御する必要があります。ブートモードバッファは、DIP スイッチまたは I2C IO エクスパンダによって駆動されるブートモード制御を分離するために使用されます。ブートモードは、ボード上の 2 つの 8 ビット DIP スイッチを使用して制御することができ、スイッチが ON 位置に設定されている場合はプルアップ抵抗をバッファの出力に、OFF 位置に設定されている場合は弱いプルダウン抵抗に接続します。バッファの出力は AM62x SIP SoC のブートモードピンに接続され、リセットサイクル中にブートモードが必要な場合にのみ出力が有効になります。

テストオートメーション ヘッダーによってブートモードを設定する場合、必要なスイッチ値が I2C IO エクスパンダ出力に設定されます。これにより、DIP スイッチ値が上書きされ、SoC に目的のブート値が与えられます。ブートモード用に使用されるピンにはそれ以外の機能もあるため、これらは、通常動作時にブートモードバッファをディスエーブルにすることによって分離されます。

テストオートメーション ヘッダーからのパワーダウン信号は、ボード上の専用電源を除くすべてのレールをパワーダウンするように SK 評価基板に指示します。同様に、PORn 信号は SoC にハードリセットを行い、WARM\_RESETn は SoC にウォームリセットを行います。テストオートメーション ヘッダーからの 1 つの割り込み信号は、SoC GPIO (GPIO1\_23) にルーティングされ、外部割り込みを提供します。

図 2-16. テストオートメーション

**表 2-10. テストオートメーションコネクタ (J23) のピン配列**

| ピン番号。 | 信号        | IO 方向 | ピン番号。 | 信号               | IO 方向 |

|-------|-----------|-------|-------|------------------|-------|

| 1     | VCC3V3_TA | 電源    | 21    | NC               | 該当なし  |

| 2     | VCC3V3_TA | 電源    | 22    | NC               | 該当なし  |

| 3     | VCC3V3_TA | 電源    | 23    | NC               | 該当なし  |

| 4     | NC        | 該当なし  | 24    | NC               | 該当なし  |

| 5     | NC        | 該当なし  | 25    | DGND             | 電源    |

| 6     | NC        | 該当なし  | 26    | TEST_POWERDOWN   | 入力    |

| 7     | DGND      | 電源    | 27    | TEST_PORz        | 入力    |

| 8     | NC        | 該当なし  | 28    | TEST_WARMRESETn  | 入力    |

| 9     | NC        | 該当なし  | 29    | NC               | 該当なし  |

| 10    | NC        | 該当なし  | 30    | TEST_GPIO1       | 双方向   |

| 11    | NC        | 該当なし  | 31    | TEST_GPIO2       | 双方向   |

| 12    | NC        | 該当なし  | 32    | TEST_GPIO3       | 入力    |

| 13    | NC        | 該当なし  | 33    | TEST_GPIO4       | 入力    |

| 14    | NC        | 該当なし  | 34    | DGND             | 電源    |

| 15    | NC        | 該当なし  | 35    | NC               | 該当なし  |

| 16    | DGND      | 電源    | 36    | SoC_I2C1_TA_SCL  | 双方向   |

| 17    | NC        | 該当なし  | 37    | BOOTMODE_I2C_SCL | 双方向   |

| 18    | NC        | 該当なし  | 38    | SoC_I2C1_TA_SDA  | 双方向   |

| 19    | NC        | 該当なし  | 39    | BOOTMODE_I2C_SDA | 双方向   |

| 20    | NC        | 該当なし  | 40    | DGND             | 電源    |

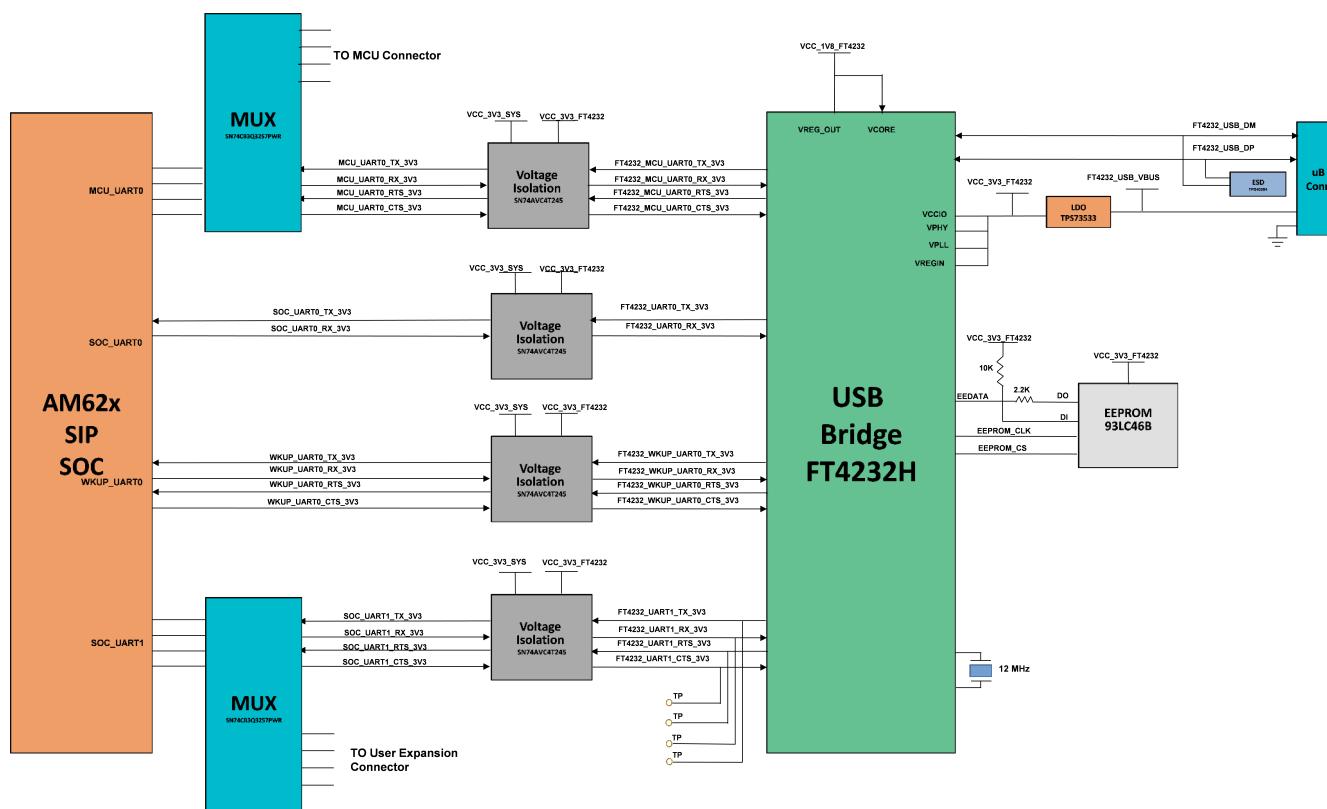

## 2.13 UART インターフェイス

AM62x SIP が提供する SoC の 4 つの UART ポート (MCU UART0, WKUP UART0, SoC UART0, SoC UART1) は、UART-to-USB 機能を実現するために FTDI ブリッジ FT4232HL とインターフェースされ、基板上の micro-B USB コネクタ (J15) で終端されています。USB ケーブルを使用して AM62x SIP SK 評価基板をホストに接続すると、コンピュータは仮想 COM ポートを確立でき、任意の端末エミュレーション アプリケーションで使用できます。FT4232HL はバス電源供給方式です。

この回路はバスから電源供給されているため、SK 評価基板の電源が切り離されても COM ポートへの接続が失われることはありません。

表 2-11. UART ポート インターフェイス

| UART ポート   | USB から UART へのブリッジ | USB コネクタ | COM ポート |

|------------|--------------------|----------|---------|

| SoC_UART0  |                    |          | COM1    |

| SoC_UART1  |                    |          | COM2    |

| WKUP_UART0 | FT4232HL           | J15      | COM3    |

| MCU_UART0  |                    |          | COM4    |

FT4232 チップは、接続された外部 SPI EEPROM からの構成ファイルを使用して、シングル チップ USB から 4 チャネル UART モードで動作するよう構成されています。EEPROM (93LC46B) は、1Mbit/s のクロック レートに対応しています。EEPROM は、FTDI の Web サイトから入手できる FT\_PROG というユーティリティ プログラムを使用して、USB 経由で回路内でプログラム可能です。FT\_PROG は、1 つまたは複数の基板がコンピュータに接続されているときに、ユーザーが基板のシリアル番号を使用して接続されている COM ポートを識別できるように、基板のシリアル番号をプログラムするためにも使用されます。

図 2-17. UART インターフェイス

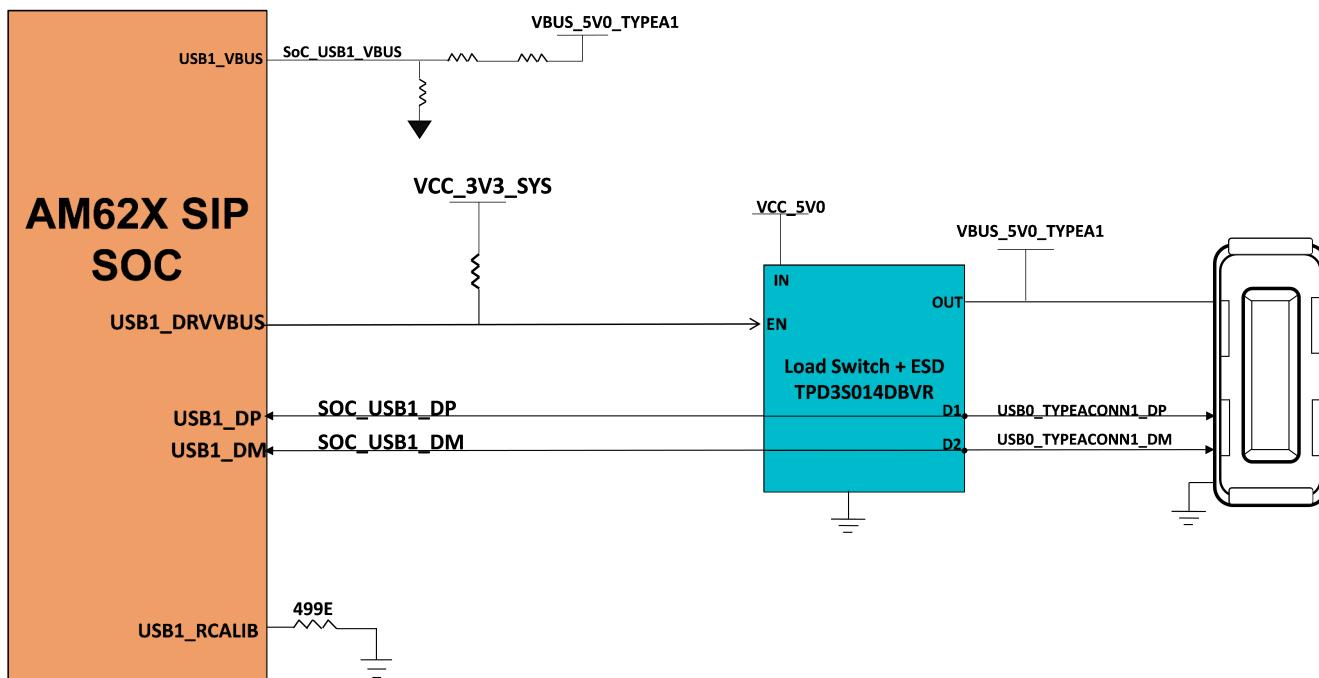

## 2.14 USB インターフェイス

### 2.14.1 USB 2.0 タイプA インターフェイス

SK 評価基板では、USB 2.0 ホストインターフェイスが、Type-A コネクタ (メーカー型番 629104151021) を使用した Type-A ポート経由で提供されます。AM62x SIP SoC の USB1 ポートは、USB 2.0 Type-A ホストインターフェイスとして使用されます。

Type-A コネクタからの USB データラインは、電流制限ロードスイッチと ESD 保護 IC (メーカー型番 TPD3S014DBVR) に接続されています。このスイッチは、電流を 500mA に制限し、IEC 61000-4-2 で規定されている最大レベルを上回る ESD 衝撃を吸収します。

図 2-18. USB 2.0 タイプA インターフェイス

## 2.14.2 USB 2.0 Type C インターフェイス

SK 評価基板では、USB Type-C コネクタ J13 (メーカー型番 2012670005) によって USB 2.0 インターフェイスが提供され、最大 480Mbps のデータレートに対応しています。J13 はデータ通信と電源コネクタとしても使用します。J13 は、PD コントローラ TPS65988DHRSHR IC を使用して DRP ポートとして構成されているため、ホストとしてもデバイスとしても動作できます。ポートのパワー ロールは、コネクタに接続されるデバイスのタイプと、そのデバイスがシンクまたはソースのどちらであるかによって決まります。ポートが DFP として機能している場合、500mA で最大 5V を供給できます。

PD コントローラの GPIO は、SoC の USB0\_DRVVBUS ピンに接続され、J13 Type-C コネクタに接続されているデバイスのデータ ロールを示します。この GPIO は、J13 コネクタのホスト / デバイスの動作に応じて High / Low を出力するように構成されています。

J13 からの USB2.0 データラインの DP と DM は、チョークおよび ESD 保護デバイスを介して、AM62x SIP SoC の USB0 インターフェイスに接続されています。SoC への USB0\_VBUS は、抵抗デバイダ ネットワークを介して供給されます。

EMI / EMC に対処するため、USB データラインにはコモン モード チョーク (メーカー型番 DLW21SZ900HQ2B) が配置されています。USB2.0 DP/DM 信号の ESD 衝撃を放散させるため、ESD 保護デバイス (型番 ESD122DMXR) が搭載されています。CC 信号には ESD 保護デバイス (部品番号 TPD1E01B04DPLT) が搭載されており、ESD 衝撃を放散させるため、Type-C コネクタ J13 の VBUS レールには TVS2200DRV IC が組み込まれています。

図 2-19. USB 2.0 Type C インターフェイス

## 2.15 メモリ インターフェイス

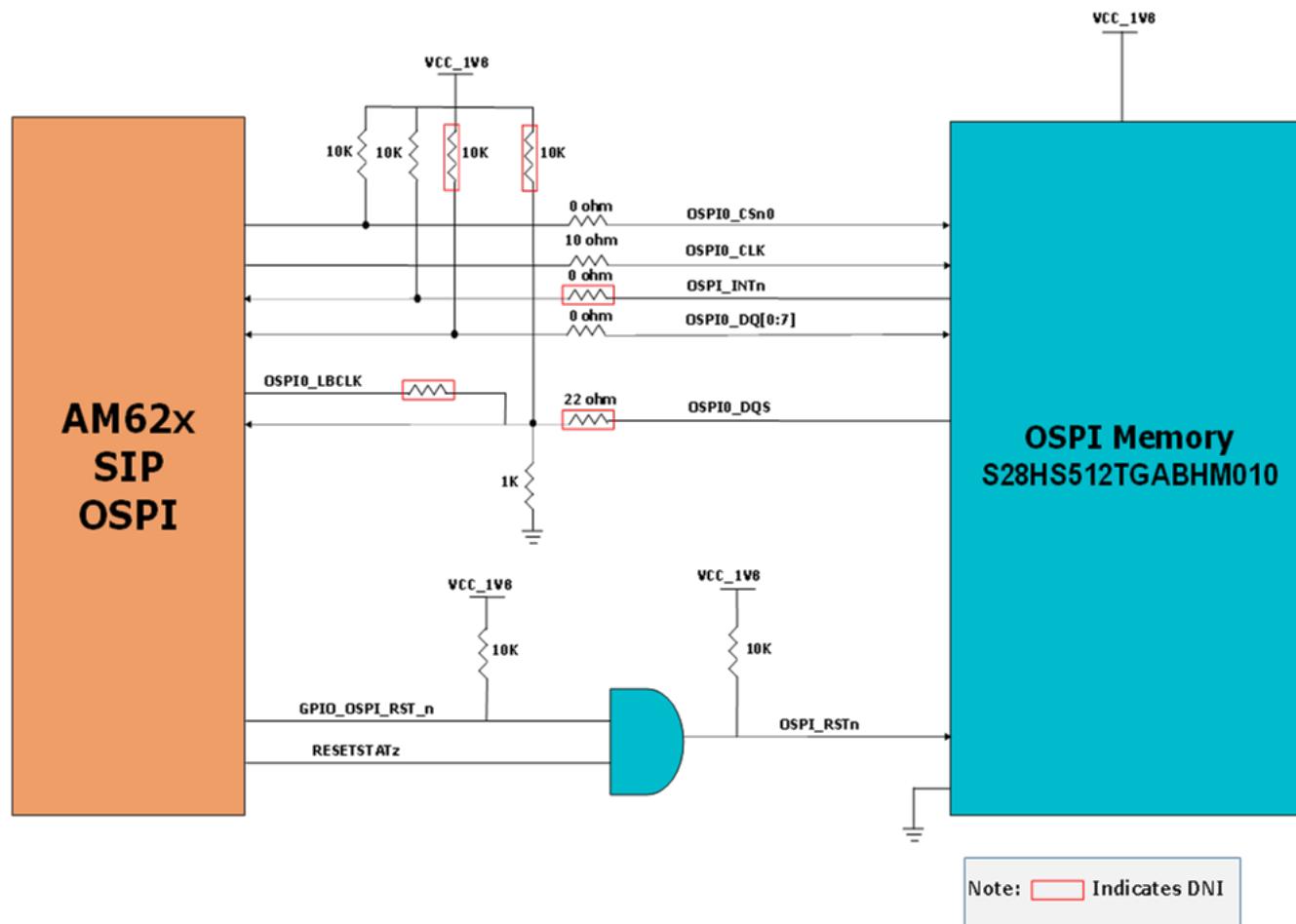

### 2.15.1 OSPI インターフェイス

AM62x SIP SK 評価基板は、AM62x SIP SoC の OSPI インターフェイスに接続された 512Mbit OSPI メモリ デバイス (Cypress 型番 S28HS512TGABHM010) を搭載しています。OSPI インターフェイスは、最高 200MBps SDR および 400MBps DDR (クロック速度 200MHz) のメモリ速度でシングル データレートおよびダブル データレートに対応しています。

OSPI および QSPI の実装: DATA[7:0]、DQS、INT#、および CLK 信号には  $0\Omega$  抵抗が設けられています。バスのプローティングを防ぐため、DATA[7:0] には外部プルアップ抵抗を実装できるフットプリントが用意されています。OSPI メモリのフットプリントでは、QSPI メモリまたは OSPI メモリのいずれかを取り付けることもできます。QSPI フラッシュを実装する場合は、OSPI\_DATA[4:7] ピンに配置された  $0\Omega$  の直列抵抗を取り外します。

リセット: OSPI フラッシュのリセットは、AM62x の RESETSTAT<sub>z</sub> と SoC GPIO の GPIO\_OSPI\_RSTn 信号を論理積する回路に接続されています。これは、ウォーム リセットおよびコールド リセットに適用されます。デフォルトのアクティブ状態を設定するために、SoC ピンからの GPIO\_OSPI\_RSTn にプルアップが提供されています。

電源: OSPI フラッシュは 1.8V IO 電源から電力を供給されます。1.8V 電源は、OSPI フラッシュ メモリの VCC ピンと VCCQ ピンの両方に供給されます。

SoC の OSPI は、SoC の VDDSHV1 電源グループから電力を供給され、1.8V IO 電源に接続されています。

図 2-20. OSPI

## 2.15.2 MMC インターフェイス

AM62x SIP SoC には、3 つの MMC ポート (MMC0、MMC1、MMC2) があります。MMC0 は eMMC フラッシュに接続されており、MMC1 は基板上の Micro SD ソケットとインターフェイスされ、MMC2 は Wi-Fi および BT インターフェイス用の M.2 モジュールに接続されています。

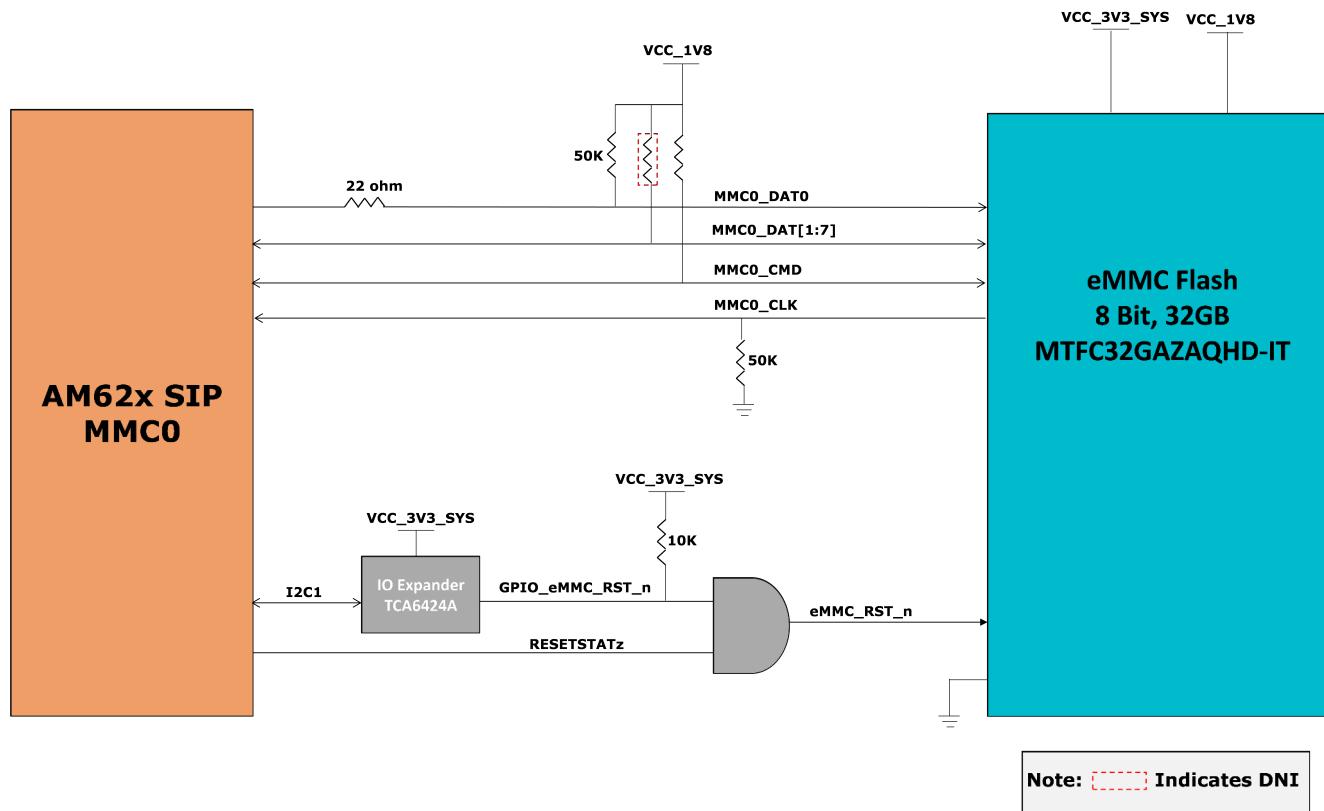

### 2.15.2.1 MMC0 - eMMC インターフェイス

この SK 評価基板には、AM62x SIP SoC の MMC0 ポートに接続された 32GB eMMC フラッシュメモリ (Micron、型番 MTFC32GAZAQHD-IT) が搭載されています。このフラッシュは、最大 200MHz の HS400 ダブルデータレートをサポートする MMC0 インターフェイスの 8 ビットに接続されています。

eMMC デバイスには、NAND メモリ用の 3.3V、eMMC インターフェイス用の 1.8V の 2 つの電源が必要です。SoC の MMC0 インターフェイスは、1.8V IO 電源に接続された VDDSHV4 電源ドメインから電力が供給されます。

図 2-21. eMMC インターフェイス

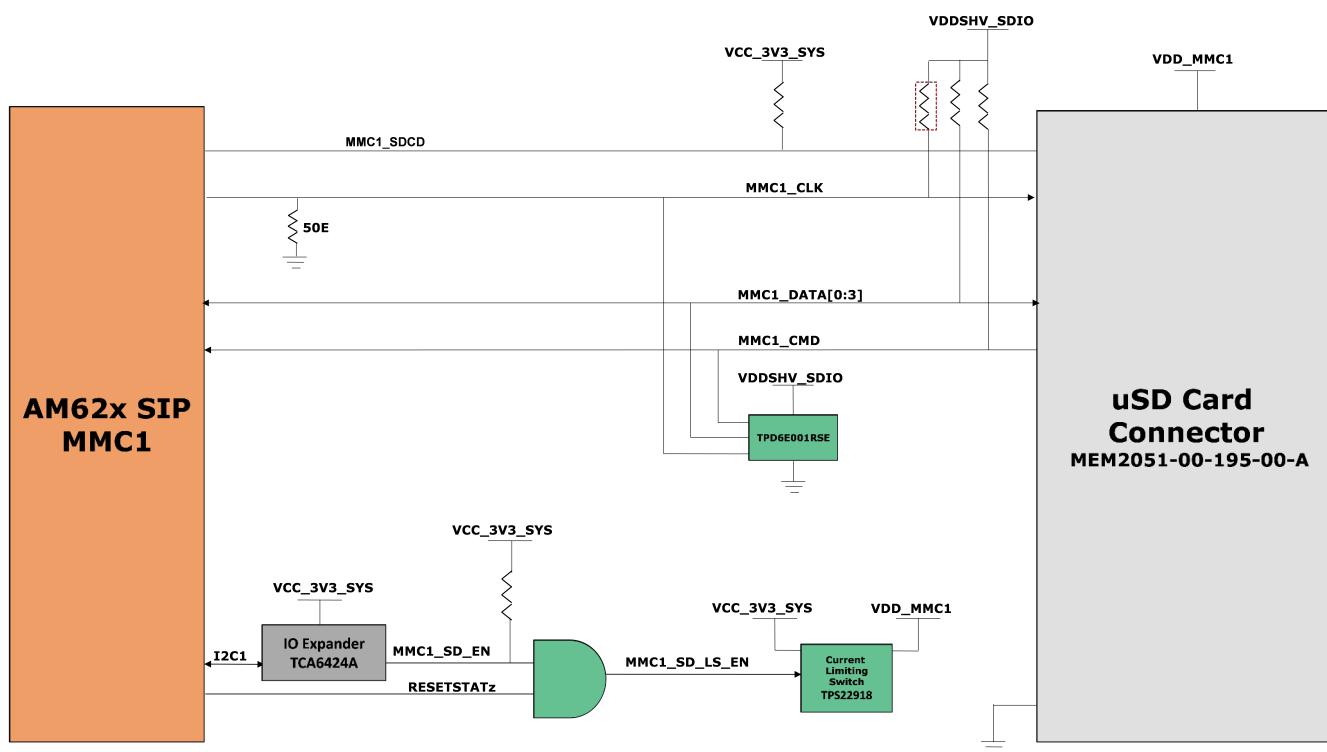

### 2.15.2.2 MMC1 — マイクロ SD インターフェイス

この SK 評価基板は、AM62x SIP SoC の MMC1 ポートに接続された micro SD カード インターフェイスを提供します。MicroSD カード ソケット (メーカー 型番 MEM2051-00-195-00-A) は、この SoC の MMC1 ポートとのインターフェイスに使用されます。1.8V と 3.3V の両方での IO 動作を含む UHS1 動作がサポートされています。マイクロ SD カード インターフェイスは、デフォルトで SD モードで動作するように設定されています。高速カードの場合、SoC の ROM コードはカードとコントローラがサポートできる最速の速度を検出しようと試み、1.8V への切り替えを行うことができます。

SD カード コネクタの電源は、ロード スイッチ (メーカー型番 TPS22918DBVR) を使用して提供され、RESETSTATz、PORz\_OUT、IO エクスパンダの GPIO 出力の論理積によって制御されます。データ信号、クロック信号、コマンド信号用に、ESD 保護デバイス (部品番号 TPD6E001RSE) が搭載されています。TPD6E001RSE は TVS ダイオードを内蔵したライン終端デバイスで、IEC 61000-4-2 に準拠したシステム レベルの ESD 保護、±8kV の接触放電、±15kV のエアギヤップ放電を提供します。

図 2-22. Micro SD インターフェイス

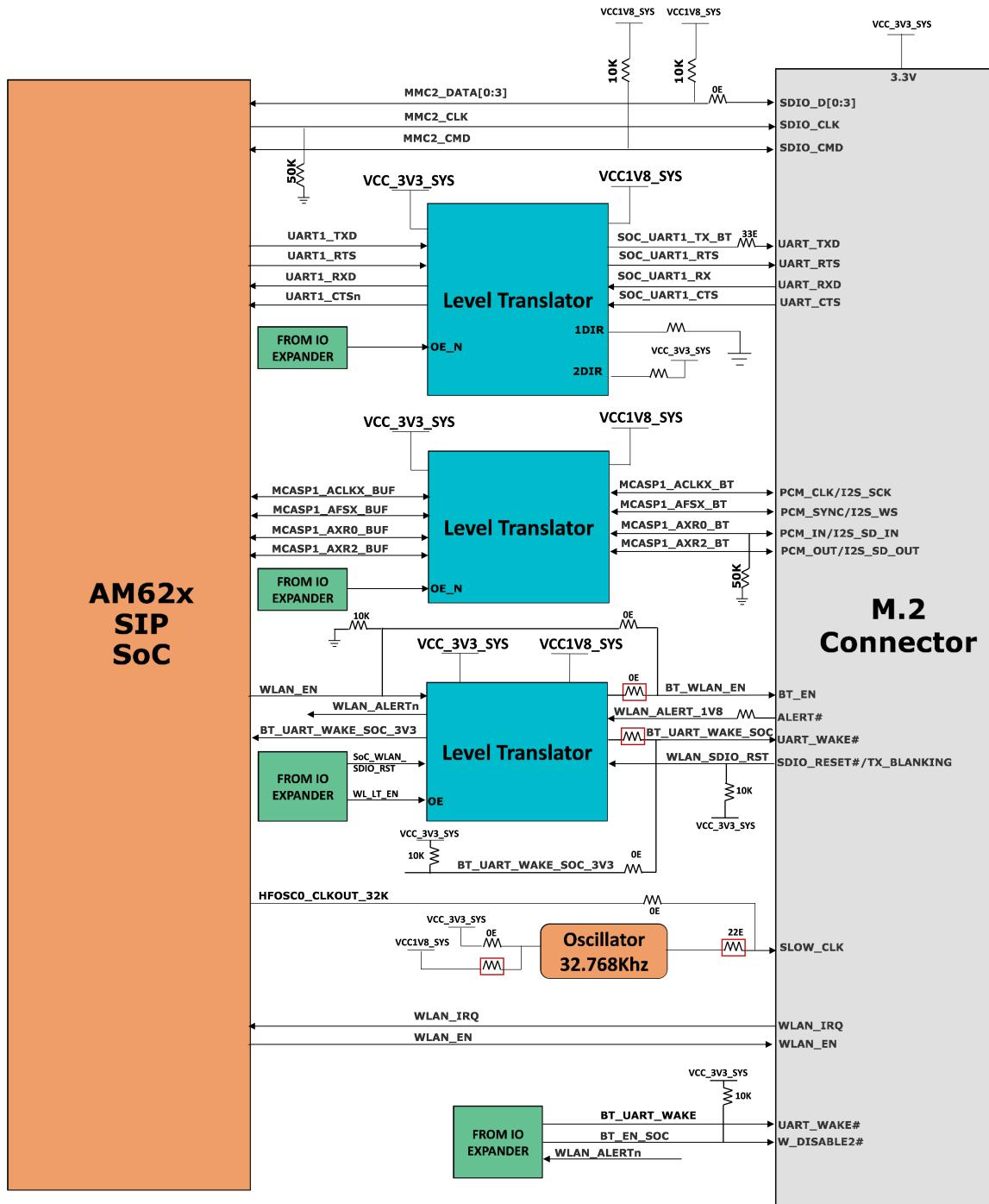

### 2.15.2.3 MMC2 - M.2 Key E インターフェイス

AM62x SIP SK 評価基板は、M.2 Key E インターフェイスを搭載しており、Wi-Fi® / BT モジュールを、バッファ経由で MMC2、UART1 インスタンス、McASP1 インターフェイスに接続できます。M.2 モジュールは、MMC2 インターフェイスの 4 ビット IO に接続されています。

このモジュールには、3.3V 電源が 1 つ必要です。M.2 モジュールへの電源は、オンボードの電源レールから供給されます。

SoC の MMC2 インターフェイスは、1.8V IO 電源に接続された VDDSHV6 電源ドメインから電力が供給されます。

図 2-23. Wi-Fi インターフェイス

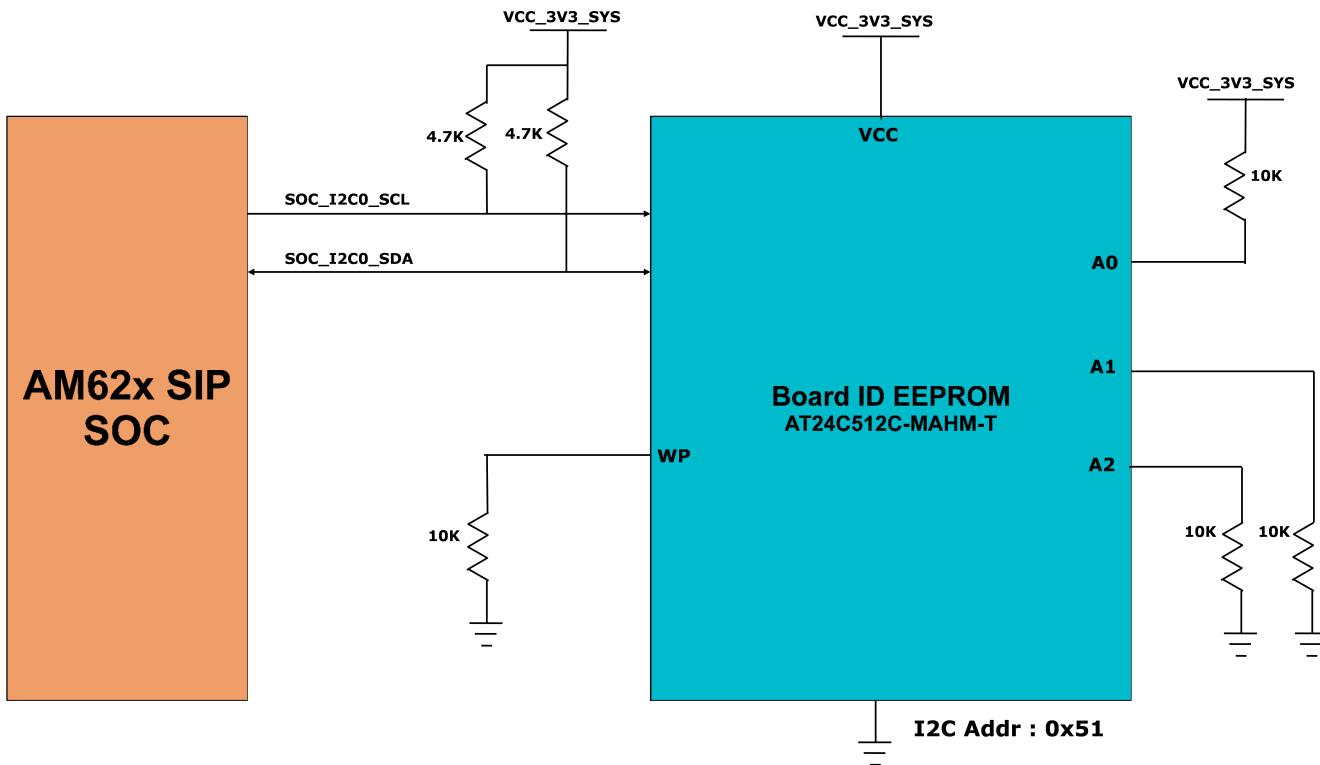

### 2.15.3 基板 ID EEPROM

AM62x SIP SK 評価基板は、オンボード EEPROM に保存されているバージョンとシリアル番号からリモートで識別可能です。EEPROM は、AM62x SIP SoC の SoC I2C0 ポートからアクセスできます。

基板 ID EEPROM の I2C アドレスは 0x51 に設定されています。

AM62x SIP SK 評価基板には、512kb EEPROM である AT24C512C-MAHM-T が搭載されています。メモリの最初の 259 バイトは、各基板の識別情報であらかじめプログラムされています。残りの 65277 バイトは、データまたはコードの保存用にユーザーが使用できます。

図 2-24. 基板 ID EEPROM

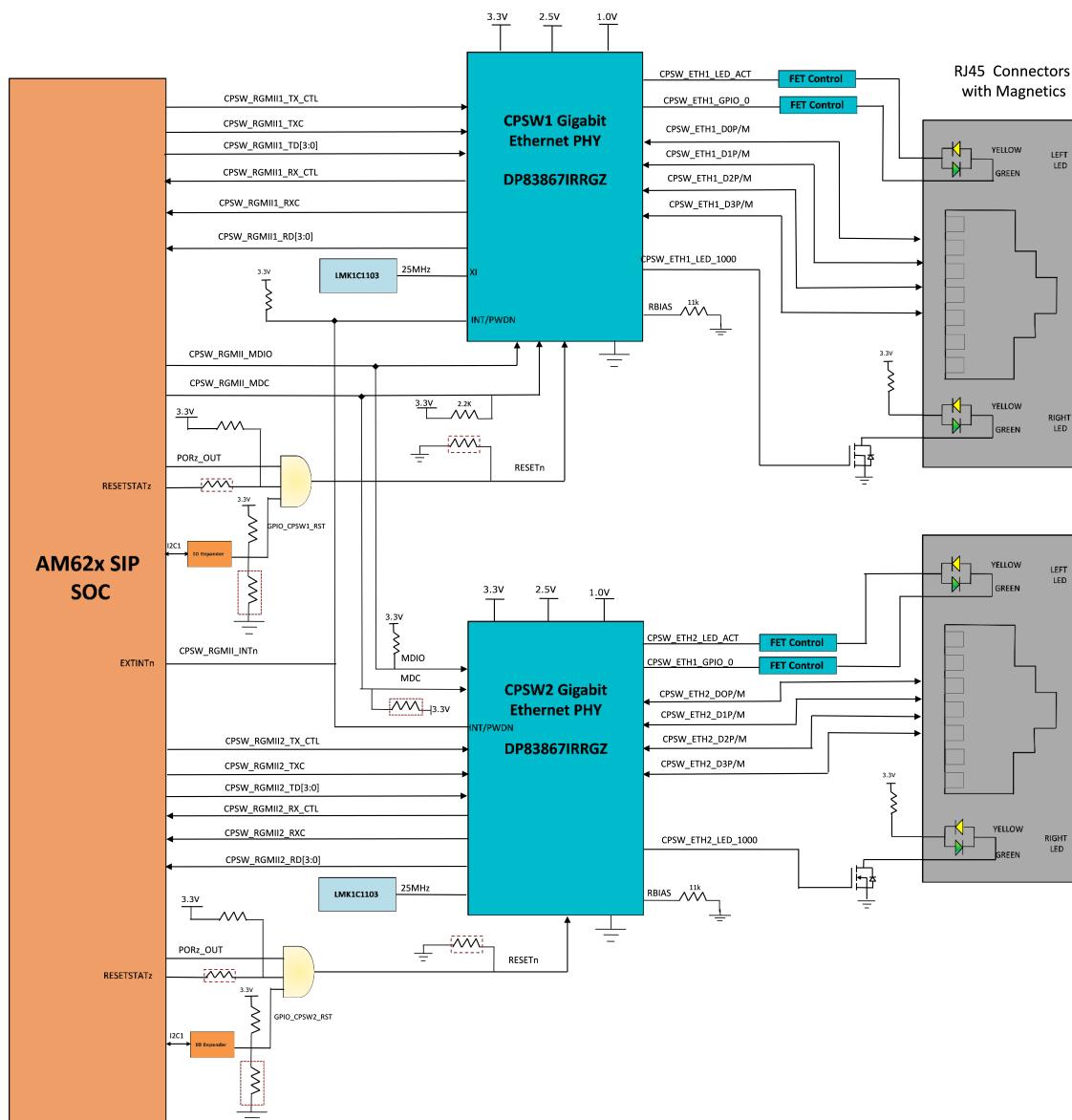

## 2.16 イーサネット インターフェイス

AM62x SIP SK 評価基板には、外部通信向けに、1 ギガビット速度のイーサネットポートが 2 つあります。AM62x SIP SoC の RGMII ギガビットイーサネット CPSW ポートの 2 つのチャネルは、個別のギガビットイーサネット PHY トランシーバ DP83867 に接続されています。これらのトランシーバは、磁気部品内蔵の 2 つの RJ45 コネクタで最終的に終端されます。

PHY DP83867 の 48 ピンバージョンは、AM62x 内部の遅延に対応するように内部遅延が設定され、1Gb 動作をアドバイスするように構成されています。CPSW\_RGMII1 ポートおよび CPSW\_RGMII2 ポートは、外部 PHY トランシーバと通信するために、共通の MDIO バスを使用しています。

イーサネット 10/100/1G 接続には、ボード上で Link-PP の 2 つのシングルポート RJ45 コネクタ（メーカー型番 LPJG16314A4NL）が使用されます。RJ45 コネクタには、1000BASE-T リンクと送受信アクティビティを示すための磁気素子および LED が内蔵されています。

イーサネット PHY への I/O 電源は 3.3V のレベルに設定されています。

図 2-25. イーサネット インターフェイス

### 2.16.1 CPSW イーサネット PHY 1 のデフォルト構成

DP83867 のデフォルト構成は、PHY の特定のピンにある複数の抵抗プルアップおよびプルダウン値を使用して決定されています。取り付け済みの値に応じて、搭載しているプルアップ / プルダウン オプションを使用して、各構成ピンを 4 つのモードのいずれかに設定することができます。AM62x SIP SK 評価基板は、RGMII インターフェイスをサポートする 48 ピン QFN パッケージを使用しています。

DP83867 PHY は、抵抗ストラッピングに基づいて 4 つのレベル構成を使用して、4 つの異なる電圧範囲を生成します。これらの抵抗は、通常 PHY によって駆動されてプロセッサへの入力となる、RX データおよび制御ピンに接続されます。各モードの電圧範囲を以下に示します。

モード 1 — 0V ~ 0.3V

モード 2 — 0.462V ~ 0.6303V

モード 3 — 0.7425V ~ 0.9372V

モード 4 — 2.2902V ~ 2.9304V

LED\_0 を除くすべてのストラッピングピンには、プルアップおよびプルダウンの両方のフットプリントが用意されています。LED\_0 はミラー イネーブル用で、デフォルトではモード 1 に設定されています。モード 4 は適用されず、モード 2 およびモード 3 のオプションは使用しません。

AM62x SIP SoC の CPSW\_RGMII1 ポートは、以下のように構成する DP83867 に接続されています：

PHYADDR:00000

Auto\_neg:有効

ANGsel 10/100/1000

RGMII Clk スキュー Tx:2ns

RGMII Clk スキュー Rx:2ns

### 2.16.2 CPSW イーサネット PHY 2 のデフォルト構成

AM62x SIP SoC の CPSW\_RGMII2 ポートに接続されている DP83867 は以下の構成になっています：

PHYADDR:00001

Auto\_neg:有効

ANGsel 10/100/1000

RGMII Clk スキュー Tx:2ns

RGMII Clk スキュー Rx:2ns

2 つの CPSW RGMII PHY から生成された割り込みは互いに接続され、AM62x SIP SoC の EXTINTn ピンに接続されています。

LED1 は RJ45 右 LED (緑色) に接続され、1000MHz リンクを示します。

LED2 は RJ45 左 LED (黄色) に接続され、送受信アクティビティを示します。GPIO\_0 は RJ45 左 LED (緑) に接続され、10/100MHz リンクを示します。

LED 制御は、外付けの MOSFET を通じて行われます。

## 2.17 GPIO ポート エクスパンダ

AM62x SIP SK 評価基板で使用されている I/O エクスパンダは、24 ビットの I2C ベース I/O エクスパンダであり、データカードのプラグイン検出や、接続されている各種ペリフェラル デバイスに対するリセット信号やイネーブル信号の生成に使用されます。AM62x SIP SoC の SoC\_I2C1 バスは、I/O エクスパンダとインターフェイスするために使用されます。I/O エクスパンダの I2C デバイス アドレスは 0x21 です。エクスパンダによって制御される信号のリストについては、以下の表を参照してください。

**表 2-12. IO エクスパンダ 1 の信号の詳細**

| ピン番号 | 信号                   | 方向   | デバイス                                   |

|------|----------------------|------|----------------------------------------|

| P00  | GPIO_CPSW2_RST       | 出力   | CPSW イーサネット PHY-2 リセット制御 GPIO          |

| P01  | GPIO_CPSW1_RST       | 出力   | CPSW イーサネット PHY-1 リセット制御 GPIO          |

| P02  | PRU_DETECT           | 入力   | PRU ボード検出                              |

| P03  | MMC1_SD_EN           | 出力   | SD カード ロード スイッチの有効化                    |

| P04  | VPP_LDO_EN           | 出力   | SOC eFuse 電圧 (VPP = 1.8V) レギュレータのイネーブル |

| P05  | EXP_PS_3V3_EN        | 出力   | EXP CONN 3.3V パワー スイッチのイネーブル           |

| P06  | EXP_PS_5V0_EN        | 出力   | EXP CONN 5V パワー スイッチのイネーブル             |

| P07  | EXP_HAT_DETECT       | 入力   | EXP CONN HAT ボード検出                     |

| P10  | WLAN_ALERT_3V3       | 出力   | Wi-Fi カードのアラート — M.2 モジュール             |

| P11  | BT_UART_WAKE_SOC_3V3 | 入力   | BT UART WKUP 信号                        |

| P12  | UART1_FET_BUF_EN     | 出力   | SOC UART1 バッファのイネーブル                   |

| P13  | WL_LT_EN             | 出力   | Wilink レベル変換器のイネーブル                    |

| P14  | GPIO_HDMI_RSTn       | 出力   | HDMI トランスマッタ リセット制御 GPIO               |

| P15  | CSI_GPIO1            | 該当なし | Raspberry Pi カメラ CSI0 GPIO1            |

| P16  | CSI_GPIO2            | 該当なし | Raspberry Pi カメラ CSI0 GPIO2            |

| P17  | PRU_3V3_EN           | 出力   | PRU パワー スイッチのイネーブル                     |

| P20  | HDMI_INTn            | 入力   | HDMI 割り込み                              |

| P21  | PD_I2C IRQ           | 入力   | PD コントローラからの割り込み                       |

| P22  | MCASP1_FET_EN        | 出力   | MCASP1 イネーブルおよび方向制御                    |

| P23  | MCASP1_BUF_BT_EN     | 出力   |                                        |

| P24  | MCASP1_FET_SEL       | 出力   |                                        |

| P25  | UART1_FET_SEL        | 出力   | SOC UART1 FET の選択                      |

| P26  | TS_INT#              | 入力   | OLDI ディスプレイ タッチの割り込み                   |

| P27  | IO_EXP_TEST_LED      | 出力   | ユーザー テスト LED 2                         |

**表 2-13. IO エクスパンダ 2 の信号の詳細**

| ピン番号 | 信号                | 方向 | デバイス                      |

|------|-------------------|----|---------------------------|

| P0   | WLAN_SDIO_RST_3V3 | 出力 | M.2 コネクタ SDIO リセット制御 GPIO |

| P1   | GPIO_TS_RSTn      | 出力 | OLDI ディスプレイ リセット制御        |

| P2   | GPIO_AUD_RSTn     | 出力 | オーディオ コーデック リセット制御 GPIO   |

| P3   | GPIO_eMMC_RSTn    | 出力 | eMMC リセット制御 GPIO          |

## 2.18 GPIO へのマッピング

以下の表に、AM62x SIP SK 評価基板のペリフェラルを搭載した AM62x SIP SoC の詳細な GPIO マッピングを示します。

| SL NO.           | GPIO DESCRIPTION                                                     | GPIO NETNAME             | Functionality                      | GPIO USED         | SOC MUXED SIGNAL NAME | DIRECTION WITH RESPECT TO CONTROL | DEFAULT STATE | ACTIVE STATE | VOLTAGE DOMAIN ON SOC SIDE | VOLTAGE CONNECTED ON SKEVIM |

|------------------|----------------------------------------------------------------------|--------------------------|------------------------------------|-------------------|-----------------------|-----------------------------------|---------------|--------------|----------------------------|-----------------------------|

| 1                | Enable for WLAN Interface                                            | Soc_WLAN_EN_1V8          | ENABLE                             | GPIO0_71          | MMC2_SD_CD            | OUTPUT                            | LOW           | HIGH         | VDDSHV6                    | Soc_DVDD1V8                 |

| 2                | WLAN Interrupt                                                       | Soc_WLAN IRQ_1V8         | INTERRUPT                          | GPIO0_72          | MMC2_SD_WP            | INPUT                             | HIGH          | LOW          | VDDSHV6                    | Soc_DVDD1V8                 |

| 3                | Enable for BT Interface                                              | BT_EN_SOC_3V3            | ENABLE                             | MCU_GPIO0_1       | MCU_SPI0_CSO          | OUTPUT                            | HIGH          | LOW          | VDDSHV_MCU                 | Soc_DVDD3V3                 |

| 4                | CPSW Ethernet PHY Interrupt                                          | CPSW_RGMII_INTr/PRU_INTr | INTERRUPT                          | GPIO1_31          | EXTINTn               | INPUT                             | HIGH          | LOW          | VDDSHV0                    | SoC_DVDD3V3                 |

|                  | PRU Connector Interrupt                                              |                          |                                    |                   |                       |                                   |               |              |                            |                             |

|                  | PMIC INTn                                                            |                          |                                    |                   |                       |                                   |               |              |                            |                             |

| 5                | OSPI Reset Control GPIO                                              | GPIO_OSPI_RSTn           | RESET                              | GPIO0_12          | OSPI0_CSn1            | OUTPUT                            | HIGH          | LOW          | VDDSHV1                    | Soc_DVDD1V8                 |

| 6                | OSPI Interrupt                                                       | OSPI_INTn                | INTERRUPT                          | GPIO0_13          | OSPI0_CSn2            | INPUT                             | HIGH          | LOW          | VDDSHV1                    | Soc_DVDD1V8                 |

| 7                | SD Card IO Voltage Select                                            | VSEL_SD                  | ENABLE                             | GPIO0_31          | GPMCO_CLK             | OUTPUT                            | LOW           | HIGH         | VDDSHV3                    | Soc_DVDD3V3                 |

| 8                | IO Expander Interrupt                                                | MCU_GPIO0_15             | INTERRUPT                          | MCU_GPIO0_15      | MCU_MCAN1_TX          | INPUT                             | HIGH          | LOW          | VDDSHV_CANUART             | SoC_DVDD3V3                 |

| 9                | TEST GPIO1 from Test Automation Connector/User Interrupt Push Button |                          |                                    |                   |                       |                                   |               |              |                            |                             |

| 10               | User Test LED 1                                                      | SOC_GPIO1_49             | GPIO                               | GPIO1_49          | MMC1_SD_WP            | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| IO EXPANDER - 01 |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

| 1                | CPSW Ethernet PHY-2 Reset Control GPIO                               | GPIO_CPSW2_RST           | RESET                              | IO EXPANDER - P00 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 2                | CPSW Ethernet PHY-1 Reset Control GPIO                               | GPIO_CPSW1_RST           | RESET                              | IO EXPANDER - P01 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 3                | PRU Board Detection                                                  | PRU_DETECT               | DETECTION                          | IO EXPANDER - P02 |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 4                | SD Card Load Switch Enable                                           | MIMC1_SD_EN              | ENABLE                             | IO EXPANDER - P03 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 5                | SOC eFuse Voltage(VPP=1.8V) Regulator Enable                         | VPP_LDO_EN               | ENABLE                             | IO EXPANDER - P04 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 6                | EXP CONN 3.3V Power Switch Enable                                    | EXP_P5_3V3_EN            | ENABLE                             | IO EXPANDER - P05 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 7                | EXP CONN 5V Power Switch Enable                                      | EXP_P5_5V0_EN            | ENABLE                             | IO EXPANDER - P06 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 8                | EXP CONN HAT Board Detection                                         | RPI_HAT_DETECT           | DETECTION                          | IO EXPANDER - P07 |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 9                | M.2 Connector Alert                                                  | WLAN_ALERT_3V3           | ALERT                              | IO EXPANDER - P10 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 10               | M.2 Connector WAKEUP                                                 | BT_UART_WAKE_SOC_3V3     | WAKEUP                             | IO EXPANDER - P11 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 11               | SOC UART1 Mux Select                                                 | UART1_MUX_SEL            | SELECT                             | IO EXPANDER - P12 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 12               | Enable for WiLink Level Translators                                  | WL_LT_EN                 | ENABLE                             | IO EXPANDER - P13 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 13               | HDMI Transmitter Reset Control GPIO                                  | GPIO_HDMI_RSTn           | RESET                              | IO EXPANDER - P14 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 14               | Raspberry Pi Camera CSI0 GPIO1                                       | CSI_GPIO1                | INPUT/OUTPUT                       | IO EXPANDER - P15 |                       | NA                                | NA            | NA           | VDDSHV0                    | Soc_DVDD3V3                 |

| 15               | Raspberry Pi Camera CSI0 GPIO2                                       | CSI_GPIO2                | INPUT/OUTPUT                       | IO EXPANDER - P16 |                       | NA                                | NA            | NA           | VDDSHV0                    | Soc_DVDD3V3                 |

| 16               | PRU Power Switch Enable                                              | PRU_3V3_EN               | ENABLE                             | IO EXPANDER - P17 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 17               | HDMI Interrupt                                                       | HDMI_INTr                | INTERRUPT                          | IO EXPANDER - P20 |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 18               | TEST GPIO2 from Test Automation Connector                            | TEST_GPIO2               | GPIO for communications with AM62x | IO EXPANDER - P21 |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 19               | MCASP2 Enable and Direction Control                                  | AUD_BUF_EN               | ENABLE                             | IO EXPANDER - P22 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| 20               |                                                                      | WL_BUF_EN                | ENABLE                             | IO EXPANDER - P23 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 21               |                                                                      | AUD_BUF_CLK_DIR          | DIRECTION CONTROL                  | IO EXPANDER - P24 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 22               |                                                                      | WL_BUF_CLK_DIR           | DIRECTION CONTROL                  | IO EXPANDER - P25 |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 23               | OLDI Display Touch Interrupt                                         | TS_INT#                  | INTERRUPT                          | IO EXPANDER - P26 |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 24               | User Test LED 2                                                      | IO_EXP_TEST_LED          | GPIO                               | IO EXPANDER - P27 |                       | OUTPUT                            | LOW           | HIGH         | VDDSHV0                    | Soc_DVDD3V3                 |

| IO EXPANDER - 02 |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

| 1                | M.2 Connector SDIO Reset Control GPIO                                | WLAN_SDIO_RST_3V3        | RESET                              | IO EXPANDER - P0  |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 2                | OLDI Display Reset control                                           | GPIO_TS_RSTn             | RESET                              | IO EXPANDER - P1  |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 3                | Audio Codec Reset Control GPIO                                       | GPIO_AUD_RSTn            | DETECTION                          | IO EXPANDER - P2  |                       | INPUT                             | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

| 4                | eMMC Reset control GPIO                                              | GPIO_eMMC_RSTn           | RESET                              | IO EXPANDER - P3  |                       | OUTPUT                            | HIGH          | LOW          | VDDSHV0                    | Soc_DVDD3V3                 |

|                  |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

|                  |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

|                  |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

|                  |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

|                  |                                                                      |                          |                                    |                   |                       |                                   |               |              |                            |                             |

図 2-26. GPIO へのマッピング

## 2.19 OLDI ディスプレイ インターフェイス

AM62x SIP SoC の OLDI0 ディスプレイ インターフェイスは、40 ピン LVDS ディスプレイコネクタ (J21、GCT 製 メーカー型番 FFC2A32-40-T) に接続されています。OLDI インターフェイスは、デュアル チャネルの 8 ビット LVDS 出力をサポートしています。

下の表に、ディスプレイコネクタのピン配置の詳細を示します。

**表 2-14. OLDI ディスプレイ コネクタのピン配置**

| ピン番号。 | 信号                       | ピン番号。 | 信号            |

|-------|--------------------------|-------|---------------|

| 1     | VCC_3V3_SYS (EEPROM_VDD) | 21    | CH1_LVDS_A2P  |

| 2     | SoC_I2C0_SCL             | 22    | GND           |

| 3     | SoC_I2C0_SDA             | 23    | CH1_LVDS_A3N  |

| 4     | NC                       | 24    | CH1_LVDS_A3P  |

| 5     | NC                       | 25    | GND           |

| 6     | GND                      | 26    | CH1_LVDS_A0N  |

| 7     | GND                      | 27    | CH1_LVDS_A0P  |

| 8     | OLDI_RESETn              | 28    | GND           |

| 9     | TS_INT#                  | 29    | CH2_LVDS_A1N  |

| 10    | GND                      | 30    | CH2_LVDS_A1P  |

| 11    | CH1_LVDS_A0N             | 31    | GND           |

| 12    | CH1_LVDS_A0P             | 32    | CH2_LVDS_CLKN |

| 13    | GND                      | 33    | CH2_LVDS_CLKP |

| 14    | CH1_LVDS_A1N             | 34    | GND           |

| 15    | CH1_LVDS_A1P             | 35    | CH2_LVDS_A2N  |

| 16    | GND                      | 36    | CH2_LVDS_A2P  |

| 17    | CH1_LVDS_CLKN            | 37    | GND           |

| 18    | CH1_LVDS_CLKP            | 38    | CH2_LVDS_A3N  |

| 19    | GND                      | 39    | CH2_LVDS_A3P  |

| 20    | CH1_LVDS_A2N             | 40    | GND           |

## 2.20 評価基板のユーザー設定/構成

### 2.20.1 評価基板 DIP スイッチ

AM62x SIP SK 評価基板には、SoC ブート モードと関連パラメータを設定するための 8 ポジション DIP スイッチが 2 つ搭載されています。

### 2.20.2 ブート モード

AM62x SIP SK 評価基板のブート モードは、SW1、SW2 のスイッチからなる 2 つのバンクによって定義されます。あるいは、テスト オートメーション コネクタに接続された I2C バッファによって定義されます。これにより、AM62x SIP SoC のブート モードは、ユーザー (DIP スイッチ制御) またはテスト オートメーション コネクタによって制御できます。

スイッチ (SW1 と SW2) のすべてのビットには、弱いプルダウン抵抗と強いプルアップ抵抗があります (以下に図示)。オフ設定のときは Low ロジック レベル ('0') が、オン設定のときは High ロジック レベル ('1') が提供されます。

図 2-27. SD ブート用のブート モード スイッチ構成

SoC のブート モード ピンは、通常動作時には代替機能が関連付けられています。このため、代替えピン機能に対応するために、バッファ IC を使用して分離が可能です。バッファの出力は AM62x SIP のブート モード ピンに接続され、リセットサイクル中にブート モードが必要な場合にのみ出力が有効になります。

バッファへの入力は、DIP スイッチ回路と、テスト オートメーション回路によって設定された I2C バッファ セットの出力に接続されています。テスト オートメーション回路がブート モードを制御する場合は、すべてのスイッチを手動でオフ位置に設定する必要があります。ブート モード バッファは、SoC の電源を入れ直してもブート モードが維持されるように、常時オンの電源から電力供給されます。

スイッチ SW1 と SW2 の各ビット [15:0] は、SoC ブート モードの設定に使用されます。

このブート モード機能へのスイッチ マッピングを以下の表に示します。

表 2-15. ブート モードのピン マッピング

| Bit15 | Bit14 | Bit13                    | Bit12          | Bit11                | Bit10         | Bit9   | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|-------|--------------------------|----------------|----------------------|---------------|--------|------|------|------|------|------|------|------|------|------|

| 予約済み  | 予約済み  | バックアップ<br>ブート モード<br>の構成 | バックアップ ブート モード | プライマリ ブート モード<br>の構成 | プライマリ ブート モード | PLL 構成 |      |      |      |      |      |      |      |      |      |

以下の表に、PLL リファレンス クロック選択の詳細を示します。

注

BOOT-MODE[0:2] – PLL の構成のシステム クロック周波数を示します。デフォルトでは、このビットは 25MHz に設定されています。

**表 2-16. PLL リファレンス クロックの選択 BOOTMODE[2:0]**

| ビット 2 | ビット 1 | ビット 0 | PLL REF CLK (MHz) |

|-------|-------|-------|-------------------|

| OFF   | OFF   | OFF   | RSVD              |

| OFF   | OFF   | オン    | RSVD              |

| OFF   | オン    | OFF   | 24                |

| OFF   | オン    | オン    | 25                |

| オン    | OFF   | OFF   | 26                |

| オン    | OFF   | オン    | RSVD              |

| オン    | オン    | OFF   | RSVD              |

| オン    | オン    | オン    | RSVD              |

以下の表に、プライマリ ブート デバイス選択の詳細を示します。

**注**

BOOT-MODE[3:6] – これにより、POR 後に、ブート元となる周辺機器やメモリなど、要求されたブート モードを選択するためのプライマリ ブート モード設定が行われます。

**表 2-17. ブート デバイス選択 BOOTMODE[6:3]**

| ビット 6 | ビット 5 | ビット 4 | ビット 3 | プライマリ ブート デバイスの選択 |

|-------|-------|-------|-------|-------------------|

| OFF   | OFF   | OFF   | OFF   | シリアル NAND         |

| OFF   | OFF   | OFF   | オン    | OSPI              |

| OFF   | OFF   | オン    | OFF   | QSPI              |

| OFF   | OFF   | オン    | オン    | SPI               |

| OFF   | オン    | OFF   | OFF   | イーサネット RGMII1     |

| OFF   | オン    | OFF   | オン    | イーサネット RMII1      |

| OFF   | オン    | オン    | OFF   | I2C               |

| OFF   | オン    | オン    | オン    | UART              |

| オン    | OFF   | OFF   | OFF   | MMC / SD カード      |

| オン    | OFF   | OFF   | オン    | eMMC              |

| オン    | OFF   | オン    | OFF   | USB0              |

| オン    | OFF   | オン    | オン    | GP MC NAND        |

| オン    | オン    | OFF   | OFF   | GP MC NOR         |

| オン    | オン    | OFF   | オン    | 予約済み              |

| オン    | オン    | オン    | OFF   | xSPI              |

| オン    | オン    | オン    | オン    | ブートなし / デバイス ブート  |

以下の表に、バックアップ ブート モード選択の詳細を示します。

**注**

BOOT-MODE[10:12] – プライマリ ブート デバイスに障害が発生した場合に、バックアップ ブート モード、つまりブート元となるペリフェラル / メモリを選択します。

**表 2-18. バックアップ ブート モードの選択 BOOTMODE[12:10]**

| ビット 12 | ビット 11 | ビット 10 | バックアップ ブート デバイスの選択 |

|--------|--------|--------|--------------------|

| OFF    | OFF    | OFF    | なし (バックアップ モードなし)  |

| OFF    | OFF    | オン     | USB                |

| OFF    | オン     | OFF    | 予約済み               |

| OFF    | オン     | オン     | UART               |

| オン     | OFF    | OFF    | イーサネット             |

表 2-18. バックアップ ブート モードの選択 BOOTMODE[12:10] (続き)

| ピット 12 | ピット 11 | ピット 10 | バックアップ ブート デバイスの選択 |

|--------|--------|--------|--------------------|

| オン     | OFF    | オン     | MMC/SD             |

| オン     | オン     | OFF    | SPI                |

| オン     | オン     | オン     | I2C                |

以下の表に、プライマリ ブート メディア構成の詳細を示します。

## 注

BOOT-MODE[9:7] — これらのピンはオプション設定を提供し、選択されたプライマリ ブート デバイスと組み合わせて使用されます。

表 2-19. プライマリ ブート メディアの構成 BOOTMODE[9:7]

| ピット 9   | ピット 8     | ピット 7            | ブート デバイス         |

|---------|-----------|------------------|------------------|

| 予約済み    | 読み取りモード 2 | 読み取りモード 1        | シリアル NAND        |

| 速度      | 入力クロック    | チップ選択            | OSPI             |

| 予約済み    | 入力クロック    | チップ選択            | QSPI             |

| 予約済み    | モード       | チップ選択            | SPI              |

| クロック出力  | 遅延        | リンク ステータス        | イーサネット (RGMII)   |

| クロック出力  | クロック ソース  | 予約済み             | イーサネット (RMII)    |

| バス リセット | 予約済み      | アドレス             | I2C              |

| 予約済み    |           | 予約済み             | UART             |

| ポート     | 予約済み      | サンプリング周波数 / 生データ | MMC/SD カード       |

| 予約済み    |           | 電圧               | eMMC             |

| 予約済み    | モード       | レーン スワップ         | USB0             |

|         | 予約済み      |                  | GPMC NAND        |

|         | 予約済み      |                  | GPMC NOR         |

|         | 予約済み      |                  | 予約済み             |

| SFDP    | 読み取りコマンド  | モード              | xSPI             |

| 予約済み    |           | なし / デバイス        | ブートなし / デバイス ブート |

表 2-20. シリアル NAND 構成フィールド

| ブートモード ピン | フィールド     | 値 | 説明                                                           |

|-----------|-----------|---|--------------------------------------------------------------|

| 8 [SW2.1] | 読み取りモード 2 | 0 | 予約済み (読み取りモードは読み取りモード 1 から取得)                                |

|           |           | 1 | SPI/ 1-1-1 モード (読み取りモードは、読み取りモード 2 から取得され読み取りモード 1 は無視されます。) |

| 7 [SW1.8] | 読み取りモード 1 | 0 | OSPI/ 1-1-8 モード (読み取りモード 2 が 0 の場合のみ有効)                      |

|           |           | 1 | OSPI/ 1-1-4 モード (読み取りモード 2 が 0 の場合のみ有効)                      |

表 2-21. OSPI ブート構成フィールド

| ブートモード ピン | フィールド  | 値 | 説明                        |

|-----------|--------|---|---------------------------|

| 8 [SW2.1] | 入力クロック | 0 | 入力クロック ソース外部              |

|           |        | 1 | 入力クロック ソース内部 (パッド ループバック) |

| 7 [SW1.8] | チップ選択  | 0 | ブート フラッシュは CS 0 に搭載       |

|           |        | 1 | ブート フラッシュは CS 1 に搭載       |

表 2-22. QSPI ブート構成フィールド

| ブートモード ピン | フィールド  | 値 | 説明                        |

|-----------|--------|---|---------------------------|

| 8 [SW2.1] | 入力クロック | 0 | 入力クロック ソース外部              |

|           |        | 1 | 入力クロック ソース内部 (パッド ループバック) |

表 2-22. QSPI ブート構成フィールド (続き)

|           |       |   |                     |

|-----------|-------|---|---------------------|

| 7 [SW1.8] | チップ選択 | 0 | ブート フラッシュは CS 0 に搭載 |

|           |       | 1 | ブート フラッシュは CS 1 に搭載 |

表 2-23. SPI ブート構成フィールド

| ブートモード ピン | フィールド | 値 | 説明                  |

|-----------|-------|---|---------------------|

| 8 [SW2.1] | モード   | 0 | SPI モード 0           |

|           |       | 1 | SPI モード 3           |

| 7 [SW1.8] | チップ選択 | 0 | ブート フラッシュは CS 0 に搭載 |

|           |       | 1 | ブート フラッシュは CS 1 に搭載 |

表 2-24. イーサネット RGMII ブートの構成フィールド

| ブートモード ピン | フィールド  | 値 | 説明                                      |

|-----------|--------|---|-----------------------------------------|

| 9 [SW2.2] | クロック出力 | 0 | 25MHz クロックは CLKOUT0 で生成されません            |

|           |        | 1 | CLKOUT0 で生成される 25MHz クロック               |

| 8 [SW2.1] | 遅延     | 0 | 内部の Tx 遅延を使用する RGMII の場合、0 に設定する必要があります |

|           |        | 1 | 予約済み                                    |

| 7 [SW1.8] | リンク情報  | 0 | リンク パラメータに使用する MDIO PHY スキャン            |

|           |        | 1 | ROM によってプログラムされたリンク パラメータ               |

表 2-25. イーサネット RMII ブートの構成フィールド

| ブートモード ピン | フィールド    | 値 | 説明                           |

|-----------|----------|---|------------------------------|

| 9 [SW2.2] | クロック出力   | 0 | 50MHz クロックは CLKOUT0 で生成されません |

|           |          | 1 | CLKOUT0 で生成される 50MHz クロック    |

| 8 [SW2.1] | クロック ソース | 0 | RMII1_REF_CLK の外部クロック ソース    |

|           |          | 1 | RMII1_REF_CLK の内部クロック ソース    |

| 7 [SW1.8] | RMII     | 0 | このビットは 0 に設定する必要があります        |

|           |          | 1 | 予約済み                         |

表 2-26. RMII イーサネット クロック供給

| BOOTMODE ピン 9 (Clk 出力) | BOOTMODE ピン 8 (Clk src) | 説明                                                                      |

|------------------------|-------------------------|-------------------------------------------------------------------------|

| 0                      | 0                       | 50MHz 外部ソースを RMII_REF_CLK および外部イーサネット PHY 入力クロックへ供給 (CLKOUT0 は未使用) 推奨設定 |

| 0                      | 1                       | 有効な設定ではありません                                                            |

| 1                      | 0                       | CLKOUT0 は 50MHz に設定され、RMII1_REF_CLK および外部イーサネット PHY 入力クロックの両方に接続        |

| 1                      | 1                       | 有効な設定ではありません                                                            |

表 2-27. イーサネット バックアップ ブート設定フィールド

| ブートモード ピン  | フィールド    | 値 | 説明                 |

|------------|----------|---|--------------------|

| 13 [SW2.2] | インターフェイス | 0 | 内部 TX 遅延付き RGMII   |

|            |          | 1 | 外部クロック ソース使用の RMII |

表 2-28. I2C ブート構成フィールド

| ブートモード ピン | フィールド   | 値 | 説明                     |

|-----------|---------|---|------------------------|

| 9 [SW2.2] | バス リセット | 0 | 1ms 後にハング バス リセットを試行   |

|           |         | 1 | ハング バスのリセットは試行されませんでした |

表 2-28. I2C ブート構成フィールド (続き)

| ブートモードピン  | フィールド | 値 | 説明                    |

|-----------|-------|---|-----------------------|

| 7 [SW1.8] | アドレス  | 0 | EEPROM のアドレスは 0x50 です |

|           |       | 1 | EEPROM のアドレスは 0x51 です |

表 2-29. SD カード ブート構成フィールド

| ブートモードピン                               | フィールド  | 値 | 説明                                       |

|----------------------------------------|--------|---|------------------------------------------|

| 9 [SW2.2]<br>13 <sup>(1)</sup> [SW2.2] | ポート    | 0 | 予約済み                                     |

|                                        |        | 1 | MMC ポート 1 (4 ビット幅)。このビットは 1 に設定する必要があります |

| 7 [SW1.8]                              | FS/Raw | 0 | ファイルシステム モード                             |

|                                        |        | 1 | Raw モード                                  |

(1) MMCSD がバックアップ モードの場合

表 2-30. eMMC ブート構成フィールド

| ブートモードピン                               | フィールド  | 値 | 説明                                         |

|----------------------------------------|--------|---|--------------------------------------------|

| 9 [SW2.2]<br>13 <sup>(1)</sup> [SW2.2] | ポート    | 0 | MMCSD ポート 0 (8 ビット幅)。このビットは 0 に設定する必要があります |

|                                        |        | 1 | 予約済み                                       |

| 7 [SW1.8]                              | FS/Raw | 0 | ファイルシステム モード                               |

|                                        |        | 1 | Raw モード                                    |

(1) MMCSD がバックアップ モードの場合

表 2-31. USB ブート構成フィールド

| ブートモードピン                               | フィールド    | 値 | 説明                            |

|----------------------------------------|----------|---|-------------------------------|

| 9 [SW2.2]                              | コア電圧     | 0 | 0.85V のコア電圧                   |

|                                        |          | 1 | 0.75V のコア電圧                   |

| 8 [SW2.1]<br>13 <sup>(1)</sup> [SW2.2] | モード      | 0 | DFU (USB デバイス フームウェア アップグレード) |

|                                        |          | 1 | ホスト (MSC ブート)                 |

| 7 [SW1.8]                              | レーン スワップ | 0 | D+/D- ラインはスワップされていません         |

|                                        |          | 1 | D+/D- ラインがスワップされています          |

(1) USB がバックアップ モードの場合。

表 2-32. xSPI ブート構成フィールド

| ブートモードピン  | フィールド    | 値 | 説明                   |

|-----------|----------|---|----------------------|

| 9 [SW2.2] | SFDP     | 0 | SFDP はディセーブル         |

|           |          | 1 | SFDP はイネーブル          |

| 8 [SW2.1] | 読み取りコマンド | 0 | 0x0B 読み取りコマンド        |

|           |          | 1 | 0xEE 読み取りコマンド        |

| 7 [SW1.8] | モード      | 0 | 1S-1S-1S モード (50MHz) |

|           |          | 1 | 8D-8D-8D モード (25MHz) |

以下の表に、バックアップ ブート メディアの構成オプションを示します。

#### 注

- **BOOT-MODE[13]** – これらのピンはオプション設定を提供し、バックアップ ブート デバイスと組み合わせて使用されます。スイッチ SW2.6 をオンにすると 1 が設定され、オフにすると 0 が設定されます。各デバイスの TRM を参照してください。

- **BOOT-MODE[14:15]** – 予約済み。

**表 2-33. プライマリ ブート メディアの構成 BOOTMODE[13]**

| ビット 13 | ブートデバイス |

|--------|---------|

| 予約済み   | なし      |

| モード    | USB     |

| 予約済み   | 予約済み    |

| 予約済み   | UART    |

| IF     | イーサネット  |

| ポート    | MMC/SD  |

| 予約済み   | SPI     |

| 予約済み   | I2C     |

### 2.20.3 ユーザー テスト LED

AM62x SIP SK 評価基板には、ユーザー定義による機能用に 2 つの LED が搭載されています。

以下の表に、ユーザー テスト LED と、その制御に使用される関連 GPIO を示します。

**表 2-34. ユーザー テスト LED**

| シリアル番号 | LED  | 使用 GPIO     | SCH ネット名        |

|--------|------|-------------|-----------------|

| 1      | LD1  | GPIO1_49    | SOC_GPIO1_49    |

| 2      | LD11 | U70.24(P27) | IO_EXP_TEST_LED |

### 2.21 拡張ヘッダ

AM62x SIP SK 評価基板は、3 個の拡張ヘッダー、1 個の 40 ピン ユーザー拡張コネクタ、1 個の 20 ピン PRU ヘッダー、1 個の 28 ピン MCU ヘッダーを搭載しています。

### 2.21.1 PRU コネクタ

AM62x SIP SK 評価基板は 20 ピン PRU ヘッダーを搭載しており、PRG0 インターフェイスに低速で接続できます。

PRG0 ポート (PRG0\_PRU0) からの PRU\_ICSSG 信号は、10x2 規格 0.1 インチ (2.54mm) 間隔のレセプタクルコネクタ (メーカー型番 PREC010DAAN-RC) に接続されています。コネクタには PRG0\_PRU0\_GPO [0: 7]、SoC\_I2C0、+3.3V PWR、グランドリファレンスが備わっています。PRU ヘッダーからの INTn 信号は、CPSW PHY 割り込みと一緒に配線され、SoC の EXTINTn ピンに接続されています。

3.3V 電源の電流は 500mA に制限されます。これは、ロードスイッチ TPS22902YFPR を使用して実現しています。ロードスイッチのイネーブルは、IO エクスパンダによって制御されています。PRU コネクタから接続されている信号を、下の表に示します。

図 2-28. PRU ヘッダ (J10) のピン配置

| ピン番号 | SOC ボール番号 | ネット名          | ピン多重化信号                                                                                                                                                                                           |

|------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | -         | VCC3V3_PRU    |                                                                                                                                                                                                   |

| 2    | -         | DGND          |                                                                                                                                                                                                   |

| 3    | -         | PRU_DETECT    |                                                                                                                                                                                                   |

| 4    | F22       | PRU_RESETz    | RESETSTATz                                                                                                                                                                                        |

| 5    | D16       | PRU_INTn      | EXTINTn/ GPIO1_31                                                                                                                                                                                 |

| 6    | B16       | SoC_I2C0_SCL  | I2C0_SCL/<br>PR0_IEP0_EDIO_DATA_IN_OUT30/<br>SYNC0_OUT/ OBSCLK0/ UART1_DCDn/<br>EQEP2_A_EHRPWM_SOCa/ GPIO1_26/<br>ECAP1_IN_APWM_OUT / SPI2_CS0                                                    |

| 7    | -         | NC            |                                                                                                                                                                                                   |

| 8    | A16       | SoC_I2C0_SDA  | I2C0_SDA/<br>PR0_IEP0_EDIO_DATA_IN_OUT31/<br>SPI2_CS2/TIMER_IO5/ UART1_DSRn/<br>EQEP2_B_EHRPWM_SOCb/ GPIO1_27/<br>ECAP2_IN_APWM_OUT                                                               |

| 9    |           | NC            |                                                                                                                                                                                                   |

| 10   | -         | NC            |                                                                                                                                                                                                   |

| 11   | -         | NC            |                                                                                                                                                                                                   |

| 12   | -         | NC            |                                                                                                                                                                                                   |

| 13   | M25       | PR0_PRU0_GPO0 | GPMC0_AD0/ PR0_PRU1_GPO8/<br>PR0_PRU1_GPI8/ MCASP2_AXR4/<br>PR0_PRU0_GPO0/PR0_PRU0_GPI0/<br>TRC_CLK/ GPIO0_15/<br>DDR0_IO_PLL_TESTOUT0P/<br>DDR0_IO_PLL_TESTOUT1P/ GPIO1_112/<br>LED_DIO0         |

| 14   | N23       | PR0_PRU0_GPO1 | GPMC0_AD1/ PR0_PRU1_GPO9/<br>PR0_PRU1_GPI9/ MCASP2_AXR5/<br>PR0_PRU0_GPO1/PR0_PRU0_GPI1/<br>TRC_CTL/ GPIO0_16/<br>DDR0_IO_PLL_REFCLK_TEST0P/<br>DDR0_IO_PLL_REFCLK_TEST1P/<br>GPIO1_113/ LED_DIO1 |

| 15   | N24       | PR0_PRU0_GPO2 | GPMC0_AD2/ PR0_PRU1_GPO10/<br>PR0_PRU1_GPI10/ MCASP2_AXR6/<br>PR0_PRU0_GPO2/ PR0_PRU0_GPI2/<br>TRC_DATA0/ GPIO0_17                                                                                |

| 16   | N25       | PR0_PRU0_GPO3 | GPMC0_AD3/PR0_PRU1_GPO11/<br>PR0_PRU1_GPI11/ MCASP2_AXR7/<br>PR0_PRU0_GPO3/ PR0_PRU0_GPI3/<br>TRC_DATA1/GPIO0_18                                                                                  |

| 17   | P24       | PR0_PRU0_GPO4 | GPMC0_AD4/PR0_PRU1_GPO12/<br>PR0_PRU1_GPI12/ MCASP2_AXR8/<br>PR0_PRU0_GPO4/PR0_PRU0_GPI4/<br>TRC_DATA2/GPIO0_19                                                                                   |

| 18   | P22       | PR0_PRU0_GPO5 | GPMC0_AD5/PR0_PRU1_GPO13/<br>PR0_PRU1_GPI13/ MCASP2_AXR9/<br>PR0_PRU0_GPO5/PR0_PRU0_GPI5/<br>TRC_DATA3/GPIO0_20                                                                                   |

| 19   | P21       | PR0_PRU0_GPO6 | GPMC0_AD6/PR0_PRU1_GPO14/<br>PR0_PRU1_GPI14/ MCASP2_AXR10/<br>PR0_PRU0_GPO6/PR0_PRU0_GPI6/<br>TRC_DATA4/GPIO0_21                                                                                  |

| 20   | R23       | PR0_PRU0_GPO7 | GPMC0_AD7/PR0_PRU1_GPO15/<br>PR0_PRU1_GPI15/ MCASP2_AXR11/<br>PR0_PRU0_GPO7/ PR0_PRU0_GPI7/<br>TRC_DATA5/GPIO0_22                                                                                 |

## 2.21.2 ユーザー拡張コネクタ

AM62x SIP SK 評価基板は、40 ピン ユーザー拡張コネクタ (メーカー型番 PEC20DAAN) を使用した RPi 拡張インターフェイスをサポートしています。これらの基板を接続できるようにするには、4 つの取り付け穴をコネクタに合わせて取り付ける必要があります。

40 ピンのユーザー拡張コネクタには、以下のインターフェイスおよび IO が含まれるものとします。

- 2x SPI:2 CS 付き SPI0 および 3 CS 付き SPI2

- 2x I2C:SoC\_I2C0 および SoC\_I2C2

- 1 × UART:UART5

- 2x PWM:EHRPWM0\_A, EHRPWM1\_B

- 1 × CLK:CLKOUT0

- 9x GPIO:MAIN ドメインからの GPIO

- 5V および 3.3V 電源 (電流制限:155mA と 500mA)

5V および 3.3V の各電源は、それぞれ 155mA および 500mA に制限されます。これは、2 個の個別ロードスイッチ TPS22902YFPR および TPS22946YZPR を使用して実現しています。ロードスイッチのイネーブルは、I2C ベースの GPIO ポート エクスパンダを介して駆動されます。

ユーザー拡張コネクタから配線された信号を下の表に示します。

図 2-29. 拡張コネクタ

| ピン番号 | SoC ポール | ネット名         | ピン多重化信号                                                                                             |

|------|---------|--------------|-----------------------------------------------------------------------------------------------------|

| 1    | -       | VCC3V3_EXP   |                                                                                                     |