# C28x Embedded Application Binary Interface

Application Note

Literature Number: SPRAC71A MARCH 2019 – REVISED FEBRUARY 2020

# Table of Contents

| 1 Introduction                                             | 7  |

|------------------------------------------------------------|----|

| 1.1 ABIs for the C28x                                      | 8  |

| 1.2 Scope                                                  | 9  |

| 1.3 ABI Variants                                           | 10 |

| 1.4 Toolchains and Interoperability                        | 10 |

| 1.5 Libraries                                              | 10 |

| 1.6 Types of Object Files                                  | 11 |

| 1.7 Segments                                               |    |

| 1.8 C28x Architecture Overview                             |    |

| 1.9 C28x Memory Models                                     |    |

| 1.10 Reference Documents                                   |    |

| 1.11 Code Fragment Notation                                |    |

| 2 Data Representation                                      |    |

| 2.1 Basic Types                                            |    |

| 2.2 Data in Registers                                      |    |

| 2.3 Data in Memory                                         |    |

| 2.4 Pointer Types                                          |    |

| 2.5 Complex Types                                          |    |

| 2.6 Structures and Unions                                  |    |

| 2.7 Arrays                                                 |    |

| 2.8 Bit Fields                                             |    |

| 2.8.1 Volatile Bit Fields                                  |    |

| 2.9 Enumeration Types                                      |    |

| 3 Calling Conventions                                      |    |

| 3.1 Call and Return                                        |    |

| 3.1.1 Call Instructions.                                   |    |

| 3.1.2 Return Instruction                                   |    |

| 3.1.3 Pipeline Conventions                                 |    |

| 3.1.4 Weak Functions.                                      |    |

| 3.2 Register Conventions.                                  |    |

| 3.2.1 Argument Registers.                                  |    |

| 3.2.2 Callee-Saved Registers                               |    |

| 3.3.1 Passing 16-Bit Arguments                             |    |

| 3.3.2 Passing Longer Arguments                             |    |

| 3.3.3 C++ Argument Passing.                                |    |

| 3.3.4 Passing Structs and Unions                           |    |

| 3.3.5 Stack Layout of Arguments Not Passed in Registers    |    |

| 3.3.6 Frame Pointer                                        |    |

| 3.3.4 Return Values                                        |    |

| 3.5 Structures and Unions Passed and Returned by Reference |    |

| 3.6 Conventions for Compiler Helper Functions.             |    |

| 3.7 Prolog and Epilog Helper Functions                     |    |

| 3.8 Scratch Registers for Functions Already Seen           |    |

| 3.9 Interrupt Functions                                    |    |

| 4 Data Allocation and Addressing                           |    |

| 4.1 Data Sections and Segments.                            |    |

| 4.2 Data Blocking                                          |    |

| 4.3 Addressing Modes                                       |    |

| 4.4 Allocation and Addressing of Static Data               |    |

| 5                                                          |    |

| 4.4.4 Addressing Mathada for Statia Data                                                | 20   |

|-----------------------------------------------------------------------------------------|------|

| 4.4.1 Addressing Methods for Static Data                                                |      |

| 4.4.2 Placement Conventions for Static Data                                             |      |

|                                                                                         |      |

| 4.5 Automatic Variables<br>4.6 Frame Layout                                             |      |

| 4.6-1 Stack Alignment                                                                   |      |

| 4.6.2 Register Save Order                                                               |      |

| 4.7 Heap-Allocated Objects                                                              |      |

| 5 Code Allocation and Addressing                                                        |      |

| 5.1 Computing the Address of a Code Label                                               |      |

| 5.2 Calls                                                                               |      |

| 5.2.1 Direct Call                                                                       |      |

| 5.2.2 Far Call Trampoline                                                               |      |

| 5.2.3 Indirect Calls                                                                    |      |

| 6 Helper Function API                                                                   |      |

| 6.1 Floating-Point Behavior                                                             |      |

| 6.2 C Helper Function API                                                               |      |

| 6.3 Floating-Point Helper Functions for C99                                             | 40   |

| 7 Standard C Library API                                                                | 41   |

| 7.1 About Standard C Libraries                                                          | 42   |

| 7.2 Reserved Symbols                                                                    | 42   |

| 7.3 <assert.h> Implementation</assert.h>                                                | 42   |

| 7.4 <complex.h> Implementation</complex.h>                                              | 42   |

| 7.5 <ctype.h> Implementation</ctype.h>                                                  |      |

| 7.6 <errno.h> Implementation</errno.h>                                                  |      |

| 7.7 <float.h> Implementation</float.h>                                                  |      |

| 7.8 <inttypes.h> Implementation</inttypes.h>                                            |      |

| 7.9 <iso646.h> Implementation</iso646.h>                                                |      |

| 7.10 <li>imits.h&gt; Implementation</li>                                                |      |

| 7.11 <locale.h> Implementation</locale.h>                                               |      |

| 7.12 <math.h> Implementation</math.h>                                                   |      |

| 7.13 <setjmp.h> Implementation</setjmp.h>                                               |      |

| 7.14 <signal.h> Implementation</signal.h>                                               |      |

| 7.15 <stdarg.h> Implementation</stdarg.h>                                               |      |

| 7.16 <stdbool.h> Implementation</stdbool.h>                                             |      |

| 7.17 <stddef.h> Implementation</stddef.h>                                               |      |

| 7.18 <stdint.h> Implementation</stdint.h>                                               |      |

| 7.19 <stdio.h> Implementation</stdio.h>                                                 |      |

| 7.20 <stdlib.h> Implementation<br/>7.21 <string.h> Implementation</string.h></stdlib.h> |      |

| 7.21 <suing.n implementation<="" td=""><td></td></suing.n>                              |      |

| 7.22 <time.h> Implementation</time.h>                                                   |      |

| 7.24 <wchar.h> Implementation</wchar.h>                                                 |      |

| 7.25 <wctype.h> Implementation</wctype.h>                                               |      |

| 8 C++ ABI                                                                               |      |

| 8.1 Limits (GC++ABI 1.2)                                                                |      |

| 8.2 Export Template (GC++ABI 1.4.2)                                                     |      |

| 8.3 Data Layout (GC++ABI Chapter 2)                                                     |      |

| 8.4 Initialization Guard Variables (GC++ABI 2.8)                                        |      |

| 8.5 Constructor Return Value (GC++ABI 3.1.5).                                           |      |

| 8.6 One-Time Construction API (GC++ABI 3.3.2)                                           |      |

| 8.7 Controlling Object Construction Order (GC++ ABI 3.3.4)                              |      |

| 8.8 Demangler API (GC++ABI 3.4)                                                         |      |

| 8.9 Static Data (GC++ ABI 5.2.2)                                                        | 51   |

| 8.10 Virtual Tables and the Key function (GC++ABI 5.2.3)                                |      |

| 8.11 Unwind Table Location (GC++ABI 5.3)                                                | 51   |

| 9 Exception Handling                                                                    |      |

| 9.1 Overview                                                                            | 54   |

| 9.2 PREL31 Encoding                                                                     |      |

| 9.3 The Exception Index Table (EXIDX)                                                   |      |

| 9.3.1 Pointer to Out-of-Line EXTAB Entry                                                | . 55 |

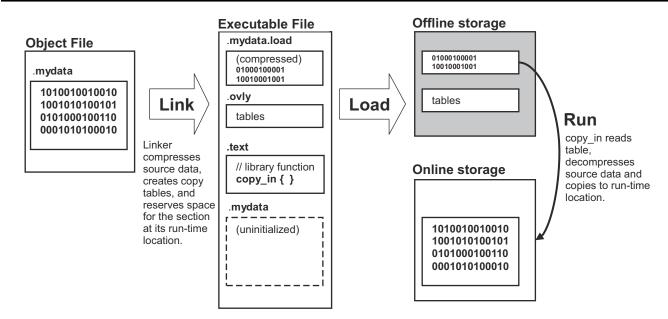

| 14.1 Åbout Copy Tables                                                            | . 88 |

|-----------------------------------------------------------------------------------|------|

| 14 Copy Tables and Variable Initialization                                        | .87  |

| 13.3 C28x Build Attribute Tags                                                    | .85  |

| 13.2 C28x ABI Build Attribute Subsection                                          |      |

| 13.1 About Build Attributes                                                       |      |

| 13 Build Attributes                                                               | .83  |

| 12.2 Program Loading                                                              | .81  |

| 12.1.3 Thread-Local Storage                                                       | .80  |

| 12.1.2 Segment Contents                                                           | .80  |

| 12.1.1 Base Address                                                               |      |

| 12.1 Program Header                                                               |      |

| 12 ELF Program Loading and Linking (Processor Supplement)                         |      |

| 11.5.3 Relocation of Unresolved Weak References                                   |      |

| 11.5.2 Relocation Operations                                                      |      |

| 11.5.1 Relocation Types                                                           |      |

| 11.5 Relocation                                                                   |      |

| 11.4.5 Mapping Symbols                                                            |      |

| 11.4.4 Reserved Symbol Names                                                      |      |

| 11.4.3 Symbol Names                                                               |      |

| 11.4.2 Common Block Symbols                                                       |      |

| 11.4.1 Symbol Types                                                               |      |

| 11.4 Symbol Table                                                                 |      |

| 11.3.6 Section Alignment                                                          |      |

| 11.3.5 Special Sections                                                           |      |

| 11.3.4 Subsections                                                                |      |

| 11.3.3 Extended Section Header Attributes                                         | .72  |

| 11.3.2 Section Types                                                              |      |

| 11.3.1 Section Indexes                                                            |      |

| 11.3 Sections                                                                     |      |

| 11.2 ELF Header                                                                   |      |

| 11.1 Registered Vendor Names                                                      | . 70 |

| 11 ELF Object Files (Processor Supplement)                                        |      |

| 10.4 Vendor Extensions                                                            |      |

| 10.3 Vendor Names                                                                 |      |

| 10.2 Call Frame Information                                                       |      |

| 10.1 DWARF Register Names                                                         |      |

| 10 DWARF                                                                          |      |

| 9.10 Assembly Language Operators in the TI Toolchain                              |      |

| 9.9.3 Interrupts                                                                  |      |

| 9.9.2 Overlays                                                                    |      |

| 9.9.1 Shared Libraries                                                            |      |

| 9.9 Interaction With System Features                                              |      |

| 9.8.2 Hand-Coded Assembly Functions                                               |      |

| 9.8.1 Automatic EXIDX Entry Generation                                            |      |

| 9.8 Interaction With Non-C++ Code                                                 |      |

| 9.7 Special Sections                                                              |      |

| 9.6.5 Function Exception Specification (FESPEC) Descriptor                        |      |

| 9.6.4 Catch Descriptor                                                            |      |

| 9.6.3 Cleanup Descriptor                                                          |      |

| 9.6.2 Scope                                                                       |      |

| 9.6.1 Encoding of Type Identifiers.                                               |      |

| 9.6 Descriptors                                                                   |      |

| 9.5.2 Byte-Encoded Unwinding Instructions                                         |      |

| 9.5.1 Common Sequence                                                             |      |

| 9.5 Unwinding Instructions                                                        |      |

| 9.4.2 EXTAB Compact Model                                                         |      |

| 9.4.2 EXTAB Compact Model                                                         |      |

| 9.4 The Exception Handling Instruction Table (EXTAB)                              |      |

| 9.3.3 Inlined EXTAB Entry<br>9.4 The Exception Handling Instruction Table (EXTAB) |      |

| 9.3.2 EXIDX_CANTUNWIND.                                                           |      |

|                                                                                   |      |

| 14.2 Copy Table Format       |    |

|------------------------------|----|

| 14.3 Compressed Data Formats |    |

| 14.3.1 RLE                   |    |

| 14.3.2 LZSS Format           | 91 |

| 14.4 Variable Initialization |    |

| 15 Revision History          |    |

# **List of Figures**

| Figure 1-1. Parts of the ABI Specification               | 9               |

|----------------------------------------------------------|-----------------|

| Figure 3-1. C28x Registers                               |                 |

| Figure 4-1. Data Sections and Segments (Typical)         |                 |

| Figure 4-2. Local Frame Layout.                          |                 |

| Figure 9-1. Short Form Scope                             | <mark>60</mark> |

| Figure 9-2. Long Form Scope                              |                 |

| Figure 14-1. Copy Table Overview                         |                 |

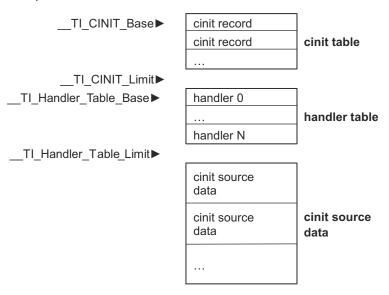

| Figure 14-2. Handler Table Format                        | 90              |

| Figure 14-3. Compressed Source Data Format               | <mark>91</mark> |

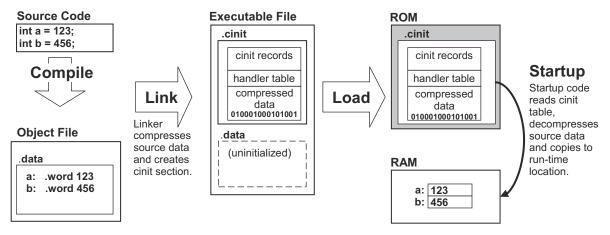

| Figure 14-4. ROM-Based Variable Initialization Via cinit |                 |

| Figure 14-5. The .cinit Section                          | <mark>93</mark> |

# List of Tables

| Table 2-1. Data Sizes for Standard Types                           | . 14               |

|--------------------------------------------------------------------|--------------------|

| Table 2-2. Data Sizes for Pointers                                 |                    |

| Table 3-1. TMS320C28x Register Conventions                         | .21                |

| Table 4-1. TMS320C28x Addressing Modes                             | . 31               |

| Table 6-1. TMS320C28x EABI Functions                               | . 38               |

| Table 6-2. Reserved Floating-Point Classification Helper Functions |                    |

| Table 9-1. C28x TDEH Personality Routines                          | .57                |

| Table 9-2. Stack Unwinding Instructions                            | .58                |

| Table 10-1. DWARF3 Register Numbers for C28x                       | . 66               |

| Table 10-2. DWARF3 Register Numbers for FPU on C28x                | . 67               |

| Table 10-3. TI Vendor-Specific Tags                                |                    |

| Table 10-4. TI Vendor-Specific Attributes                          | . <mark>68</mark>  |

| Table 11-1. Registered Vendors                                     | .70                |

| Table 11-2. ELF Identification Fields                              | .70                |

| Table 11-3. ELF and TI Section Types                               | .71                |

| Table 11-4. C28x Special Sections                                  |                    |

| Table 11-5. C28x Relocation Types                                  | . 76               |

| Table 11-6. C28x Relocation Operations                             | . 78               |

| Table 12-1. Steps to Create a Process Image from an ELF Executable | . 81               |

| Table 12-2. Steps to Initialize the Execution Environment          | .81                |

| Table 12-3. Termination Steps                                      | . <mark>8</mark> 1 |

| Table 13-1. C28x ABI Build Attribute Tags                          | .86                |

| Table 15-1. Revision History                                       | . 95               |

|                                                                    |                    |

This document is a specification for the ELF-based Embedded Application Binary Interface (EABI) for the C28x family of processors from Texas Instruments. The EABI is a broad standard that defines the low-level interface between programs, program components, and the execution environment, including the operating system if one is present. Components of the EABI include calling conventions, data layout and addressing conventions, and object file formats.

This specification aims to enable tool providers, software providers, and users of the C28x to build tools and programs that can interoperate with each other.

| 1.1 ABIs for the C28x               | 8  |

|-------------------------------------|----|

| 1.2 Scope                           |    |

| 1.3 ABI Variants                    |    |

| 1.4 Toolchains and Interoperability | 10 |

| 1.5 Libraries                       | 10 |

| 1.6 Types of Object Files           |    |

| 1.7 Segments                        | 11 |

| 1.8 C28x Architecture Overview      |    |

| 1.9 C28x Memory Models              | 11 |

| 1.10 Reference Documents            |    |

| 1.11 Code Fragment Notation         | 12 |

| -                                   |    |

7

# 1.1 ABIs for the C28x

Prior to release 18.12.0.LTS of TI's C28x Compiler Tools , the one and only ABI for C28x was the original COFF-based ABI. It was strictly a bare-metal ABI; there was no execution-level component.

Release 18.12.0.LTS of the TI Compiler Tools introduced a new ABI called the C28x EABI. It is based on the ELF object file format. It is derived from industry standard models, including the *IA-64 C++ ABI* and the *System V ABI for ELF and Dynamic Linking*. The processor-specific aspects of the ABI, such as data layout and calling conventions, are largely unchanged from the COFF ABI, although there are some differences. Needless to say, the COFF ABI and the EABI are incompatible; that is to say, all of the code in a given system must follow the same ABI. TI's compiler tools support both the new EABI and the older COFF ABI, although we encourage migration to the new ABI as support for the COFF ABI may be discontinued in the future.

A *platform* is the software environment upon which a program runs. The ABI has platform-specific aspects, particularly in the area of conventions related to the execution environment, such as the number and use of program segments, addressing conventions, visibility conventions, pre-emption, program loading, and initialization. Currently bare metal is the only supported platform. The term *bare metal* represents the absence of any specific environment. That is not to say there cannot be an OS; it simply says that there are no OS-specific ABI specifications. In other words, how the program is loaded and run, and how it interacts with other parts of the system, is not covered by the bare-metal ABI.

The bare-metal ABI allows substantial variability in many specific aspects. For example, an implementation may provide position independence (PIC), but if a given system does not require position independence, these conventions do not apply. Because of this variability, programs may still be ABI-conforming but incompatible; for example if one program uses PIC but the other does not, they cannot interoperate. Toolchains should endeavor to enforce such incompatibilities.

# 1.2 Scope

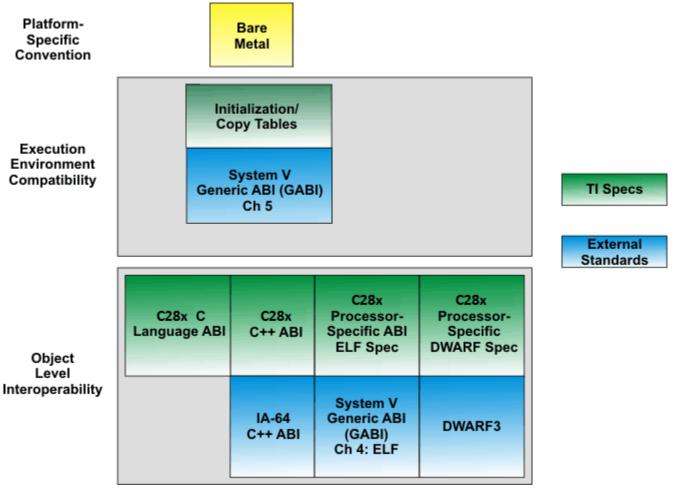

Figure 1-1 shows the components of the ABI and their relationship. We will briefly describe the components, beginning with the lower part of the diagram and moving upward, and provide references to the appropriate chapter of this ABI specification.

The components in the bottom area relate to object-level interoperability.

Figure 1-1. Parts of the ABI Specification

The **C** Language ABI (Chapter 2, Chapter 3, Chapter 4, Chapter 5, Chapter 6 and Chapter 7) specifies function calling conventions, data type representations, addressing conventions, and the interface to the C run-time library.

The **C++ ABI** (Chapter 8) specifies how the C++ language is implemented; this includes details about virtual function tables, name mangling, how constructors are called, and the exception handling mechanism (Chapter 9). The C28x C++ ABI is based on the prevalent IA-64 (Itanium) C++ ABI.

The **DWARF** component (Chapter 10) specifies the representation of object-level debug information. The base standard is the DWARF3 standard. This specification details processor-specific extensions.

The **ELF** component (Chapter 11) specifies the representation of object files. This specification extends the System V ABI specification with processor specific information.

**Build Attributes** (Chapter 13) refer to a means of encoding into an object file various parameters that affect inter-object compatibility, such as target device assumptions, memory models, or ABI variants. Toolchains can use build attributes to prevent incompatible object files from being combined or loaded.

9

The components in the central area of the diagram relate to execution-time interoperability.

The components in the top part of Figure 1-1 augment the ABI with platform-specific conventions that define the requirements for executables to be compatible with an execution environment, such as the number and use of program segments, addressing conventions, visibility conventions, pre-emption, program loading, and initialization. **Bare-Metal** refers to the absence of any specific environment.

Finally, there is a set of specifications that are not formally part of the ABI but are documented here both for reference and so that other toolchains can optionally implement them.

**Initialization** (Chapter 14) refers to the mechanism whereby initialized variables obtain their initial value. Nominally these variables reside in the .data section and they are initialized directly when the .data section is loaded, requiring no additional participation from the tools. However the TI toolchain supports a mechanism whereby the .data section is encoded into the object file in compressed form, and decompressed at startup time. This is a special use of a general mechanism that programmatically copies compressed code or data from offline storage (e.g. ROM) to its execution address. We refer to this facility as *copy tables*. While not part of the ABI, the initialization and copy table mechanism is documented here so that other toolchains can support it if desired.

# 1.3 ABI Variants

As mentioned, the ABI does not define specific behavior in all instances but rather is a canon of principles that allow for platform or system-specific variation. There are model variants within the ABI that may be used or not used. The ABI standardizes the implementation in cases where such variants are used. Some of the variants are incompatible with each other. If any object uses a particular model, all objects must. In such cases, toolchains are expected to use build attributes to prevent incompatible objects from being combined.

• **Bare Metal—Standalone**. This model refers to a single self-contained statically-linked executable. It is the simplest form in terms of interoperability. The relevant parts of the ABI are the object-level components in the lower part of Figure 1-1. Since the executable is statically linked and bound (relocated), there is no need for position-independence.

# 1.4 Toolchains and Interoperability

This ABI is not specific to any particular vendor's toolchain. In fact, its purpose is to enable alternative toolchains to exist and interoperate. The ABI describes how mechanisms are implemented; not how toolchains support them at the user level. Occasionally references are made to the TI tools, these are for illustration only. However, TI's C28x Compiler Tools by nature have unique status since they originate from the silicon vendor and were co-developed with the ABI specification, and in some cases form its basis.

In cases where the behavior of the TI tools conflict with this ABI, it shall be considered a defect in the tools; if you find such a case, please submit a defect report to support@tools.ti.com. However, in cases where this specification is incomplete or unclear, the behavior of the TI tools shall be considered definitive. A major goal of the ABI standard is interoperability with TI tools; toolchain vendors should strive to meet this goal regardless of omissions or ambiguities in the standard itself. Please notify us in such cases and we will endeavor to clarify the specification.

# 1.5 Libraries

Generally, a toolchain includes a linker as well as standard run-time libraries that implement part of the language support provided by the toolchain.

The library format used by the C28x is the common GNU/SVR4 ar format.

Often the linker and libraries have interdependencies that are outside the realm of the ABI. For example, many linkers use special symbols to control the inclusion or exclusion of various library components; alternatively some libraries refer to special linker-defined symbols. For this reason the linker and library are expected to come from the same toolchain. Using a linker from one toolchain and a library from a different one is not supported under this ABI. This only applies to the built-in libraries that are part of the toolchain; application libraries built with a different toolchain can be linked.

# 1.6 Types of Object Files

ELF defines the following distinct classes of object files:

- A **relocatable** file holds code and data suitable for static linking with other object files to create an executable file.

- An executable file holds a program suitable for execution.

This specification uses the terms static link unit and load module interchangeably to refer to executables .

# 1.7 Segments

An ELF load module (an executable file ) represents the memory image of the program in the form of *segments*. In this context a segment is a contiguous, indivisible range of memory with common properties. A segment becomes bound when its address is determined, which happens statically at link time.

# 1.8 C28x Architecture Overview

C28x devices have 16-bit and 32-bit CPU registers.

C28x devices have 32-bit address registers, but almost all C28x devices have only a 22-bit address space.

C28x is compiled in little-endian mode only.

C28x is word-addressable, and words are 16 bits.

There are no 8-bit objects on C28x devices. This presents unique challenges for implementing the ELF object file format on C28x devices. See Chapter 11 for more about ELF files.

# 1.9 C28x Memory Models

C28x EABI supports only one memory model: the unified large memory model. In this model, both pointers and the ptrdiff\_t type are 32 bits.

For information about pointers, see Section 2.4.

#### **1.10 Reference Documents**

| Link or URL                                                                             |

|-----------------------------------------------------------------------------------------|

| SPRU514                                                                                 |

| SPRU513                                                                                 |

| SPRU430                                                                                 |

| http://www.caldera.com/developers/gabi/2003-12-17/contents.html                         |

| http://refspecs.linux-foundation.org/cxxabi-1.83.html                                   |

| http://www.codesourcery.com/public/cxx-abi/abi-eh.html                                  |

| http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.subset.swdev.abi/index.html |

| http://infocenter.arm.com/help/topic/com.arm.doc.ihi0039b/IHI0039B_clibabi.pdf          |

| http://dwarfstd.org/Dwarf3.pdf                                                          |

| http://www.open-std.org/jtc1/sc22/wg14, ISO/IEC 9899:1990                               |

| http://www.open-std.org/jtc1/sc22/wg14, ISO/IEC 9899                                    |

| http://www.open-std.org/jtc1/sc22/wg21, ISO/IEC 14882:1998                              |

|                                                                                         |

# 1.11 Code Fragment Notation

Throughout this document we use code fragments to illustrate addressing, calling sequences, and so on. In the fragments, the following notational conventions are often used:

| sym             | The symbol being referenced                               |  |

|-----------------|-----------------------------------------------------------|--|

| label           | A symbol referring to a code address                      |  |

| func            | A symbol referring to a function                          |  |

| tmp             | A temporary register (also tmp1, tmp2, etc)               |  |

| reg, reg1, reg2 | 2 An arbitrary register                                   |  |

| dest            | The destination register for a resulting value or address |  |

There are several assembler built-in operators introduced. These serve to generate appropriate relocations for various addressing constructs, and are generally self-evident.

This section describes the representation in memory and registers of the standard C data types. Other languages may be supported; the types used by those languages will define their own mapping to these representations.

In the descriptions and diagrams in this section, bit 0 always refers to the least-significant bit.

| 2.1 Basic Types           | 14 |

|---------------------------|----|

| 2.2 Data in Registers     | 15 |

| 2.3 Data in Memory        |    |

| 2.4 Pointer Types         |    |

| 2.5 Complex Types         |    |

| 2.6 Structures and Unions |    |

| 2.7 Arrays                | 16 |

| 2.8 Bit Fields            | 17 |

| 2.9 Enumeration Types     | 18 |

|                           |    |

# 2.1 Basic Types

Integral values use twos-complement representation. Floating-point values are represented using IEEE 754.1 representation. Floating-point operations follow IEEE 754.1 to the degree supported by the hardware.

Table 2-1 gives the size and alignment of C data types in bits.

| Table 2-1. Data Sizes for Standard Types |              |                          |           |

|------------------------------------------|--------------|--------------------------|-----------|

| Туре                                     | Generic Name | Size                     | Alignment |

| signed char                              | schar        | 16                       | 16        |

| unsigned char                            | uchar        | 16                       | 16        |

| char                                     | plain char   | 16                       | 16        |

| bool (C99)                               | uchar        | 16                       | 16        |

| _Bool (C99)                              | uchar        | 16                       | 16        |

| bool (C++)                               | uchar        | 16                       | 16        |

| short, signed short                      | int16        | 16                       | 16        |

| unsigned short                           | uint16       | 16                       | 16        |

| int, signed int                          | int16        | 16                       | 16        |

| unsigned int                             | uint16       | 16                       | 16        |

| long , signed long                       | int32        | 32                       | 32        |

| unsigned long                            | uint32       | 32                       | 32        |

| long long, signed long long              | int64        | 64                       | 32        |

| unsigned long long                       | uint64       | 64                       | 32        |

| enum                                     |              | varies (see Section 2.9) | 32        |

| float                                    | float32      | 32                       | 32        |

| double                                   | float64      | 64                       | 32        |

| long double                              | float64      | 64                       | 32        |

| pointer                                  |              | 32                       | 16        |

The generic names in the table are used in this specification to identify these types in a language-independent way.

The *char* type is unsigned by default. This is in contrast to the "signed char" and "unsigned char" types, which specify their sign behavior.

The integral types have complementary unsigned variants. The generic names are prefixed with 'u' (e.g. uint32).

The type bool uses the value 0 to represent false and 1 to represent true. Other values are undefined.

The additional types from C, C99 and C++ are defined as synonyms for standard types:

```

typedef unsigned long wchar_t;

typedef unsigned long wint_t;

typedef char * va_list;

```

# 2.2 Data in Registers

In general, implementations are free to use registers as they see fit. The standard register representations specified in this section apply only to values passed to or returned from functions.

Some struct objects can reside in registers. See Section 2.6 for more information.

Numeric values in registers are always right justified; that is, bit 0 of the register contains the least significant bit of the value. Signed integral values smaller than 16 bits are sign extended into the upper bits of the register. Unsigned values smaller than 16 bits are zero extended.

C28x has registers of varying sizes. Most commonly-used CPU registers are 16 or 32 bits, and the choice of register depends on the size of the data.

The ACC, P, and XT registers may hold 32-bit data.

- · ACC is a register pair of AH:AL. The two 16-bit subregisters can be accessed independently.

- P is a register pair of PH:PL. The two 16-bit subregisters can be accessed independently.

- XT is T:TL. While T can be accessed independently, TL cannot.

The following register pairs may hold 64-bit data or pointers: ACC:P, XAR1:XAR0, XAR3:XAR2, AR5:XAR4, and XAR7:XAR6. In these pairs, the least-significant bits are contained in the second register of the pair.

The XAR0-XAR7 registers may hold 32-bit pointers.

The AH, AL, T, PH, PL, and AR0-AR7 registers may hold 16-bit data.

For devices that support FPU, the R0-R7 registers may hold 32-bit float values.

For more about C28x registers, see the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (SPRU430).

#### 2.3 Data in Memory

The C28x uses little-endian mode only. Endianness refers to the memory layout of multi-byte values. In little endian mode, the least significant byte is stored at the smallest address. Endianness affects only objects' memory representation; scalar values in registers always have the same representation regardless of endianness. Endianness does affect the layout of structures and bit fields, which carries over into their register representation.

Scalar variables are aligned such that they can be loaded and stored using the native instructions appropriate for their type: MOV for words, and MOVL for doublewords. There are no native instructions to load or store 64-bit types. These instructions correctly account for endianness when moving to and from memory.

# 2.4 Pointer Types

Pointers have the following data sizes.

| Table 2-2. Data Sizes for Pointers |    |    |    |  |

|------------------------------------|----|----|----|--|

| Type Size Storage Alignment        |    |    |    |  |

| function pointer                   | 32 | 32 | 32 |  |

| data pointer                       | 32 | 32 | 32 |  |

| size_t                             | 32 | 32 | 32 |  |

| ptrdiff_t                          | 32 | 32 | 32 |  |

Even though pointers are stored as 32 bites, the compiler should assume that the addresses of global variables and functions are within a 22-bit limit.

# 2.5 Complex Types

The \_Complex types defined in the C99 standard are supported. The internal representation is as follows:

```

struct _Complex

{ float_type real;

float_type imag; };

```

# 2.6 Structures and Unions

Structure members are assigned offsets starting at 0. Each member is assigned the lowest available offset that satisfies its alignment. Padding may be required between members to satisfy this alignment constraint.

Union members are all assigned an offset of 0.

The underlying representation of a C++ class is a structure. Elsewhere in this document the term *structure* applies to classes as well.

The alignment requirement of a structure or union is equal to the most strict alignment requirement among its members, including bit field containers as described in the next section. The size of a structure or union in memory is rounded up to a multiple of its alignment by inserting padding after the last member. Structures and unions passed by value on the stack have special alignment rules as specified in Section 3.3.

In general, structures having size 32 bits or less may reside in registers or register pairs while being passed to or returned from functions. Such structures are passed by value in the R0H-R3H registers, then by value on the stack. Single field structures are passed and returned by value corresponding to the underlying scalar type. See Section 3.5 for information about larger structures and unions passed and returned by reference.

For devices that support FPU32 or FPU64, homogeneous float structures with a size less than 128 bits are passed by value. In addition, for devices that support FPU64, 64-bit doubles (R0-R3) are passed by value.

In little-endian mode a structure in a register is always right justified; that is, the first byte occupies the LSB of the register (the even register if a pair) and subsequent bytes of the structure are filled into the increasingly significant bytes of the register(s). The C28x uses little-endian mode only.

# 2.7 Arrays

The minimum alignment for an object with the array type is that specified by the type of its elements.

| C62x, C67x | 4 bytes |

|------------|---------|

| All others | 8 bytes |

# 2.8 Bit Fields

The C28x EABI adopts its bit field layout from the IA64 C++ ABI. The following description is consistent with that standard unless explicitly indicated.

The **declared type** of a bit field is the type that appears in the source code. To hold the value of a bit field, the C and C++ standards allow an implementation to allocate any *addressable storage unit* large enough to hold it, which need not be related to the declared type. The addressable storage unit is commonly called the *container type*, and that is how we refer to it in this document. The container type is the major determinant of how bit fields are packed and aligned.

For efficiency, the compiler may access a bit-field with a type that does not match either the declared type or the container type. The declared type and container type are strictly used to determine bit field packing and alignment. The type used to actually load the bit-field is the access type. It can be a narrower type, computed from the size and offset of the bit-field. For instance, in the following example, the container type is 32 bits, but the bit-field will be loaded using a 16-bit access:

struct S

{

long :16;

long bf:16;

};

The C89, C99, and C++ language standards have different requirements for the declared type:

| C89 | int, unsigned int, signed int                                                     |

|-----|-----------------------------------------------------------------------------------|

| C99 | int, unsigned int, signed int, _Bool, or "some other implementation-defined type" |

| C++ | Any integral or enumeration type, including bool                                  |

There is no *long long* type in strict C++, but because C99 has it, C++ compilers commonly support it as an extension. The C99 standard does not require an implementation to support long or long long declared types for bit fields, but because C++ allows it, it is not uncommon for C compilers to support them as well.

A bit field's value is fully contained within its container, exclusive of any padding bits. Containers are properly aligned for their type. The alignment of the structure containing the field is affected by that of the container in the same way as a member object of that type. This also applies to unnamed fields, which is a difference from the IA64 C++ ABI. The container may contain other fields or objects, and may overlap with other containers, but the bits reserved for any one field, including padding for oversized fields, never overlap with those of another field.

In the C28x EABI, the container type of a bit field is its declared type, with one exception. C++ allows so-called oversized bit fields, which have a declared size larger than the declared type. In this case the container is the largest integral type not larger than the declared size of the field.

The layout algorithm maintains a *next available bit* that is the starting point for allocating a bit field. The steps in the layout algorithm are:

- 1. Determine the container type T, as described previously.

- 2. Let C be the properly-aligned container of type T that contains the next available bit. C may overlap previously allocated containers.

- 3. If the field can be allocated within C, starting at the next available bit, then do so.

- 4. If not, allocate a new container at the next properly aligned address and allocate the field into it.

- 5. Add the size of the bit field (including padding for oversized fields) to determine the next available bit.

In little-endian mode, containers are filled from LSB to MSB. The C28x uses little-endian mode only.

Zero-length bit fields force the alignment of the following member of a structure to the next alignment boundary corresponding to the declared type, and affect structure alignment.

A declared type of plain *int* is treated as a *signed int* by C28x EABI.

# 2.8.1 Volatile Bit Fields

A volatile bit field is one declared with the C *volatile* keyword. When a volatile bit field is read, its container must be read exactly once using the appropriate access for the entire container.

When a volatile bit field with a size less than its container is written, its container must be read exactly once and written exactly once using the appropriate access. The read and the write are not required to be atomic with respect to each other.

The compiler does not use a narrower type for volatile bit-fields; it will instead use exactly the declared type.

When a volatile bit-field with a size exactly equal to the container size is written, it is unspecified whether the read takes place. Because such reads are unspecified, it is not safe to interlink object files compiled with different implementations if they both write to a volatile bit-field with exactly the width of its container. For this reason, using volatile bit-fields in external interfaces should be avoided.

Multiple accesses to the same volatile bit field, or to additional volatile bit fields within the same container may not be merged. For example, an increment of a volatile bit field must always be implemented as two reads and a write. These rules apply even when the width and alignment of the bit field would allow more efficient access using a narrower type. For a write operation the read must occur even if the entire contents of the container will be replaced. If the containers of two volatile bit fields overlap then access to one bit field will cause an access to the other.

An access to 'a' will also cause an access to 'b', but not vice-versa. If the container of a non-volatile bit field overlaps a volatile bit field then it is undefined whether access to the non-volatile field will cause the volatile field to be accessed.

# 2.9 Enumeration Types

Enumeration types (C type *enum*) are represented using an underlying integral type. Normally the underlying type is int or unsigned int, unless neither can represent all the enumerators. In that case, if long or unsigned long can represent all the enumerators, that type is used. Otherwise, the underlying type is long long or unsigned long long. When both the signed and unsigned versions can represent all the values, the ABI leaves the choice among the two alternatives to the implementation. (An application that requires consistency among different toolchains can ensure the choice of the signed alternative by declaring a negative enumerator.)

The C standard requires enumeration constants to fit in type "signed int", so enum types may only be int or unsigned int in strict ANSI mode. Wider enum types are possible in C++. The TI compiler also allows wider enum types in relaxed and GCC modes.

# Chapter 3 Calling Conventions

| 3.1 Call and Return                                        | 20 |

|------------------------------------------------------------|----|

| 3.2 Register Conventions                                   |    |

| 3.3 Argument Passing                                       |    |

| 3.4 Return Values                                          |    |

| 3.5 Structures and Unions Passed and Returned by Reference | 25 |

| 3.6 Conventions for Compiler Helper Functions              | 26 |

| 3.7 Prolog and Epilog Helper Functions                     | 26 |

| 3.8 Scratch Registers for Functions Already Seen           |    |

| 3.9 Interrupt Functions                                    | 27 |

# 3.1 Call and Return

A function call is made by calling the dedicated LCR instruction, which pushes the return address to the function call stack and branches to the called function. The called function returns by executing a dedicated LRETR instruction, which pops the return address from the stack and branches to it.

#### 3.1.1 Call Instructions

#### 3.1.1.1 Indirect Calls

When the function to be called is not known at compile time, for all architectures, the address of the function will be stored in CPU register XAR7. This instruction reaches the entire address space. For example:

LCR \*XAR7

#### 3.1.1.2 Direct Calls

When the called function is known at compile time, all architectures use a direct call instruction. This instruction may use an immediate, absolute, or symbolic addressing mode. The examples here show only the immediate addressing modes.

The C28x uses the LCR instruction. This addressing mode reaches all valid code memory.

LCR #func ; immediate mode, call func

#### 3.1.2 Return Instruction

A called function returns by executing a dedicated LRET instruction, which pops the return address from the stack and branches to it.

If the function is an interrupt handler function, the IRET instruction is used instead.

#### **3.1.3 Pipeline Conventions**

The C28x pipeline is protected. Consideration of pipeline latencies or instruction completion is not required (though it may be helpful in improving code performance).

#### 3.1.4 Weak Functions

A weak function is a function whose symbol has binding STB\_WEAK. A program can successfully link without a definition of a weak function, leaving references to it unresolved.

The ABI supports calls to imported weak functions; that is, functions potentially defined in a different static link unit. If a reference to a weak function remains unresolved at link time, the linker replaces its address with zeros. The user is responsible for adding a check that the address is not zero or NULL before attempting to call a weak function.

# 3.2 Register Conventions

Implementations must not use the special-purpose registers for any purpose other than the dedicated special purpose. The remaining registers are general-purpose registers.

**SP** is the call stack pointer. The stack pointer must always remain properly aligned, even during hand-coded assembly functions (see Section 4.6.1). TMS320C28x requires alignment to 16-bit words. Stack management and the local frame structure is presented in Section 4.6.

The ABI designates the following as *callee-saved* registers. That is, a called function is expected to preserve them so they have the same value on return from a function as they had at the point of the call.

- XAR1-XAR3

- R4H-R7H (on FPU32)

- R4L-R7L (on FPU64)

All other registers are *caller-save* registers. That is, they are not preserved across a call, so if their value is needed following the call, the caller is responsible for saving and restoring their contents.

| Register | Size    | Description                     |

|----------|---------|---------------------------------|

| ACC      | 32 bits | Accumulator                     |

| AH       | 16 bits | High half of ACC                |

| AL       | 16 bits | Low half of ACC                 |

| XAR0     | 16 bits | Auxiliary register 0            |

| XAR1     | 32 bits | Auxiliary register 1            |

| XAR2     | 32 bits | Auxiliary register 2            |

| XAR3     | 32 bits | Auxiliary register 3            |

| XAR4     | 32 bits | Auxiliary register 4            |

| XAR5     | 32 bits | Auxiliary register 5            |

| XAR6     | 32 bits | Auxiliary register 6            |

| XAR7     | 32 bits | Auxiliary register 7            |

| AR0      | 16 bits | Low half of XAR0                |

| AR1      | 16 bits | Low half of XAR1                |

| AR2      | 16 bits | Low half of XAR2                |

| AR3      | 16 bits | Low half of XAR3                |

| AR4      | 16 bits | Low half of XAR4                |

| AR5      | 16 bits | Low half of XAR5                |

| AR6      | 16 bits | Low half of XAR6                |

| AR7      | 16 bits | Low half of XAR7                |

| DP       | 16 bits | Data-page pointer               |

| IFR      | 16 bits | Interrupt flag register         |

| IER      | 16 bits | Interrupt enable register       |

| DBGIER   | 16 bits | Debug interrupt enable register |

| Р        | 32 bits | Product register                |

| PH       | 16 bits | High half of P                  |

| PL       | 16 bits | Low half of P                   |

| PC       | 22 bits | Program counter                 |

| RPC      | 22 bits | Return program counte           |

| SP       | 16 bits | Stack pointer                   |

| ST0      | 16 bits | Status register 0               |

| ST1      | 16 bits | Status register 1               |

| XT       | 32 bits | Multiplicand register           |

| Т        | 16 bits | High half of XT                 |

| TL       | 16 bits | Low half of XT                  |

In addition, some devices have an FPU instruction set, which adds registers R0-R7.

Figure 3-1 shows the C28x registers. See the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (SPRU430) for more information about the registers.

| T[16]     | TL[16     | ;]                 | XT[32]        |

|-----------|-----------|--------------------|---------------|

| PH[16]    | PL[16     | ·]                 | P[32]         |

| AH[16]    | AL[16     | 6]                 | ACC[32]       |

|           |           |                    | _             |

|           | SP[1      | 6]                 | •             |

| DP        | [16]      | 6/7-bit<br>offset† |               |

| AR0H[16]  | AR0[16    | ]                  | XAR0[32]      |

| AR1H[16]  | AR1[16]   | ]                  | XAR1[32]      |

| AR2H[16]  | AR2[16]   | ]                  | XAR2[32]      |

| AR3H[16]  | AR3[16]   | ]                  | -<br>XAR3[32] |

| AR4H[16]  | AR4[16]   | ]                  | XAR4[32]      |

| AR5H[16]  | AR5[16]   | ]                  | XAR5[32]      |

| AR6H[16]  | AR6[16]   | ]                  | XAR6[32]      |

| AR7H[16]  | AR7[16]   | ]                  | XAR7[32]      |

|           | PC[22]    |                    |               |

|           | RPC[22]   |                    | •             |

|           |           |                    | •             |

|           | ST0[1     | [6]                |               |

|           | ST1[1     | 6]                 |               |

|           |           |                    | 1             |

|           | IER[1     | 6]                 |               |

|           | DBGIEF    | २[16]              |               |

|           | IFR[1     | 6]                 |               |

| Figure 3- | 1. C28x R | Registe            | rs            |

Figure 3-1. C28x Registers

#### 3.2.1 Argument Registers

The registers that may be used to pass arguments include R0-3 (32-bit float arguments for devices that support FPU), ACC:P (64-bit arguments), ACC (32-bit arguments, XAR4 and XAR5 (pointer arguments), and AL and AH (16-bit arguments). The first argument of each type is placed in the register for that type, and remaining arguments of that type are placed on the stack.

On devices with FPU64 support, double precision floats (64-bit) are passed in registers. On devices without FPU64 support, doubles are passed by reference.

See "How a Function Makes a Call" in the TMS320C28x Optimizing C/C++ Compiler User's Guide (SPRU514).

#### 3.2.2 Callee-Saved Registers

A called function is required to preserve the callee-saved registers so that they have the same value on return from a function as they had at the point of the call.

Registers XAR1, XAR2, and XAR3 are callee-saved. If the target supports FPU, the R4H, R5H, R6H, and R7H registers are also callee-saved.

All other general-purpose registers are caller-save; that is, they are not preserved across a call, so if their value is needed following the call, the caller is responsible for saving and restoring their contents.

# 3.3 Argument Passing

The number of arguments passed in registers depends on the size and type of each argument. Arguments are assigned, in declared order, to an available register of the appropriate size. Additional arguments are passed on the stack. See "How a Function Makes a Call" in the *TMS320C28x Optimizing C/C++ Compiler User's Guide* (SPRU514).

#### 3.3.1 Passing 16-Bit Arguments

Arguments with a type that fits in a single CPU register are passed in a single CPU register. That is, types up to 16 bits are passed in a single register. Pointer types are also passed in a single register, regardless of size.

Pointer types are stored as 32-bit values but should be treated as having a 22-bit limit on the address space.

#### Example 1:

C source code:

```

void func1(int a0, int a1, int a2, int a3);

int a0, a1, a2, a3;

void func2(void)

{

func1(a0, a1, a2, a3);

}

```

Compiled assembly code:

| MOVW   | DP <b>,</b> #a0 |      |

|--------|-----------------|------|

| MOV    | AL,@a0          |      |

| MOV    | AH,@al          |      |

| MOVZ   | AR4,@a2         |      |

| MOVZ   | AR5,@a3         |      |

| ; call | instruction     | here |

|        |                 |      |

# Example 2:

C source code:

```

void func1(int *a0, int *a1, int *a2, int *a3);

int a0, a1, a2, a3;

void func2(void)

{

func1(&a0, &a1, &a2, &a3);

}

```

Compiled assembly code:

MOVL XAR4,#a2 MOVL XAR5,#a1 MOVL \*-SP[2],XAR4 MOVL XAR4,#a3 MOVL \*-SP[4],XAR4 MOVL XAR4,#a0 ; call instruction here

# 3.3.2 Passing Longer Arguments

The 32-bit ACC register (AH:AL) is used to pass long arguments.

#### Example:

#### C source code:

```

void func1(int a0, long a1, int a2);

int a0, a2;

long a1;

func2(void)

{

func1(a0, a1, a2);

}

```

#### Compiled assembly code:

The 64-bit ACC:P register pair is used to pass long long arguments.

# Example:

#### C source code:

```

void func1(long long a0);

long long a0;

func2(void)

{

func1(a0);

}

```

#### Compiled assembly code:

# 3.3.3 C++ Argument Passing

In C++, the "this" pointer is passed to non-static member functions in XAR4 as an implicit first argument. (If a non-static member function returns a struct by reference, the order is "&struct", "this".)

#### 3.3.4 Passing Structs and Unions

Structures and unions 32 bits or smaller are passed by value. Structures and unions larger than 32 bits are generally passed by reference, as described in Section 3.5. However, see Section 2.6 for additional cases where structures and unions are passed by value when using FPU32 or FPU64.

#### 3.3.5 Stack Layout of Arguments Not Passed in Registers

Any arguments not passed in registers are placed on the stack in reverse order. Each argument is placed at the next available address correctly aligned for its type, subject to the following additional considerations:

- The stack alignment of a scalar is that of its declared type.

- Regardless of the alignment required by its members, the stack alignment of a structure passed by value is

the smallest power of two greater than or equal to its size. (This cannot exceed 2 bytes, which is the largest

allowable size for a structure passed by value). This is to allow loading arguments with aligned loads, even if

the type is not naturally aligned strictly enough, which might be the case with struct of size 32 containing an

array of char.

- Each argument reserves an amount of stack space equal to its size rounded up to the next multiple of its stack alignment.

For a variadic C function (that is, a function declared with an ellipsis indicating that it is called with varying numbers of arguments), the last explicitly declared argument and all remaining arguments are passed on the stack, so that its stack address can act as a reference for accessing the undeclared arguments.

Undeclared scalar arguments to a variadic function that are smaller than int are promoted to and passed as int, in accordance with the C language.

Alignment "holes" can occur between arguments passed on the stack, but "back-fill" does not occur.

#### 3.3.6 Frame Pointer

C28x does not use a frame pointer. This effectively limits a single call frame to 0xfffe bytes, which is the minimum SP offset supported by any instruction.

# 3.4 Return Values

The function return value is placed in the same register as the usual first argument register, based on its type and size.

- 16-bit results are returned in the AL register.

- 32-bit results are returned in the ACC register.

- 64-bit results are returned in the ACC:P register pair.

- Structs returned by reference are returned in \*XAR6.

- 32-bit float results are returned in R4H for FPU32 and FPU64.

- 64-bit double results are returned in R4 for FPU64. If FPU64 is not supported, double results are returned by reference.

Aggregates larger than 32 bits are returned by reference.

See "How a Called Function Responds" in the *TMS320C28x Optimizing C/C++ Compiler User's Guide* (SPRU514).

# 3.5 Structures and Unions Passed and Returned by Reference

Structures (including classes) and unions larger than 32 bits are passed and returned by reference. See Section 2.6 for additional cases where structures and unions are passed by value when using FPU32 or FPU64.

To pass a structure or union by reference, the caller places its address in the appropriate location: either in a register or on the stack, according to its position in the argument list. To preserve pass-by-value semantics (required for C and C++), the callee may need to make its own copy of the pointed-to object. In some cases, the callee need not make a copy, such as if the callee is a leaf and it does not modify the pointed-to object.

If the called function returns a structure or union larger than 32 bits, the caller must pass an additional argument containing a destination address for the returned value, or NULL if the returned value is not used.

This additional argument is passed in the first argument register as an implicit first argument. The callee returns the object by copying it to the given address. The caller is responsible for allocating memory if required. Typically this involves reserving space on the stack, but in some cases the address of an already-existing object can be passed and no allocation is required. For example, if f returns a structure, the assignment s = f() can be compiled by passing &s in the first argument register.

#### Examples

C source code:

```

struct S { char big[100]; } g;

struct S accepts_and_returns_struct(struct S s)

{

s.big[0] = 1;

return s;

}

void caller(void)

{

struct S w;

w.big[0] = 0;

g = accepts_and_returns_struct(w);

}

```

"Lowered" C code: (higher-level C code converted to lower-level C code)

```

struct S { char big[100]; } g;

void accepts_and_returns_struct(struct S *dst, struct S *sptr)

{

struct S s;

s = *sptr;

s.big[0] = 1;

if (dst) *dst = s;

}

void caller(void)

{

struct S w;

w.big[0] = 0;

accepts_and_returns_struct(&g, &w);

}

```

# 3.6 Conventions for Compiler Helper Functions

The ABI specifies *helper functions* that the compiler uses to implement language features. Generally, these functions adhere to the standard calling conventions. See Section 6.2 for a list of helper functions.

#### 3.7 Prolog and Epilog Helper Functions

The following prolog and epilog functions are used as helper functions to reduce code size. Each function performs a typical POP-and-RET function epilog sequence. Code size is reduced by replacing the typical POP-and-RET epilog sequence with a branch to one of these functions. Each function is named after the number of consecutive registers that it restores.

```

_prolog_c28x_1

_prolog_c28x_2

_prolog_c28x_3

_epilog_c28x_1

_epilog_c28x_2

```

The --opt\_for\_space option performs procedural abstraction by replacing common blocks of code, such as prolog and epilog code, with calls to functions that are defined in the run-time library. For this reason, it is necessary to link with the supplied run-time library when using the --opt\_for\_space option. See "Increasing Code-Size Optimizations" in the *TMS320C28x Optimizing C/C++ Compiler User's Guide* (SPRU514) for more information. Note that this procedural abstraction does not support the FPU registers.

# 3.8 Scratch Registers for Functions Already Seen

When a caller-save register is live across a call, but the callee is known not to modify that register, the compiler may optimize the caller function code by omitting the save and restore around the call. This arises when the definition has been seen.

# **3.9 Interrupt Functions**

Interrupt functions (that is, the assembly function that performs the ISR) must save a number of registers. These registers include AR1H, AR0H, XT, and XAR4-XAR7. The following assembly code performs the proper context save and C environment fixing actions for devices *without* FPU32 support:

| ASP<br>PUSH<br>SPM<br>MOVL<br>MOVL<br>MOVL<br>CLRC<br>CLRC<br>CLRC<br>CLRC<br>; call occ<br>MOVL<br>MOVL<br>MOVL<br>MOVL<br>MOVL<br>POP<br>NASP | ; [CPU_]<br>AR1H:AR0H<br>0<br>*SP++,XT<br>*SP++,XAR4<br>*SP++,XAR5<br>*SP++,XAR5<br>*SP++,XAR7<br>PAGE0,OVM<br>AMODE<br>#  call  <br>Call  <br>CAR7,*SP<br>XAR6,*SP<br>XAR4,*SP<br>XAR4,*SP<br>XAR4,*SP<br>AR1H:AR0H<br>; [CPU] | ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | [CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_]<br>[CPU_] | 3 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|

| NASP<br>IRET                                                                                                                                    | ; [CPU_]<br>; [CPU_]                                                                                                                                                                                                            |                                                                              | _                                                                                                                                        |   |

|                                                                                                                                                 |                                                                                                                                                                                                                                 |                                                                              |                                                                                                                                          |   |

The following assembly code performs the proper context save and C environment fixing actions for devices that do support FPU32:

| ASP            | ; [CPU ]              |             |

|----------------|-----------------------|-------------|

| PUSH           | RB                    | ; [CPU ] x  |

| PUSH           | AR1H:AR0H             | ; [CPU ]    |

| MOVL           | *SP++,XT              | ; [CPU ]    |

| MOVL           | *SP++, XAR4           | ; [CPU ]    |

| MOVL           | *SP++, XAR5           | ; [CPU ]    |

| MOVL           | *SP++,XAR6            | ; [CPU ]    |

| MOVL           | *SP++, XAR7           | ; [CPU ]    |

| MOV32          | *SP++,STF             | ; [CPU ] x  |

| MOV32          | *SP++, R0H            | ; [CPU ]    |

| MOV32          | *SP++,R1H             | ; [CPU ]    |

| MOV32          | *SP++, R2H            | ; [CPU ]    |

| MOV32<br>MOV32 | *SP++,R3H             | ; [CPU ]    |

| SETFLG         | RNDF32=1, RNDF64=1    | ; [CPU ]    |

| SPM            | 0                     | ; [CPU ]    |

| CLRC           | •                     | · · · _ ·   |

|                | PAGE0, OVM            | ; [CPU_]    |

| CLRC           | AMODE                 | ; [CPU_]    |

| LCR            | #  call               | ; [CPU_]  3 |

|                | curs [#  call  ] ; [] |             |

| MOV32          | R3H, *SP              | ; [CPU_]    |

| MOV32          | R2H, *SP              | ; [CPU_]    |

| MOV32          | R1H, *SP              | ; [CPU_]    |

| MOV32          | ROH, *SP              | ; [CPU_]    |

| MOV32          | STF, *SP              | ; [CPU_]    |

| MOVL           | XAR7,*SP              | ; [CPU_]    |

| MOVL           | XAR6,*SP              | ; [CPU_]    |

| MOVL           | XAR5,*SP              | ; [CPU_]    |

| MOVL           | XAR4,*SP              | ; [CPU_]    |

| MOVL           | XT,*SP                | ; [CPU_]    |

| POP            | AR1H:AR0H             | ; [CPU_]    |

| POP            | RB                    | ; [CPU_]    |

| NASP           | ; [CPU_]              |             |

| IRET           | ; [CPU_]              |             |

|                |                       |             |

Interrupts push the SR and PC registers onto the stack and branch to an interrupt handler. To return from an interrupt function, the function must execute the special instruction IRET, which restores the SR register and branches to the PC where the interrupt occurred.

# Chapter 4 Data Allocation and Addressing

| 4.1 Data Sections and Segments               | 30 |

|----------------------------------------------|----|

| 4.2 Data Blocking                            |    |

| 4.3 Addressing Modes                         |    |

| 4.4 Allocation and Addressing of Static Data |    |

| 4.5 Automatic Variables                      |    |

| 4.6 Frame Layout                             | 32 |

| 4.7 Heap-Allocated Objects                   |    |

| • •                                          |    |

# 4.1 Data Sections and Segments

In a relocatable object file that is output by the compiler or assembler, variables are allocated into sections using default rules and compiler directives. A section is an indivisible unit of allocation in a relocatable file. Sections often contain objects with similar properties. Various sections are designated for data, depending on whether the section is initialized, whether it is writable or read-only, how it will be addressed, and what kind of data it contains.

The data sections defined by the ABI are shown in Figure 4-1. Conventions for placement of static variables into sections and for how they are addressed are covered in Section 4.4.2.

The linker combines sections from object files to form segments in an ELF load module (executable ). A segment is a continuous range of memory allocated to a load module, representing part of the execution image of the program.

A load module may contain one or more segments for data, into which the linker allocates stack, heap, and static variables. These items may be grouped into a single segment or use multiple segments, subject only to these restrictions:

- Within a segment, initialized data must precede uninitialized data. This is a structural constraint of ELF.

- Any additional restrictions imposed by the platform-specific conventions.

The run-time environment can dynamically allocate or resize uninitialized data segments, to allocate space for items such as the stack and heap.

Figure 4-1 shows the data sections defined by the ABI, and an abstract mapping of sections into segments. The mapping is only representative; the specific configuration may vary by platform or system. Initialized sections are shaded blue; uninitialized sections are shaded gray.

| Data Sect | ions                          |     |

|-----------|-------------------------------|-----|

| .data     | Initialized read-write data   |     |

| .bss      | Uninitialized read-write data | RAM |

| .stack    | Program stack                 |     |

| .sysmem   | Dynamic data (heap)           |     |

| Read-On |                            |               |

|---------|----------------------------|---------------|

| .const  | Far const (read-only) data | ROM or<br>RAM |

# Figure 4-1. Data Sections and Segments (Typical)

The .const section contains read-only constants. The .const section may be located in read-only memory, and may be addressed using absolute addressing.

The .data section contains initialized read-write data.

The .bss section contains uninitialized read-write data.

Additional special sections that can be placed by the linker command file are listed in Section 11.3.5.

# 4.2 Data Blocking

Blocking ensures that an object fits entirely within a page or begins on a page boundary. Data blocking allows the compiler to reduce the number of unnecessary DP loads.

For C28x EABI, the default blocking rules are:

- Arrays and their sections are not blocked.

- Scalars and their sections are blocked.

- Structs with external linkages (extern in C) are blocked.

- Structs with internal linkages (static in C) are not blocked, but their sections are blocked.

- Uninitialized, initialized, and const data are blocked.

However, data page blocking can result in alignment holes in memory due to aligning data to page boundaries. So, there is a tradeoff between your application's need for code size and speed optimization and its need for data size optimization. You can use the **blocked** and **noblocked** data attributes to control blocking on specific variables. See "Data Page (DP) Pointer Load Optimization" and "Variable Attributes" in the *TMS320C28x Optimizing C/C++ Compiler User's Guide* (SPRU514).

# 4.3 Addressing Modes

C28x devices use a variety of assembly code addressing modes. These modes are briefly listed here and described in detail in the "C28x Addressing Modes" chapter of the *TMS320C28x DSP CPU and Instruction Set Reference Guide* (SPRU430).

The C28x EABI calling convention requires that the address mode bit (AMODE) of the Status Register (ST1) be set to 0, which is the default. Setting AMODE=0 restricts the set of addressing modes allowed, but allows SP-relative addressing.

Note that assembly code may set AMODE=1, so the linker must be prepared to handle 7-bit direct addressing.

| Table 4-1. TM3520C26X Addressing Modes |                        |                        |                                              |  |  |  |

|----------------------------------------|------------------------|------------------------|----------------------------------------------|--|--|--|

| Mode Name                              | Assembly<br>Example    | Relocation<br>Type     | Notes                                        |  |  |  |