# C7000 C/C++ Optimization Guide

User's Guide

Literature Number: SPRUIV4B MAY 2020 – REVISED JANUARY 2022

# Table of Contents

|                                                                 | - |

|-----------------------------------------------------------------|---|

| Read This First                                                 |   |

| Related Documentation                                           |   |

|                                                                 |   |

| 1 Introduction                                                  |   |

| 1.2 C7000 Split Datapath and Functional Units                   |   |

| 2 C7000 C/C++ Compiler Options                                  |   |

| 2.1 Overview                                                    |   |

| 2.1 Overview                                                    |   |

| 2.3 Understanding Compiler Optimization.                        |   |

| 2.3 Onderstanding Complier Optimization.                        |   |

| 2.3.2 Vectorization and Vector Predication                      |   |

| 2.3.3 Loop Collapsing and Loop Coalescing                       |   |

| 2.3.4 Automatic Inlining                                        |   |

| 2.3.5 If Conversion                                             |   |

| 3 Basic Code Optimization                                       |   |

| 3.1 Signed Types for Iteration Counters and Limits              |   |

| 3.2 Floating-Point Division                                     |   |

| 3.3 Loop-Carried Dependencies and the Restrict Keyword.         |   |

| 3.3.1 Loop-Carried Dependencies                                 |   |

| 3.3.2 The Restrict Keyword                                      |   |

| 3.3.3 Run-Time Alias Disambiguation                             |   |

| 3.3 Function Calls and Inlining                                 |   |

| 3.4 Function Calls and mining                                   |   |

| 3.6 If Statements and Nested If Statements                      |   |

| 3.7 Intrinsics                                                  |   |

| 3.8 Vector Types                                                |   |

| 3.9 C++ Features to Use and Avoid                               |   |

| 3.10 Streaming Engine                                           |   |

| 3.11 Streaming Address Generator                                |   |

| 3.12 Optimized Libraries.                                       |   |

| 3.13 Memory Optimizations                                       |   |

| 4 Understanding the Assembly Comment Blocks                     |   |

| 4.1 Software Pipelining Processing Stages.                      |   |

| 4.2 Software Pipeline Information Comment Block                 |   |

| 4.2.1 Loop and Trip Count Information.                          |   |

| 4.2.2 Dependency and Resource Bounds                            |   |

| 4.2.3 Initiation Interval (ii) and Iterations                   |   |

| 4.2.4 Constant Extensions                                       |   |

| 4.2.5 Resources Used and Register Tables                        |   |

| 4.2.6 Stage Collapsing                                          |   |

| 4.2.7 Memory Bank Conflicts                                     |   |

| 4.2.8 Loop Duration Formula                                     |   |

| 4.3 Single Scheduled Iteration Comment Block                    |   |

| 4.4 Identifying Pipeline Failures and Performance Issues.       |   |

| 4.4.1 Issues that Prevent a Loop from Being Software Pipelined. |   |

| 4.4.2 Software Pipeline Failure Messages.                       |   |

| 4.4.3 Performance Issues                                        |   |

| Revision History                                                |   |

| •                                                               |   |

# List of Figures

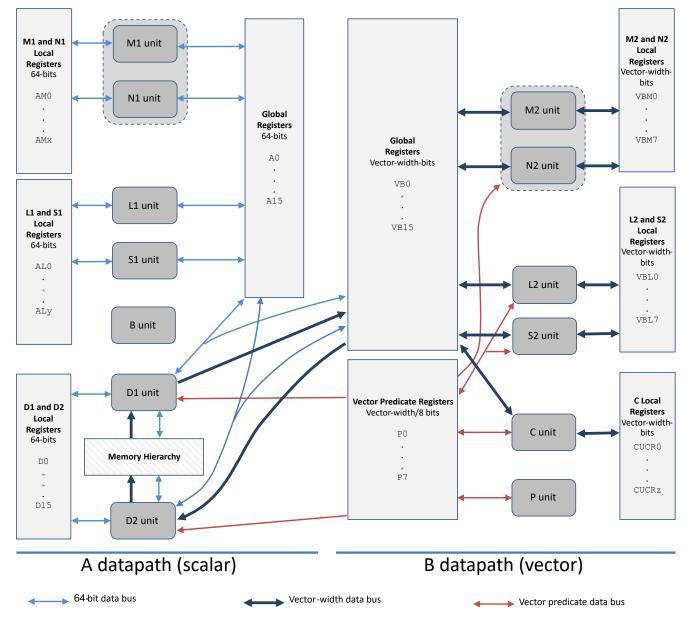

| Figure 1-1. C7000 Datapath Block Diagram                | 9    |

|---------------------------------------------------------|------|

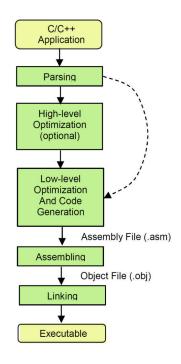

| Figure 2-1. C7000 Compiler Processing Stages            | . 12 |

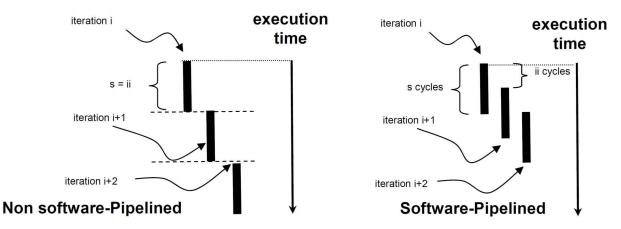

| Figure 2-2. Effects of Software Pipelining on Execution |      |

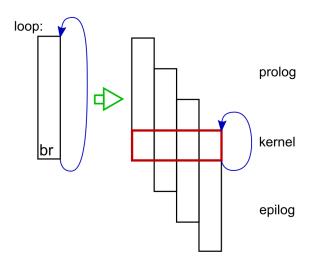

| Figure 2-3. Loop Iterations with Prolog and Epilog      |      |

# About This Manual

This document is for those who want to improve the performance of code running on C7000<sup>™</sup> CPUs.

This guide is not intended to help optimize code for the memory/cache hierarchy, MSMC, DMA, or Matrix Multiply Accelerator (MMA).

Readers of this document should have the following:

- Knowledge of C and C++.

- · Experience invoking the C7000 compiler using compiler options.

- Knowledge of basic assembly language concepts.

- Knowledge of CPU architectural features like registers, caches, and functional units.

#### **Related Documentation**

Use the following documents from Texas Instruments to supplement this user's guide:

- SPRUIG8 C7000 Optimizing C/C++ Compiler User's Guide

- SPRUIG4 C7000 Embedded Application Binary Interface (EABI) Users Guide

- SPRUIU4 C7x Instruction Guide (available through your TI Field Application Engineer)

- **SPRUIP0** C71x DSP CPU, Instruction Set, and Matrix Multiply Accelerator Technical Reference Manual (available through your TI Field Application Engineer)

- **SPRUIQ3** *C71x DSP Corepac Technical Reference Manual* (available through your TI Field Application Engineer)

- SPRU425 C6000<sup>™</sup> Optimizing C Compiler Tutorial

- SPRA666 Hand-Tuning Loops and Control Code on the TMS320C6000™

- SPRABK5 Throughput Performance Guide for KeyStone™ II Devices

- SPRUIG5 C6000-to-C7000 Migration Users Guide

#### Trademarks

C7000<sup>™</sup>, C6000<sup>™</sup>, TMS320C6000<sup>™</sup>, and KeyStone<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

This page intentionally left blank.

Before describing compiler options and source code strategies you can use to make code more efficient, it is necessary to know some information about the C7000 Digital Signal Processor and instruction set. This chapter provides an overview of the C7000 architecture, datapath, and functional units.

| 1.1 C7000 Digital Signal Processor CPU Architecture Overview |  |

|--------------------------------------------------------------|--|

| 1.2 C7000 Split Datapath and Functional Units                |  |

# 1.1 C7000 Digital Signal Processor CPU Architecture Overview

The C7000 CPU DSP architecture is the latest high-performance digital signal processor (DSP) from Texas Instruments. It is featured in some Texas Instruments Keystone 3 devices. This Very-Long-Instruction-Word (VLIW) DSP has significant mathematical processing capabilities, due to its wide vector instructions and multiple functional units. This optimization guide can help developers get the most performance of the C7000 DSPs.

When integrated into a larger TI device, such as some Keystone 3 devices, the C7000 is often paired with a Matrix Multiply Accelerator (MMA), which can significantly improve the performance of certain machine learning networks. We recommend use of the TI Deep Learning library, which has been optimized to use the Matrix Multiply Accelerator. The TI Deep Learning library is part of the Processor SDK.

The C7000 DSP has vector (SIMD) instructions that are capable of performing up to 64 operations in a single instruction, depending on the data type and version of the C7000 CPU. Nearly all computational instructions on C7000 DSP cores are fully pipelined, which means independent instructions can be started on every clock cycle. This combination of vector instructions and pipelined behavior allows you to perform a large number of computations per cycle. The C7000 DSP cores feature both fixed-point and floating-point vector instructions.

Each C7000 DSP core has several functional units. On each clock cycle, each functional unit can be executing an independent instruction. In this guide, we focus on the first generation of C7000 DSP cores, the C7100 and C7120. Because the C7100 and C7120 DSP cores have 13 functional units, there are 13 instructions that can execute every clock cycle. In reality, some of the functional units are specialized for certain kinds of instructions, so for this and other reasons, it is common that not all 13 functional units execute an instruction every cycle.

For more information on the C7000 instruction set, please see the C71x DSP CPU, Instruction Set, and Matrix Multiply Accelerator Technical Reference Manual (SPRUIP0).

# 1.2 C7000 Split Datapath and Functional Units

The following block diagram shows the datapath split on the C7100 DSP CPU. There is an A-side datapath and a B-side datapath. The diagram shows the functional units and multiple, heterogeneous register files. The A-side datapath is responsible for scalar computation, loading and storing scalars and vectors to and from memory, and control-flow (branches, calls). The B-side datapath handles vector math operations, permutations of data, and vector predication operations.

Figure 1-1. C7000 Datapath Block Diagram

To simplify the image above, some data movement capabilities and data paths are not shown in this figure.

- In general, a functional unit can write to any register file on the same datapath.

- Most functional units can obtain data from one or both of the streaming engines.

- There is one 64-bit cross path per datapath (A/B). Each cross path allows one read per cycle from the

opposite side global register file.

On C7100 and C7120 devices, the vector width is 512 bits.

On a given datapath, there are several different kinds of register files. On a given datapath, each functional unit can write to the global register file on that datapath and most of the "local" register files on that datapath. However, only some functional units can read from a "local" register file. Registers are 64-bits per register ("scalar") or 512-bits per register ("vector") and the register files vary in the number of registers.

- D1 and D2 units: These reside on the A-side datapath and can load from and store to memory. Two 64-bit loads can operate in parallel. Two 64-bit stores can operate in parallel. A 64- or 512-bit load can execute in parallel with a 64- or 512-bit load or store. It is not possible for two 512-bit ("vector") stores to be in parallel or two 512-bit ("vector") loads to be in parallel.

- L1, S1, M1, and N1 units: These are general-purpose functional units, handling a varied mix of scalar and small vector computation. The M1 and N1 functional units perform various multiplication instructions.

- L2, S2, M2, and N2 units: These are also general-purpose functional units, but can operate on 512-bit-wide vectors. The M2 and N2 functional units perform various multiplication instructions.

- **B unit:** This unit handles indirect branches and calls.

- C unit: This unit performs permutations and shuffles of data.

- **P unit:** This unit computes predicates used to mask off vector lanes so particular lanes are not computed or are not stored to memory.

In addition to the D1 and D2 units providing CPU access to the memory hierarchy, the C7100 DSP has two "streaming engines" that facilitate a fast path to obtain data from memory. A *streaming engine* is a hardware feature that allows you (or the compiler) to specify a pattern of memory addresses to obtain from memory. The streaming engine will do its best to pre-fetch that data from the memory hierarchy into a scratchpad memory close to the CPU, to minimize CPU stalls due to cold cache misses.

# Chapter 2 C7000 C/C++ Compiler Options

This chapter describes the Texas Instruments C7000 C/C++ Compiler and options that can be used to optimize performance.

| 2.1 Overview                                   | 12 |

|------------------------------------------------|----|

| 2.2 Selecting Compiler Options for Performance |    |

| 2.3 Understanding Compiler Optimization        |    |

# 2.1 Overview

The Texas Instruments C7000 compiler accepts C or C++ source input. When compiling, the compiler proceeds through several stages, as shown in the following figure

Figure 2-1. C7000 Compiler Processing Stages

First, the source file is parsed to create a high-level intermediate representation that closely resembles the source language, but is more tailored for optimization transformations.

Files and functions (optionally) compiled with some level of optimization pass through the high-level optimizer, which performs function inlining, loop transformations, and other code optimizations.

Next, the high-level intermediate language is translated into a low-level intermediate language, which closely resembles assembly. The low-level optimizer and code generation pass performs partitioning, register allocation, software pipelining, instruction scheduling, and other optimizations.

The output of the code generation pass is the assembly file, which is assembled into an object file by the assembler and then linked into a library or executable by the linker.

# 2.2 Selecting Compiler Options for Performance

After your application has been fully debugged and is working properly, it is time to begin the optimization process. First, you need to select appropriate compiler options. The following compiler options affect performance. See the *C7000 C/C++ Compiler User's Guide* (SPRUIG8) for more details on command-line options.

- --opt\_level=3 (-o3). The compiler performs function-level optimization at -opt\_level=2 and file-level optimization and function inlining at --opt\_level=3. At both --opt\_level=2 and --opt\_level=3, the compiler performs various loop optimizations, such as software pipelining, vectorization, and loop coalescing. By default, the --opt\_level switches optimize for performance. Such optimization can increase code size. If code size is an issue, do not reduce the level of optimization. Instead use the --opt\_for\_speed (-mf) switch to change the optimization goal (performance versus code size) and the -oi option to control the amount of automatic inlining.

- --opt\_level=4 (-o4). Consider using this option to perform optimizations across all files at link-time. Using this option can increase compile time significantly. If used for any step, this option must be used at all compilation and linking steps. Source files can be compiled separately, as long as they are all compiled with --opt\_level=4. This optimization level cannot be used with --program\_level\_compile (-pm).

- --gen\_func\_subsections (-mo). Consider using this option if the source code uses many functions that are never called. This option places each function in its own input subsection, so the linker can exclude that function from the executable if it is never referenced. However, this optimization can increase code size, because there are minimum section alignment requirements the compiler must apply.

- --opt\_for\_speed=0 (-mf0) or --opt\_for\_speed=1 (-mf1). If code size is a concern, use these options when compiling files with functions that are not executed often or are not critical to performance. This tells the compiler to optimize for code size instead of performance. Do not lower the optimization level (--opt\_level) in an attempt to lower code size.

*Do not use* the --disable\_software\_pipelining (-mu) option if you are concerned about performance. This option turns off software pipelining. Software pipelining is critical to achieving high performance on most loops. This option can be a debugging tool, as it makes the assembly code easier to understand.

The following options provide additional information for debugging and performance evaluation purposes:

--src\_interlist (-s). This option causes the compiler to emit into the compiler-generated assembly files a copy of what the source code looks like after high-level optimization. This output is placed in the assembly files as comments among the assembly code. The comments output from the optimizer look like C code and show the high-level transformations that have been applied such as inlining, loop coalescing, and vectorization. This option can be useful in helping you understand the assembly code and some of what the compiler is doing to optimize the performance of the code. This option turns on the --keep\_asm (-k) option, so the compiler-generated assembly (.asm) files will not be deleted.

--debug\_software\_pipeline (-mw). This option emits extra information about software-pipelined loops, including the single-scheduled iteration of the loop. This information is used in loop tuning examples presented later in this document. This option turns on the --keep\_asm (-k) option, so the compiler-generated assembly (.asm) files will not be deleted.

--gen\_opt\_info=2 (-on2). This option creates a .nfo file with the same base name as the .obj file. This file contains summary information regarding the high-level optimizations that have been applied, as well as providing advice.

## 2.3 Understanding Compiler Optimization

Before you can interpret the assembly code and the software pipelining information within, it helps to understand some of what the compiler is trying to do with the C/C++ source code as it compiles it into assembly code.

#### 2.3.1 Software Pipelining

Very-Long Instruction Word (VLIW) digital signal processors (DSPs) like the C7000 depend on software pipelining of loops to achieve maximum performance. *Software pipelining* is a technique in which successive iterations of a source loop are overlapped so that the functional units on the CPU are utilized on as many cycles as possible throughout the loop.

The following figure shows loop iteration execution both without and with software pipelining. You can see that without software pipelining, loops are scheduled so that loop iteration *i* completes before iteration *i*+1 begins. With software pipelining, iterations overlap. Thus, as long as correctness can be preserved, iteration *i*+1 can start before iteration *i* finishes. This generally permits a much higher utilization of the machine's resources than might be achieved from other scheduling techniques. In a software-pipelined loop, even though a single iteration might take *s* cycles to complete, a new iteration is initiated every *ii* cycles.

Figure 2-2. Effects of Software Pipelining on Execution

In an efficient software pipelined loop, *ii* is much less than *s*. *ii* is called the initiation interval; it is the number of cycles between starting iteration *i* and starting iteration i+1. *s* is the number of cycles for the first iteration to complete, or equivalently, the length of a single scheduled iteration of the software-pipelined loop.

The compiler attempts to software pipeline the innermost source loops. These are loops that do not have any other loops within them. Note that during the compilation process, software pipelining occurs after inlining and after loop transformations that may combine loops, so in certain cases you may see the compiler software pipelining more of your code than you expect.

After software pipelining, the loop has three major phases, as shown in the following figure:

- pipe-up (prolog) phase during which the overlapped iterations are started.

- steady-state (kernel) phase during which iterations continue to be started.

- pipe-down (epilog) phase during which any iterations that have not yet completed are allowed to finish.

# Figure 2-3. Loop Iterations with Prolog and Epilog

The following example shows the source code for a simple weighted vector sum.

To simplify this first software-pipelining example, two pragmas are used:

- The UNROLL pragma tells the compiler not to perform vectorization, which is a transformation technique that is demonstrated in the next section.

- The MUST\_ITERATE pragma conveys information on how many times the loop executes and is explained later in this document. The example uses this pragma to prevent a "duplicate loop" from being generated, which is also explained later in this document.

Then we compile this code with the following command:

cl7x --opt\_level=3 --debug\_software\_pipeline --src\_interlist --symdebug:none weighted\_vector\_sum.cpp

The --symdebug:none option prevents the compiler from generating debug information and the associated debug directives in the assembly. This debug information is not relevant to the discussion in this document and if included, would unnecessarily lengthen the examples shown here. Normally, you would not turn off debug generation as the generation of debug information does not degrade performance.

# Because the --src\_interlist option is used, the compiler-generated assembly file is not deleted and has the following contents:

|;\*-----\*

|                                             | Loop source<br>Loop openi<br>Loop closi<br>Known Mini<br>Known Max<br>Loop Carri<br>Unpartitice<br>Partitione | ce line<br>ing brace<br>img brace<br>imum Trip<br>Trip Cou<br>ied Depen<br>oned Resc<br>ed Resour | <pre>source line : source line : source line : o Count : int Factor : dency Bound(^) : vurce Bound : 'ce Bound : </pre>                        | 11<br>13<br>1024<br>32<br>0<br>2<br>2 (pre-sched)                                                       |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                             | 2                                                                                                             |                                                                                                   | ware pipeline sch<br>e found with 7 it                                                                                                         | edule at<br>erations in parallel                                                                        |

|                                             | Partitione                                                                                                    | ed Resour                                                                                         | ce Bound(*) :                                                                                                                                  | 2 (post-sched)                                                                                          |

|                                             | SINGLE S                                                                                                      | SCHEDULED                                                                                         | ITERATION                                                                                                                                      |                                                                                                         |

| 0<br>1<br>2<br>7<br>1<br>1<br>1<br>12<br>13 | I<br>I                                                                                                        | TICK<br>SLDW<br>SLDW<br>NOP<br>MPYWW<br>NOP<br>ADDW<br>STW<br>BNL<br>; BRAN                       | .D2 *D2++(4<br>0x5 ; [A_B]<br>.N2 BM2,BM0<br>.M2 BM3,BM1<br>0x3 ; [A_B]<br>.L2 BL1,BL0<br>.D1X B0,*D0+<br>.B1   \$C\$C3<br>ICHCC OCCURS {  \$C | ),BM1 ; [A_D2]  12 <br>,BL0 ; [B_N]  12 <br>,BL1 ; [B_M2]  12                                           |

| \$C\$L1                                     | : ; PI                                                                                                        | IPED LOOP                                                                                         |                                                                                                                                                |                                                                                                         |

|                                             |                                                                                                               | IVE CPU C                                                                                         | YCLES: 8                                                                                                                                       |                                                                                                         |

|                                             |                                                                                                               |                                                                                                   |                                                                                                                                                | ; [A_U] (R) (SP) <1,0><br>; [A_D1]  12  (P) <1,1><br>; [A_D2]  12  (P) <1,1>                            |

|                                             | MV<br>TICK                                                                                                    | .L2X                                                                                              |                                                                                                                                                | ; [B_L2]  7  (R)<br>; [A_U] (P) <2,0>                                                                   |

|                                             | MV<br>SLDW<br>SLDW                                                                                            |                                                                                                   | A8,B1<br>*D1++(4),BM0<br>*D2++(4),BM1                                                                                                          | ; [B_L2]  7  (R)<br>; [A_D1]  12  (P) <2,1><br>; [A_D2]  12  (P) <2,1>                                  |

|                                             | MV<br>MV<br>TICK                                                                                              | .S2<br>.L2                                                                                        | B0,BM2<br>B1,BM3                                                                                                                               | ; [B_S2] (R)<br>; [B_L2] (R)<br>; [A_U] (P) <3,0>                                                       |

|                                             | MPYWW<br>MPYWW<br>SLDW<br>SLDW                                                                                | .N2<br>.M2<br>.D1<br>.D2                                                                          | BM2,BM1,BL0<br>BM3,BM0,BL1<br>*D1++(4),BM0<br>*D2++(4),BM1                                                                                     | ; [B_N]  12  (P) <0,7><br>; [B_M2]  12  (P) <0,7><br>; [A_D1]  12  (P) <3,1><br>; [A_D2]  12  (P) <3,1> |

|                                             | TICK                                                                                                          |                                                                                                   |                                                                                                                                                | ; [A_U] (P) <4,0>                                                                                       |

|                                             | MPYWW<br>MPYWW<br>SLDW                                                                                        | .N2<br>.M2<br>.D1<br>.D2                                                                          | BM2,BM1,BL0<br>BM3,BM0,BL1<br>*D1++(4),BM0<br>*D2++(4),BM1                                                                                     | ; [B_N]  12  (P) <1,7><br>; [B_M2]  12  (P) <1,7><br>; [A_D1]  12  (P) <4,1><br>; [A_D2]  12  (P) <4,1> |

|                                             | SLDW                                                                                                          |                                                                                                   |                                                                                                                                                |                                                                                                         |

| ;                | EXCLUSIVE CPU                      | CYCLES: 2                                  |                                                                                                                                          |

|------------------|------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| <br>  <br>  <br> | MPYWW .N2<br>MPYWW .M2<br>SLDW .D1 | BM2,BM0,BL0<br>BM3,BM1,BL1<br>*D1++(4),BM0 | ; [B_L2]  12  <0,11><br>; [B_N]  12  <2,7><br>; [B_M2]  12  <2,7><br>; [A_D1]  12  <5,1><br>; [A_D2]  12  <5,1>                          |

| <br>  <br>;**    |                                    |                                            | ; [A_B]  10  <0,12><br>; [A_D1]  12  <0,12><br>; [A_U] <6,0>                                                                             |

| \$C\$L3  :       | ; PIPED LOC<br>EXCLUSIVE CPU       |                                            |                                                                                                                                          |

|                  | LDD .D1<br>ADDW .L2<br>MPYWW .N2   | BL1,BL0,B0                                 | ; [A_D2] (O)<br>; [A_D1] (O)<br>; [B_L2]  12  (E) <4,11><br>; [B_N]  12  (E) <6,7><br>; [B_M2]  12  (E) <6,7>                            |

|                  | STW .D1X<br>ADDW .L2               | BL1,BL0,B0<br>B0,*D0++(4)                  | ; [A_D1]  12  (E) <4,12><br>; [B_L2]  12  (E) <5,11><br>; [A_D1]  12  (E) <5,12><br>; [B_L2]  12  (E) <6,11><br>; [A_D1]  12  (E) <6,12> |

| 11               | RET .B1<br>PROT                    | ; [A_B] (O)                                | ; [A_U] (E)                                                                                                                              |

|                  | ; RETURN OCCU                      | RS {RP}                                    | ; [] (0)                                                                                                                                 |

This assembly output shows the software pipelined loop from the compiler-generated assembly file along with part of the software pipelining information comment block, which includes important information about various characteristics of the loop.

If the compiler successfully software pipelines a loop, the compiler-generated assembly code contains a software pipeline information comment block that contains a message about "ii = xx Schedule found with yy iterations in parallel". The *initiation interval*, (ii), is a measure of how often the software pipelined loop is able to start executing a new iteration of the loop. The smaller the initiation interval, the fewer cycles it will take to execute the entire loop. The software-pipelined loop information also includes the source lines from which the loop originates, a description of the resource and latency requirements for the loop, and whether the loop was unrolled (among other information). When compiling with -mw, the information also contains a copy of the single scheduled iteration.

In this example, the achieved initiation interval (ii) is 2 cycles, and the number of iterations that will run in parallel is 7.

The comment block also includes a *single-scheduled iteration* view of the software pipelined loop. The single-scheduled iteration view of the software pipelined loop allows you to see how the compiler transformed the code and how the compiler scheduled one iteration of the software pipelined loop overlap iterations in software pipelining. See Section 4.2 for more information on how to interpret the information in this comment block.

#### 2.3.2 Vectorization and Vector Predication

The C7000 instruction set has many powerful single-instruction, multiple-data (SIMD) instructions that can perform multiple operations in a single instruction. To take advantage of this, the compiler tries to *vectorize* the source code when possible and profitable. Vectorization usually involves using vector (SIMD) instructions to perform an operation on several loop iterations of data at a time.

The following example removes the UNROLL pragma from the example in the previous section. The UNROLL(1) pragma prevented certain loop-transformation optimizations in the C7000 compiler.

The following shows the resulting internal compiler code, which has been vectorized. Vectorization by the compiler can be inferred by the "+= 16" address increments and "32x16" in the names of optimizer temporary variables (to indicate there are 16 32-bit elements in the temporary variable).

```

-----g3:

:**

;** 9

if ( !((d$1 == 1)&U$33) ) goto g5;

_____

;** 9

------

VP$19 = VP$18;

;**

-----g5:

;** 11

_____

VP$20 =

expand vpred p64 U8(VP$19, 2);

;** 11

_____

vstore pred p64 P64 S32(VP$20, &(*(packed int (*)<[16]>)U$52),

*(packed int (*)<[16]>)U$43*VRC$s32x16$001+

*(packed int (*)<[16]>)U$47*VRC$s32x16$002);

;** 9

----- U$43 += 16;

;** 9

_____

U$47 += 16;

;** 9

-----

U$52 += 16;

** 9

-----

--d$1;

;** 9

_____

if ( L$1 = L$1-1 ) goto g3;

```

The software pipeline information block from the resulting assembly file is as follows:

```

;*

SOFTWARE PIPELINE INFORMATION

;*

;*

Loop found in file

: weighted vector sum v2.cpp

;*

: 9

Loop source line

;*

: 10

Loop opening brace source line

;*

Loop closing brace source line

: 12

;*

Loop Unroll Multiple

: 16x

;*

: 1

Known Minimum Trip Count

;*

Known Max Trip Count Factor

: 1

;*

Loop Carried Dependency Bound(^) : 1

;*

Unpartitioned Resource Bound

: 2

;*

Partitioned Resource Bound

: 2 (pre-sched)

;*

;*

Searching for software pipeline schedule at ...

;*

ii = 2 Schedule found with 7 iterations in parallel. . .

;*-----

____/

;*

SINGLE SCHEDULED ITERATION

;*

;*

||$C$C41||:

;*

0

TTCK

; [A U]

*D0++(64),VBM0 ; [A_D1] |11| [SI]

*D1++(64),VBM0 ; [A_D1] |11| [SI]

;*

1

VLD16W .D1

;*

2

VLD16W .D1

;*

0x3

3

NOP

; [A B]

NOF

0x3

; [A_B]

CMPEQW

.S1

A2,0x1,AL0

; [A_S1] |9|

ANDW

.L1

AL1,AL0,AL0

; [A_L1] |9|

VMPYWW

.N2

VBM2,VBM0,VBL0

; [B_N2] |11|

;*

6

;*

7

;*

A2,0xffffffff,A2 ; [A_M1] |9|

;*

ADDW

.M1

CMPEQW .L1

;*

8

AL0,0,A0 ; [A_L1] |9|

VBM1,VBM0,VBL1 ; [B_N2] |11|

;*

VMPYWW .N2

; [B_P] |9| CASE-1

; [B_P] |11|

;*

9

[!A0]

MV

.P2

P2,P1

P1,0x2,P0

;*

10

BITXPND .P2

NOP 0x1

VADDW .L2

;*

11

; [A_B]

, [1,2]

VBL1, VBL0, VB0

; [B_L2] |11|

PO, VB0, *A1(0)

; [A_D2] |11|

A1, 0x40, A1

; [A_S1] |9| [C1]

||$C$$C41||

; [A_B] |9|

;*

12

;*

13

VSTP16W .D2

ADDD .S1

;*

;*

BNL

.B1

14

; BRANCHCC OCCURS {||$C$C41||} ; [] |9|;

```

TEXAS INSTRUMENTS

#### www.ti.com

This example compares the output from that in the previous section to show these effects of vectorization:

- The "optimizer" code after several high-level optimization steps, including vectorization. (This "optimizer" code appears in the assembly when using the -os compiler option.) The address increments are by 16 and there are optimizer temporary variables with the partial name of 32x16, indicating 16 32-bit elements.

- The "SOFTWARE PIPELINE INFORMATION" comment block in the assembly file shows that the loop has been unrolled by 16x. This may or may not indicate vectorization has occurred, but is often associated with vectorization.

- The software pipelined loop now uses the VMPYWW and VADDW instructions. The 'V' in the instruction

mnemonics often (but not always) indicates that the compiler has vectorized a code sequence (using vector/

SIMD instructions).

- Larger address increments in load and store instructions can be another clue that vectorization has occurred.

In this loop, the compiler does not know how many times the loop will execute. Therefore in our example, the compiler must not store to memory an entire vector on the last loop iteration if the number of loop iterations is not a multiple of the number of elements in the vector width that was chosen. For example, if the original (unvectorized) loop will execute 40 iterations and the compiler vectorized the loop by 16, the last optimized iteration will compute 16 elements, but only 8 of them should be stored to memory.

The C7000 ISA has certain vector predication features, where a vector predicate affects which lanes of a vector operation should be performed. In this case, a BITXPND instruction generates a vector predicate that is used in a vector-predicate-aware store instruction. This vector store instruction (VSTP16W) uses the vector predicate to prevent storing to memory those elements on the last iteration that were computed only as a result of the vectorization process and would not have been computed or stored in the original loop. The compiler attempts to perform vector predication automatically during the vectorization process. Vector predication helps avoid the need for generating peeled loop iterations, which can inhibit loop nest optimizations.

#### Note

Vector predicated stores may lead to page faults if the Corepac Memory Management Unit (CMMU) is enabled and the store overlaps an illegal memory page. Any memory range that will be within 63 bytes of an illegal memory page at run-time should be reduced in length in the linker command file. For more information, see the *C7000 C/C++ Compiler User's Guide* (SPRUIG8).

#### 2.3.3 Loop Collapsing and Loop Coalescing

The compiler attempts to *collapse* or *coalesce* nested loops if it is legal and can improve performance. A *nested loop* is a set of two loops where one loop resides inside of another enclosing loop. Both collapsing and coalescing involve transforming a nested loop into a single loop. Collapsing takes place when there is no code in the outer loop. Coalescing takes place when there is code in the outer loop.

After the two nested loops are combined into one loop, the code that was in the body of the outer loop must be transformed so that it conditionally executes only when necessary. Collapsing and coalescing can have performance benefits because only one pipe-up and pipe-down are executed when the loop nest is executed, instead of a pipe-down and pipe-up of the inner loop every time the outer loop executes when loop coalescing/ collapsing is not performed.

In order to perform loop collapsing or loop coalescing, the combined loop must be able to be software pipelined. This means that the loop nest must not contain function calls. The loops must each have a signed counting iterator that iterates a fixed amount each time. That is, the inner loop must not iterate a different number of times depending on which outer loop iteration execution is in. Also, the outer loop must not contain too much code, otherwise the transformation will not improve performance. If the outer loop carries a memory dependence, loop coalescing and loop collapsing likely will not be performed.

When loop collapsing or loop coalescing take place, the software pipelined loop indicates the beginning loop source line ("Loop source line") near the top of the software information comment block. When this source line number references an outer loop, this indicates that the inner loop has been fully unrolled or the compiler has performed loop coalescing or collapsing. In cases of loop coalescing, the compiler uses special instructions, such as NLCINIT, TICK, GETP, and BNL. A description of these hardware features, encompassing what is

known as the "NLC", is beyond the scope of this document. More details of the NLC may be found in the C71x DSP CPU, Instruction Set, and Matrix Multiply Accelerator Technical Reference Manual (SPRUIP0).

#### 2.3.4 Automatic Inlining

The compiler sometimes takes functions defined in header files and places the code at the call site. This allows software pipelining in an enclosing loop and thus improves performance. The compiler may also do this to eliminate the cost of calling and returning from a function.

In the following example, the add\_and\_saturate\_to\_255() function sums two values and caps the sum at 255 if the sum is over 255. This function is called from a function in inlining.cpp, which includes the inlining.h file via a preprocessor #include directive.

```

// inlining.cpp

// Compile with "cl7x -mv7100 --opt level=3

11

--debug_software_pipeline --src_interlist"

#include "inlining.h"

void saturated_vector_sum(int * restrict a, int * restrict b,

int * restrict out, int n)

#pragma MUST ITERATE(1024,,)

#pragma UNROLL(1)

for (int i = 0; i < n; i++)

{

out[i] = add and saturate to 255(a[i], b[i]);

}

// inlining.h

int add_and_saturate_to_255(int a, int b)

int sum = a + b;

if (sum > 255) sum = 255;

return sum;

```

In this case, the compiler will inline the call to add\_and\_saturate\_to\_255() so that software pipelining can be performed. You can determine that inlining has been performed by looking at the bottom of the generated assembly file. Here, the compiler places a comment that add\_and\_saturate\_to\_255() has been inlined. Note that the function's identifier has been modified due to C++ name mangling.

```

;; Inlined function references:

;; [0] _Z23add_and_saturate_to_255ii

```

The inlining can also be seen in the generated assembly code, because there is no CALL instruction to a function in the loop. In fact, because of the inlining (and thus the elimination of the call to a function), the loop can be software pipelined. Software pipelining cannot occur if there is a call to another function in the loop. Note that because of code size concerns, not every call that can be inlined will be inlined automatically. See the *C7000 Optimizing Compiler User's Guide* for more information on inlining.

|   |    | SINGLE S | CHEDULED | ITERATI  | ON                 |             |

|---|----|----------|----------|----------|--------------------|-------------|

|   |    | \$C\$C44 | :        |          |                    |             |

| * | 0  |          | TICK     |          |                    | ; [A U]     |

| * | 1  |          | SLDW     | .D1      | *D1++(4),BL0       | ; [A D1]  5 |

| * | 2  |          | SLDW     | .D2      | *D2++(4),BL1       | ; [A D2]  5 |

| * | 3  |          | NOP      | 0x5      | ; [A B]            | _           |

| * | 8  |          | ADDW     | .L2      | BL1, BL0, BL1      | ; [B L2]  5 |

| * | 9  |          | VMINW    | .L2      | BL2,BL1,B0         | ; [B_L2]  5 |

| * | 10 |          | STW      | .D1X     | B0,*D0++(4)        | ; [A D1]  5 |

| * |    |          | BNL      | .B1      | \$C\$C44           | ; [A B]  11 |

| * | 11 |          | ; BRANG  | снсс осс | URS {  \$C\$C44  } | ; [] 11     |

#### 2.3.5 If Conversion

In order to software pipeline a loop (and thus improve performance), the only branch that may occur in a loop is a branch back to the top of the loop. Branches for if-then and if-then-else statements or for other control-flow constructs will prevent software pipelining.

To get around this limitation, the compiler performs *if-conversion*. If-conversion attempts to remove branches associated with if-then and if-then-else statements, by predicating instructions so that they conditionally execute depending on the test in the "if" statement. As long as there are not too many nesting levels, too many condition terms, or too many instructions in the if-then or if-then-else statements, if-conversion usually succeeds.

The following example demonstrates if-conversion. In order to software pipeline the "for" loop in this C++ code, if-conversion must be performed. The pragmas are used to prevent the compiler from vectorizing and generating additional code that is not important for this example.

```

// if_conversion.cpp

// Compile with "cl7x -mv7100 --opt_level=3 --debug_software_pipeline

// --src interlist --symdebug:none if conversion.cpp"

void function 1(int * restrict a, int *restrict b, int *restrict out, int n)

{

#pragma UNROLL(1)

#pragma MUST ITERATE(1024, ,32)

for (int i = 0; i < n; i++)

{

int result;

if (a[i] < b[i])

result = a[i] + b[i];

else

result = 0;

out [i] = result;

}

}

```

After compilation, the single-scheduled iteration of the loop in the software pipeline information comment block looks like the following:

```

:*-----

;*

SINGLE SCHEDULED ITERATION

;*

;*

||$C$C65||:

;*

0

TICK

; [A_U]

.D1 *D2++(4),A1 ; [A_D1] |17|

.D2 *D1++(4),A2 ; [A_D2] |17|

;*

1

SLDW

;*

^

SLDW

;*

NOP

0x5

; [A_B]

CMPGEW

L1

A2,A1,A0

ADDW

.D2

A1,A2,D3

2

;*

7

; [A L1] |17|

;*

8

; [A_D2] |17|

^

[!A0]

MVKU32 .S1

STW .D1

DNI D1

; [A_S1] |17|

; [A_D1] |17|

; [A_B] |9|

;*

9

[ A0]

0,D3

D3,*D0++(4)

;*

10

;*

||$C$C65||

BNL

.B1

;*

11

; BRANCHCC OCCURS {||$C$C65||}

; [] |9|

;*-

```

The instruction [!A0] ADDW.D2 A1, A2, D3 represents the "then" part of the if statement. The instruction [A0] MVK32.S1 0, D3 represents the "else" part of the if statement. The CMPGEW instruction computes the if-condition and puts the result into a predicate register, which is used to conditionally execute the ADDW and MVKU32 instructions.

This page intentionally left blank.

# Chapter 3 Basic Code Optimization

This section discusses basic code optimization techniques that can be applied to C/C++ code that will run on the C7000 DSP core.

| 3.1 Signed Types for Iteration Counters and Limits       |    |

|----------------------------------------------------------|----|

| 3.2 Floating-Point Division                              | 24 |

| 3.3 Loop-Carried Dependencies and the Restrict Keyword   | 24 |

| 3.4 Function Calls and Inlining                          | 27 |

| 3.5 MUST_ITERATE and PROB_ITERATE Pragmas and Attributes |    |

| 3.6 If Statements and Nested If Statements               | 28 |

| 3.7 Intrinsics                                           |    |

| 3.8 Vector Types                                         | 28 |

| 3.9 C++ Features to Use and Avoid                        |    |

| 3.10 Streaming Engine                                    | 29 |

| 3.11 Streaming Address Generator                         |    |

| 3.12 Optimized Libraries                                 |    |

| 3.13 Memory Optimizations                                | 30 |

# 3.1 Signed Types for Iteration Counters and Limits

In order for automatic vectorization to occur, the iteration counters and iteration limits for loops should have signed types. In other words, use int rather than unsigned int.

The C language standard defines the behavior for unsigned arithmetic overflow, but not for signed arithmetic overflow.

In the unsigned case, an overflowing value will "wrap-around". Therefore, the compiler must assume (in certain cases) that the loop counter may loop around and thus cannot make certain necessary conclusions about the behavior of the loop.

In the signed type case, the compiler can assume the iteration counter will not overflow, because that has undefined behavior according to the C-standard. Thus, the compiler can make certain conclusions about the behavior of the loop and from there may be able to vectorize the loop.

# 3.2 Floating-Point Division

Floating-point division operations can be costly. Often, a division operation results in a run-time-support call to a predefined function that implements floating-point division. Such calls prevent software pipelining.

If your code divides by a constant that is known at compile time, consider pre-calculating the 1/constant value and replacing the division operation with a multiplication by 1/constant. The compiler automatically performs this optimization only if the 1/constant value can be precisely represented in an IEEE-754 float or double.

## 3.3 Loop-Carried Dependencies and the Restrict Keyword

To maximize the efficiency of generated code, the C7000 compiler schedules as many instructions as possible in parallel, especially during software pipelining. To schedule instructions in parallel, the compiler must determine the relationships, or dependencies, between instructions. Dependency means that one instruction must occur before another; for example, a variable must be loaded from memory before it can be used. Because only independent instructions can execute in parallel, dependencies inhibit parallelism.

- If the compiler cannot determine that two instructions are independent, it assumes a dependency and schedules the two instructions sequentially accounting for any latencies needed to complete the first instruction.

- If the compiler can determine that two instructions are independent of one another, it may be able to schedule them in parallel.

#### 3.3.1 Loop-Carried Dependencies

In certain cases when software pipelining, the compiler will not be able to overlap successive iterations of the loop in order to get the best performance. When the compiler is not able to overlap successive iterations of the loop, performance suffers: the initiation interval (ii, described earlier) will be larger than desired and few functional units will be simultaneously utilized.

In almost all cases, this is due to a *loop-carried dependency*. A loop-carried dependency prevents to some degree the execution of iteration  $\pm\pm1$  from overlapping with iteration  $\pm$ . A *loop-carried dependency bound* is a lower limit on the initiation interval of the software pipelined loop (and thus a limit on the speed of the software pipelined loop). A loop-carried dependency bound arises because there is a cycle in the ordering constraints (dependencies) for a set of the instructions in a loop. Out of all these cycle lengths in the loop, the maximum loop-carried dependency cycle is the loop-carried dependency bound. This can occur even if there are plenty of functional units available to perform several iterations in parallel.

If the loop-carried dependency bound is greater than the partitioned resource bound, then one of the loopcarried dependencies is slowing the loop, as the initiation interval is always at least the maximum of the partitioned resource bound and the loop-carried dependency bound.

To reduce or eliminate a problematic loop-carried dependency, one must identify the cycle and then find a way to shorten or break it.

The following example shows a loop with a problematic loop-carried dependency.

The compiler-generated assembly code for this example (shown below) shows that the Loop Carried Dependency Bound in the Software Pipeline Information section of the assembly code is 7 cycles.

```

;*

SOFTWARE PIPELINE INFORMATION

;*

;*

Loop found in file

: weighted_vector_sum_v3.cpp

;*

Loop source line

: 10

Loop opening brace source line : 11

;*

;*

Loop closing brace source line : 13

;*

Known Minimum Trip Count

: 1024

;*

Known Max Trip Count Factor

: 32

;*

Loop Carried Dependency Bound(^) : 12

Unpartitioned Resource Bound

: 2

;*

: 2 (pre-sched)

Partitioned Resource Bound

;*

;*

Searching for software pipeline schedule at ...

;*

ii = 12 Schedule found with 2 iterations in parallel

:*-

;*

SINGLE SCHEDULED ITERATION

;*

;*

||$C$C51||:

0

TICK

; [A_U]

LDW

.D2

*D1++(4),BM0

; [A_D2] |12|

LDW

.D1

*D2++(4),BM1

; [A_D1] |12|

NOP

0x5

; [A B]

;

MPYWW

.M2

BM2, BM0,BL0

; [B_M2] |12|

NOP

0x3

; [A_B]

ADDW

.L2

BL1, BL0, B0

; [B L2] |12|

;*

TICK

; [A U]

;*

~

1

;*

^

;*

2

;*

7

~

;*

, [A_D]

BL1,BL0,BO ; [B_L2] |12|

B0,*D0++(4) ; [A_D1] |12|

||$C$C51|| ; [A_B1 |10|

ZUBS_[]||600000

;*

8

.L2

;*

11

.D1X

STW

;*

12

;*

BNL

.B1

;*

13

; BRANCHCC OCCURS {||$C$C51||} ; [] |10|

;*-

```

The final software pipelined initiation interval of the software pipelined loop is at least the greater of the Loop Carried Dependency Bound and the Partitioned Resource Bound. *When the Loop Carried Dependency Bound value is greater than the Partitioned Resource Bound value, this indicates the code has a loop-carried dependency bound problem that likely should be addressed.* In other words, when the loop-carried dependence bound is greater than the partitioned resource bound, the software pipelined loop could likely run faster if the loop-carried dependency bound is eliminated. Therefore in this example, because the partitioned resource bound is 2 and the loop-carried dependency bound is 12, this code has an issue that should be investigated.

To identify the problem, we need to look at the instructions involved in the loop-carried dependency. These instructions are marked with the caret "^" symbol in the comment block in the compiler-generated assembly file. Notice that the load and store instructions are marked with a caret. This tells us the compiler thinks there *may* be a loop-carried dependence between successive iterations. This is likely because the compiler cannot prove the stores are writing to an area of memory that is independent of the location from which the load instructions are loading values. In absence of information about the locations of the pointers, arrays and address access patterns, the compiler must assume that successive iterations may load from the location of the previous iteration's stores. See *Hand-Tuning Loops and Control Code on the TMS320C6000* (SPRA666) for more about loop-carried dependencies and how to identify them.

#### 3.3.2 The Restrict Keyword

The correct the problem in the previous example caused by a loop-carried dependency, we need to tell the compiler that these arrays do not overlap in memory, and thus there is no memory dependence from one iteration to the next.

Many common digital signal processing loops contain one or more load operations, some computation, and then a store operation. Typically, the loads are reading from an array and the stores are storing values to an array. If the compiler does not know that the arrays are separate (or do not overlap), the compiler must be conservative and assume that the stores of iteration i may be needed in the loads of iteration i+1, or i+2, etc. Therefore, it is important to tell the compiler if the load and store arrays inhabit entirely different memory areas (that is, the objects/arrays pointed-to do not overlap).

We can do this with the use of the restrict keyword. This keyword tells the compiler that throughout the scope of the variable (array name or pointer name used to access the array), accesses to that object or array will only be made through that array name or pointer name.

Note

This description of the restrict pointer is not precisely accurate; it is good enough for most purposes. If you wish to learn more about the restrict keyword, see the C standard or *Demystifying The Restrict Keyword*.

Use of the restrict keyword effectively allows you to tell the compiler that the store to memory will not write to the same place where the next iterations' loads will read from. Thus, successive iterations can be overlapped when the compiler performs software pipelining, thus allowing the generated code to run faster.

This C function example uses the restrict keyword. The resulting Software Pipeline Information comment block will show that when the restrict keyword is used, the loop-carried dependence bound is zero, while the partitioned resource bound is two. This leads to a much-improved initiation interval (ii) of two cycles.

The Texas Instruments C7000 C/C++ Compiler allows the restrict keyword to be used in both C and C++ modes, despite the restrict keyword not being part of the C++14 or C++17 standards.

#### Note

If you use the restrict keyword incorrectly, the compiler will often produce code with undefined behavior--meaning that the code generated by the compiler will produce an incorrect result.

#### 3.3.3 Run-Time Alias Disambiguation

Under certain limited circumstances, the compiler may generate two loops: one that assumes two pointers are not aliased and one that assumes the two pointers are aliased. It generates a run-time check to determine if the two pointers alias. This optimization is called *run-time alias disambiguation*. The advantage is that the loop that assumes no-aliased pointers can usually software pipeline at a much smaller initiation interval, leading to improved performance of the loop.

The compiler cannot always perform run-time alias disambiguation due to considerations that are too technical to describe here. In addition, certain further optimizations such as nested loop coalescing are inhibited when the compiler produces two different loops with a run-time alias check, so it is best to use the restrict keyword whenever legally possible.

For further discussion and details regarding identifying and eliminating loop-carried dependencies, consult the following references:

- TMS320C6000 Programmer's Guide (SPRU198K), Section 2.2.2 "Memory Dependencies"

- Hand-Tuning Loops and Control Code on the TMS320C6000 (SPRA666), Section 4.1, "Using restrict qualifiers, MUST\_ITERATE pragmas, and \_nasserts()"

### 3.4 Function Calls and Inlining

In some instances, functional calls inhibit optimization. For instance, a loop containing a function call will not be software pipelined if the compiler is not able to inline the called function. In order to enable optimizations such as software pipelining, it may be necessary to define the called function in one of these ways:

- In the same source file as the call with the "inline" keyword

- In a .h file included with the #include preprocessor directive, with the called function using the keywords "static inline"

The compiler performs some amount of automatic inlining at the --opt\_level=3 and --opt\_level=4 optimization levels.

# 3.5 MUST\_ITERATE and PROB\_ITERATE Pragmas and Attributes

The compiler can often generate faster code when the compiler knows how many times a loop will execute. Adding this information via the MUST\_ITERATE and PROB\_ITERATE pragmas and the TI\_must\_iterate and TI\_prob\_iterate C++ attributes can help the compiler:

- · Determine if it is profitable to vectorize a loop

- · Determine if it is profitable to perform certain loop optimizations and loop nest optimizations

- Determine if a redundant loop is needed (see Redundant Loops, below)

Before vectorizing a loop, the compiler tries to determine if the change will improve performance. It is helpful if the compiler has information about the iteration counts of the loop so the compiler can make better predictions about the profitability of vectorization. In the same way, the compiler also tries to determine if certain loop optimizations and loop-nest optimizations will be profitable and so information about the iterations counts of the loops can be helpful to the compiler.

Note

Do not provide incorrect information about the trip count in the MUST\_ITERATE pragma or TI\_must\_iterate C++ attribute. If incorrect information is specified in this pragma/attribute, the compiler may create code that produces unexpected and incorrect behavior.

**Redundant Loops:** In some cases, if the compiler does not know how many times a loop will execute, the compiler generates two different versions of the loop. Software pipelined loops often must execute a certain minimum number of iterations to be legal to execute. If the iteration count of the loop is less than this *minimum safe trip count*, the compiler generates a run-time iteration count check and branches to either the software pipelined version of the loop, or a *duplicate loop*. That is, the compiler generates a "regular" version of the loop (that executes much more slowly).

The minimum safe trip count depends on how many iterations were scheduled in parallel and how effectively the compiler was able to perform an optimization called *stage collapsing*. See Section 4.2.6 for more information.

The Software Pipeline Information in the comment block in the assembly file specifies the minimum safe trip count (iteration count) of the loop and states whether the compiler has generated a duplicate loop.

Because the compiler must sometimes generate a redundant loop and the control code necessary to choose between the two loops, it is helpful to tell the compiler the minimum iteration count of the loop with a MUST\_ITERATE pragma when it is known, as the redundant loop may not be necessary. This can improve performance, especially when the loop is enclosed within an outer loop and if the compiler can then perform loop collapsing or other loop optimizations with the outer and inner loops.

The following example shows redundant loop generation information in the Software Pipeline Information section of the assembly comment block.

| ;* | Redundant loop generated |   |   |

|----|--------------------------|---|---|

| ;* | Collapsed epilog stages  | : | 5 |

| ;* | Prolog not removed       |   |   |

| ;* | Collapsed prolog stages  | : | 0 |

## 3.6 If Statements and Nested If Statements

Because software pipelined loops may not have any control flow except for the branch to the kernel, any calls or control-flow (if-statements) will prevent software pipelining. To mitigate the effect that control-flow inside a loop has on whether the loop is software pipelined, the compiler performs "if-conversion" on some if statements, which adds a proper predicate onto the instructions in the "then" and "else" clauses. Because there are a limited number of machine predicate registers, and because of other factors, you should limit the nesting level of if-statements inside loops you hope will software pipeline.

### 3.7 Intrinsics

If the compiler is not using the specialized C7000 instructions you would like it to use, or if the operation is not easily expressed in C (for example, saturated add), there may be an intrinsic available for use in C/C++ code. The available intrinsics appear in the .h files in the include directory of the compiler installation directory.

# 3.8 Vector Types

If the compiler is not vectorizing a loop, consider using vector types. See the C7000 Optimizing C/C++ Compiler User's Guide (SPRUIG8) for more information.

Be aware that the compiler may vectorize some operations in a loop, but not others, leading to an inefficient loop. In this instance, it may be best to vectorize the loop by hand using vector types and intrinsics.

#### 3.9 C++ Features to Use and Avoid

Some C++ features incur in a run-time penalty. Other features are handled completely at compile-time and thus do not cause a run-time penalty. A full discussion of which C++ features do and do not incur a run-time penalty is outside the scope of this document; discussion is available from several sources on the internet and in print.

Some features that do incur a run-time penalty are so useful in providing the desired level of abstraction and/or safety, that you should consider using them anyway. Here are some guidelines for some of the more commonly-used features:

These features have potential run-time overheads. Consider whether the benefits are worth the cost:

- Calls to new(), although this is essentially no more or less expensive than malloc()

- Use of the Standard Template Library (STL), mainly due to hidden calls to new()

- Exceptions / exception handling

- Run-Time Type Information (RTTI)

- Multiple inheritance

- Virtual functions (although the run-time cost is usually small)

Use these features freely, as they have little to no run-time overhead:

- Templates

- Operator overloading

- Function overloading

- Inlining

- Well-designed inheritance. In particular, calling a member function of a derived class incurs no penalty if the object type is known at compile-time.

The following features improve performance and should be used where possible:

- Use of const

- Use of constexpr

- Passing objects by-reference instead of passing objects by-value

- · Constructs and expressions that can be evaluated at compile-time versus run-time

## 3.10 Streaming Engine

The C7100 CPU has two *streaming engines*. A streaming engine is a feature of the C7000 CPU cores that aids in loading data from memory to the CPU. The streaming engines can significantly improve the performance of the memory hierarchy by prefetching data from memory to a location near the CPU. Prefetching data can significantly reduce the time needed to bring data into the CPU. It may also reduce the number of L1 data cache capacity misses as the L1 cache is bypassed for data accessed through the streaming engine.

The streaming engine supports up to a six-dimensional address access pattern. When the performance bottleneck involves reads from memory (if D unit resource bound dominates or cache misses dominate), consider using one or both of the streaming engines if the access pattern to the objects in memory is known in advance. Streaming engines have the greatest effect when used in conjunction with loops that are vectorized by hand. For more information on the streaming engine and code examples, please see the *C71x DSP CPU*, *Instruction Set, and Matrix Multiply Accelerator Technical Reference Manual* (SPRUIP0), the *C7000 Optimizing C/C++ Compiler User's Guide* (SPRUIG8), and the c7x\_strm.h file in the include directory of the compiler's installation directory.

The C7000 compiler does not yet make automatic use of the streaming engine feature.

## 3.11 Streaming Address Generator

Use of a *streaming address generator* can help limit the number of instructions required to calculate an address used for a load or store instruction. This in turn can reduce the resource bound of the software-pipelined loop and so can positively affect the initiation interval of the loop (and thus improve performance of the loop). It can also allow loop collapsing or loop coalescing to occur, possibly leading to improved performance of the loop.

There are four streaming address generators on C7100 cores. For more information and code examples, please see the *C71x DSP CPU*, *Instruction Set*, and *Matrix Multiply Accelerator Technical Reference Manual* (SPRUIP0), the *C7000 Optimizing C/C++ Compiler User's Guide* (SPRUIG8) and the c7x\_strm.h file in the include directory of the compiler installation directory.

The C7000 compiler does not yet make automatic use of the streaming address generator feature.

#### 3.12 Optimized Libraries

If available, use libraries that are optimized for the C7000 core, such as TI's Deep Learning Library (TIDL). See the Processor SDK for Jacinto 7 documentation for more information about the available libraries.

# 3.13 Memory Optimizations

Optimizations that improve the loading and storing of data are often crucial to the performance of an application. A detailed examination of useful memory optimizations on Keystone 3 devices is outside the scope of this document. However, the following are the most common optimizations used to aid memory system throughput and reduce memory hierarchy latency.

- **Blocking:** Input, output, and temporary arrays/objects are often too large to fit into Multicore Shared Memory Controller (MSMC) or L2 memory. For example, when performing an algorithm over an entire 1000x1000 pixel image, the image is too large to fit into most or all configurations of L2 memory, and the algorithm may thrash the caches, leading to poor performance. Keeping the data as close to the CPU as possible improves memory system performance, but how do we do this when the image is too large to fit into the L2 cache? Depending on the algorithm, it may be useful to use a technique called "blocking," in which the algorithm is modified to operate on only a portion of the data at a given time. Once that "block" of data is processed, the algorithm moves to the next block. This technique is often paired with the other techniques in this list.

- **Direct Memory Access (DMA):** Consider using the asynchronous DMA capabilities of the device to move new data into MSMC memory or L2 memory and DMA to move processed data out. This frees the C7000 CPU to perform computations while the DMA is readying data for the next frame, block, or layer.

- **Ping-Pong Buffers:** Consider using ping-pong memory buffers so that the C7000 CPU is processing data in one buffer while a DMA transfer is occurring to/from another buffer. When the C7000 CPU is finished processing the first buffer, the algorithm switches to the second buffer, which now has new data as a result of a DMA transfer. Consider placing these buffers in MSMC or L2 memory, which is much faster than DDR memory.

# Chapter 4 Understanding the Assembly Comment Blocks

This chapter provides an explanation of the Software Pipeline Information block added to the assembly output by the --debug\_software\_pipeline compiler option and the Single Scheduled Iteration block added by the --src interlist compiler option.

| 4.1 Software Pipelining Processing Stages                | 32 |

|----------------------------------------------------------|----|

| 4.2 Software Pipeline Information Comment Block          |    |

| 4.3 Single Scheduled Iteration Comment Block             |    |

| 4.4 Identifying Pipeline Failures and Performance Issues | 37 |

# 4.1 Software Pipelining Processing Stages

The C7000 compiler goes through three basic stages when software pipelining a loop. The three stages are:

- 1. Qualify the loop for software pipelining

- 2. Collect loop resource and dependency graph information

- 3. Attempt to software pipeline the loop

By the time the compiler tries to software pipeline an inner loop, the compiler may have applied certain transformations to the code in the loop, and also may have combined adjacent or nested loops.

#### Stage 1: Qualification

Several conditions must be met before software pipelining is allowed, or found to be legal, from the compiler's point of view. Two of the most common conditions that cause software pipelining to fail are:

- The loop cannot have too many instructions. Loops that are too big typically require more registers than are available and require a longer compilation time.

- Another function cannot be called from within the loop unless the called function is inlined. Any break in control flow makes it impossible to software pipeline, since multiple iterations are executing in parallel.

If any conditions for software pipelining are *not* met, qualification of the pipeline halts and a disqualification messages appears. See Section 4.4.1. for troubleshooting and Section 4.2.1 for information provided during this stage.

If all conditions for software pipelining are met, the compiler continues to Stage 2.

#### Stage 2: Collecting Loop and Dependency Information

The second stage of software pipelining involves collecting loop resource and dependency graph information. See Section 4.2.2 for information about output from this stage.

#### **Stage 3: Software Pipelining Attempts**

Once the compiler has qualified the loop for software pipelining, partitioned it, and analyzed the necessary loop carry and resource requirements, it can attempt software pipelining.

The compiler attempts to software pipeline a loop starting at a certain *initiation interval* (ii). Each time a compiler software pipelining attempt at a particular initiation interval fails, the ii is increased, and another software pipelining attempt is made. This can be seen in the Software Pipeline Information comment block. This process continues until a software pipelining attempt succeeds or ii sequal to the length of a scheduled loop with no software pipelining. If ii reaches the length of a scheduled loop with no software pipeline stop and the compiler generates a non-software pipelined loop. See Section 4.2.3 for more about the information provided during this stage.

If a software pipelining attempt is not successful, the compiler provides additional feedback to help explain why. See Section 4.4.2 for a list of the most common software pipeline failures and strategies for mitigation.

After a successful software pipeline schedule and register allocation is found at a particular initiation interval, more information about the loop is displayed. See Section 4.2.4, Section 4.2.5, Section 4.2.6, Section 4.2.7, and Section 4.2.8.

# 4.2 Software Pipeline Information Comment Block

The subsections that follow describe some of the information found in the Software Pipeline Information comment block that is added to the generated assembly source file when you use the -debug\_software\_pipeline compiler option. The --keep\_asm option is used automatically in this case to preserve the assembly output.

By understanding the feedback that is generated when the compiler pipelines a loop, you may be able tune your C code to obtain better performance.

# 4.2.1 Loop and Trip Count Information

If the compiler qualifies the loop for software pipelining, the first few lines look like the following example:

```

SOFTWARE PIPELINE INFORMATION

;*

;*

;*

Loop found in file

: s.cpp

;*

Loop source line

: 5

;*

Loop opening brace source line : 6

;*

Loop closing brace source line : 8

: 768

;*

Known Minimum Trip Count

;*

: 1024

Known Maximum Trip Count

;*

Known Max Trip Count Factor : 256

```

The loop counter is called the "trip counter" because it is the number of trips through a loop. The statistics provided in this section of the block are:

- Loop found in file, Loop source line, Loop opening brace source line, Loop closing brace source line: Information about where the loop is located in the original C/C++ source code.

- Known Minimum Trip Count: The minimum number of times the loop might execute given the amount of information available to the compiler.

- Known Maximum Trip Count: The maximum number of times the loop might execute given the amount of information available to the compiler.

- Known Max Trip Count Factor: The maximum number that will divide evenly into the trip count. Even though the exact value of the trip count is not deterministic, it may be known that the value is a multiple of 2, 4, etc., which may allow more aggressive packed data/SIMD optimization.

The compiler tries to identify information about the loop counter such as minimum value (known minimum trip count), and whether it is a multiple of something (has a known maximum trip count factor).

If a Max Trip Count Factor greater than 1 is known, the compiler might be more aggressive in packed data processing and loop unrolling optimizations. For example, if the exact value of a loop counter is not known but it is known that the value is a multiple of some number, the compiler may be better able to unroll the loop to improve performance.

#### 4.2.2 Dependency and Resource Bounds

The second stage of software pipelining involves collecting loop resource and dependency graph information. The results of Stage 2 are shown in the Software Pipeline Information comment block as follows:

```

;*Loop Carried Dependency Bound(^) : 2;*Unpartitioned Resource Bound : 12;*Partitioned Resource Bound : 12 (pre-sched)

```

The statistics provided in this section of the block are: