## Application Note

## TI のプログラマブル ロジック デバイス (TPLD) を使用するオープンドレイン出力および消費電力

## 概要

このアプリケーション ノートでは、TI のプログラマブル ロジック デバイス (TPLD) が採用しているオープンドレイン出力とミックスド シグナル 電圧回路の使用方法について説明し、これらの回路に関する設計の原理と課題の概要を示します。このドキュメントでは、低電圧のデジタル処理と高電圧センシングやアクチュエーションを組み合わせた、産業用制御システム、医療機器、個人用電子アプリケーションなど、複数の電圧ドメインと接続する必要があるシステムでのこれらの回路の使用に特に焦点を当てて説明します。

## 目次

|                      |   |

|----------------------|---|

| 1 TPLD での混合電圧ロジックの概要 | 2 |

| 2 出力モードの概要紹介         | 2 |

| 3 オープンドレイン出力のタイミング   | 3 |

| 4 消費電力の計算            | 6 |

| 5 まとめ                | 6 |

| 6 参考資料               | 6 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 TPLD での混合電圧ロジックの概要

デバイスの小型化と電力効率の向上が求められ、多くの半導体デバイスや回路設計では、1.8V などの低い電源電圧レベルを使用するようになっています。このようなテクノロジーと製造の進歩の中で、既存のデバイスとの統合を管理したり、3.3V や 5V などの高い電源電圧を必要とする可能性がある業界規格に準拠したりするという課題に直面しています。これらの課題に対処するため、ロジック デバイス内の機能である電圧レベル変換は、プロセッサ、センサのようなデバイスやさまざまな世代のデバイス間のブリッジとして機能します。電圧変換の包括的な説明については、『[電圧レベル変換の基礎](#)』を参照してください。

TI のプログラマブル ロジック デバイス (TPLD) は、電圧の昇圧変換と降圧変換が可能であり、さまざまなロジック レベルの使用を可能にします。すべての TPLD には入力ピン用の低電圧デジタル入力モードがオプションで用意されており、すべての電源電圧にわたって 1.8V ロジック入力が可能です。同様に、TPLD はオプションのオープンドレイン NMOS 出力モードを使用することで電圧変換を容易にできます。これらの TPLD 機能の使用方法の詳細については、『[TI のプログラマブル ロジック デバイス \(TPLD\) での昇圧および降圧変換](#)』を参照してください。

## 2 出力モードの概要ご紹介

CMOS デバイスには 3 つの同相出力モードがあり、TPLD ではこれらのモードはすべてオプションです。モードには、プッシュプル、オープンドレイン、トライステートがあります。

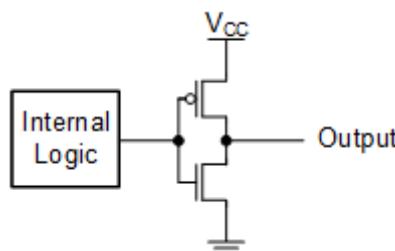

図 2-1. 標準的なプッシュプル出力の構成

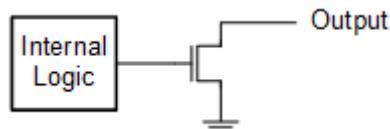

図 2-2. 標準的なオープンドレインの構成

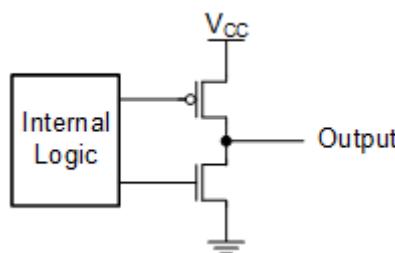

図 2-3. 標準的なトライステート出力の構成

オープンドレイン出力とプッシュプル出力の違いは、出力が出力信号を駆動する方法です。プッシュプル出力は、2 個のトランジスタを使用してラインを High と Low の両方でアクティブに駆動します。一方のトランジスタを VCC にプッシュし、もう一方のトランジスタをグランドにプルすることで、両方向に強い駆動を発生させます。オープンドレイン出力には、ラインをグランドにプルするトランジスタのみがあります。オープンドレイン出力は、トランジスタがオフのときにラインを High にするために外付けプルアップ抵抗に依存します。その結果、プッシュプル出力は両方の状態をアクティブに制御しますが、オープンドレインはラインをパッシブに High に解放し、ラインをアクティブに Low にプルします。名前が示すように、トライステート出力は、いつでも次の 3 つの状態のいずれかになります。

- High に駆動する

- Low に駆動する

- 駆動しない (ハイインピーダンス)

トライステート出力はプッシュプルデバイスと似ていますが、ハイインピーダンス状態が追加されています。

出力タイプの選択は、信号の使用方法と、設計においてどのトレードオフが最も重要かで決まります。プッシュプル出力は、高速エッジまたは頻繁なスイッチングが必要な場合に優れています。オープンドレイン出力は、信号ラインが複数のデバイスで共有されている場合、レベルの柔軟性が必要な場合、またはほとんどの時間信号がアイドル状態の場合に適しています。信号ラインが複数のデバイスで共有される場合はトライステート出力が適していますが、外付け抵抗の使用は望ましくありません。トライステート出力では多くの場合、ハイインピーダンス状態への移行と解除のために、追加の入力が必要になります。

プッシュプル出力は、主にスイッチング中に電力を消費し、スイッチング中に負荷容量をアクティブに充電および放電します。オープンドレイン出力デバイスとは異なり、プッシュプル出力デバイスは、Low信号のために抵抗を通じて電流をプルする必要がないため、頻繁にトグルする信号や長時間 Low に維持される信号に対して、プッシュプルは電力効率が向上します。

小さなリーク電流以外に、オープンドレイン出力は信号が High のときは実質的に電力を消費しません。これにより、オープンドレインのデバイスは、ステータスラインや割り込みなど、High 状態でアイドルになり、頻繁にスイッチングしない信号に最適です。ただし、オープンドレイン出力は、Low 信号を生成するためにプルアップ抵抗を介して電流を引き込む必要があります。プルアップ抵抗のサイズを大きくすると消費電流を低減できますが、抵抗を大きくするとスイッチング速度が低下し、ライン上で負荷を駆動するデバイスの能力に影響を及ぼす可能性があります。

### 3 オープンドレイン出力のタイミング

オープンドレイン出力は、外部プルアップ抵抗に依存して出力電圧を High にします。その結果、出力の立ち上がり時間はプルアップ抵抗の値と、ピン容量や寄生容量を含む負荷容量に依存します。プルアップ抵抗と負荷容量の組み合わせは、標準的な抵抗コンデンサ (RC) 回路のすべての特性動作を備えています。

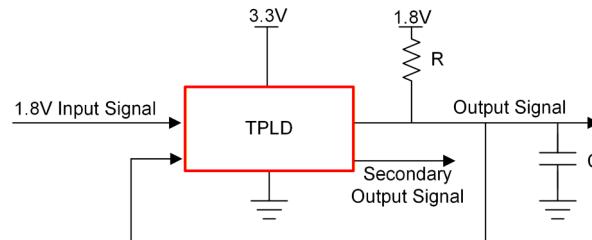

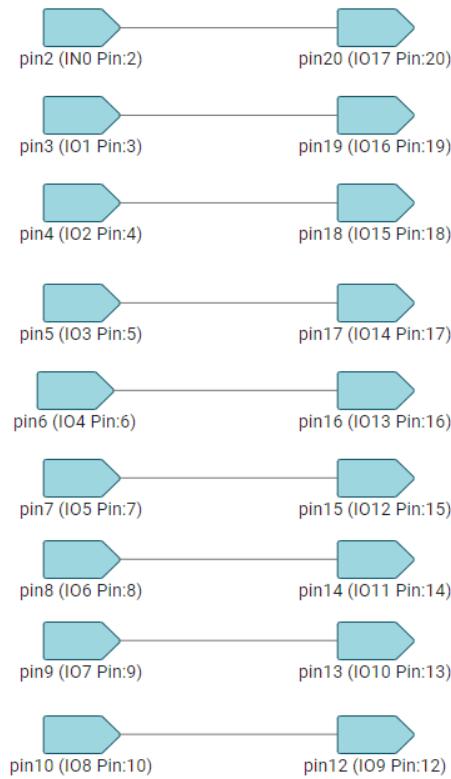

例として、このセクションでは、図 3-2 に示す基本的なバッファ構成を使用した 図 3-1 に示す設定を参照しています。

図 3-1. TPLD オープンドレイン出力の例

図 3-2. TPLD バッファ構成

この出力信号は RC 回路の一部であり、Low 状態から High 状態に遷移するときに観測される電圧は、次の式で決まります。

$$V_C = V_S (1 - e^{-t/RC}) \quad (1)$$

RC 回路の 10% ~ 90% 立ち上がり時間は次の式で与えられます。

$$t_{rise} = 2.2\tau = 2.2RC \quad (2)$$

この場合、 $V_S$  はプルアップ抵抗からの 1.8V 電源であり、 $V_C$  は C 両端の電圧です。

式 1 は、多くのアプリケーションで負荷容量を変更することは容易ではないため、オープンドレイン デバイスの立ち上がり時間がプルアップ抵抗に依存することを示しています。つまり、特定のアプリケーションに適した抵抗値を選択することが非常に重要になります。オームの法則により、抵抗を大きくすると電流が減少するので、消費電力が減少します。ただし、抵抗が大きいと、出力信号の立ち上がり時間も長くなります。

オームの法則では、使用可能なプルアップ抵抗の最小サイズ、したがって最大立ち上がり時間も規定されます。この式は、次のとおりです。

$$R_{pullup, min} = \frac{V_{out}}{I_{OL}} \quad (3)$$

すべてのオープンドレイン デバイスは、最大 Low レベル出力電流  $I_{OL}$  を定義しており、これを用いて、大電流でデバイスに損傷を与えるリスクを冒す前に、許容される最小の抵抗を計算できます。TPLD2001 の例を続けます。 $I_{OL}$  には 2 つのオプションがあります。この例では、 $I_{OL} = 20mA$  を選択し、 $V_{OUT} = 1.8V$  です。この選択により、 $R_{pullup, min} = 90\Omega$  にな

ります。この抵抗は立ち上がり時間が高速になりますが、多くの電力を消費します。9k $\Omega$  抵抗の代わりに 90 $\Omega$  の抵抗を選択すると、立ち上がり時間が 100 倍短くなりますが、消費電力が 10,000 倍に増加します。この結果が妥当とみなされるかどうかは、設計要件によって異なります。

オープンドレイン出力の立ち上がり時間はプルアップ抵抗のサイズに依存しますが、立ち下がり時間はそうではありません。オープンドレイン デバイスは出力をパッシブに High に解放しますが、デバイスは出力をアクティブに Low にプルします。この結果、オープンドレイン出力デバイスの立ち上がり時間と立ち下がり時間は非対称になります。

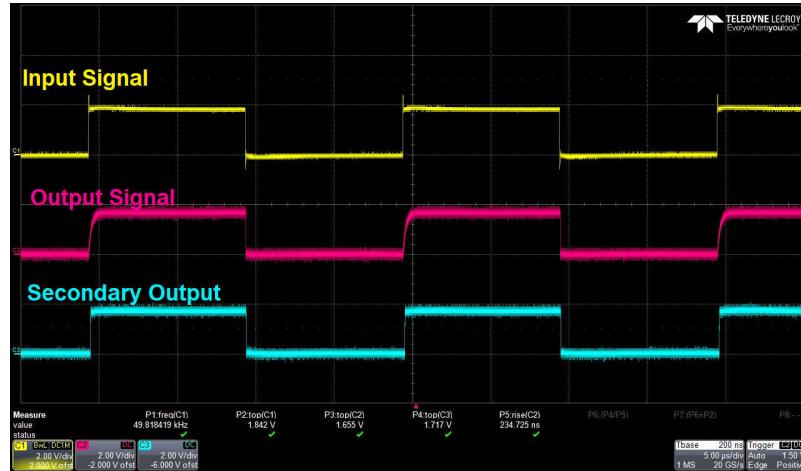

図 3-3. 50kHz での入出力

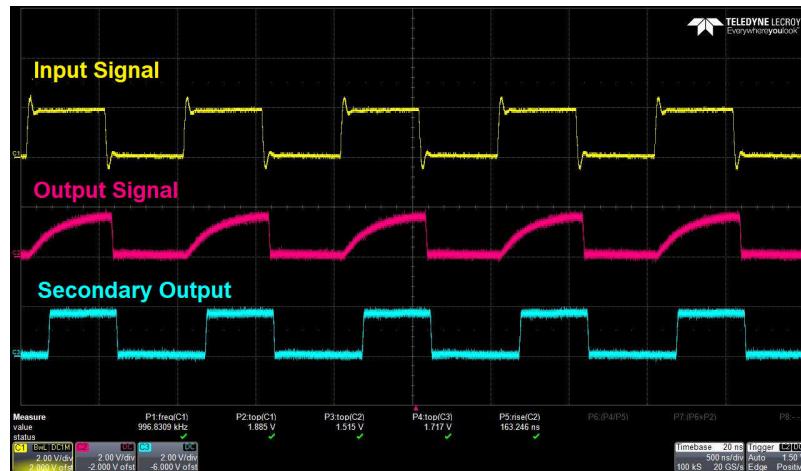

図 3-4. 1MHz での入出力

図 3-3 および図 3-4 の波形は、図 3-1 に示すテスト設定構成の入力と出力を示しています。この設定には、低電圧入力を持つシンプルなバッファとして構成された TPLD2001 抵抗が含まれており (図 3-2 を参照)、TPLD が 3.3V レールから電力を供給されても 1.8V ロジックに対応できます。TPLD には、1.8V から直接電力を供給することもできます。「2 次側出力」とラベル付けされた出力は、プッシュプル出力として構成されています。プルアップ抵抗は 10k $\Omega$  です。50kHz で、この大きなプルアップ抵抗の影響が明らかになります。1MHz では、出力信号の低速な立ち上がり時間が 2 次側出力信号のデューティサイクルに影響を及ぼし始めます。TPLD2001 抵抗は、プッシュプルモードでは任意の出力ピンから最大 8MHz までの周波数を出力できますが、抵抗のオープンドレイン モード出力の出力速度は依然として RC 時定数によって決定されます。このため、オープンドレイン出力は高速アプリケーションに適していることはほとんどありません。

プルアップ抵抗の選択方法の詳細については、『オープンドレイン出力に適切なプルアップ/プルダウン抵抗の選択』を参照してください。

## 4 消費電力の計算

CMOS デバイスでは、デバイスの静的消費電力と動的消費電力が重要です。この点については TPLD も同様です。

CMOS デバイスの静的消費電力は、次の式を使用して計算されます。

$$P_{S, \text{Device}} = V_{\text{Supply}} I_{CC} \quad (4)$$

プッシュプル デバイスでは、これは、出力がスイッチしないときにデバイスの VCC ピンから引き込まれるすべての電力です。オープンドレイン デバイスの場合、この計算は依然として有効ですが、システム全体としては、外付けプルアップ抵抗から引き込まれる電流も含まれます。[図 3-1](#) の例を使用すると、これは 1.8V ソースです。出力が **Low** の場合、システムの消費電力には、プルアップ抵抗によってデバイス内で消費される電力に加えて、デバイスの 3.3V ソースから引き出される電力も含まれます。オープンドレイン デバイスのシステムの合計消費電力には、以下を含める必要があります。

$$P_{S, \text{Total}} = P_{S, \text{Device}} + N_{\text{Low}} \frac{V^2}{R} \quad (5)$$

[式 5](#) は、消費電力が懸念される場合に大きなプルアップ抵抗が有効であることを示しています。特に、多くの出力が同時に **Low** 状態の場合に有効です。ただし、前のセクションで示したように、より大きいプルアップ抵抗を使用するとスイッチング速度に悪影響を及ぼします。オープンドレイン デバイスの主なトレードオフとして、タイミングと消費電力を考慮する必要があります。

動的消費電力は、もう少し複雑です。このタイプの消費電力には、過渡消費電力と容量性負荷の消費電力が含まれ、デバイスがある状態から別の状態に切り替わるときにのみ発生します。動的消費電力には、外部負荷容量の充電に消費される電力、内部ノードの充電に必要な電力、および P チャネルと N チャネルのトランジスタの両方が同時に短時間オンになったときに Vcc から GND に流れる貫通電流の消費電力が含まれます。オープンドレインの NMOS モードで使用すると、類似のオープンドレイン デバイスと同様に、オープンドレイン出力モードの TPLD によって貫通電流が回避されます。

このトピックの詳細については、[『CMOS の消費電力と Cpd の計算』](#)を参照してください。

## 5 まとめ

TPLD は電圧の昇圧変換と降圧変換を実行できるため、さまざまなロジックレベルを使用できます。また、オプションのオープンドレイン NMOS 出力モードにより出力での電圧変換が容易になります。オープンドレイン出力は、ステータスラインや割り込みなど、High でアイドル状態になり、頻繁にはスイッチしない信号に適しています。これらの信号は、信号が High のときは事実上電力を消費せず、信号を出力で互いに接続できるため、バス競合の危険性が生じません。オープンドレイン出力を使用するシステムの消費電力を考慮する場合、出力信号の立ち上がり時間と消費電力に影響を与えるため、適切なプルアップ抵抗の選択が重要です。抵抗が大きいほど、消費電力は低減されますが、立ち上がり時間が長くなります。これらのトレードオフを理解することは、優れたシステム設計に不可欠です。

## 6 参考資料

- テキサスインスツルメンツ、『電圧変換の基礎』アプリケーション レポート

- テキサスインスツルメンツ、『TI のプログラマブル ロジック デバイス (TPLD) での昇圧および降圧変換』アプリケーション ブリーフ

- テキサス・インスツルメンツ、『オープンドレイン出力に適切なプルアップ/プルダウン抵抗の選択』アプリケーション レポート

- テキサス・インスツルメンツ、『CMOS の消費電力と Cpd の計算』アプリケーション レポートノート

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月