## Application Note

**AM62Px eMMC HS400 基板の設計およびシミュレーションガイド

ライン***Sitara MPU HW Apps***概要**

このアプリケーション レポートには、AM62Px プロセッサ ボードの設計の eMMC HS400 インターフェイスに適用できる資料が含まれています。

**目次**

|                                    |    |

|------------------------------------|----|

| <b>1 概要</b>                        | 3  |

| 1.1 サポート対象のボード設計                   | 3  |

| 1.2 一般的なボードレイアウト ガイドライン            | 3  |

| 1.3 PCB 積層                         | 4  |

| 1.4 バイパスコンデンサ                      | 4  |

| 1.4.1 バルク バイパス コンデンサ               | 4  |

| 1.4.2 高速バイパスコンデンサ                  | 5  |

| 1.5 速度補正                           | 5  |

| <b>2 eMMC 基板の設計およびレイアウトのガイドライン</b> | 6  |

| 2.1 eMMC の紹介                       | 6  |

| 2.2 eMMC 信号終端                      | 6  |

| 2.3 信号配線仕様                         | 6  |

| 2.4 電源の設計                          | 7  |

| <b>3 eMMC ボード設計シミュレーション</b>        | 11 |

| 3.1 ボードモデルの抽出                      | 11 |

| 3.2 ボード - モデルの検証                   | 11 |

| 3.3 コンデンサ ループのインダクタンス              | 11 |

| 3.4 AC インピーダンス                     | 12 |

| 3.5 IBIS モデル シミュレーション              | 13 |

| 3.5.1 シミュレーションの設定                  | 13 |

| 3.5.2 シミュレーション ビット パターン            | 15 |

| 3.5.3 シミュレーションのベスト プラクティス          | 15 |

| 3.5.4 シミュレーション戦略と例                 | 15 |

| 3.5.5 合格 / 不合格チェック                 | 19 |

| <b>4 設計例</b>                       | 42 |

| 4.1 スタックアップ                        | 42 |

| 4.2 電力ルーティング                       | 42 |

| 4.3 信号の配線取り回し                      | 44 |

| <b>5 まとめ</b>                       | 47 |

| <b>6 参考資料</b>                      | 47 |

**図の一覧**

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| 図 2-1. SK-AM62P-LP (PROC164E2) 最上層 - VDDS_MMCO (紫)、GND (緑)、VDDR_CORE (赤).....     | 8  |

| 図 2-2. SK-AM62P-LP (PROC164E2) 最下層 - VDDS_MMCO (紫)、GND (緑)、および VDDR_CORE (赤)..... | 9  |

| 図 3-1. VDDS_MMCO AC インピーダンス振幅と周波数との関係 (ボードのみ).....                                | 13 |

| 図 3-2. システムレベルの代表的な eMMC 回路図.....                                                 | 14 |

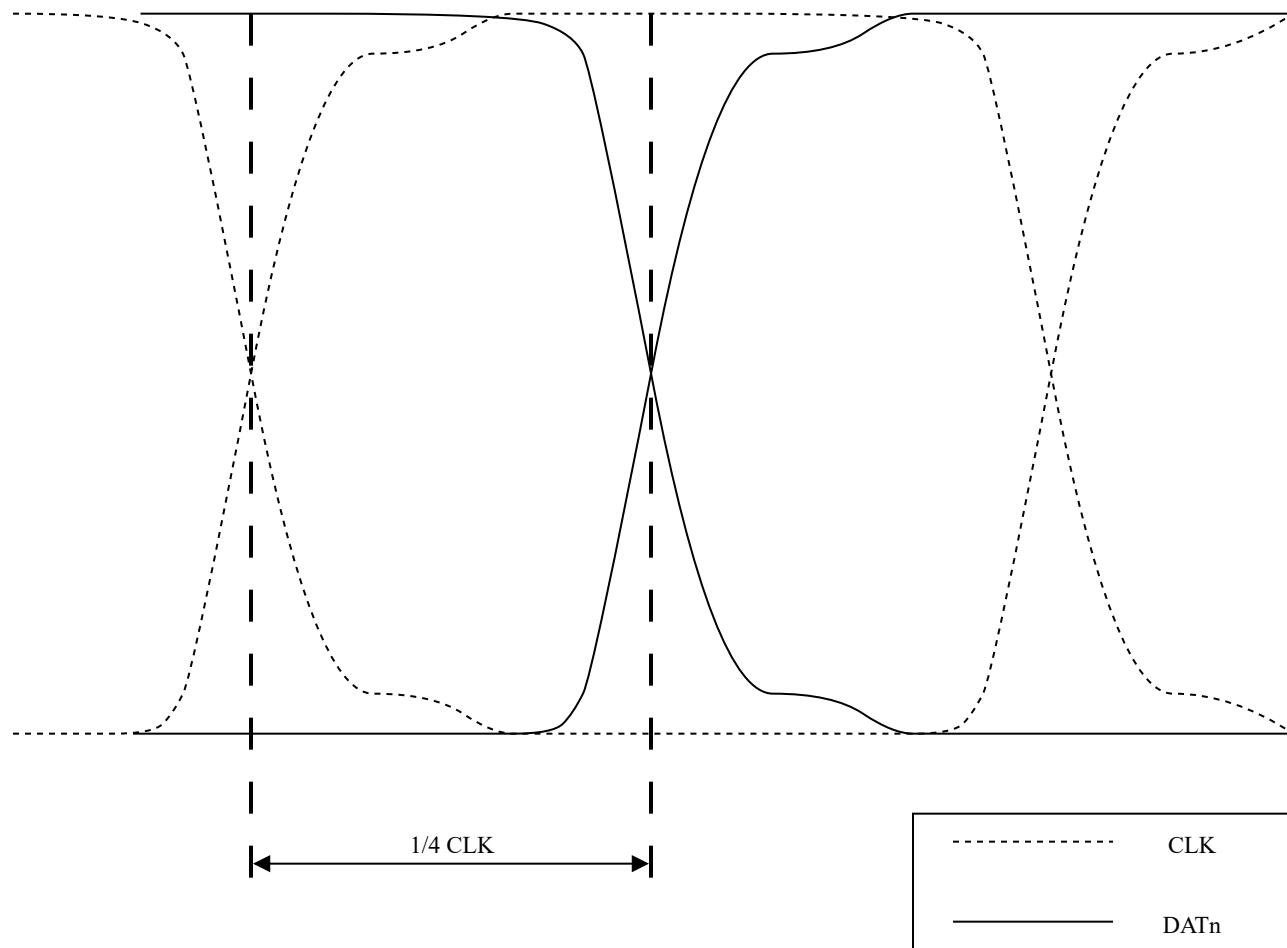

| 図 3-3. セットアップ / ホールド時間:CLK に対する DATA のオフセット (1/4 CLK サイクル遅延).....                 | 27 |

|                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

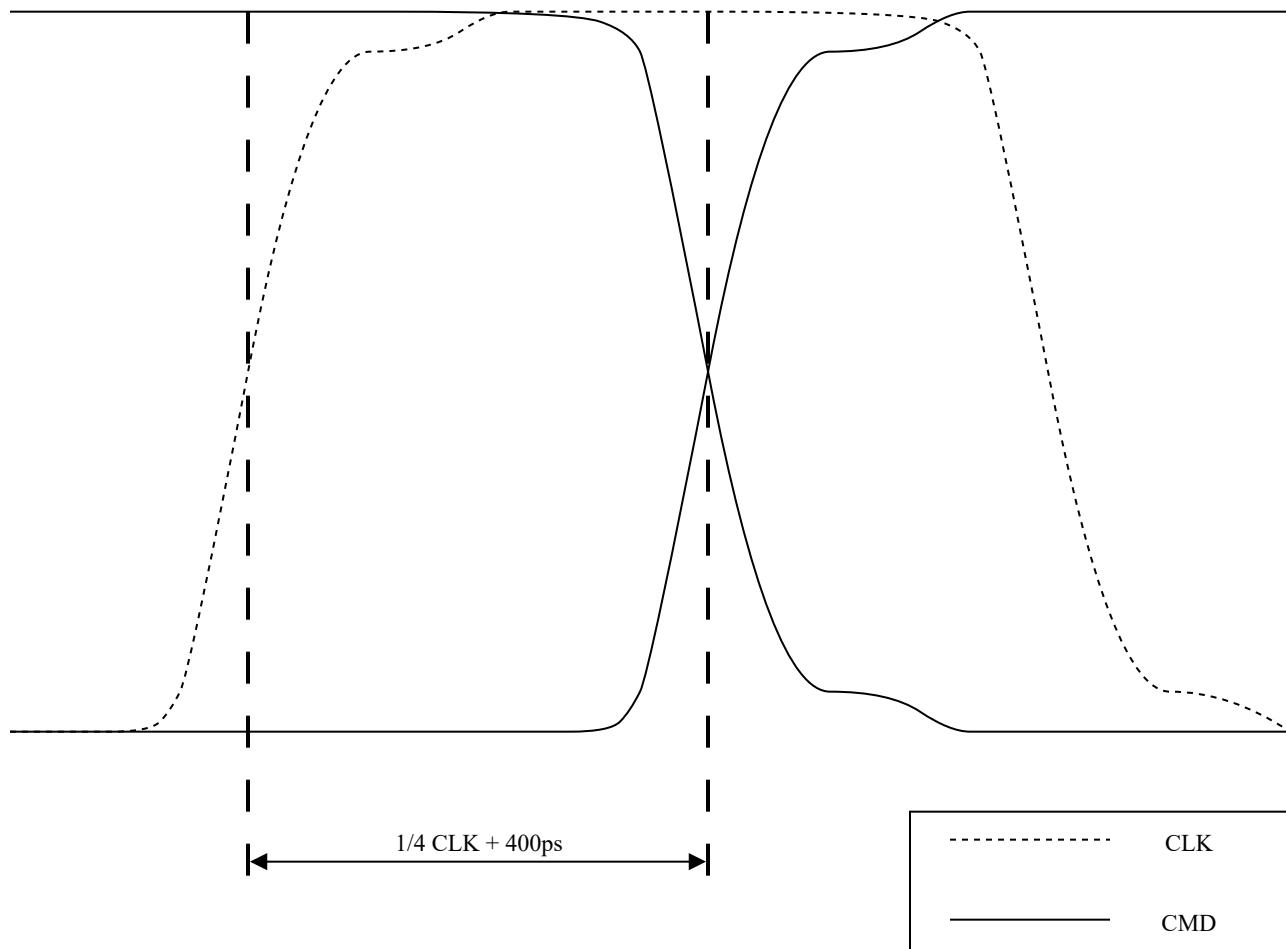

| 図 3-4. セットアップ / ホールド時間: CLK に対する CMD のオフセット (1/4 CLK サイクル + 400ps の遅延).....                                  | 28 |

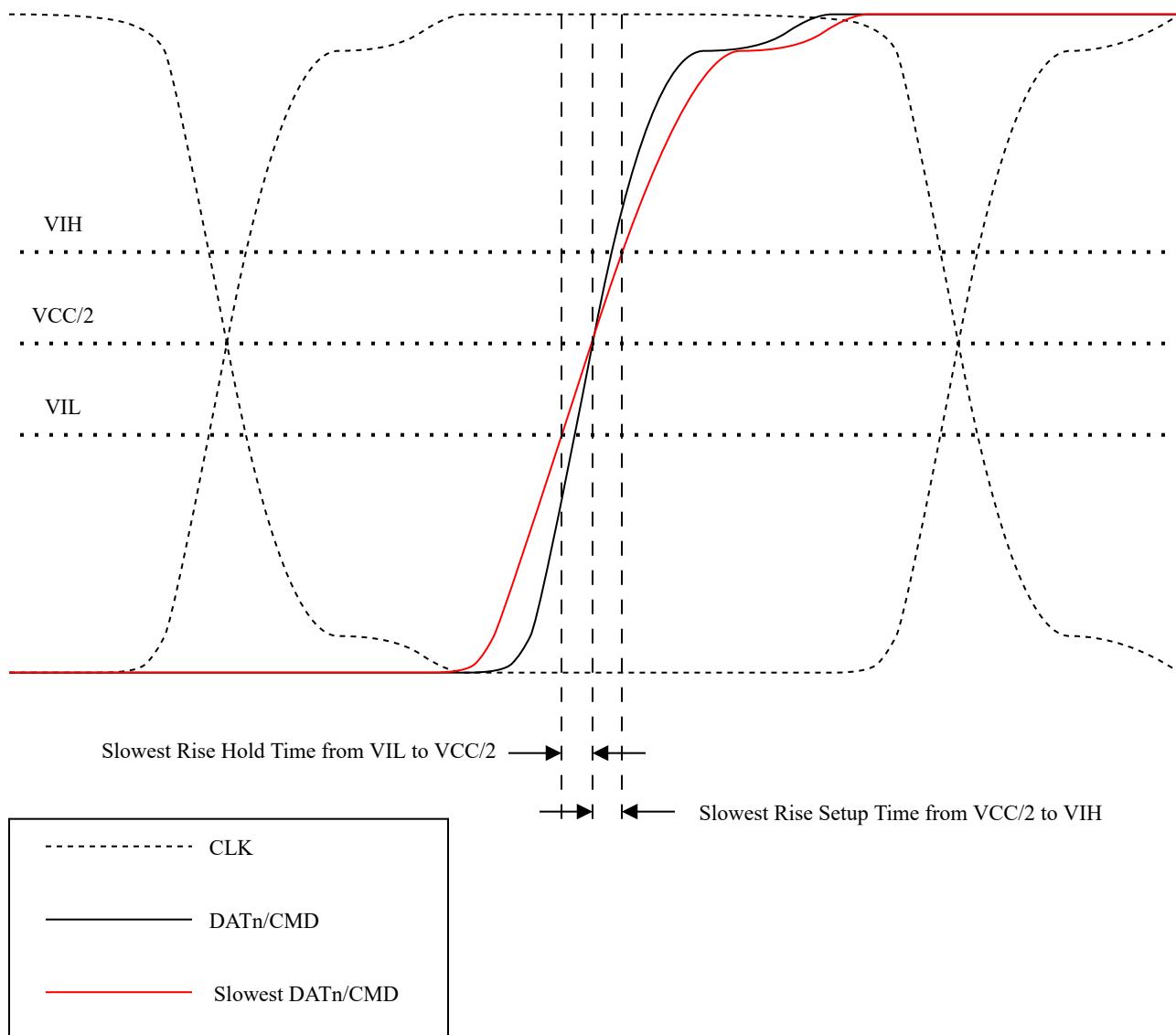

| 図 3-5. セットアップ / ホールド時間: 最も遅い DATn/CMD の立ち上がりエッジにおけるスルーは、セットアップ時は VCC/2 から VIH まで、ホールド時は VIL から VCC/2 まで..... | 29 |

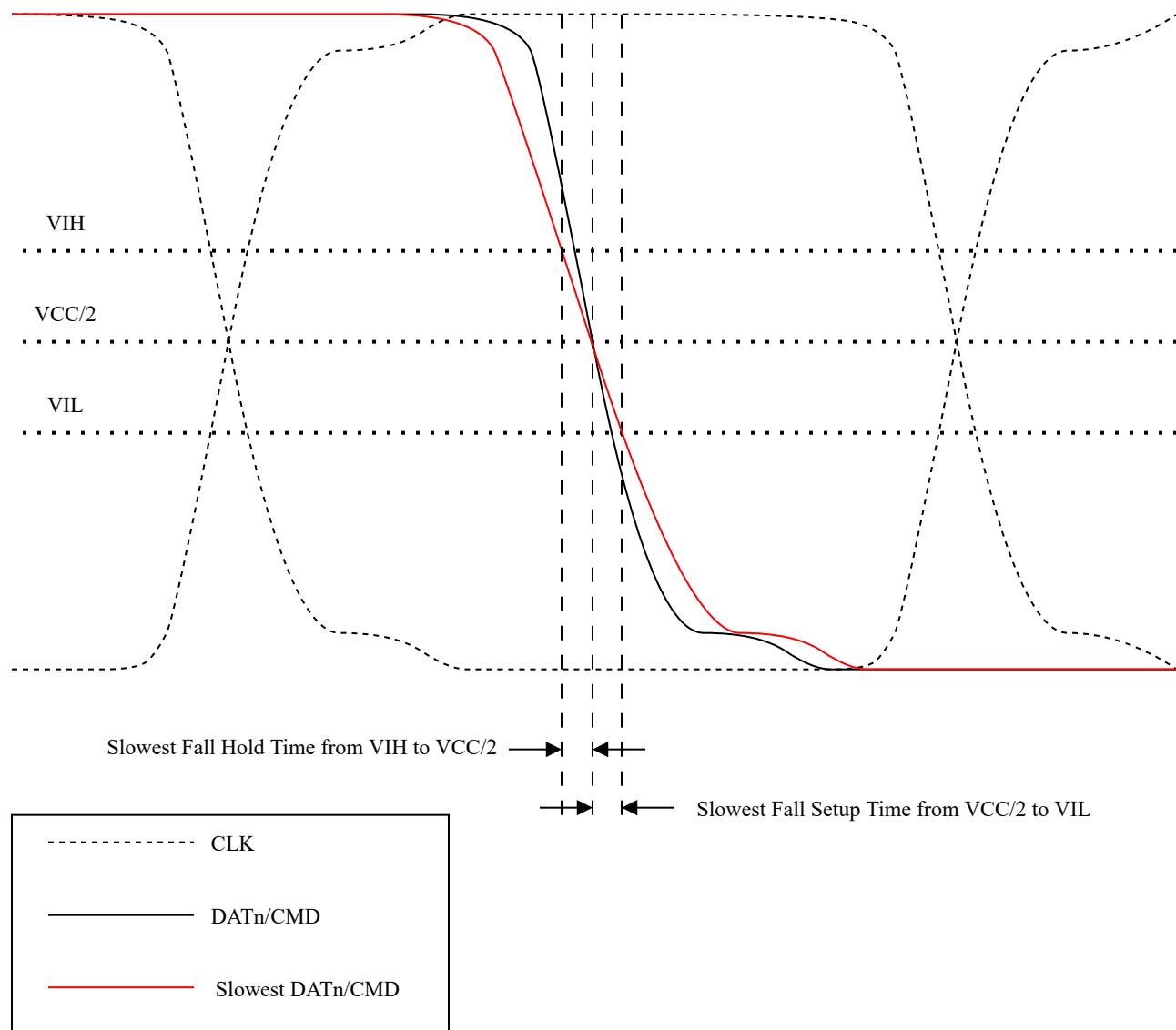

| 図 3-6. セットアップ / ホールド時間: 最も遅い DATn/CMD の立ち下がりエッジにおけるスルーは、セットアップ時は VCC/2 から VIL まで、ホールド時は VIH から VCC/2 まで..... | 30 |

| 図 3-7. VIH/VIL: 非単調な CLK の良好な例 (VIL -60mV) から (VIH +60mV) の範囲内では単調.....                                      | 31 |

| 図 3-8. VIH/VIL: 非単調な CLK の不適切な例 (VIL -60mV) から (VIH +60mV) の範囲内で非単調.....                                     | 32 |

| 図 3-9. VIH/VIL: リングバックを伴う DATn/CMD の最も遅い立ち上がりエッジのスルー (次のキャプチャ用 CLK エッジの前における最後の (VIH +60mV) 交差点まで測定).....    | 33 |

| 図 3-10. VIH/VIL: リングバックを伴う DATn/CMD の最も遅い立ち下がりエッジのスルー (次のキャプチャ用 CLK エッジの前における最後の (VIL -60mV) 交差点まで測定).....   | 34 |

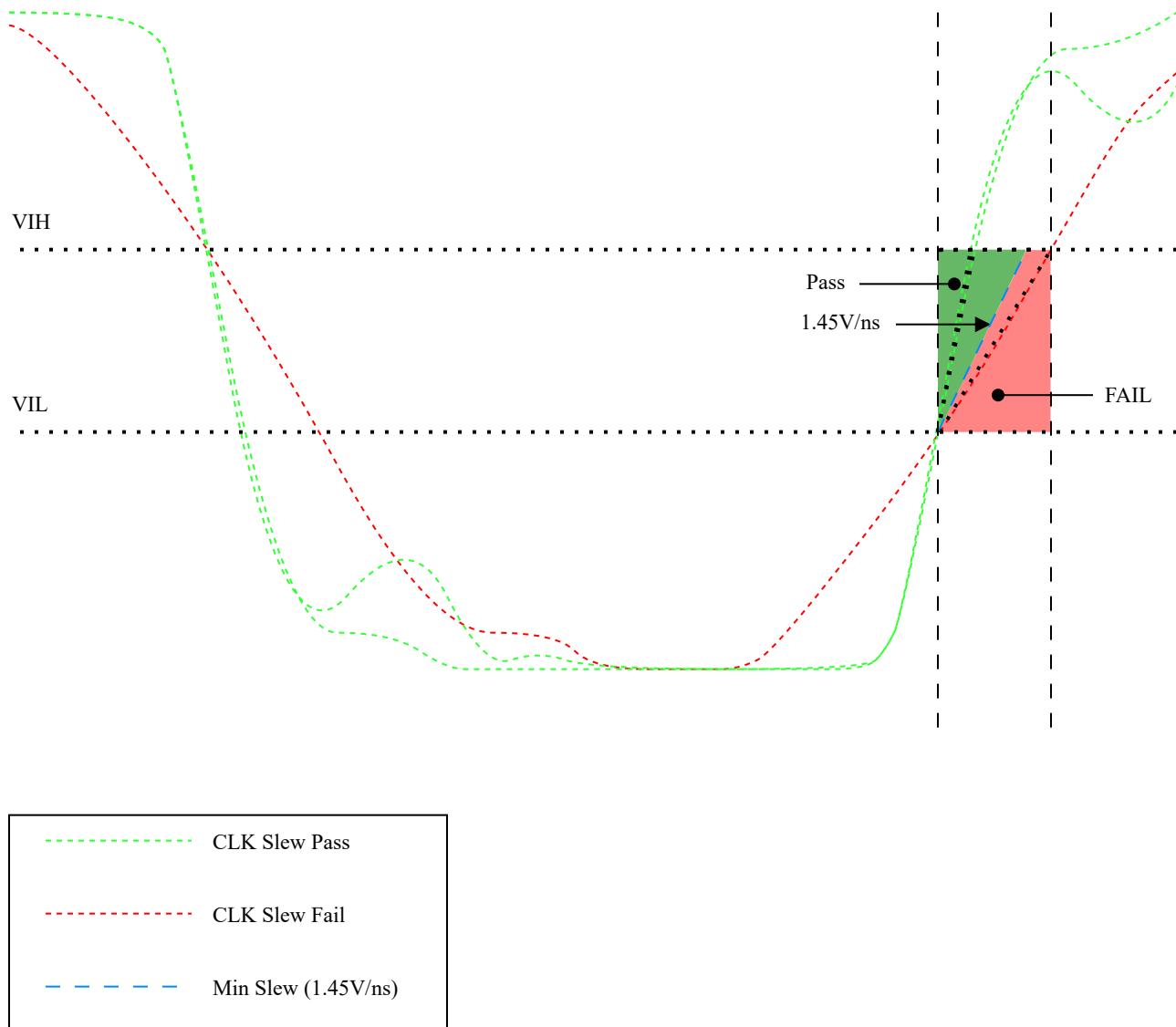

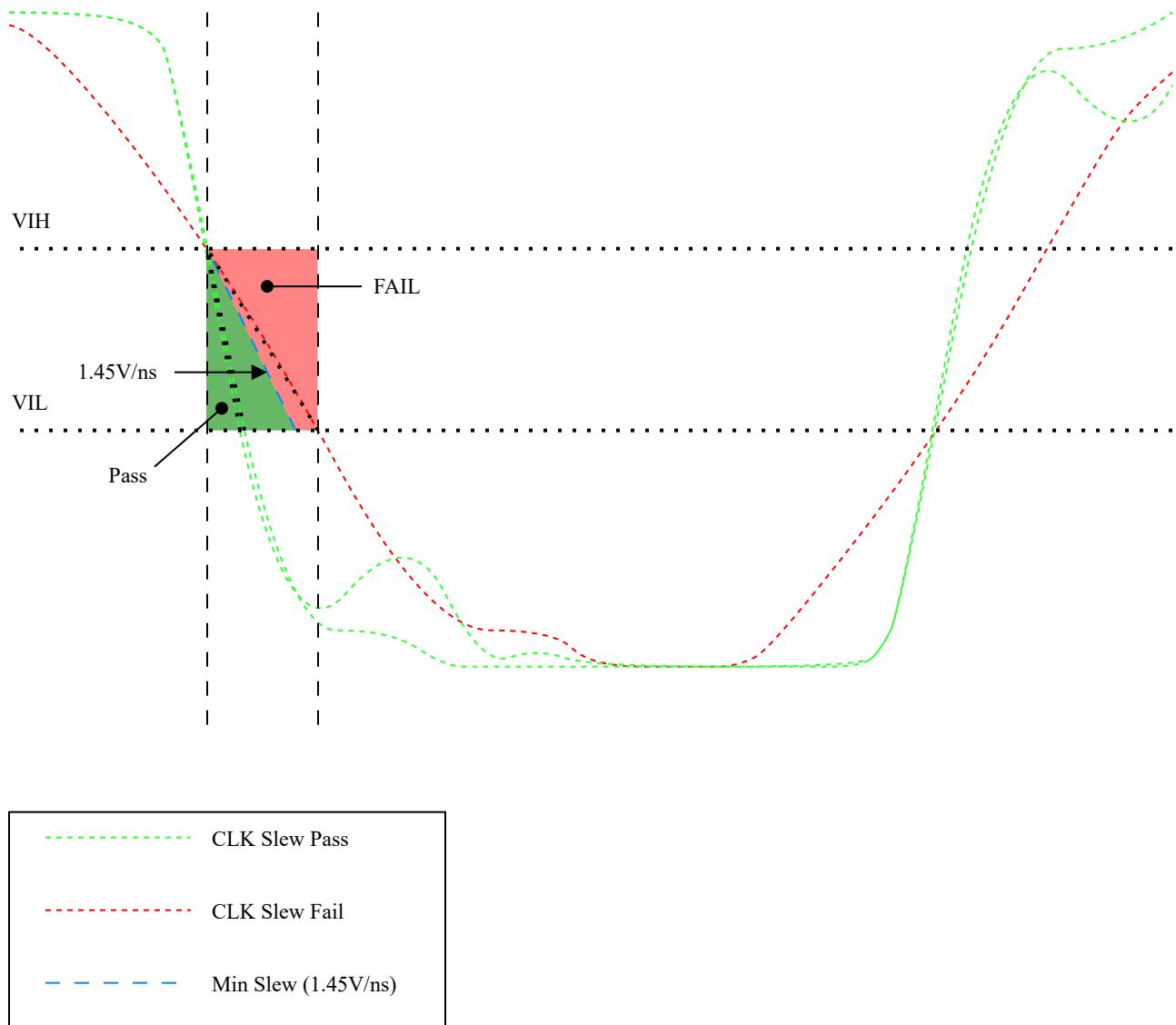

| 図 3-11. スルーレート: CLK の立ち上がりエッジ - VIL から VIH の間におけるスルーレートは 1.45V/ns より速い必要があります.....                           | 35 |

| 図 3-12. スルーレート: CLK の立ち下がりエッジ - VIH から VIL の間におけるスルーレートは、1.45V/ns より速い必要があります.....                           | 36 |

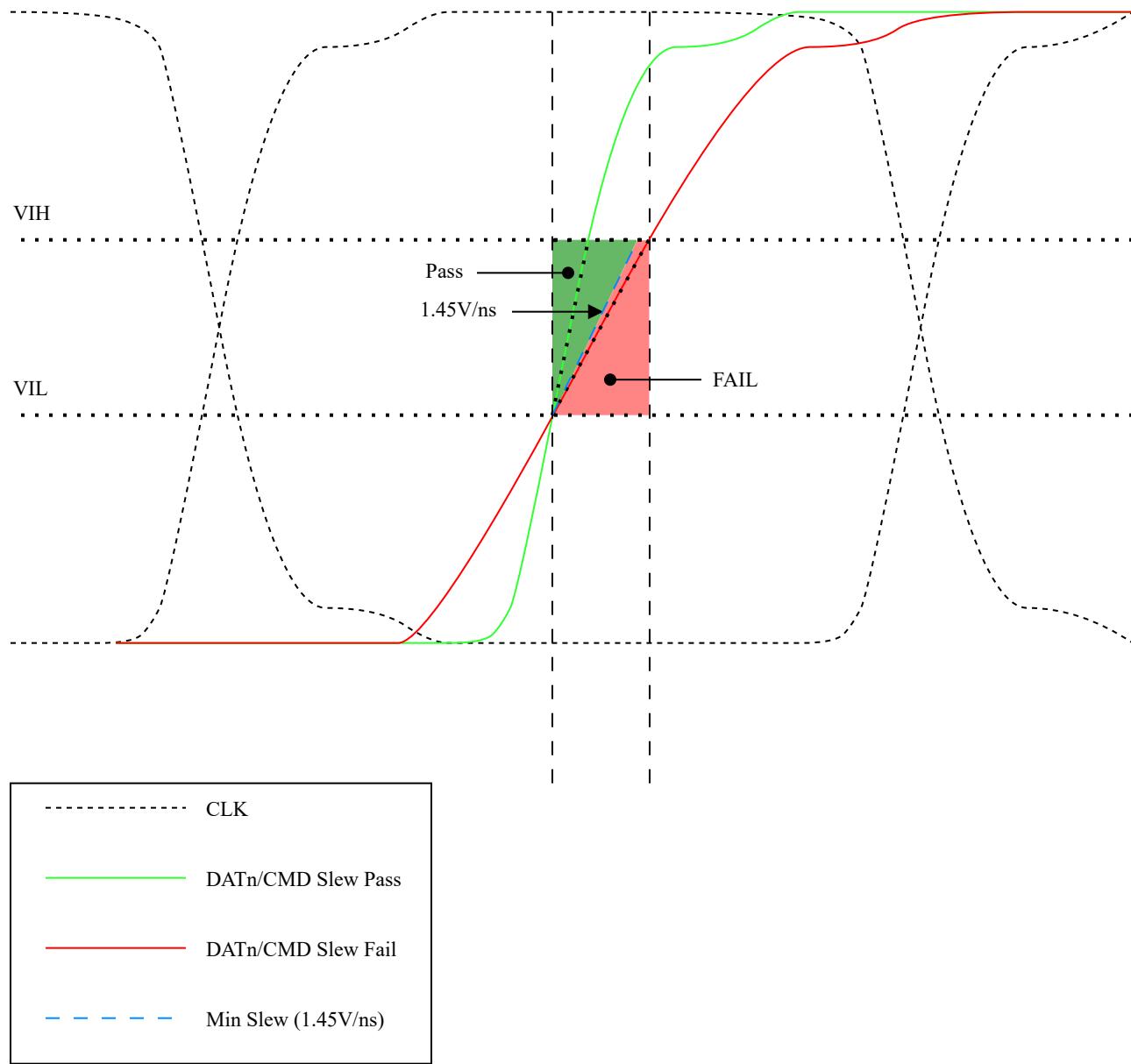

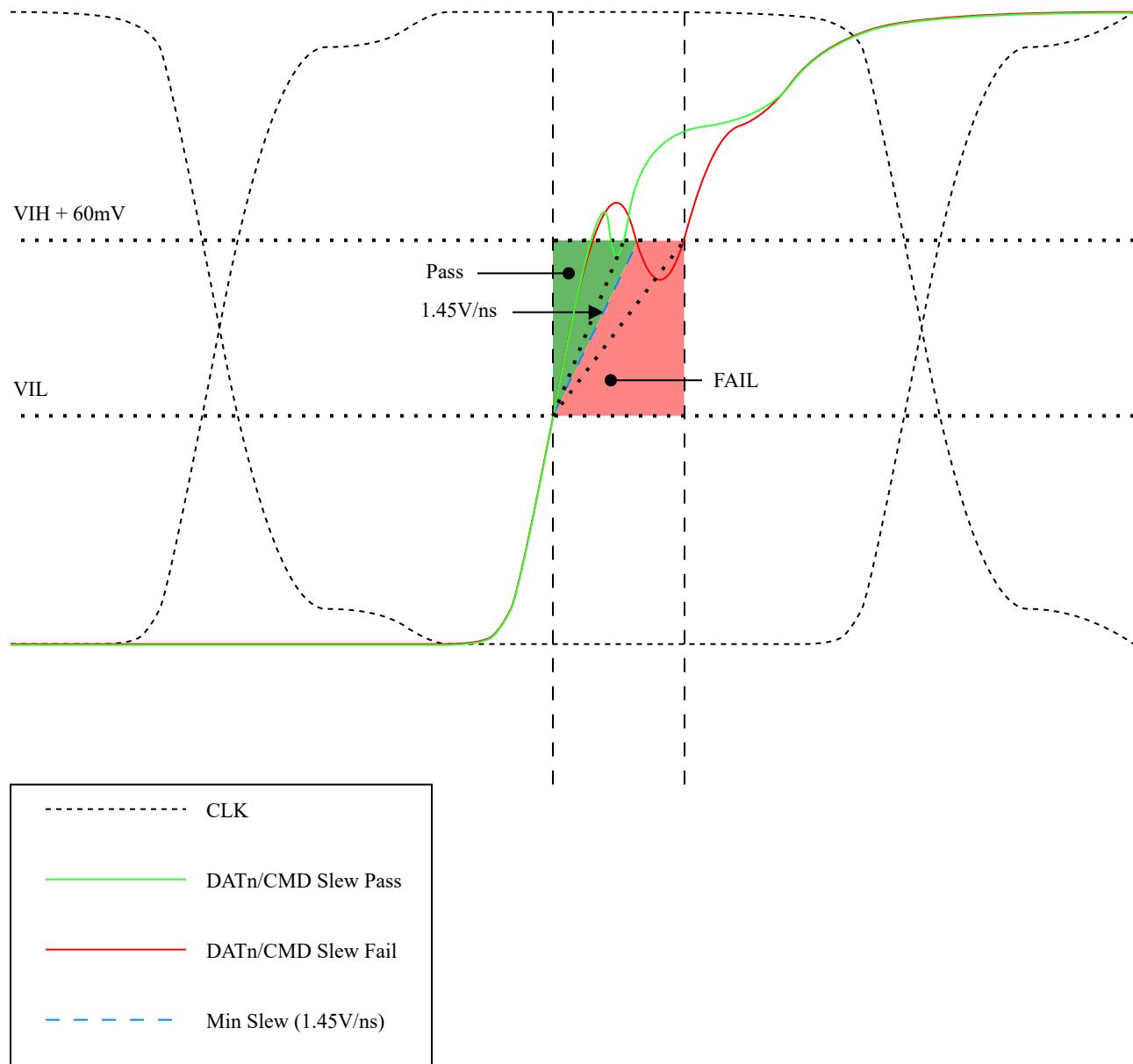

| 図 3-13. スルーレート: DATn/CMD の立ち上がりエッジ - VIL から VIH の間におけるスルーレートは、1.45V/ns より速い必要があります.....                      | 37 |

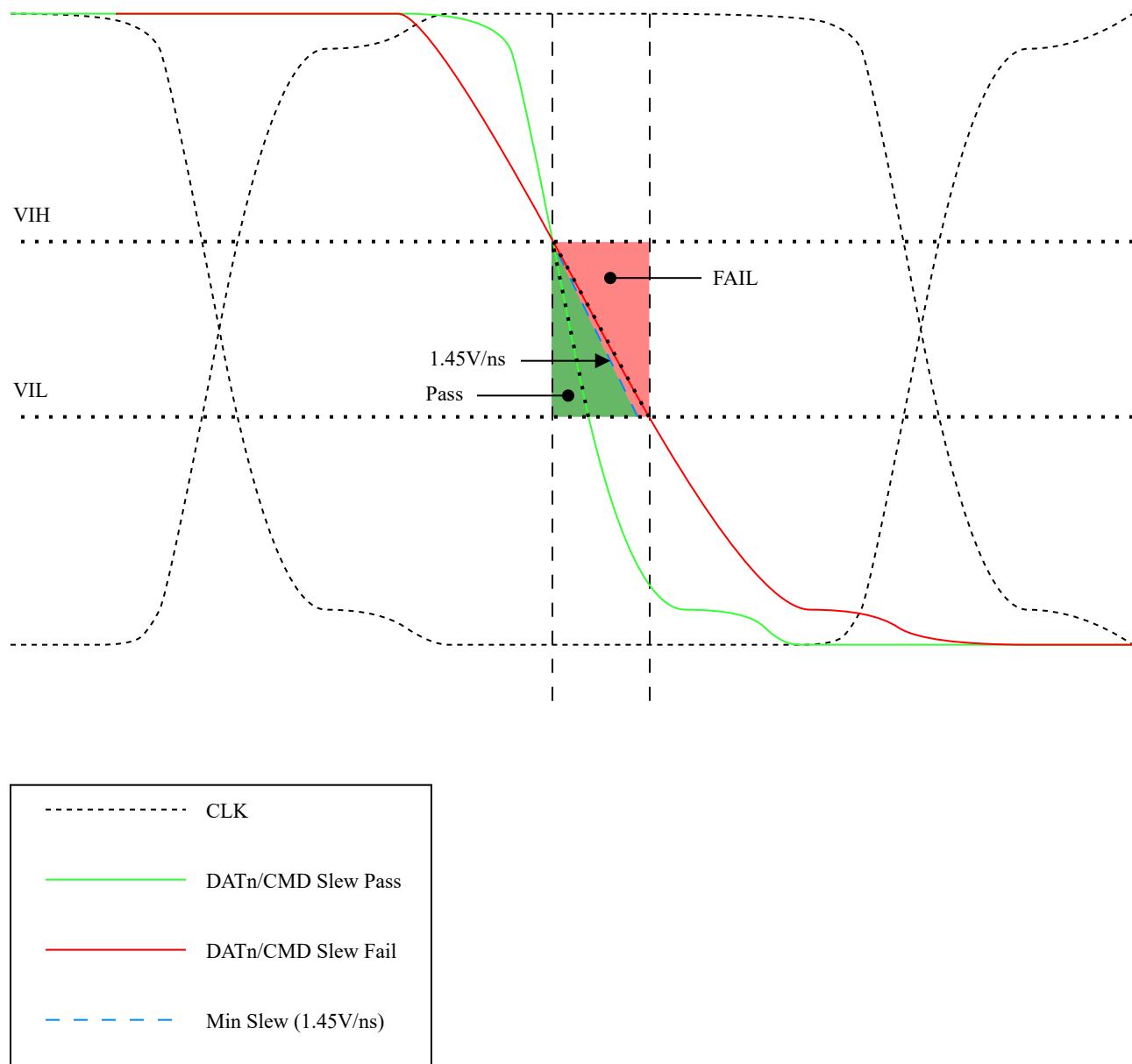

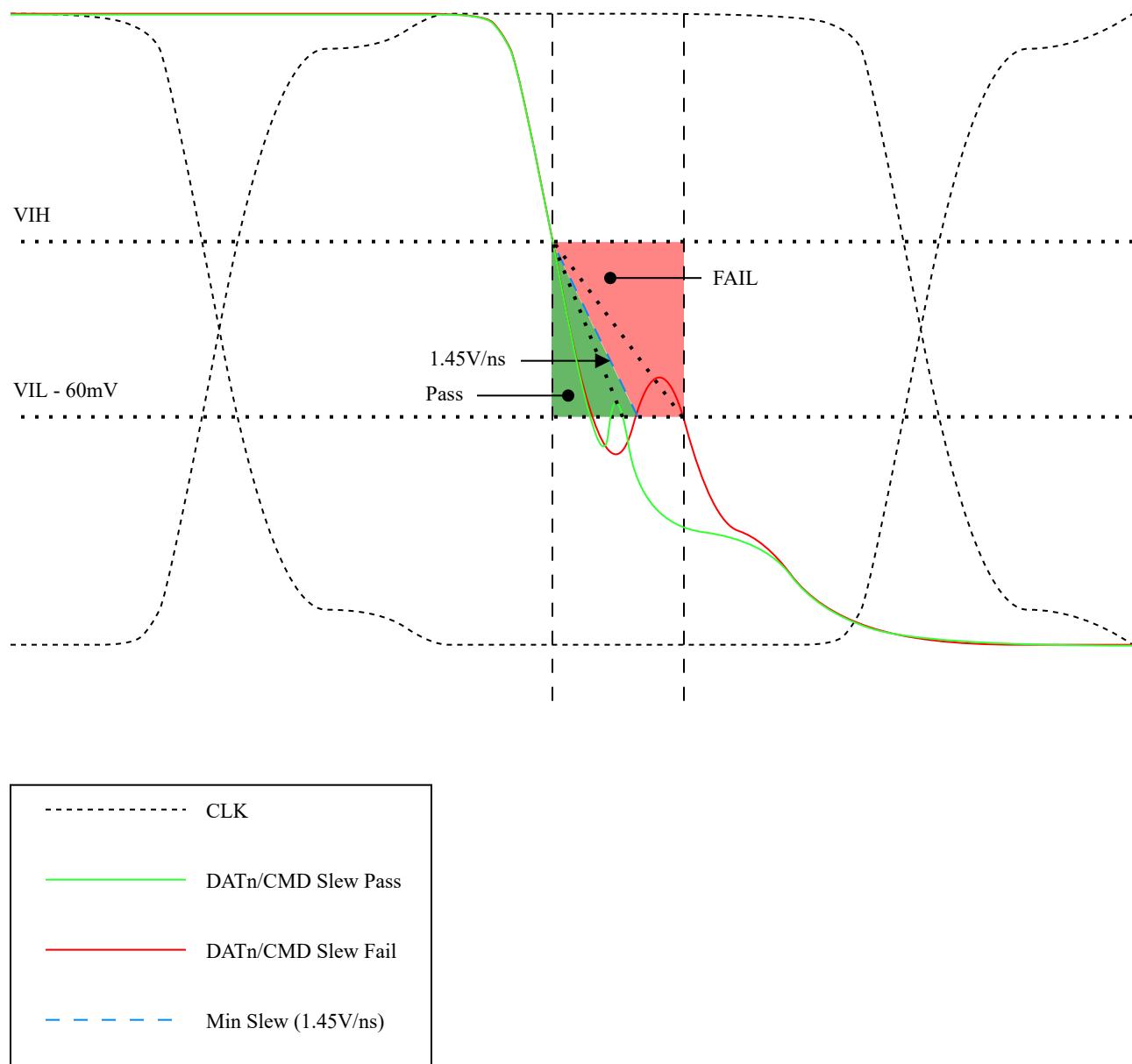

| 図 3-14. スルーレート: DATn/CMD の立ち下がりエッジ - VIH から VIL の間におけるスルーレートは、1.45V/ns より速い必要があります.....                      | 38 |

| 図 3-15. スルーレート: リングバックを伴う DATn/CMD の立ち上がりエッジ - VIL から (VIH +60mV) の間におけるスルーレートは、1.45V/ns より速い必要があります.....    | 39 |

| 図 3-16. スルーレート: リングバックを伴う DATn/CMD の立ち下がりスルー - VIL から (VIL -60mV) の間におけるスルーレートは、1.45V/ns より高速である必要があります..... | 40 |

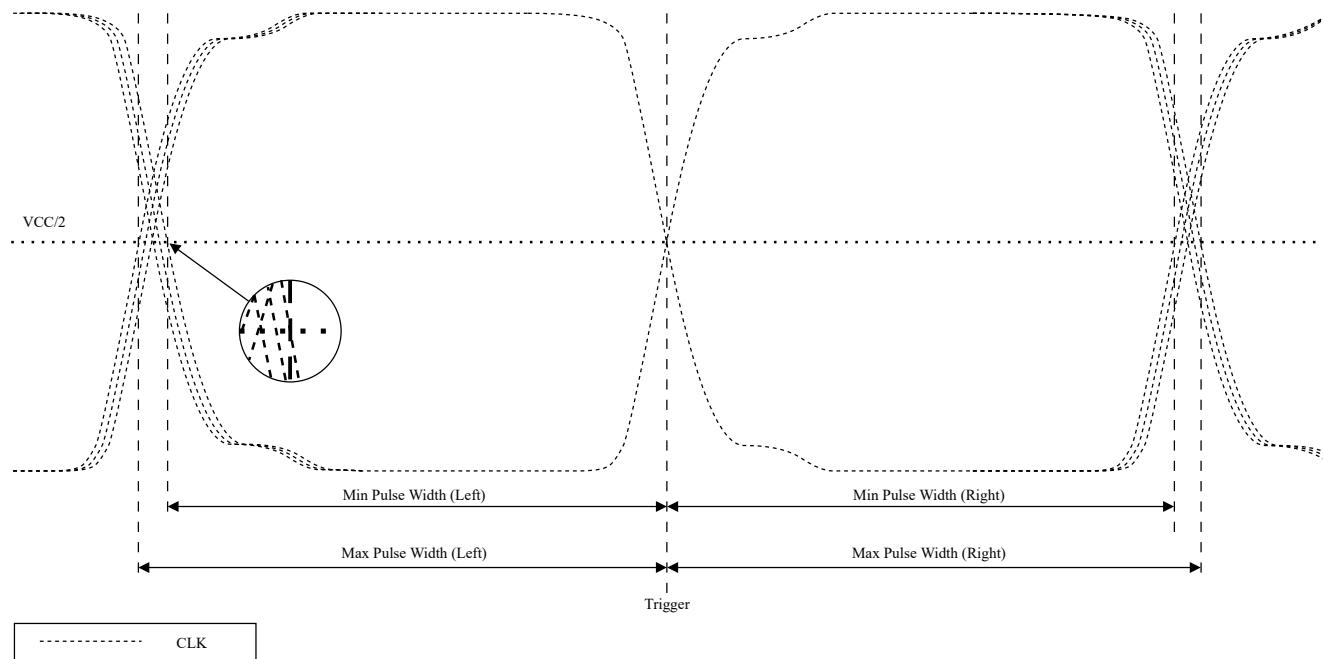

| 図 3-17. DCD およびパルス幅の測定におけるパルス幅の測定方法.....                                                                     | 41 |

| 図 4-1. SK-AM62P-LP (PROC164E2) の eMMC 電源配線 2D レイアウト - VCC1V8_SYS (白) および SoC_DVDD1V8 (紫).....                | 43 |

| 図 4-2. SK-AM62P-LP (PROC164E2) の eMMC 電源配線 3D レイアウト - VCC1V8_SYS (白) および SoC_DVDD1V8 (紫).....                | 44 |

| 図 4-3. SK-AM62P-LP (PROC164E2) の eMMC 信号配線 - CMD と DAT [7:0].....                                            | 45 |

| 図 4-4. SK-AM62P-LP (PROC164E2) eMMC 信号ルーティング - CLK と DS.....                                                 | 46 |

## 表の一覧

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 表 1-1. PCB スタックアップ仕様.....                                          | 4  |

| 表 1-2. バルク バイパスコンデンサ.....                                          | 5  |

| 表 1-3. 高速バイパスコンデンサ.....                                            | 5  |

| 表 3-1. VDDS_MMC0 および他の共有 1.8V 電源レール上のコンデンサのループ インダクタンス.....        | 12 |

| 表 3-2. SK-AM62P-LP (PROC164E2) のセットアップ / ホールド (FF) 全体マージン計算の例..... | 16 |

| 表 3-3. SK-AM62P-LP (PROC164E2) の DCD 全体マージン計算の例.....               | 18 |

| 表 3-4. SK-AM62P-LP (PROC164E2) におけるパルス幅の全体マージンの計算例.....            | 19 |

| 表 3-5. 合格 / 不合格チェック.....                                           | 21 |

| 表 4-1. 12 層 PCB スタックアップの例.....                                     | 42 |

| 表 4-2. eMMC トレースのインピーダンスの概要例.....                                  | 46 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 概要

AM62Px プロセッサは、eMMC HS400 をサポートしています。このドキュメントには、eMMC メモリを搭載したボード設計に適用可能な内容が含まれています。対応データレートについては、デバイス固有のデータマニュアルを参照してください。

### 1.1 サポート対象のボード設計

AM62Px ファミリのデバイスでサポートされる eMMC インターフェイスの高周波ターゲットを達成するには、優れた PCB 実装が必要です。TI は、規定されているインターフェイス周波数およびデータレートを完全に達成するため、顧客設計において **SK-AM62P-LP (PROC164E2)** レイアウトを、あらゆる細部 (PCB 材料、配線、間隔、ビアなど) に至るまで正確にコピーすることを強く推奨しています。設計上の理由で TI の設計をコピーしない、またはコピーできない場合でも、EVM は引き続き出発点として使用し、シミュレーションを実施する必要があります。顧客設計では、PCB の実装内容に基づいて、インターフェイス周波数およびデータレートを制限する必要があります。

このドキュメントの目的は、堅牢な eMMC HS400 設計を確実に実装できるようにするための、レイアウト、配線、およびシミュレーションに関する一連のルールを定義することです。設計目標を達成できることを検証するには、PCB 設計をシミュレーションする必要があります。TI は、このドキュメントで定義された手順に従って設計およびシミュレーションされていないボードについては、デバッグおよびサポートを制限します。TI の EVM 実装に従っていない、または有効なシミュレーション結果を有していないシステムは、周波数を下げて動作させる必要が生じる可能性があります。

このドキュメントでは、シミュレーション結果の妥当性を検証するための指針として、IBIS モデルによるシミュレーション手法を提供します。なお、PCB 設計作業 (設計、レイアウト、製造) は、高速 PCB 設計に精通した設計者によって実施され、レビューされることが前提とされています。信号がリファレンスプレーンの分割部を横断する際に生じるインピーダンスの非連続性などの問題は、十分な経験を有する者であれば視覚的に検出できます。

TI は、本ドキュメントのガイドラインに従ったボード設計のみをサポートします。これらのガイドラインは、連続したリファレンスプレーン上に配線された銅配線の、よく知られた伝送線路特性に基づいています。PCB スペースが不足していると主張しても、配線ガイドラインを無視する理由にはなりません。TI は、このドキュメントで定義された手順に従ってシミュレーションが行われていない設計については、デバッグおよびサポートを制限します。

### 1.2 一般的なボードレイアウトガイドライン

良好な信号性能を確認するために、以下の一般的なボード設計ガイドラインに従う必要があります：

- TI のリファレンスレイアウトや EVM 設計に、できるだけ忠実に従う必要があります。コンセプトや配線の方針が理解できない場合は、E2E で質問してください。

- すべての信号にグランドリファレンス (両側に強く推奨) が必要です。

- 信号基準プレーン内でプレーンの分割が交差しないようにします。

- デカップリングコンデンサと電源ピンの間は、実用上可能な限り最も太い配線幅を使用します。

- インピーダンスを整合させて、シンボル間干渉 (ISI) を最小限に抑えます。

- ストローブやクロックなどの高感度信号を分離し、適切な PCB スタックアップを使用することで、クロストークを最小化します。

- 信号が層や基準プレーンを切り替わる際には、ビアやコンデンサを追加してリターンパスの非連続性を避けます。

- 適切な絶縁とデカップリングコンデンサの適切な使用により、リファレンス電圧ノイズを最小限に抑えます。

- 信号配線のスタブ長は可能な限り短くします。

- クロックおよびストローブ配線には追加の間隔を設け、クロストークを最小化します。

- 全ての信号線やバイパス/デカップリングコンデンサは、共通のグランド (GND) 基準を持つようにします。

- タイミング制約を評価するときは、マイクロストリップとストリップラインネットの伝搬遅延の違いを考慮します。

- ビアからビアへの結合は、PCB レベルのクロストークの重要な部分になる可能性があります。ビアの寸法とピッチが重要です。高速インターフェイスの場合、GND シールドビアを検討します。このビア結合は、データ信号をプロセッサに最も近い層に配線することを推奨する要因の一つです。

- ビアスタブは信号の完全性に影響を与えます。ビアのバックドリルは信号の完全性を改善でき、場合によっては必須となります。

詳細については、[高速インターフェイスのレイアウトガイドライン](#) アプリケーションノートを参照してください。これは、高速信号を適切に配線するための追加の一般的な指針を示しています。

## 1.3 PCB 積層

AM62Px システム オンチップ (SoC) を用いたルーティング設計では、10 層または 12 層のスタックアップが推奨されています。ただし、これは大きなキープアウト領域を確保でき、十分な配線スペースを持つ基板でのみ実現可能です。次の場合は、追加のレイヤが必要です：

- PCB のレイアウト面積が制限されているため、クロストークを最小化するために信号を十分に分散させるための領域が限られています。

- 他の回路は同一エリアに存在する必要がありますが、eMMC のルーティングとは分離された層に配置されます。

- 電源の配線を強化し、または EMI シールドを改善するために、追加のプレーン層が必要です。

基板設計の密度が比較的高い場合、すべての設計ルールを満たした形で eMMC の配線を行うために、より多くの層が必要になることがあります。

すべての eMMC 信号は、連続した GND リファレンス プレーンに隣接して配線する必要があります。eMMC の配線領域に複数の GND リファレンス プレーンが存在する場合、信号が別の GND リファレンス プレーンへ移行するビアの近くには、必ずスティッチング ビアを配置する必要があります。これは、低インダクタンスのリターン電流パスを維持するために必要です。

TI は、すべての eMMC 信号をストリップ ラインとして配線することを推奨しています。一部の PCB スタックアップでは、隣接する 2 つの層で信号配線を行う構成が採用されています。これは推奨されません。隣接する層で他の配線と平行に配線されたトレースでは、たとえごく短い距離であってもクロストークが発生するためです。TI は、eMMC 信号をスタックアップ内で SoC により近い PCB 層に配線することを推奨しています。これにより、ビアを通過する際の信号の伝搬距離を短くできます。SoC から離れた PCB 層では、ビア内での信号伝搬距離が長くなり、その結果、ビア間の結合が増加する可能性があります。信号間結合およびビア間結合のいずれも、タイミング マージンの縮小につながる可能性があります。

なお、(標準的なドリル ビアを使用している場合) ビア内の伝搬距離が短いほど、ビア スタブが長くなる可能性があるため、その点も考慮する必要があります。シミュレーションを使って、ビア スタブの長さが問題であるかどうかを判断できます。

**表 1-1. PCB スタックアップ仕様**

| 個数 | パラメータ <sup>(5)</sup>                                   | 最小値   | 標準値       | 最大値     | 単位 |

|----|--------------------------------------------------------|-------|-----------|---------|----|

| 1  | PCB 配線層およびプレーン層                                        |       | 10 または 12 |         |    |

| 2  | 信号配線層                                                  |       | 6         |         |    |

| 3  | eMMC 配線領域下の全面 GND リファレンス 層 <sup>(1)</sup>              | 1     |           |         |    |

| 4  | eMMC ルーティング領域内で許可されているリファレンス プレーン カットの数 <sup>(2)</sup> |       |           | 0       |    |

| 5  | eMMC 配線層とリファレンスプレーン間のレイヤ数 <sup>(3)</sup>               |       |           | 0       |    |

| 6  | PCB の配線形状のサイズ                                          |       | 0.10      |         | mm |

| 7  | PCB のパターン幅、w                                           | 0.08  |           |         | mm |

| 8  | ポイントツー ポイント、シングル エンド インピーダンス                           |       | 50        |         | Ω  |

| 9  | インピーダンス制御 <sup>(4)</sup>                               | Z-10% | Z         | Z + 10% | Ω  |

(1) グランド リファレンス層は、電力リファレンス層よりも推奨されます。リターン信号のビアは層遷移の近くに配置する必要があります。

(2) eMMC 配線領域内のリファレンス プレーンを交差させるパターンはありません。高速信号トレースがリファレンス プレーンのカットを横断すると、リターン電流バスが大きくなり、その結果、過度なクロストークや EMI 放射を引き起こす可能性があります。ビアのアンチパッドによって生じるリファレンス プレーンのボイドにも注意してください。これらもリターン電流バスに非連続性を生じさせます。

(3) リターン電流ループのサイズを最小限に抑えるため、リファレンス プレーンは信号層に直接隣接して配置する必要があります。

(4) Z は、PCB 用に選択された公称シングル エンド インピーダンスです。

(5) これらの仕様は、設計を行う際の出発点として使用されます。TI は、すべての要件が満たされていることを確認するため、各設計について抽出およびシミュレーションを行うことを推奨しています。

## 1.4 バイパス コンデンサ

### 1.4.1 バルク バイパス コンデンサ

バルク バイパス コンデンサは、eMMC および他の回路の中程度の速度域でのバイパス (デカップリング) に必要です。

表 1-2 に、バルク バイパス コンデンサに必要な最小数と容量を示します。表 1-2 は、SoC の eMMC PHY のバイパス要

件のみをカバーします。他の回路には、追加のバルク バイパス容量が必要です。eMMC デバイスに関する追加のデカップリング要件については、メーカーのデータシートを参照してください。

**表 1-2. バルク バイパス コンデンサ**

| 個数 | パラメータ                                    | 最小値               | 最大値 | 単位   |

|----|------------------------------------------|-------------------|-----|------|

| 1  | VDDS_MMC0 バルク バイパス コンデンサ数 <sup>(1)</sup> | 1 <sup>(2)</sup>  |     | デバイス |

| 2  | VDDS_MMC0 バルク バイパス合計容量                   | 10 <sup>(2)</sup> |     | μF   |

- (1) これらの部品は、バイパス対象のデバイスの近くに配置する必要がありますが、高速 (HS) バイパス コンデンサの配置を優先する必要があります。

(2) このガイドのコンデンサ推奨事項は、このプロセッサの要件のみに基づくものです。メモリ デバイスに適したデカップリング コンデンサの構成を決定するには、eMMC デバイス ベンダのガイドラインを参照してください。

#### 1.4.2 高速バイパス コンデンサ

高速 (HS) バイパス コンデンサは、eMMC HS400 インターフェイスを正しく動作させるために不可欠です。高速 (HS) バイパス コンデンサから VDDS\_MMC0 電源ピンおよびそれに対応するグラウンド接続までの寄生直列インダクタンスを最小限に抑えることが重要です。表 1-3 に、HS バイパス コンデンサの仕様と PCB 上の電源接続の仕様が含まれています。一般的に、TI は次の点を推奨しています：

- できるだけ多くの HS バイパス コンデンサを配置します。

- バイパス コンデンサから、バイパス対象となるピンおよびボールまでの距離を最小限に抑えます。

- 入手可能な中で最も高い容量を持つ、できるだけ物理サイズの小さいセラミックコンデンサを使用します。

- バイパス コンデンサのパッドは、可能な限り最も太い配線を用いてビアに接続し、ビア ホール径も可能な限り最大のものを使用します。

- ビアの共有を最小限に抑えます。表 1-3 に示すビア共有の制限に注意します。

- 2 端子コンデンサの代わりに、3 端子コンデンサを使用します。3 端子コンデンサはループ インダクタンスを低減でき、1 個の 3 端子コンデンサで複数の 2 端子コンデンサを置き換えることができるため、ループ インダクタンスをさらに最適化できます。

eMMC デバイスに関する追加要件については、メーカーのデータシートを参照してください。

**表 1-3. 高速バイパス コンデンサ**

| 個数 | パラメータ                                                  | 最小値 | 標準値  | 最大値  | 単位   |

|----|--------------------------------------------------------|-----|------|------|------|

| 1  | VDDS_MMC0 レールあたりのプロセッサ用 HS バイパス コンデンサの数 <sup>(2)</sup> | 3   |      |      | デバイス |

| 2  | VDDS_MMC0 レールあたりのプロセッサ用 HS バイパス コンデンサの合計容量             | 0.3 |      |      | μF   |

| 3  | VDDS_MMC0 電源ボールの接続ビアの数                                 | 3   |      |      | ビア   |

| 4  | プロセッサの電源 / グランド ボールから接続ビア <sup>(1)</sup> までのパターン長      |     | 0.25 | 0.51 | mm   |

(1) より近く、より短いほど望ましいです。

(2) 低 ESL コンデンサや多端子コンデンサを使用することで、必要なバイパス コンデンサの数を削減できます。

## 1.5 速度補正

PCB 設計では、eMMC 信号トレースの一部はマイクロストリップ (BGA ブレークアウト部) ですが、パターン セグメントの大部分はストリップライン (内部層) です。マイクロストリップとストリップラインとして配線されるパターン長の割合には大きなばらつきがあるものの、長さ / 遅延マッチングの手順には、これら 2 種類の PCB インターコネクト間の伝搬速度差 ( $\Delta v$ ) を補償する仕組みを含める必要があります。この目的のために、JEDEC は補償係数 1.1 を規定しています。長さマッチング式に合算する前に、すべてのマイクロストリップ セグメント長を 1.1 で除算する必要があります。結果として生じる補正長はストリップライン等価長と呼ばれます。設計には伝搬速度ミスマッチによる残留スキューがある程度残るもの、この手法は単純な長さマッチングより大幅に改善されます。

## 2 eMMC 基板の設計およびレイアウトのガイドライン

### 2.1 eMMC の紹介

eMMC は、JEDEC 規格 JESD84-B51、組み込み型マルチメディアカード (eMMC) 電気規格 (5.1) によって規定されている管理型メモリデバイス仕様です。この規格は、モバイル機器に求められる低消費電力を維持しつつ、小規模なランダムデータアクセス (コード) を犠牲にすることなく、大容量データ転送における高スループットをサポートすることを目指しています。11 信号バスは、クロック (CLK)、コマンド (CMD)、データストローブ (DS)、およびデータ (DAT [7:0]) で構成されており、3 種類のバス幅が定義されています 1 ビット (デフォルト)、4 ビットと 8 ビット。クロック周波数は 0 ~ 200MHz の範囲で、シングルデータレートおよびデュアルデータレートに対応しており、最大 400MB/s のデータ転送レート (HS400) を実現します。HS400 モードでは、IO 電圧は 1.8V に固定されています。

以下のセクションでは、AM62Px の eMMC PHY への電源供給に焦点を当て、eMMC インターフェースの配線仕様およびレイアウトガイドラインについて詳しく説明します。

#### 注

AM62Px プロセッサがサポートしている eMMC の最大データレートは、[AM62Px Sitara™ プロセッサ データシート](#)で定義されています。「MMC0 のスイッチング特性 – HS400 モード」表で、HS4005 サイクル時間、MMC0\_CLK を参照してください。

### 2.2 eMMC 信号終端

AM62Px の MMC0 eMMC 信号については、PHY が eMMC に必要な内部プルアップ / プルダウンを有効化して制御するため、外付けプル抵抗は不要です。

DAT [7:0] および CMD のプルアップは、リセット中およびリセット解除後に内部で有効化されます。DS にはプルダウンが有効化され、リセット解除後はクロック出力 (CLK) が Low に駆動されます。MMC0 ピンには、PADCONFIG レジスタは関連付けられていません。MMC0 ピンに関連付けられた内部プルは、MMC0 ホストおよび PHY によって動的に制御されます。

外部プルは、eMMC データ、CMD、DS、または CLK 信号の要件ではありません。

『[AM62P、AM62P-Q1 プロセッサ ファミリ回路設計ガイドラインおよび回路レビュー チェックリスト](#)』を参照してください。

### 2.3 信号配線仕様

eMMC 信号は常にポイントツー ポイントです。TI は、配線時の層遷移を最小限に抑えることを推奨しています。層遷移が避けられない場合には、同一のリファレンスプレーンを持つ層へ遷移することが推奨されます。これを満たせない場合には、リターン電流がリファレンスプレーン間を移行できるよう、近くにグランドビアを設ける必要があります。目的は、リターン電流に対して低インダクタンスの経路を確保することです。スキュー マッチングを最適化するために、TI では、すべてのネットを 1 つの層で配線し、すべてのネットでビア数を完全に同一にし、ビア バレル長も同一にすることを推奨しています。[AM62Px Sitara™ プロセッサ データシート](#)の「MMC0 のタイミング条件」表に、パターン遅延とパターンミスマッチ遅延の要件が定義されています。

ネットにスタブは使用できません。すべてのテストおよびプローブ アクセス ポイントは、分岐やスタブがないライン内に配置する必要があります。

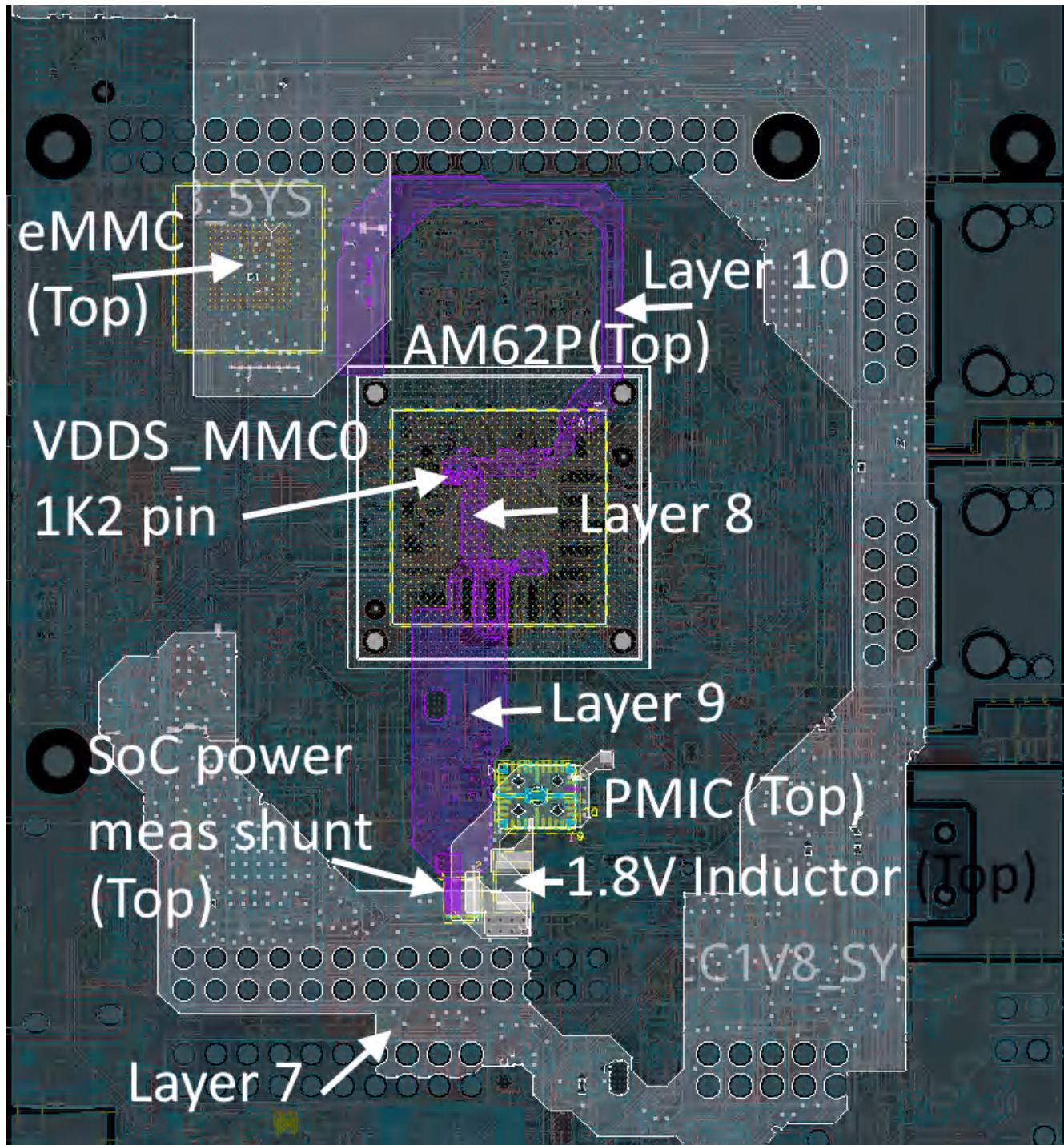

## 2.4 電源の設計

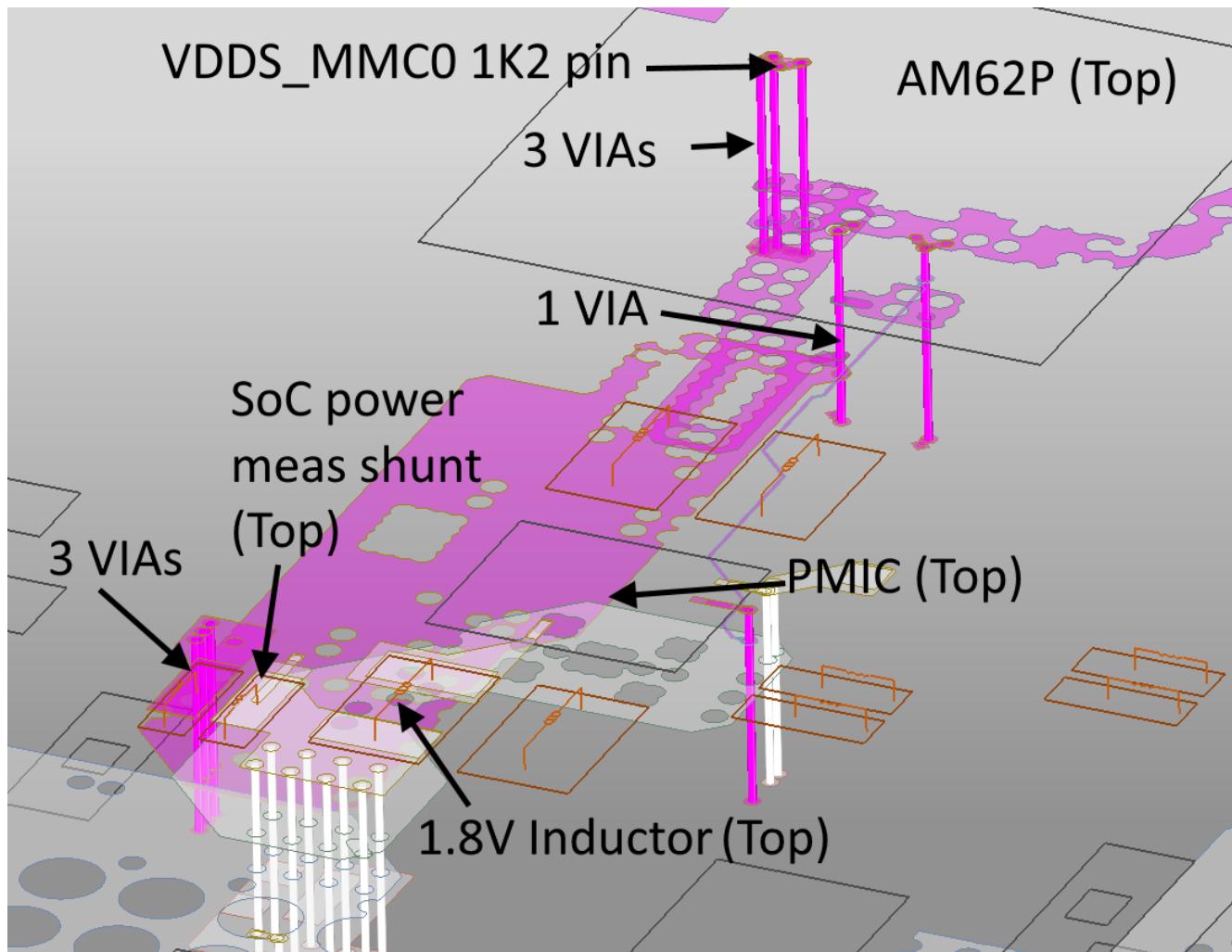

AM62Px の VDDS\_MMCO PHY IO 電源ピンに供給される 1.8V IO 電圧の電源供給ネットワーク (PDN) は、特定の周波数において定められた目標インピーダンス要件を満たす必要があります。SK-AM62P-LP (PROC164E2) におけるこの電源の PDN は、eMMC の JEDEC 仕様である JESD84-B51 への適合性を示すために設計およびシミュレーションされています。これらの要件を満たすため、この基板では、VDDS\_MMCO ピンの近くに配置された複数のデカップリングコンデンサに接続された、複数の電源およびグランドのビア構造が必要となります。これらのビアおよびデカップリングコンデンサの配置は重要で、以下で説明します。表 1-3 の要件も参照してください。

SK-AM62P-LP (PROC164E2) ボードは厚さ 1.73mm で 12 層構成され、スルーホール (PTH) ビアのみ (0.20mm ドリル) です。

3 本の独立した VDDS\_MMCO 用ビアが、それぞれ VDDS\_MMCO の 1K2 ピンから 0.76mm 以内に配置されています (距離はピン中心からビア中心まで測定しています)。基板の AM62Px ピン側には、3 本のビアおよび VDDS\_MMCO ピンを取り囲み、相互に接続する銅形状が配置されています。これら 3 本の電源ビアは、基板の反対側に配置されたデカップリングコンデンサに密接に接続された 6 本の GND ビアによって取り囲まれています。

3 個の 0.1uF の 2 端子デカップリングコンデンサは、ビAINパッドを実装せずに、それぞれの一方のパッドが 3 本の VDDS\_MMCO ビアの近くにできるだけ近づくよう配置されています。各コンデンサのパッド中心から各ビア中心までの最大距離は、0.51mm 未満です。銅形状が、3 本の VDDS\_MMCO ビアおよび VDDS\_MMCO に接続される 3 つのコンデンサパッドを取り囲み、相互に接続しています。各コンデンサの GND パッドは、ビAINパッドを実装せずに、6 本の GND ビアのうち 3 本にできるだけ近づくよう配置されています。短くて幅の広い配線により、各コンデンサはそれぞれの GND ビアに接続されています (配線幅は 0.25mm、配線長は 0.51mm 未満で、中心間距離で測定しています)。いずれのデカップリングコンデンサも、同一の電源ビアまたは GND ビアを共有していません。GND ビアは、内層の複数のソリッド GND リファレンスプレーンに接続します。以下の SK-AM62P-LP (PROC164E2) のリファレンスデザインでは、コンデンサを 45 度の角度で配置していますが、90 度刻みの配置に制限した場合でも、同等の性能が得られることが確認されています。

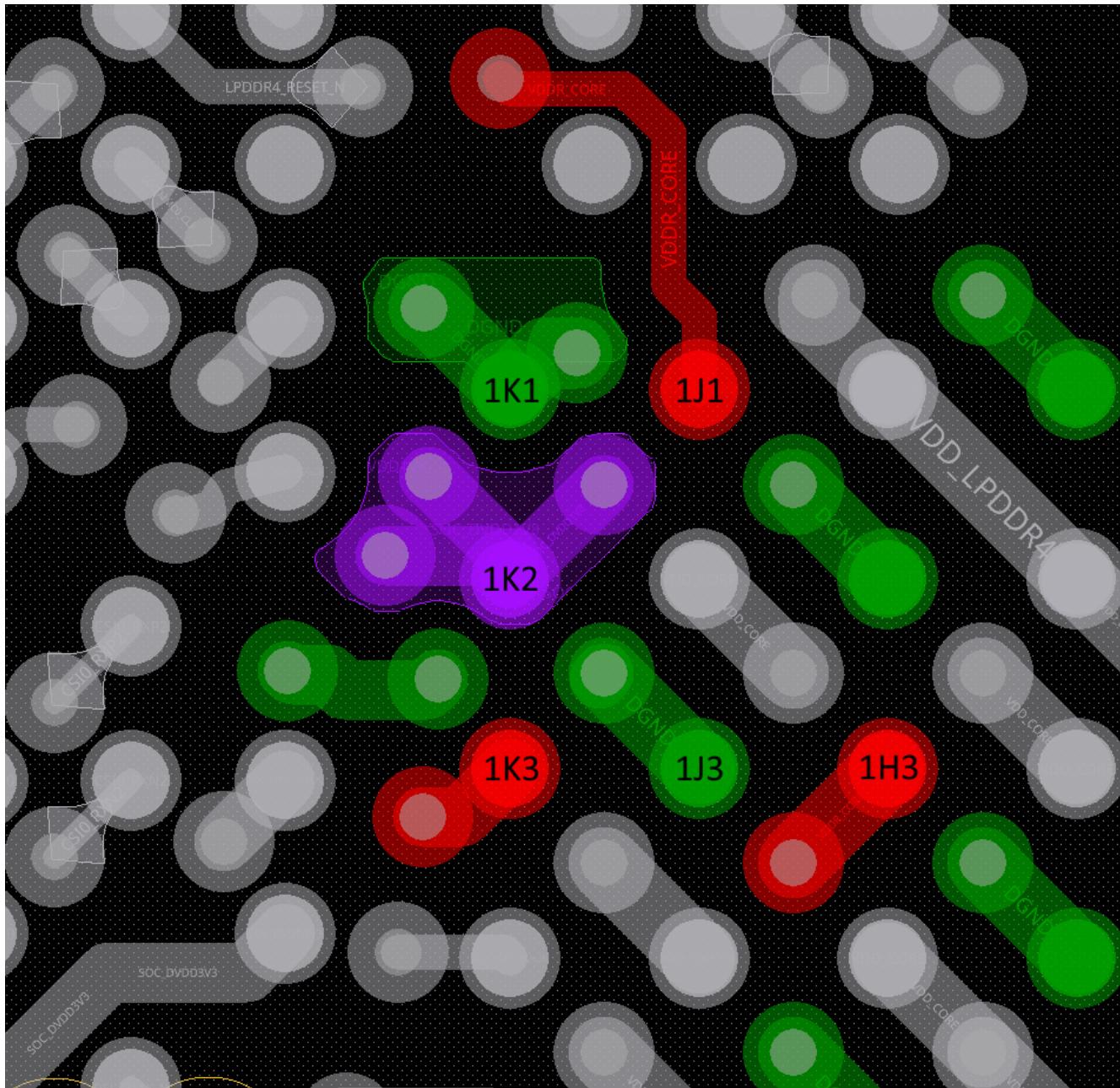

図 2-1. SK-AM62P-LP (PROC164E2) 最上層 - VDD\_MMCO (紫)、GND (緑)、VDDR\_CORE (赤)

図 2-2. SK-AM62P-LP (PROC164E2) 最下層 - VDDS\_MMCO (紫)、GND (緑)、および VDDR\_CORE (赤)

共通の 1.8V IO 電源は、AM62Px VDDS\_MMCO PHY IO 電源ピンと、接続されている eMMC デバイス IO 電源の両方に接続する必要があります。1.8V IO 電源は、VDDSHV1、VDDSHV6、VMON\_1P8\_SOC など、AM62Px の他の電源ピンにも接続できます。

AM62Px VDDS\_MMCO の銅箔は、インダクタンスを最小化するため、BGA ピンにできるだけ近い PCB 層に配置する必要があります。VDDS\_MMCO と短絡している個別の 1.8V 電源レールに対する銅箔は、BGA ピンにできるだけ近い位置に配置する必要があります。ただし、VDDS\_MMCO と、VDDS\_MMCO に短絡されている各 1.8V 電源レールを接続するスター接続部については、BGA ピンからできるだけ離れた位置 (SoC の BGA から遠い PCB 層) に配置する必要があります。この手法の目的は、VDDS\_MMCO と、VDDS\_MMCO に短絡されている他の 1.8V 電源レールとの間で発生する電源干渉を最小化することです。このドキュメントのセクション 3 では、VDDS\_MMCO の IO 電源用デカップリングコンデンサおよび、VDDS\_MMCO に短絡されている他の 1.8V 電源レール用デカップリングコンデンサのループインダクタンスは、設計目標として提示されています。

AM62Px VDDS\_MMCO PHY IO 電源ピンと隣接する電源ピンの間を分離し、各ビアの近くにデカップリング コンデンサを配置することで絶縁する必要があります。

たとえば、[SK-AM62P-LP \(PROC164E2\)](#) 設計では、任意の VDDS\_MMCO ビアと最も近い VDDR\_CORE ビアの間のビアからビアへの最小間隔は 1.11mm です。また、電源クロストークをさらに制限するため、これら 2 つの電源のビアの間に GND ビアも挿入します。

AM62Px eMMC PHY のコアは、VDDR\_CORE 電源ピンから電力が供給されます。PCB 上では、1.8V の VDDS\_MMCO PHY IO 電源と 0.85 V の VDDR\_CORE 電源との間にアイソレーションを設ける必要があります。これは、1.8V の VDDS\_MMCO 電源から 0.85V の VDDR\_CORE 電源へノイズが結合するのを防ぐためです。このようなノイズが eMMC PHY のコアに結合するとジッタが発生し、信号インテグリティのマージンが低下します。[図 2-1](#) と [図 2-2](#) に、[SK-AM62P-LP \(PROC164E2\)](#) の VDDS\_MMCO および VDDR\_CORE 電源のビア配置およびデカップリング コンデンサの配置を示します。VDDS\_MMCO は紫、VDDR\_CORE は赤で示しています。

### 3 eMMC ボード設計シミュレーション

このセクションは、高速 eMMC インターフェイスに対する基本的なシステム レベルのボード抽出、シミュレーション、および解析手法の概要を提供することを目的としています。これは、PCB 設計が目標とする動作速度で動作するためのすべての要件を満たしていることを確認するための重要なステップです。

#### 3.1 ボード モデルの抽出

以下に示すボード レベル抽出ガイドラインは、あらゆる EDA 抽出ツールで利用できるように意図されており、特定のツールに依存するものではありません。タッチストーン モデルの抽出が完了した直後に、[セクション 3.2](#) に示された手順に従うことが重要です。IBIS シミュレーションを実行する前に、次の手順で設計をチェックする必要があります。

1. 電源抽出は、常に 3D-EM ソルバーを用いて実施する必要があります。

2. 信号抽出の場合、2.5D 抽出で十分です

3. 広帯域モデルを使用します。TI は、DC からナイキスト周波数の少なくとも 6 倍まで抽出することを推奨しています (例えば、eMMC HS400 の場合は、少なくとも 2.4GHz までモデルを抽出します)。

4. 正確な層厚および材料特性を確認するために、基板のスタックアップを確認します。

- a. TI は、誘電体材料の定義において Djordjevic-Sarkar モデルを使用することを推奨しています。

5. スタックアップの全層にわたる信号トレースに対して、正確なエッチング形状と表面の粗さを反映させる必要があります。

6. 基板レイアウトを抽出前にカットする場合 (シミュレーション時間を短縮するため)、信号および電源ネットから少なくとも 0.25 インチ離れた位置にカット境界を設定します。

7. ビアのパッド スタック定義を確認します。

- a. 信号ビアにおける機能しない内層パッドが、実際の製造方法と同じ形でモデル化されていることを確認します。

- b. 信号ビアにおける機能しない内層パッドは、TI では推奨されていません。

8. システム内のすべての受動部品のモデル化には、Spice/S パラメータ モデル (通常はベンダから提供されます) を使用します。

#### 3.2 ボード - モデルの検証

抽出したボード モデルについては、以下の特性を確認する必要があります:

- 受動性:これにより、ボード モデルが受動ネットワークであり、エネルギーを生成しないことを確認できます。

- 因果性:これにより、ボード モデルが因果関係 (入力に対して出力が後続する) を満たしていることを確認できます。

これらの点検は、標準の EDA シミュレータまたは抽出エンジンで実行できます。

#### 3.3 コンデンサ ループのインダクタンス

高周波デカッピング コンデンサは、瞬時の電流要求に応答するため、ループ インダクタンスを低く抑える必要があります。この局所的な応答は、同じ電源を共有する別の電源ピンに、ある電源ピンからの電源ノイズが結合するのを防ぐのにも役立ちます。デカッピング コンデンサまでの経路がインダクティブである場合、SoC パッケージに固有のインダクタンスにさらにインダクタンスを加えるだけです。

高周波デカッピング コンデンサは、低い実装直列インダクタンス (ESL) を持つ必要があります。[SK-AM62P-LP \(PROC164E2\)](#) は、ESL が約 0.146nH のセラミック 0.1uF、10V、10%、0201 コンデンサを使用しています。各コンデンサの配置およびパターンやビアによる接続は、合計ループ インダクタンスを最小化するため、短くかつ幅広に保つ必要があります。

1.8V の VDDS\_MMC0 eMMC PHY IO 電源は、通常、eMMC 用と非 eMMC 用の電源で共有されます。各電源ピンには、それぞれの電源ピンの近傍に配置されたデカッピング コンデンサが必要です。下表に、[SK-AM62P-LP \(PROC164E2\)](#) が使用する 1.8V レール上の各コンデンサのループ インダクタンスを示します。

以下の手順でループ インダクタンスを確認してください:

1. VDDS\_MMC0 に短絡されている他の 1.8V 電源レール上のすべての高周波デカッピング コンデンサについてループ インダクタンスを抽出します。

- a. ループ インダクタンスは、3D フィールドソルバーを使用して抽出する必要があります。インダクタンス抽出には、**2.5D ソルバー**では不十分です。

- b. インダクタンスの抽出は、デカップリング コンデンサのパッドから SoC の BGA までを対象とする必要があります。

2. 抽出されたループ インダクタンスを、[表 3-1](#) に記載されている目標値と比較します。

- a. ループインダクタンスのチェックに合格するためには、VDDS\_MMCO および VDDS\_MMCO に短絡されている他の 1.8V 電源ネット上のすべてのデカップリング コンデンサのループ インダクタンスが、目標値より小さくなっている必要があります。

**表 3-1. VDDS\_MMCO および他の共有 1.8V 電源レール上のコンデンサのループ インダクタンス**

| 電源名                                               | 説明                                         | ターゲット                |

|---------------------------------------------------|--------------------------------------------|----------------------|

| VDDS_MMCO                                         | 1.8V eMMC0 PHY IO 電源                       | $\leq 0.72\text{nH}$ |

| VDDSHVn <sup>(1)</sup> 、VDDSHV_CANUART、VDDSHV MCU | VDDS_MMCO と共有された 1.8V IO 電源 <sup>(2)</sup> | $\leq 1.37\text{nH}$ |

(1)  $N = 0 - 6$

(2) VDDS\_MMCO 電源と共有されている 1.8V IO 電源のみを対象として考慮します。

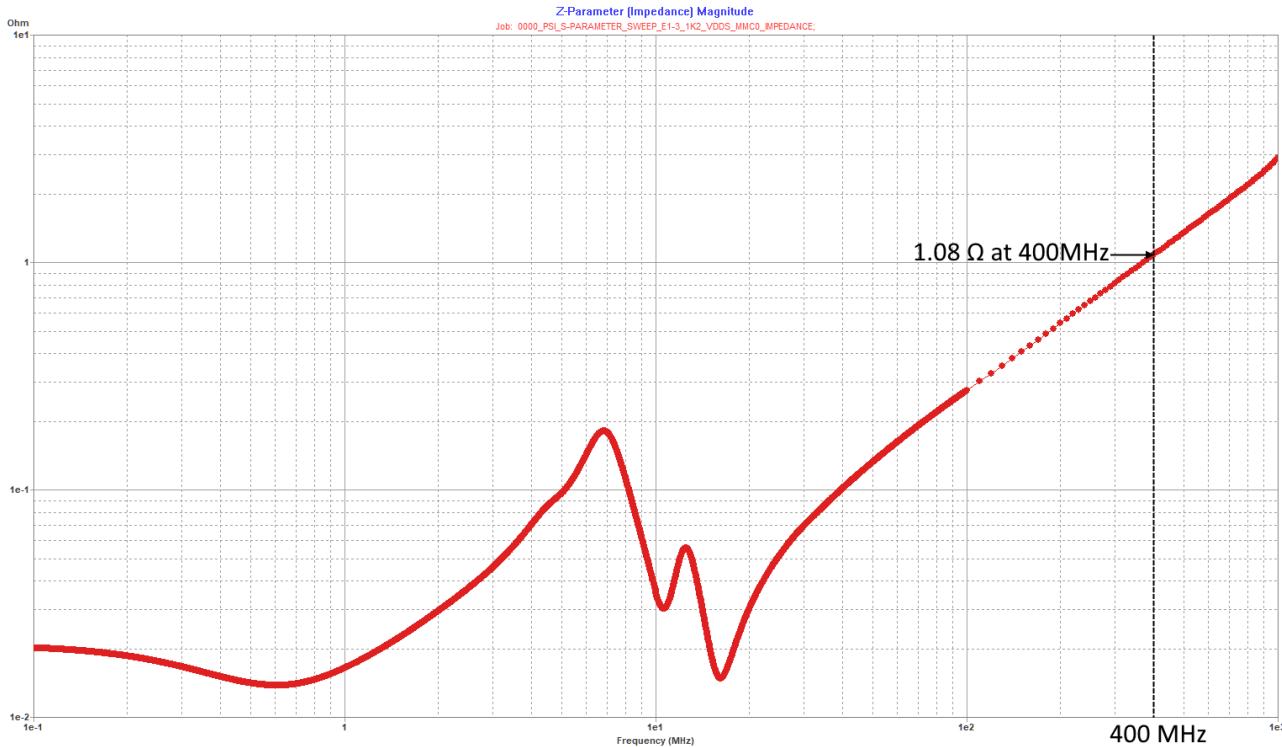

### 3.4 AC インピーダンス

以下に示す [SK-AM62P-LP \(PROC164E2\)](#) 上の VDDS\_MMCO eMMC PHY IO 電源の AC インピーダンスプロットは、PMIC のインダクタ出力から VDDS\_MMCO の SoC ピンまでの、ビアおよびデカップリング コンデンサを含む電源および GND の形状を考慮したものです。SoC パッケージとダイはモデル化されていません。

完全なシステム モデル化を通じて、TI は、[図 3-1](#) に示した AC インピーダンス プロファイルが、HS400 データレートにおいて JESD84-B51 規格への準拠を達成するのに十分なレベルで電源ノイズを制御できていることを実証しています (例: 400MHz)。

次の手順で AC インピーダンスを確認します:

1. デカップリング コンデンサを含め、PCB の 1.8V AM62Px VDDS\_MMCO eMMC PHY IO 電源の S パラメータ ファイルを抽出します。

- a. 電源 S パラメータの抽出には、3D フィールド ソルバーを使用する必要があります。電源の抽出には、**2.5D ソルバー**では不十分です。

- b. 電力は、PMIC のインダクタの出力から AM62Px VDDS\_MMCO ピンまでモデル化する必要があります。

- c. 電源バス上に含まれるコンデンサやその他の部品は、ベンダ 提供の S パラメータまたは SPICE モデルを使用して、正確にモデル化する必要があります。

2. eMMC PHY IO 電源 VDDS\_MMCO の AC インピーダンスをプロットし、以下の [図 3-1](#) に示す目標 AC インピーダンス プロファイルと比較します。

- a. VDDS\_MMCO の AC インピーダンスを、DC から 400MHz まで確認します。AC インピーダンスのチェックに合格するためには、抽出した AC インピーダンスが [図 3-1](#) 以下である必要があります。

#### 注

おおよそ 50MHz を超えると、PCB の電源プレーンやデカップリング コンデンサがインピーダンスに与える影響は次第に小さくなります。周波数が高くなるにつれて、SoC パッケージのインダクタンスやオンダイ容量の影響がより支配的になります

図 3-1. VDDS\_MMCO AC インピーダンス振幅と周波数との関係 (ボードのみ)

### 3.5 IBIS モデル シミュレーション

このセクションでは、eMMC 信号を検証するための手法を概説しています。IBIS モデルおよび抽出された PCB モデルを用いたチャネル シミュレーションでは、ターゲットとするデータ攻撃ビット パターン (セクション 3.5.2 を参照) を適用し、信号波形やアイダイアグラムを生成します。これらの結果は、JESD84-B51 規格で定義されているセットアップ / ホールド時間、スルーレート、DCD、パルス幅への適合性について確認されます。さらに、VIH/VIL の電圧レベルに対するリングバックについても追加のチェックが実施されます。

#### 3.5.1 シミュレーションの設定

以下の手順で IBIS シミュレーションをセットアップします:

1. 基板上の eMMC 信号の S パラメータ ファイルを抽出します。

- a. 基板信号については、2.5D エクストラクタを使用しても問題ありません。

2. TI.com の [AM62Px](#) 製品ページから SoC の IBIS モデルを入手します。

3. SoC パッケージの S パラメータ モデルは、TI の担当者から入手します (NDA の下で別途提供されます)

- a. セクション 3.5.5 に記載されている合否チェックは、S パラメータ SoC パッケージ モデルを用いたシステムを前提として導出されているため、S パラメータの SoC パッケージ モデルを使用することが必須です。

- b. S パラメータの SoC パッケージ モデルではなく SoC の IBIS RLC パッケージ モデルを使用したシミュレーションでは、楽観的な結果が得られてしまい、適用可能なマージン計算は行えません。

- c. SoC IBIS RLC パッケージ モデルの使用は禁止されています。シミュレーション設定において、SoC の IBIS モデルで「パッケージ寄生成分」にチェックが入っていないことを確認します。

4. eMMC デバイスの IBIS モデルは、eMMC ベンダーから入手します。

- a. この IBIS モデルには、eMMC デバイスのパッケージ RLC モデルが含まれている必要があります

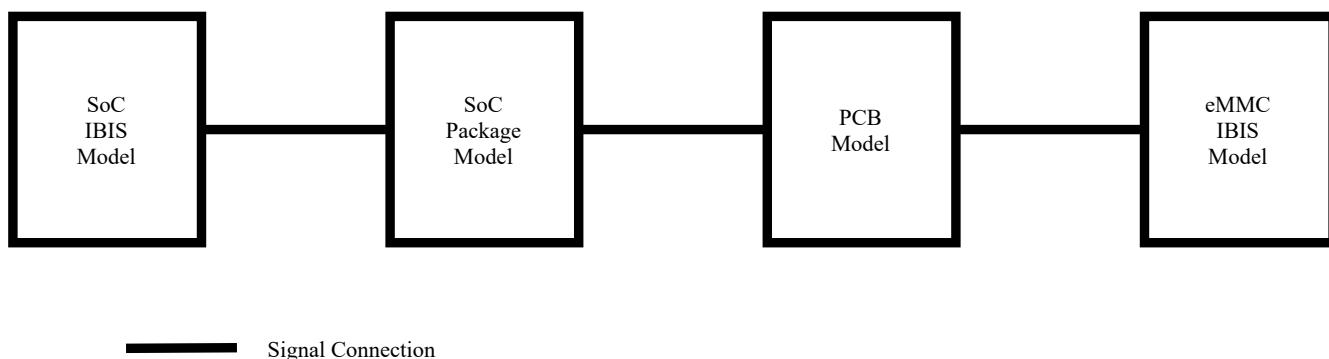

5. 任意のシミュレータに示されているように、シミュレーション ネットリストを作成します。

- a. SoC の IBIS モデル、基板モデル、電源、および eMMC デバイスの IBIS モデルを接続して、シミュレータ上でシステム レベルの回路図を構成します。

- b. 図 3-2 に、代表的なシステム レベルの eMMC 回路図を示します。

6. シミュレーションで使用するプロセス、電圧、温度の各コーナー条件を構築します

- IBIS モデルでサポートされているすべてのプロセス、電圧、温度条件にわたってシミュレーションを実施することが推奨されます

- 標準 (TT):

- IO 電圧 = 1.8V

- 温度 = 30C

- 最小 (SS):

- IO 電圧 =  $1.8V * 0.9 = 1.62V$

- 温度 = 125C

- 最大 (FF):

- IO 電圧 =  $1.8V * 1.1 = 1.98V$

- 温度 = -40C

- JEDEC で規定されている公称ドライブ強度は  $50\Omega$  です。ただし、シミュレーションの結果、より良好な信号整合マージンが得られる場合には、顧客が他のドライブ強度を試すことも可能です。

7. シミュレーションを実行する前に、セクション 3.5.3 を確認し、これらのベスト プラクティスが順守されていることを確認します。

8. セクション 3.5.2 に記載されているすべてのアタック パターンを、シミュレーションの刺激信号として使用します。

9. 波形解析ツールで結果を解析し、セクション 3.5.5 に記載されているデータシートの規格に基づいた合否判定を行って品質を評価します

電力を意識したシミュレーションを設定しないでください。電源ノイズは、このドキュメントの前章で述べたループ インダクタンスおよび AC インピーダンスのチェックによって制御されます。

図 3-2. システム レベルの代表的な eMMC 回路図

### 3.5.2 シミュレーション ビット パターン

標的型データ攻撃用のビット パターンは、[こちらからダウンロード](#)できます。

これらのパターンは、実際の動作条件に近く、かつ最悪ケースとなる条件でシステムを評価できるよう設計されています。各データラインは個別のパターンを使用します。すべてのデータラインは同時にシミュレーションする必要があります。各ビット パターンは 6,964 ビットで構成されており、以下に示す 6 つの攻撃パターン グループを連結したものです

1. 2,096 ビット - VIH/VIL に対する攻撃、および 200MHz と 400MHz での攻撃

2. 296 ビット - 200MHz における補助攻撃

3. 2,124 ビット - 最悪ケースの ISI/SSO 攻撃パターン。PRBS と ISISSO38 を組み合わせ、8 ビットすべてに攻撃します

4. 296 ビット - 400MHz における補助攻撃

5. 1,000 ビット - ISI/SSO 攻撃 (3 UI, 8 ビット)

6. 1,152 ビット - 8 ビットすべてで回転した PRBS パターン

### 3.5.3 シミュレーションのベスト プラクティス

提供されているガイダンスは、特定の EDA ツールを前提としたものではありません。以下に示すベスト プラクティスの一覧は、適切な EDA ベンダと連携することで、使用するシミュレータに実装できます

- S パラメータを用いたシミュレーションを行う際には、シミュレータの収束性を高め、正確な波形結果を得るために、S パラメータのスムージングを可能にするオプションを有効にすることを強く推奨します

- シミュレータの収束を確保し、正確な波形結果を得るためにには、シミュレータのタイムステップおよび精度設定を適切に設定する必要があります

- 最大 5GHz のボード信号とボード電源モデルを抽出できます

- 抽出した S パラメータについては、因果性および受動性が満たされているかを確認する必要があります。因果性や受動性を満たしていない S パラメータは、不正確な結果を招く可能性があります

- アタック パターンを用いた一連のシミュレーションを実行する前に、シミュレーション設定および接続を検証する目的で、10 ~ 15 ビット程度の短いシミュレーションを実施することが推奨されます

- 抽出モデルにおける信号パターンのインピーダンスを確認し、インピーダンスのばらつきが許容範囲内に収まっていることを確認することが推奨されます

### 3.5.4 シミュレーション戦略と例

JESD84-B51 仕様の各パラメータが正のマージンをもって満たされているかどうかを評価するため、シミュレーションの方針および目的についての説明に加え、用いられた計算方法の詳細を説明しています。

SOC および eMMC デバイスの IBIS モデルを用いてシミュレーションを行い、SOC パッケージ、基板、eMMC パッケージのインターフェクトについて高精度なモデルを使用します。IBIS シミュレーションによる測定結果と TI データシートに記載された出力タイミング パラメータを組み合わせ、JESD84-B51 仕様に対するタイミング マージンを実証します。

TI は、本アプリケーション ノートで説明している IBIS シミュレーション手法に加え、電源影響を考慮した SPICE シミュレーションも、同一のシステム (SOC モデル、eMMC モデル、パッケージ モデル、および基板) を用いて実施しています。IBIS シミュレーションによる測定結果には、IBIS シミュレーション手法の結果を電源影響を考慮した SPICE シミュレーションと整合させるため、IBIS/SPICE 相関に基づく補正を含める必要があります。これが、電源ノイズの影響を IBIS シミュレーションにおいて考慮する方法です。主な目的は、電源影響を考慮した SPICE シミュレーションと比較した際に、IBIS シミュレーションが示す可能性のある過度な楽観性を考慮することです。ループ インダクタンスおよび AC インピーダンスのチェックによって電源ノイズが許容範囲内に制御されているため、電源考慮型の IBIS シミュレーションは設定しません。[セクション 3.3](#) および [セクション 3.4](#) を参照してください。

基板およびパッケージにおける信号クロストークは、IBIS シミュレーション用に抽出された各 S パラメータ モデルにすべての信号配線を含めることで考慮されています。

SOC の IBIS モデルは、標準 (TT)、最小 (SS)、および最大 (FF) の各プロセスコーナーをサポートしています：

- 標準 (TT):

- IO 電圧 = 1.8V

- コア電圧 = 0.85V

- 最小 (SS):

- IO 電圧 =  $1.8V * 0.9 = 1.62V$

- コア電圧 =  $0.85V * 0.9 = 0.765V$

- 最大 (FF):

- IO 電圧 =  $1.8V * 1.1 = 1.98V$

- コア電圧 =  $0.85V * 1.1 = 0.935V$

### セットアップ / ホールド時間

DAT および CMD のセットアップ時間およびホールド時間は、JESD84-B51 仕様に規定されている入力セットアップ時間および入力ホールド時間のパラメータを満たす必要があります。以下に説明するシミュレーション戦略を使用して、IBIS モデルのシミュレーションに基づいてシステムの全体的なマージンを計算します。これらの計算には、TI のデータシートに記載されている出力セットアップ時間および出力ホールド時間のパラメータを使用します。

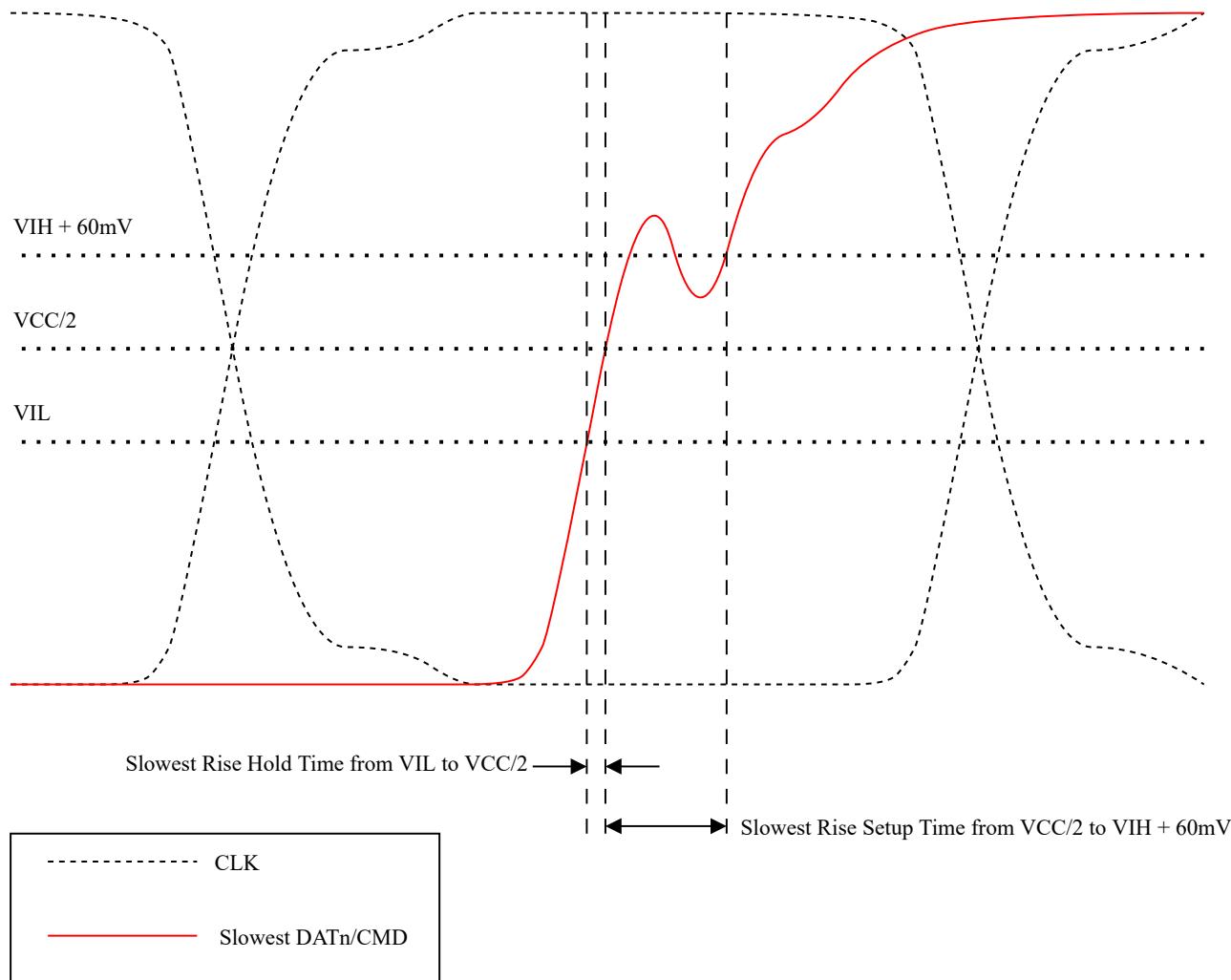

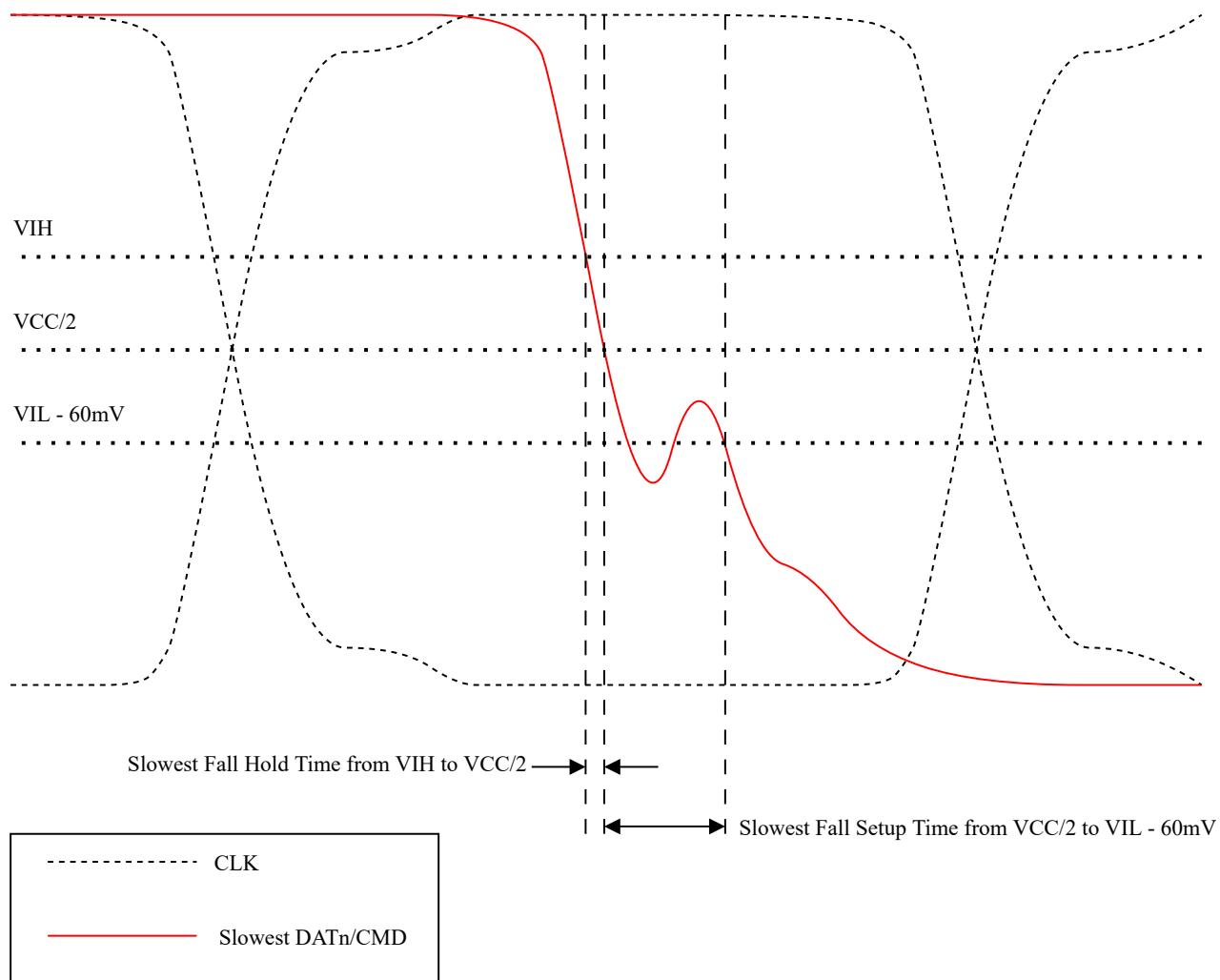

出力セットアップ時間パラメータと出力ホールド時間のパラメータは、データシートの「MMC0 スイッチング特性 – HS400 モード」表に定義されています。これらのパラメータには、TI データシートの「MMC0 のタイミング条件」表に定義されている最大伝搬遅延の不一致値が含まれます。セットアップ時間およびホールド時間の計算においては、VCC/2 と VIL/VIH の間ににおける最も遅い信号スルーフィルタを差し引く必要がある点に注意が必要です。これは、TI データシートでは DAT または CMD 信号遷移の VCC/2 から CLK 信号遷移の VCC/2 をタイミング基準として定義しているのに対し、JESD84-B51 では DAT または CMD 信号遷移の VIL または VIH から CLK 信号遷移の VCC/2 をセットアップ時間の基準として定義しているためです。

- E: 全体的なマージン

- $E = (A - B - C) - D$

- マージンを確保するためには、E が 0 より大きい必要があります

- データのセットアップ、データのホールド、CMD のセットアップ、および CMD のホールドについて、FF および SS シミュレーションの測定結果 (ならびに IBIS/SPICE 相関に基づく各 FF/SS の調整値) を用いて、全体のマージンを計算します。全体のマージンを評価する際には、最もマージンが小さくなる結果 E を考慮します。表 3-2 は、SK-AM62P-LP (PROC164E2) において最悪条件となる FF コーナーの例を示しています。

- A: データシートに基づく AM62P の AC タイミング仕様

- 出力セットアップ時間 HS4008 (CMD)、HS4009 (DAT)

- 出力ホールド時間 HS40010 (CMD)、HS40011 (DAT)

- B: eMMC デバイスにおける CMD または DAT 信号の VCC/2 から VIH/VIL までの最悪ケースの立ち上がり / 立ち下がり時間を、IBIS シミュレーション結果から測定したものです。図 3-5 および図 3-6 を参照してください。

- C: IBIS/SPICE 相関からの調整

- セットアップ時間およびホールド時間の計算において、IBIS モデルは SPICE に比べて楽観的な結果を示す傾向があります

- FF コーナーの場合は 80ps

- SS コーナーの場合は 35ps

- この調整値は、シミュレーションしている該当の FF または SS コーナーに対する全体マージン計算から差し引く必要があります

- D: JESD84-B51 仕様で定義されている CMD/DAT の入力セットアップ時間および入力ホールド時間です。

**表 3-2. SK-AM62P-LP (PROC164E2) のセットアップ / ホールド (FF) 全体マージン計算の例**

| メトリック        | A: AC タイミング仕様    | B: IBIS シミュレーションから得られた VCC/2 から VIH/VIL までの値 | C: SPICE と IBIS の相関から求められる追加で必要なマージン | D: JESD84-B51 仕様 | E: 全体的なマージン |

|--------------|------------------|----------------------------------------------|--------------------------------------|------------------|-------------|

| データ (SETUP)  | 0.70ns (HS4009)  | 0.150ns                                      | 0.080                                | 0.4ns            | 0.070ns     |

| データ (HOLD)   | 0.76ns (HS40011) | 0.150ns                                      | 0.080                                | 0.4ns            | 0.130ns     |

| CMD (セットアップ) | 2.86ns (HS4008)  | 0.124ns                                      | 0.080                                | 1.4ns            | 1.256ns     |

| CMD (ホールド)   | 1.16ns (HS40010) | 0.124ns                                      | 0.080                                | 0.8ns            | 0.156ns     |

### VIH/VIL (リングバック)

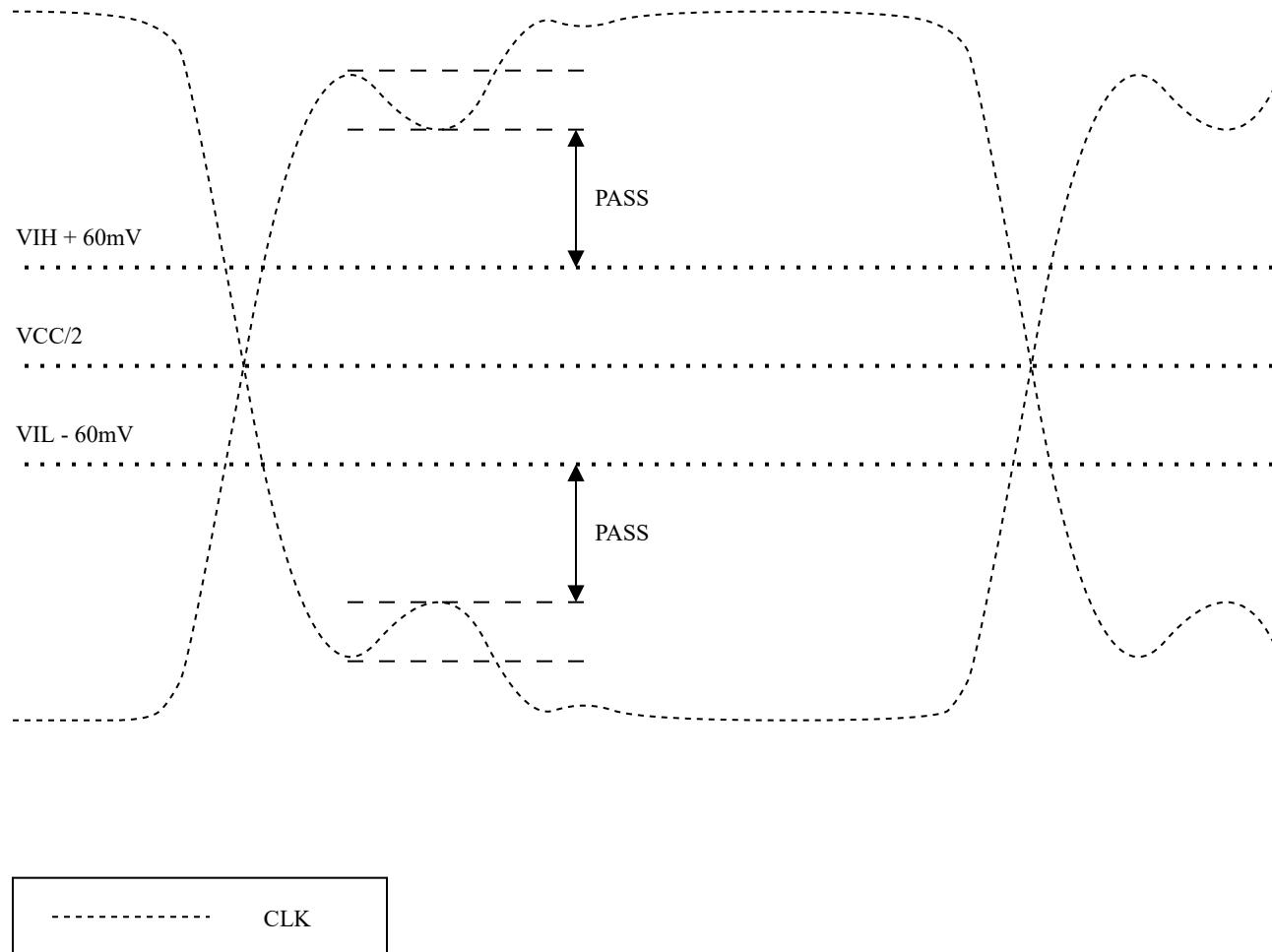

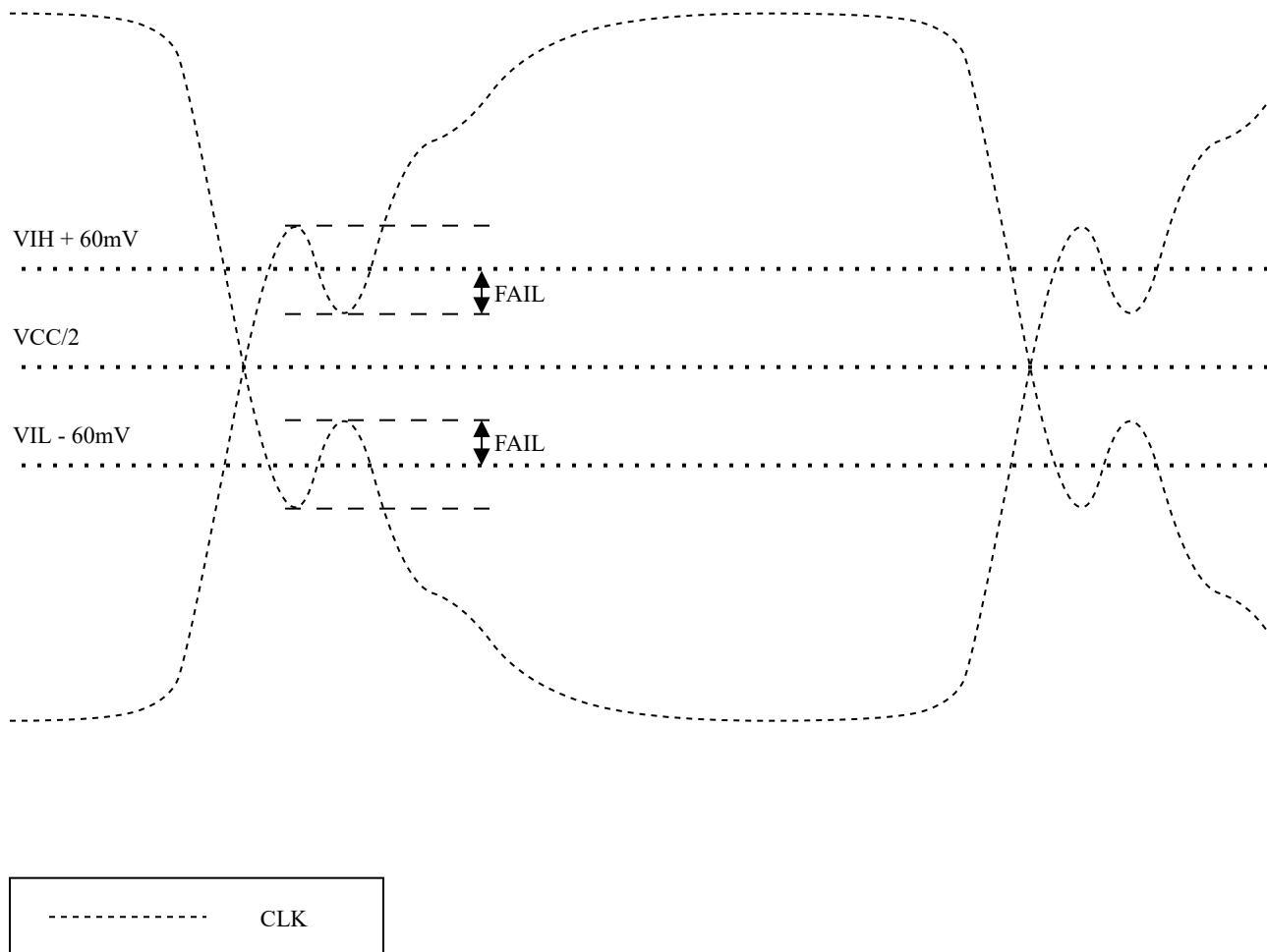

信号は、反射、電源ノイズ、クロストーク、その他の要因により、リングバックを示す場合があります。シミュレーションされた CLK 信号は、(VIH -60mV) から (VIH +60mV) の電圧範囲において、立ち上がりおよび立ち下がりの両方の遷移で単調である必要があります。図 3-7 を参照してください。VIH/VIL レベルの前後でリングバックが発生する場合、DAT と CMD のセットアップ / ホールド時間マージンを減らすことができます。過度なリングバックが発生すると、IO バッファが論理状態を切り替えてしまい、機能不良を引き起こす場合があります。そのため、リングバックが発生する可能性については、必ずシミュレーションを行い、評価することが重要です。

VIH/VIL 付近のリングバックに関して、IBIS モデルは SPICE に比べて楽観的な結果を示す傾向があります。60mV は、SPICE と比較した際の IBIS シミュレーションの楽観性に起因する、IBIS/SPICE 相関に基づいて必要となる調整値です。これは、SPICE シミュレーションに含まれているリングバックに対する電源ノイズの影響を考慮するために必要です。

表 3-5 で説明されている IBIS シミュレーションの手法は、リングバックが信号品質に与える影響を定量化し、VIH/VIL レベル付近でリングバックが発生した場合に、システムにおけるセットアップ時間 / ホールド時間のマージンをどのように調整すべきかを評価するために用いられます。

リングバックは挙動が複雑であるため、どのプロセスコーナーが最悪ケースのリングバックを引き起こすかを事前に特定することはできません。そのため、少なくとも SS および FF のプロセスコーナーでシミュレーションを実施する必要があります。IBIS シミュレーションで評価している各 TT、SS、FF のプロセスコーナーに対する JESD84-B51 仕様の電圧スレッショルドを以下に示します：

- 標準 (TT):

- VIH = 1.8V \* 0.65 = 1.170V

- VIL = 1.8V \* 0.35 = 0.630V

- 最小 (SS):

- VIH = 1.62V \* 0.65 = 1.053V

- VIL = 1.62V \* 0.35 = 0.567V

- 最大 (FF):

- VIH = 1.98V \* 0.65 = 1.287V

- VIL = 1.98V \* 0.35 = 0.693V

IBIS シミュレーションの楽観性を考慮するため、上記の電圧スレッショルドには 60mV の調整を適用する必要があります。表 3-5 の VIH/VIL (リングバック) を参照し、図 3-9 および 図 3-10 を確認してください。

## スルーレート

eMMC デバイスにおいて、VIL から VIH、および VIH から VIL におけるすべての信号のスルーレートは、JESD84-B51 に定義されているスルーレートパラメータに基づく最小スルーレート要件である 1.125V/ns 以上である必要があります。システム内に存在する電源ノイズ、クロストーク、および反射は、信号のスルーレートに影響を与えます。SPICE では電源ノイズの追加影響がモデル化されているため、スルーレートに関しては、IBIS モデルは SPICE に比べて楽観的な結果を示す傾向があります。

SPICE と比較した際の IBIS シミュレーションの楽観性を考慮し、IBIS シミュレーションのサインオフ条件としては、1.45V/ns のスルーレート (JESD84-B51 仕様の 1.125V/ns に対し、IBIS/SPICE 相関に基づく 30% の調整を適用した値) が必要です。図 3-11 および 図 3-12 に CLK を示します。リングバックなしの DAT/CMD については、図 3-13 および 図 3-14 を参照してください。VIH/VIL に 60mV の調整が適用された後、スルーレートを満たす必要がある VIH/VIL 領域でリングバックを行う DAT/CMD については、図 3-15 と 図 3-16 を参照してください。

## DCD

JESD84-B51 仕様に従って、合計 DCD は 300ps 未満である必要があります。以下に説明するシミュレーション戦略を使用して、IBIS モデルのシミュレーションに基づいてシステムの全体的なマージンを計算します。

- G: 全体的なマージン

- $G = A - B - C - D - E - F$

- マージンを確保するためには、G が 0 より大きい必要があります

- A: JESD84-B51 仕様 (最大デューティサイクル歪み tCKDCD: 300ps)

- B: IBIS シミュレーションからの DCD 測定

- 「JESD84-B51 図 88 - HS400 デバイス データ入力タイミング」の tCKDCC タイミング定義を参照してください

- トリガを中央に配置して CLK 信号をプロットし、トリガの左側に正パルス幅と負パルス幅を各 1 つ、右側に正パルス幅と負パルス幅をそれぞれ 1 つ表示します。[図 3-17](#) を参照してください。

- トリガの左側および右側の両方について、CLK の最小および最大パルス幅を測定します (合計 4 回の測定)。各側について、正パルスおよび負パルスの両方を考慮します。

- シミュレーションしているプロセスコーナーの IO 電圧に基づいてスケーリングされた VCC/2 (Vt) と VCC/2 (Vt) のクロッシング間を測定します:

- 標準 (TT):  $VCC/2 = 1.8V / 2 = 0.90V$

- 最小 (SS):  $VCC/2 = 1.62V / 2 = 0.81V$

- 最大 (FF):  $VCC/2 = 1.98V / 2 = 0.99V$

- CLK ジッタを二重にカウントしないよう、各測定の一方の端点はトリガに合わせて開始します

- トリガの左側および右側について、最小および最大のパルス幅を記録します (4 回の測定値)

- 各最小値 / 最大値の測定結果から、理想クロックのパルス幅を差し引きます (HS400 の 200MHz CLK の場合は 2.5ns)

- 各差分の絶対値を取得します

- DCD は、4 つの数値のうち最大 (最悪) です

- DCD 測定の例:

1. 最小パルス幅 (左):  $absval(2.387ns - 2.5ns) = 0.113ns$

2. 最大パルス幅 (左):  $absval(2.618ns - 2.5ns) = 0.118ns$  (最悪)

3. 最小パルス幅 (右):  $absval(2.392ns - 2.5ns) = 0.108ns$

4. 最大パルス幅 (右):  $absval(2.613ns - 2.5ns) = 0.113ns$

5.  $DCD = \max(0.113ns, 0.118ns, 0.108ns, 0.113ns) = 0.118ns$

- C: DCD に対する IBIS/SPICE 相関に基づく調整値

- DCD の計算に関して、IBIS モデルは SPICE に比べて楽観的な結果を示す傾向があります

- 39ps は、SPICE と比較した際の IBIS シミュレーションの楽観性に起因する調整値です

- この調整値は、全体マージンの計算から差し引く必要があります

- D: ベータ プロセス (SF/FS) コーナーからの調整

- IBIS モデルによる標準 (TT)、最小 (SS)、および最大 (FF) のシリコン プロセスばらつきのシミュレーションでは、ベータ プロセス (SF/FS) コーナーはシミュレーションされていません

- 8ps は、ベータ プロセス (SF/FS) コーナーに対する調整値です

- この調整値は、全体マージンの計算から差し引く必要があります

- E: CLK ツリーと PHY レベル シフタの影響

- IBIS モデルのシミュレーションでは、AM62Px SoC 内の eMMC コントローラと PHY の間にあるクロック ツリーおよびレベル シフタによる DCD の寄与は考慮されていません

- 42ps は、eMMC コントローラと PHY の間にあるクロック ツリーおよびレベル シフタによる寄与です

- この値は、全体的なマージンの計算から減算する必要があります

- F: PLL ジッタの影響

- IBIS モデルのシミュレーションは、AM62Px SoC 内の PLL ジッタの DCD の寄与を考慮していません

- 61ps は PLL ジッタの寄与です

- この値は、全体的なマージンの計算から減算する必要があります

**表 3-3. SK-AM62P-LP (PROC164E2) の DCD 全体マージン計算の例**

| A: JESD84-B51 仕様 | B: IBIS シミュレーションからの DCD 測定 | C: IBIS/SPICE 相関からの調整 | D: ベータ プロセス (SF/FS) コーナーからの調整 | E: CLK ツリーと PHY レベル シフタの影響 | F: PLL ジッタの影響 | G: 全体的なマージン |

|------------------|----------------------------|-----------------------|-------------------------------|----------------------------|---------------|-------------|

| 0.3ns            | 0.118ns                    | 0.039ns               | 0.008ns                       | 0.042ns                    | 0.061ns       | 0.032ns     |

### パルス幅

JESD84-B51 仕様に基づき、合計パルス幅は 2.2ns を超えていなければなりません。以下に説明するシミュレーション戦略を使用して、IBIS モデルのシミュレーションに基づいてシステムの全体的なマージンを計算します。

- **G: 全体的なマージン**

- $G = B - A - C - D - E - F$

- マージンを確保するためには、**G** が 0 より大きい必要があります

- **A: JESD84-B51 の仕様 (最小パルス幅 tCKMPW: 2.2ns)**

- **B: IBIS シミュレーションによる最小パルス幅測定**

- JESD84-B51 図 88 - HS400 デバイス データ入力タイミングの tCKMPW タイミング定義を参照してください。

- トリガを中央に配置して CLK 信号をプロットし、トリガの左側に正パルス幅と負パルス幅を各 1 つ、右側に正パルス幅と負パルス幅をそれぞれ 1 つ表示します。[図 3-17](#) を参照してください。

- トリガの左右両方の最小 CLK パルス幅を測定します (2 回の測定)。各側について、正パルスおよび負パルスの両方を考慮します。

- シミュレーションしているプロセス コーナーの IO 電圧に基づいてスケーリングされた VCC/2 (Vt) と VCC/2 (Vt) のクロッシング間を測定します:

- 標準 (TT):  $VCC/2 = 1.8V / 2 = 0.90V$

- 最小 (SS):  $VCC/2 = 1.62V / 2 = 0.81V$

- 最大 (FF):  $VCC/2 = 1.98V / 2 = 0.99V$

- CLK ジッタを二重にカウントしないよう、各測定の一方の端点はトリガを基準にします

- 最小パルス幅は、2 つの測定結果のうち最も小さい値 (最悪値) です

- 最小パルス幅測定の例:

1. 最小パルス幅 (左): 2.387ns

2. 最小パルス幅 (右): 2.392ns

3. 最小パルス幅 =  $\min(2.387ns, 2.392ns) = 2.387ns$

- **C: パルス幅に対する IBIS/SPICE 相関に基づく調整値**

- パルス幅の計算に関して、IBIS モデルは SPICE に比べて楽観的な結果を示す傾向があります

- 39ps は、SPICE と比較した際の IBIS シミュレーションの楽観性に起因する調整値です

- この調整値は、全体マージンの計算から差し引く必要があります

- **D: ベータ プロセス (SF/FS) コーナーからの調整**

- IBIS モデルによる標準 (TT)、最小 (SS)、および最大 (FF) のシリコン プロセスばらつきのシミュレーションでは、ベータ プロセス (SF/FS) コーナーはシミュレーションされていません

- 8ps は、ベータ プロセス (SF/FS) コーナーに対する調整値です

- この調整値は、全体マージンの計算から差し引く必要があります

- **E: CLK ツリーと PHY レベル シフタの影響**

- IBIS モデルのシミュレーションでは、AM62Px SoC 内の eMMC コントローラと PHY の間にあるクロック ツリーおよびレベル シフタによる DCD の寄与は考慮されていません

- 42ps は、eMMC コントローラと PHY の間にあるクロック ツリーおよびレベル シフタによる寄与です

- この値は、全体的なマージンの計算から減算する必要があります

- **F: PLL ジッタの影響**

- IBIS モデルのシミュレーションは、AM62Px SoC 内の PLL ジッタの DCD の寄与を考慮していません

- 61ps は PLL ジッタの寄与です

- この値は、全体的なマージンの計算から減算する必要があります

**表 3-4. SK-AM62P-LP (PROC164E2) におけるパルス幅の全体マージンの計算例**

| B: IBIS シミュレーションによる最小パルス幅測定 | A: JESD84-B51 仕様 | C: IBIS/SPICE 相関からの調整 | D: ベータ プロセス (SF/FS) コーナーからの調整 | E: CLK ツリーと PHY レベル シフタの影響 | F: PLL ジッタの影響 | G: 全体的なマージン |

|-----------------------------|------------------|-----------------------|-------------------------------|----------------------------|---------------|-------------|

| 2.387ns                     | 2.2ns            | 0.039ns               | 0.008ns                       | 0.042ns                    | 0.061ns       | 0.037ns     |

### 3.5.5 合格 / 不合格チェック

以下の表 3-5 では、JESD84-B51 仕様への適合性を確認するための、セットアップ時間 / ホールド時間、スルーレート、DCD、およびパルス幅のチェックについて説明しています。追加のリングバック チェックにより、信号が VIH/VIL の電圧レベル要件を満たしていることを確認します。それぞれのチェックは、CLK、DATA、および CMD で個別に詳細に説明され

ています。JEDEC のチェックについては、JESD84-B51 の表 212 - HS200 デバイス入力タイミング (JESD84-B51 セクション 10.8.2) および表 215 - HS400 デバイス入力タイミング (JESD84-B51 セクション 10.10.1) を参照してください。

**表 3-5. 合格 / 不合格チェック**

| パラメータ           | CLK                                                    | データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| セットアップ / ホールド時間 | <ul style="list-style-type: none"> <li>該当なし</li> </ul> | <ul style="list-style-type: none"> <li>電源を考慮していないモードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>CLK 信号に対して、DAT [7:0] 信号に 1/4 クロック サイクルの遅延を適用してください (図 3-3 を参照)。</li> <li>データシートの「スイッチング特性」のタイミング表から、適切な出力セットアップ時間または出力ホールド時間を使用します。例えば、セットアップ マージンを確認する際には出力セットアップ時間 (HS4009) を使用し、ホールド マージンを確認する際には出力ホールド時間 (HS40011) を使用します。</li> <li><b>セットアップ時間:</b> 全体マージン E は、<math>E = (A - B - C) - D</math> として算出します。接続されているデバイスのセットアップ要件に対して十分なマージンがあるかどうかを判断するため、データシートに記載されている最小出力セットアップ時間パラメータ (A) から、以下の 3 つの値を差し引きます： <ul style="list-style-type: none"> <li>B:接続されている eMMC デバイスの BGA において、立ち上がり遷移時の VCC/2 から VIH まで (図 3-5 を参照)、または立ち下がり遷移時の VCC/2 から VIL まで (図 3-6 を参照) で測定された、最も遅い DAT 信号のスルーレートです。<sup>(4)</sup></li> <li>C:IBIS/SPICE 相関からの調整:<sup>(3)</sup> <ul style="list-style-type: none"> <li>FF コーナーの場合は 80ps</li> <li>SS コーナーの場合は 35ps</li> </ul> </li> <li>D:接続された eMMC デバイスが必要とする 400ps のセットアップ時間 (JESD84-B51 規格準拠<sup>(1)</sup>)</li> </ul> </li> <li>これら 3 つの値をデータシートの最小出力セットアップ時間の値から差し引いた後、全体マージン (E) が正の値である必要があり、これを満たせば合格です</li> <li><b>ホールド時間:</b> 全体マージン E は、<math>E = (A - B - C) - D</math> として算出しま</li> </ul> | <ul style="list-style-type: none"> <li>電源を考慮していないモードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>各立ち上がり CLK 遷移に対して CMD 信号に 1/4 クロック サイクル + 400ps の遅延を印加します (図 3-4 を参照)。</li> <li>データシートの「スイッチング特性」のタイミング表から、適切な出力セットアップ時間または出力ホールド時間を使用します。例えば、セットアップ マージンを確認する際には出力セットアップ時間 (HS4008) を使用し、ホールド マージンを確認する際には出力ホールド時間 (HS40010) を使用します。</li> <li><b>セットアップ時間:</b> 全体マージン E は、<math>E = (A - B - C) - D</math> として算出します。接続されているデバイスのセットアップ要件に対して十分なマージンがあるかどうかを判断するため、データシートに記載されている最小出力セットアップ時間パラメータから、以下の 3 つの値を差し引きます： <ul style="list-style-type: none"> <li>B:接続されている eMMC デバイスの BGA において、立ち上がり遷移時の VCC/2 から VIH まで (図 3-5 を参照)、または立ち下がり遷移時の VCC/2 から VIL まで (図 3-6 を参照) で測定された、最も遅い CMD 信号のスルーレートです。<sup>(4)</sup></li> <li>C:IBIS/SPICE 相関からの調整:<sup>(3)</sup> <ul style="list-style-type: none"> <li>FF コーナーの場合は 80ps</li> <li>SS コーナーの場合は 35ps</li> </ul> </li> <li>D:接続された eMMC デバイスが必要とする 1400ps のセットアップ時間 (JESD84-B51 規格準拠<sup>(2)</sup>)</li> </ul> </li> <li>これら 3 つの値をデータシートの最小出力セットアップ時間の値から差し引いた後、全体マージン (E) が正の値である必要があり、これを満たせば合格です</li> <li><b>ホールド時間:</b> 全体マージン E は、<math>E = (A - B - C) - D</math> として算出しま</li> </ul> |

表 3-5. 合格 / 不合格チェック (続き)

| パラメータ | CLK | データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     | <p>出します。接続されているデバイスのホールド要件に対して十分なマージンがあるかどうかを判断するため、データシートに記載されている最小出力ホールド時間パラメータ (A) から、以下の 3 つの値を差し引きます：</p> <ul style="list-style-type: none"> <li>- B:接続されている eMMC デバイスの BGA において、立ち上がり遷移時の VIL から VCC/2 まで (図 3-5 を参照)、または立ち下がり遷移時の VIH から VCC/2 まで (図 3-6 を参照) で測定された、最も遅い DAT 信号のスルーレートです。<sup>(4)</sup></li> <li>- C:IBIS/SPICE 相関からの調整:<sup>(3)</sup> <ul style="list-style-type: none"> <li>• FF コーナーの場合は 80ps</li> <li>• SS コーナーの場合は 35ps</li> </ul> </li> <li>- D:接続済みの eMMC デバイスが必要とする 400ps のホールド時間 (JESD84-B51 規格準拠<sup>(1)</sup>)</li> <li>• これら 3 つの値をデータシートの最小出力ホールド時間の値から差し引いた後、全体マージン (E) が正の値である必要があり、これを満たせば合格です</li> </ul> | <p>す。接続されているデバイスのホールド要件に対して十分なマージンがあるかどうかを判断するため、データシートに記載されている最小出力ホールド時間パラメータから、以下の 3 つの値を差し引きます：</p> <ul style="list-style-type: none"> <li>- B:接続されている eMMC デバイスの BGA において、立ち上がり遷移時の VIL から VCC/2 まで (図 3-5 を参照)、または立ち下がり遷移時の VIH から VCC/2 まで (図 3-6 を参照) で測定された、最も遅い CMD 信号のスルーレートです。<sup>(4)</sup></li> <li>- C:IBIS/SPICE 相関からの調整:<sup>(3)</sup> <ul style="list-style-type: none"> <li>• FF コーナーの場合は 80ps</li> <li>• SS コーナーの場合は 35ps</li> </ul> </li> <li>- D:接続済みの eMMC デバイスが必要とする 800ps のホールド時間 (JESD84-B51 規格準拠<sup>(2)</sup>)</li> <li>• これら 3 つの値をデータシートの最小出力ホールド時間の値から差し引いた後、全体マージン (E) が正の値である必要があり、これを満たせば合格です</li> </ul> |

**表 3-5. 合格 / 不合格チェック (続き)**

| パラメータ            | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIH/VIL (リングバック) | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>(VIL - 60mV)<sup>(3)</sup> と (VIH + 60mV)<sup>(3)</sup> の間の電圧領域での立ち上がりおよび立ち下がり遷移の両方について、シミュレーションされた CLK 信号が単調であることを確認します。<sup>(3)</sup></li> <li>また、シミュレーションされた CLK 信号の立ち上がり遷移が (VIH + 60mV)<sup>(3)</sup> を超えて上昇し、次の立ち下がり遷移まで (VIH + 60mV)<sup>(3)</sup> を上回った状態を維持していることを確認してください。さらに、立ち下がり遷移では (VIL - 60mV)<sup>(3)</sup> を下回るまで低下し、次の立ち上がり遷移まで (VIL - 60mV)<sup>(3)</sup> を下回った状態を維持していることを確認してください。</li> <li>CLK 信号は、(VIL - 60mV)<sup>(3)</sup> から (VIH + 60mV)<sup>(3)</sup> の電圧領域では、非単調となる場合があります。<a href="#">図 3-7</a> の例を参照してください。</li> <li>CLK 信号は、(VIL - 60mV)<sup>(3)</sup> から (VIH + 60mV)<sup>(3)</sup> の間の電圧領域において、非単調であってはなりません。<a href="#">図 3-8</a> の例を参照してください。</li> </ul> | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>シミュレーションされた DAT 信号の立ち上がり遷移が VIH を超えて上昇し、立ち下がり遷移が VIL を下回ること、また「セットアップ時間 / ホールド時間の合否判定チェック」で上記に説明したセットアップ試験に合格できる十分なタイミング マージンが確保されていることを確認します。</li> <li>シミュレーションされた DAT 信号にリングバックがある場合、上記のセットアップ時間計算で使用する最も遅い DAT 信号のスルー成分は、立ち上がり遷移では (VIH + 60mV)<sup>(3)</sup> を上回る最後の交差点から、立ち下がり遷移では (VIL - 60mV)<sup>(3)</sup> を下回る最後の交差点から測定する必要があります。</li> <li>リングバックを伴う立ち上がり DAT 信号におけるスルー測定の例を <a href="#">図 3-9</a> に、リングングを伴う立ち下がり DAT 信号における例を <a href="#">図 3-10</a> に示しています</li> </ul> | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>シミュレーションされた CMD 信号の立ち上がり遷移が VIH を超えて上昇し、立ち下がり遷移が VIL を下回ること、また「セットアップ時間 / ホールド時間の合否判定チェック」で上記に説明したセットアップ試験に合格できる十分なタイミング マージンが確保されていることを確認します。</li> <li>シミュレーションされた CMD 信号にリングバックがある場合、上記のセットアップ時間計算で使用する最も遅い CMD 信号のスルー成分は、立ち上がり遷移では (VIH + 60mV)<sup>(3)</sup> を上回る最後の交差点から、立ち下がり遷移では (VIL - 60mV)<sup>(3)</sup> を下回る最後の交差点から測定する必要があります。</li> <li>リングバックを伴う立ち上がり CMD 信号におけるスルー測定の例を <a href="#">図 3-9</a> に、リングングを伴う立ち下がり CMD 信号における例を <a href="#">図 3-10</a> に示しています</li> </ul> |

表 3-5. 合格 / 不合格チェック (続き)

| パラメータ  | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CMD                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| スルーレート | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>接続されている eMMC デバイスにおいて、立ち上がり遷移時に <math>VIL</math> から <math>VIH</math> まで、および立ち下がり遷移時に <math>VIH</math> から <math>VIL</math> まで測定したシミュレーション済み CLK 信号のスルーレートが、最小スルーレート要件である <b>1.45V/ns</b> (JESD84-B51 に定義されているスルーレート <math>1.125V/ns</math> に対し、IBIS シミュレーション<sup>(3)</sup>向けに 30% の追加マージンを適用した値) 以上であることを確認します</li> <li>「JESD84-B51 表 215 - HS400 デバイスの入力タイミング」の「入力 CLK スルーレート」を参照してください。</li> <li>立ち上がりの CLK 信号については図 3-11 に、立ち下がりの CLK 信号については図 3-12 に、スルーレートが合格となる例および不合格となる例を示しています</li> </ul> | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>接続されている eMMC デバイスにおいて、立ち上がり遷移時に <math>VIL</math> から <math>VIH</math> まで、および立ち下がり遷移時に <math>VIH</math> から <math>VIL</math> まで測定したシミュレーション済み DAT 信号のスルーレートが、最小スルーレート要件である <b>1.45V/ns</b> (JESD84-B51 に定義されているスルーレート <math>1.125V/ns</math> に対し、IBIS シミュレーション<sup>(3)</sup>向けに 30% の追加マージンを適用した値) 以上であることを確認します</li> <li>シミュレーションされた DAT 信号にリングバックがある場合、接続されている eMMC デバイスにおいて、立ち上がり遷移時に <math>VIL</math> から (<math>VIH</math> <math>+60mV</math>)<sup>(3)</sup> まで、また立ち下がり遷移時に <math>VIH</math> から (<math>VIL</math> <math>-60mV</math>)<sup>(3)</sup> まで測定した DAT 信号のスルーレートが、最小スルーレート要件である <b>1.45V/ns</b> (JESD84-B51 に定義されているスルーレート <math>1.125V/ns</math> に対し、IBIS シミュレーション向けに 30% の追加マージンを適用した値<sup>(3)</sup>) 以上であることを確認してください。</li> <li>「JESD84-B51 表 215 - HS400 デバイスの入力タイミング」の「入力 DAT スルーレート」を参照してください。</li> <li>立ち上がりの DAT 信号については図 3-13 に、立ち下がりの DAT 信号については図 3-14 に、スルーレートが合格となる例および不合格となる例を示しています</li> <li>リングバックを伴う DAT 信号について、立ち上がり遷移のスルーレートが合格および不合格となる例を図 3-15 に示し、リングバックを伴う DAT 信号について、立ち下がり遷移のスルーレートが合格および不合格となる例を図 3-16 に示しています。</li> </ul> | <ul style="list-style-type: none"> <li>該当なし</li> </ul> |

表 3-5. 合格 / 不合格チェック (続き)

| パラメータ | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | データ                                                    | CMD                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| DCD   | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>全体マージン <math>G</math> は、<math>G = A - B - C - D - E - F</math> として算出します。十分なマージンがあるかどうかを判断するため、最悪条件でシミュレーションされた CLK 信号のデューティサイクル歪みの測定値 (B) から、以下の値を差し引きます:           <ul style="list-style-type: none"> <li>A: JESD84-B51 仕様 (tCKDCD 最大 300ps)</li> <li>B: IBIS シミュレーションによる DCD の測定値 - JESD84-B51 の図 88 - HS400 デバイスデータ入力タイミングに示されている tCKDCD のタイミング定義を参照してください。<a href="#">セクション 3.5.4</a> も参照してください</li> <li>C: DCD の IBIS/SPICE 相関からの調整 (39ps)<sup>(3)</sup></li> <li>D: ベータプロセス (SF/FS) コーナーからの調整 (8ps)</li> <li>E: CLK ツリーと PHY レベルシフタの影響 (42ps)</li> <li>F: PLL ジッタの影響 (61ps)</li> </ul> </li> <li>これらの値を測定した DCD から差し引いた後、全体マージン (<math>G</math>) が正の値である必要があり、これを満たせば合格です</li> <li>「JESD84-B51 表 215 - HS400 デバイスの入力タイミング」および「図 88 - HS400 デバイスのデータ入力タイミング」の tCKDCD タイミングを参照してください。<a href="#">図 3-17</a> も参照してください</li> </ul> | <ul style="list-style-type: none"> <li>該当なし</li> </ul> | <ul style="list-style-type: none"> <li>該当なし</li> </ul> |

表 3-5. 合格 / 不合格チェック (続き)

| パラメータ | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | データ                                                    | CMD                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| パルス幅  | <ul style="list-style-type: none"> <li>電源非考慮モードで IBIS モデルを用いたシミュレーションを実行し、結果をプロファイルします</li> <li>全体マージン <math>G</math> は、<math>G = B - A - C - D - E - F</math> として算出します。十分なマージンがあるかどうかを判断するため、最悪条件でシミュレーションされた CLK パルス幅の測定値 (B) から、以下の値を差し引きます: <ul style="list-style-type: none"> <li>B:IBIS シミュレーションのパルス幅 -「JESD84-B51、図 88 - HS400 デバイス データ入力タイミング」の tCKMPW タイミングの定義を参照してください。セクション 3.5.4 も参照してください</li> <li>A: JESD84-B51 仕様 (最小 tCKMPW: 2.2ns)</li> <li>C:パルス幅に対する IBIS/SPICE 相関に基づく調整値 (39ps)<sup>(3)</sup></li> <li>D:ベータ プロセス (SF/FS) コーナーからの調整 (8ps)</li> <li>E:CLK ツリーと PHY レベルシフタの影響 (42ps)</li> <li>F:PLL ジッタの影響 (61ps)</li> <li>これらの値を測定したパルス幅から差し引いた後、全体マージン (G) が正の値である必要があり、これを満たせば合格です</li> </ul> </li> <li>「JESD84-B51 表 215 - HS400 デバイスの入力タイミング」および「図 88 - HS400 デバイスのデータ入力タイミング」の tCKMPW タイミングを参照してください。</li> <li>図 3-17 も参照してください</li> </ul> | <ul style="list-style-type: none"> <li>該当なし</li> </ul> | <ul style="list-style-type: none"> <li>該当なし</li> </ul> |

- (1) JEDEC HS400 仕様は、表 215 - HS400 デバイスの入力タイミング (eMMC JESD84-B51 セクション 10.10.1) を参照しています。

- (2) JEDEC HS200 仕様は、表 212 - HS200 デバイスの入力タイミング (eMMC JESD84-B51 セクション 10.8.2) を参照しています。

- (3) IBIS シミュレーションの結果は、IBIS/SPICE 相関に基づく調整が必要です (IBIS シミュレーションの結果は、SPICE シミュレーションの結果と比較して楽観的であるためです)。

- (4) セットアップ時間およびホールド時間の計算では、VCC/2 と VIL/VIH の間における最も遅い信号スルーフィルタを差し引く必要があります。これは、TI データシートでは、これらのパラメータのタイミング基準が DAT または CMD 信号遷移の VCC/2 から CLK 信号遷移の VCC/2 までとして定義されている一方、JESD84-B51 では、DAT または CMD 信号遷移の VIL または VIH から CLK 信号遷移の VCC/2 までをセットアップ時間の基準として定義しているためです。

図 3-3. セットアップ / ホールド時間: CLK に対する DATA のオフセット (1/4 CLK サイクル遅延)

図 3-4. セットアップ / ホールド時間: CLK に対する CMD のオフセット ( $1/4$  CLK サイクル + 400ps の遅延)

図 3-5. セットアップ / ホールド時間: 最も遅い DATn/CMD の立ち上がりエッジにおけるスルーは、セットアップ時は VCC/2 から VIH まで、ホールド時は VIL から VCC/2 まで

図 3-6. セットアップ / ホールド時間: 最も遅い DATn/CMD の立ち下がりエッジにおけるスルーは、セットアップ時は VCC/2 から VIL まで、ホールド時は VIH から VCC/2 まで

図 3-7. VIH/VIL: 非単調な CLK の良好な例 ( $V_{IL} - 60mV$ ) から ( $V_{IH} + 60mV$ ) の範囲内では単調

図 3-8. VIH/VIL: 非単調な CLK の不適切な例 (VIL -60mV) から (VIH +60mV) の範囲内で非単調

図 3-9. VIH/VIL: リングバックを伴う DATn/CMD の最も遅い立ち上がりエッジのスルー (次のキャプチャ用 CLK エッジの前における最後の (VIH +60mV) 交差点まで測定)

図 3-10. VIH/VIL: リングバックを伴う DATn/CMD の最も遅い立ち下がりエッジのスルー (次のキャプチャ用 CLK エッジの前における最後の (VIL -60mV) 交差点まで測定)

図 3-11. スルーレート:CLK の立ち上がりエッジ - VIL から VIH の間におけるスルーレートは 1.45V/ns より速い必要があります

図 3-12. スルーレート:CLK の立ち下がりエッジ - VIH から VIL の間におけるスルーレートは、1.45V/ns より速い必要があります

図 3-13. スルーレート: DATn/CMD の立ち上がりエッジ - VIL から VIH の間におけるスルーレートは、1.45V/ns より速い必要があります

図 3-14. スルーレート: DATn/CMD の立ち上がりエッジ - VIH から VIL の間におけるスルーレートは、1.45V/ns より速い必要があります

図 3-15. スルーレート: リングバックを伴う DATn/CMD の立ち上がりエッジ - VIL から (VIH +60mV) の間におけるスルーレートは、1.45V/ns より速い必要があります

図 3-16. スルーレート: リングバックを伴う DATn/CMD の立ち下がりスルー - VIH から (VIL -60mV) の間におけるスルーレートは、1.45V/ns より高速である必要があります

図 3-17. DCD およびパルス幅の測定におけるパルス幅の測定方法

注

VCC/2 は、シミュレーションしている TT、SS、FF の各コーナーにおける IO 電圧に応じてスケーリングされます。

## 4 設計例

このセクションは、SK-AM62P-LP (PROC164E2) に実装されているスタックアップ、電力配線、信号配線について説明しています。この設計は TI によってシミュレーションされており、セクション 3.5.5 に記載された合否判定チェックに対して十分な正のマージンがあることが確認されています。このデザインは、AM62Px eMMC 設計のベースライン リファレンスとして使用できます。

### 4.1 スタックアップ

これらのガイドラインでは、デバイスの仕様をフルに活用するために、10 層または 12 層の PCB スタックアップを推奨しています。SK-AM62P-LP (PROC164E2) で使用された 12 層のスタックアップ例を以下に示します：

**表 4-1. 12 層 PCB スタックアップの例**

| 層の番号 | スタックアップ          | ルーティング プランの最優先度とレイヤ                                                                     |

|------|------------------|-----------------------------------------------------------------------------------------|

|      | 半田マスク            |                                                                                         |

| 1    | TOP - PWR/SIG    | PMIC、SoC、eMMC デバイスと BGA ブレークアウト、GND                                                     |

| 2    | GND              | REF                                                                                     |

| 3    | PWR/SIG          | eMMC 信号、LPDDR4 データ信号、VDDA_1V8、GND、および LVCMOS エスケープ                                      |

| 4    | GND              | REF                                                                                     |

| 5    | SIG/GND          | GND、LPDDR データ信号、LVCMOS エスケープ                                                            |

| 6    | GND              | REF                                                                                     |

| 7    | PWR              | VCC1V8_SYS (PMIC の L4 インダクタから eMMC デバイス直下のビアまでの eMMC 電源)、VDD_CORE、VDD_LPDDR4、DVDD_3V3   |

| 8    | PWR/GND          | DVDD_1V8 (SoC 領域の VDDS_MMCO 電源から VDDS_MMCO ピンの下のビア)、VDD1_LPDDR4_1V8、GND、VDDA_x          |

| 9    | PWR/GND          | DVDD_1V8 (PMIC の L4 インダクタから SoC 領域へ供給される VDDS_MMCO 電源)、GND、VDDR_CORE、VDDA_1V8、DVDD_3V3、 |

| 10   | SIG/GND          | GND、LPDDR CA 信号、LVCMOS エスケープ                                                            |

| 11   | GND              | REF                                                                                     |

| 12   | BOTTOM - SIG/PWR | eMMC CLK 用直列終端抵抗 (SoC の近く)、eMMC DS 用直列終端 (eMMC の近く)、デカップリング コンデンサ、LVCMOS エスケープ、GND      |

|      | 半田マスク            |                                                                                         |

### 4.2 電力ルーティング

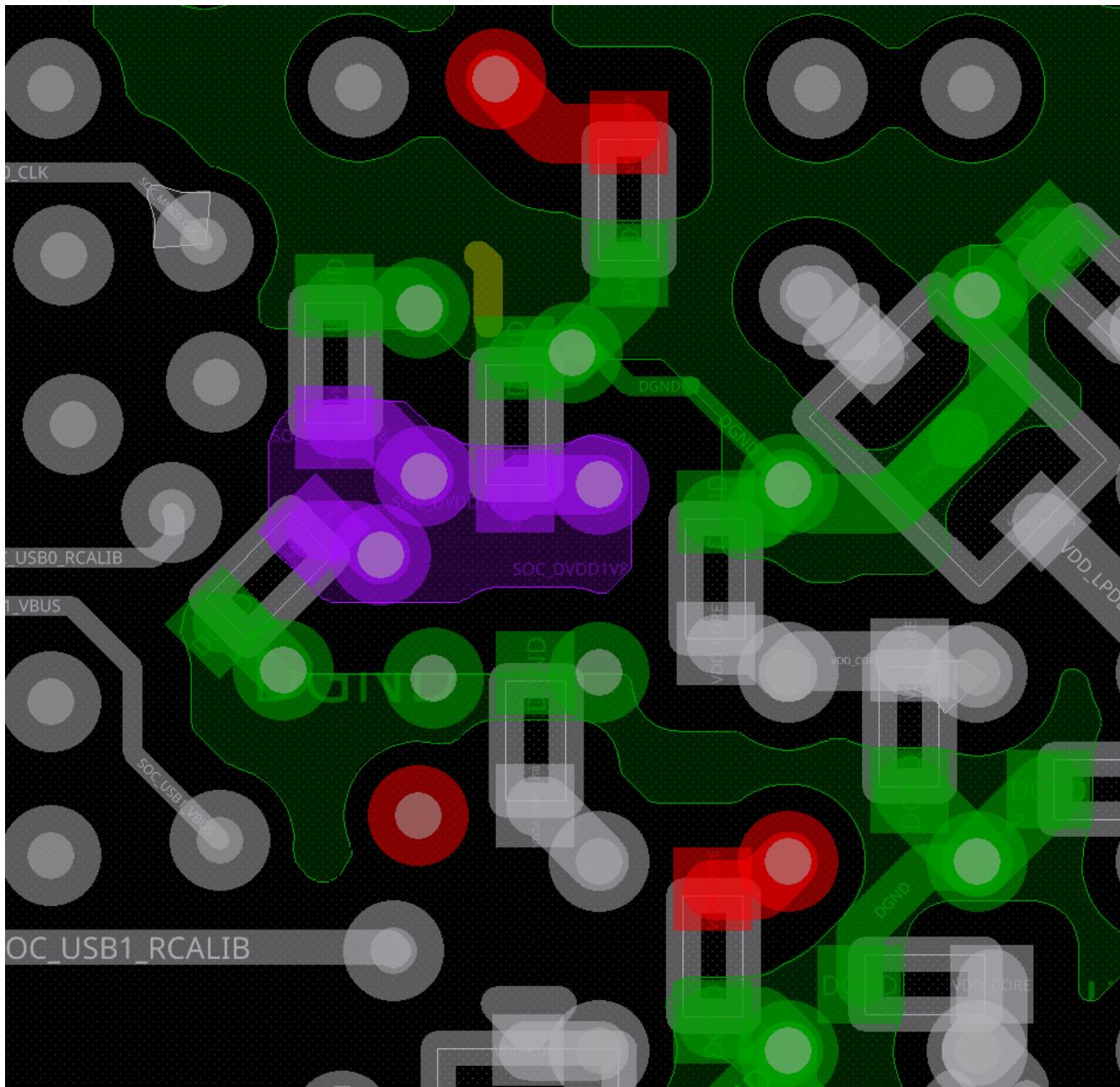

図 4-1 の 2D レイアウトと 3D レイアウト表では、図 4-2 SK-AM62P-LP (PROC164E2) に実装された VDDS\_MMCO 電源の配線を示します。

AM62Px の eMMC PHY 電源 VDDS\_MMCO 用 1.8V 電源レールと eMMC IO 電源は、いずれも PMIC のスイッチング レギュレータに接続された共通のインダクタから供給されます。SoC の電源を eMMC とは独立して測定できるようにするため、VCC1V8\_SYS 電源はシャント抵抗を通過し、VDDS\_MMCO 電源および他の SoC 電源ピンに到達する前に SoC\_DVDD1V8 となります。

2D レイアウトでは各形状に使用されている層が示されており、3D レイアウト表示では層間遷移に使用されているビアが明確に示されています。2 層、4 層、6 層、11 層には連続した GND プレーンが存在します。

このレイアウトは、シミュレーションによって電源ノイズ要件を十分なマージンをもって満たし、eMMC の JEDEC 規格に準拠していることが実証されています。VDDS\_MMCO 電源に隣接する層に全面 GND を配置すること、電源配線の層遷移を減らすこと、または層遷移間に追加のビアを設けることといったさらなる改善は、AC インピーダンス特性の向上に寄与し、信号整合マージンを改善する効果が期待されます。基板設計者には、実現可能な範囲で最善の PCB を設計することが推奨されます。

図 4-1. SK-AM62P-LP (PROC164E2) の eMMC 電源配線 2D レイアウト - VCC1V8\_SYS (白) および SoC\_DVDD1V8 (紫)

図 4-2. SK-AM62P-LP (PROC164E2) の eMMC 電源配線 3D レイアウト - VCC1V8\_SYS (白) および SoC\_DVDD1V8 (紫)

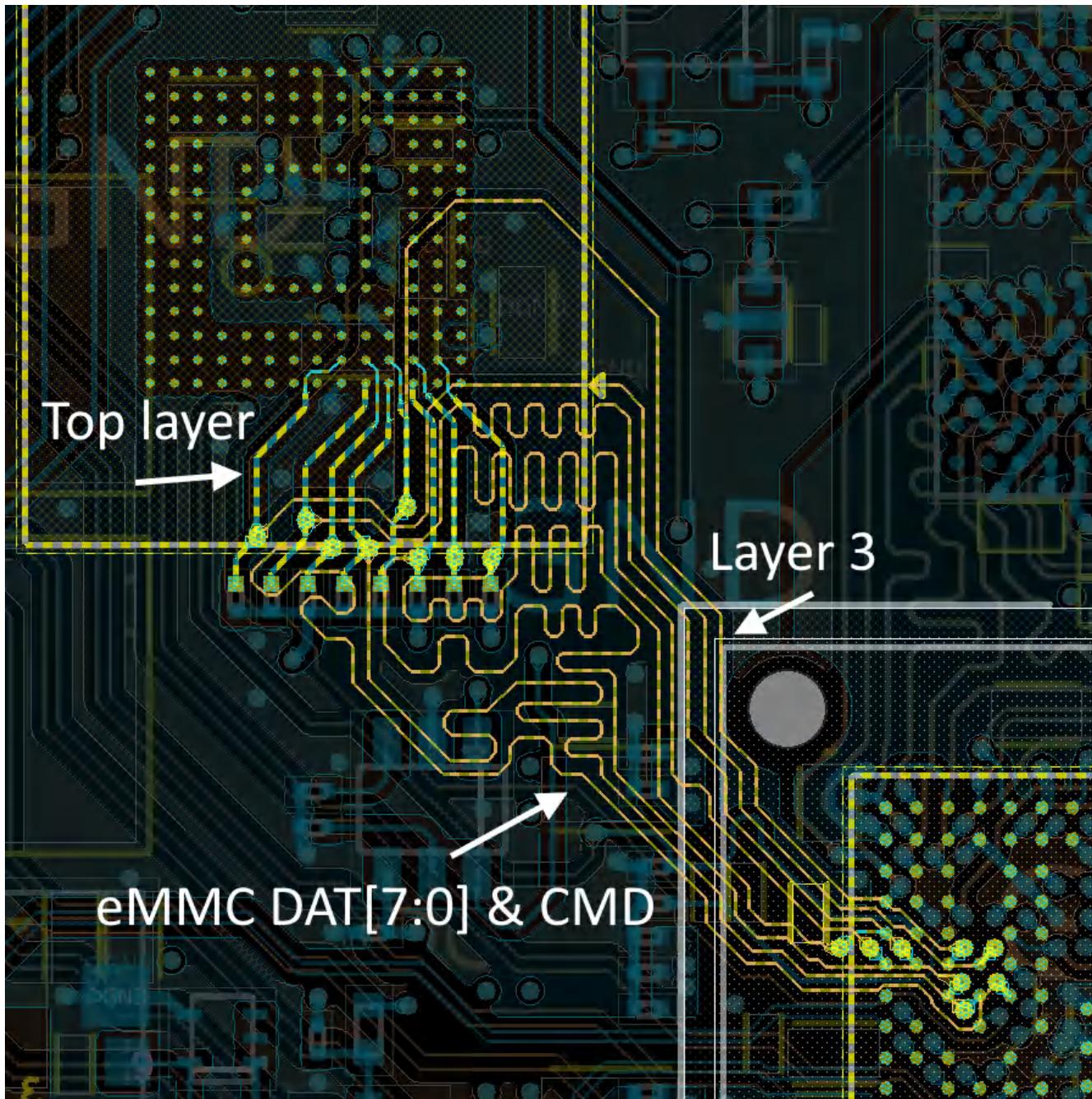

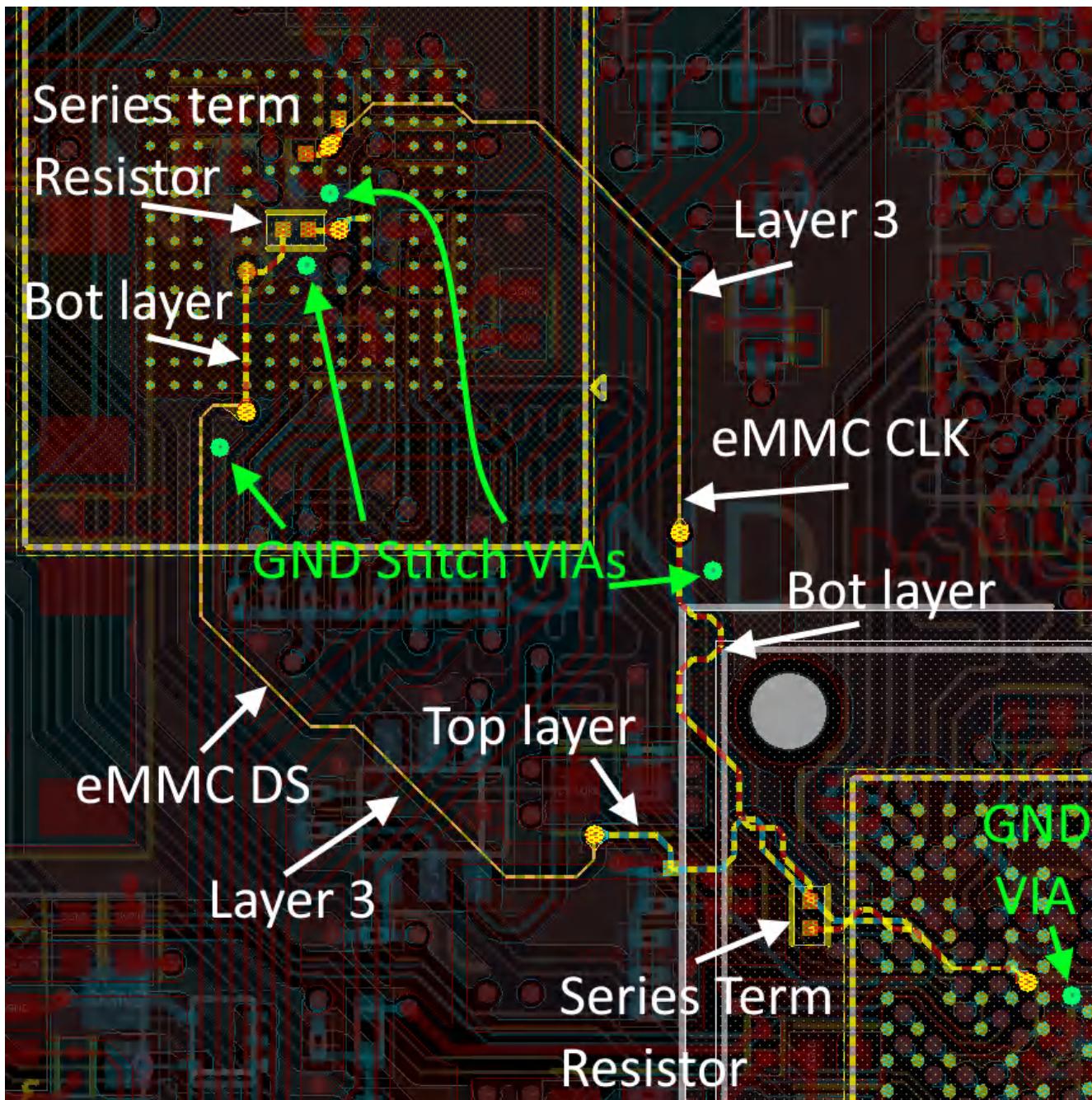

#### 4.3 信号の配線取り回し

以下の図 4-3 および図 4-4 に示す信号配線例は、SK-AM62P-LP (PROC164E2) の 12 層 PCB 設計において使用されている eMMC 信号配線を示しています。

eMMC の CMD および DAT [7:0] 信号は、目標インピーダンス  $50\Omega$  で、レイヤ 3 上に完全にストリップラインとして配線されています。

CLK は、SoC ピンから SoC 直下の最下層に配置された直列終端抵抗までを目標インピーダンス  $50\Omega$  で配線し、その後、目標インピーダンス  $50\Omega$  のままレイヤ 3 へ遷移しています。

DS は、eMMC ピンから eMMC デバイス直下の最下層に配置された直列終端抵抗までを目標インピーダンス  $50\Omega$  で配線し、その後、目標インピーダンス  $50\Omega$  のままレイヤ 3 へ遷移しています。

GND スティッチング ビアは、CLK および DS 信号が最下層の直列終端抵抗へ至るまで、ビアの両側において連続した GND 帰路を確保する役割を果たします。

このレイアウトは、上記で述べた合否チェックを十分なマージンをもって満たし、JEDEC 規格への準拠を示すことが、シミュレーションによって実証されています。

図 4-3. SK-AM62P-LP (PROC164E2) の eMMC 信号配線 - CMD と DAT [7:0]

図 4-4. SK-AM62P-LP (PROC164E2) eMMC 信号ルーティング - CLK と DS

表 4-2. eMMC ト雷斯のインピーダンスの概要例

| 基板面 | 信号                                                       | シングル エンド インピーダンス ( $\Omega$ ) |

|-----|----------------------------------------------------------|-------------------------------|

| L3  | eMMC CLK <sup>(1)</sup> 、CMD、DAT [7:0]、DS <sup>(1)</sup> | 49.87                         |

| L12 | eMMC CLK <sup>(1)</sup> 、DS <sup>(1)</sup>               | 50.13                         |

(1) CLK および DS は、直列終端抵抗のために L12 (最下層) へ遷移し、その後、残りの配線区間は L3 に戻って配線されています

## 5 まとめ

このアプリケーション レポートでは、AM62Px プロセッサの設計を使用して eMMC HS400 動作を成功させるために、PCB の計画、配線、シミュレーションを行う方法について説明します。内容には、ボードレイアウト ガイドライン、電源ノイズのチェック、合否判定基準を伴う IBIS シミュレーション、ならびに実際のボード設計例が含まれます。

## 6 参考資料

- テキサス インスツルメンツ、『[SK-AM62P-LP \(PROC164E2\)](#)』

- テキサス インスツルメンツ、『[eMMC データ攻撃ビット パターン](#)』

- テキサス インスツルメンツ、『[AM62Px Sitara™ プロセッサ 製品ページ](#)』

- テキサス インスツルメンツ、『[AM62Px Sitara™ プロセッサ データシート](#)』

- テキサス インスツルメンツ、『[EVM ユーザー ガイド: SK-AM62P-LP](#)』

- テキサス インスツルメンツ、『[AM62x, AM62Ax, AM62D-Q1, AM62Px プロセッサ ファミリ 回路設計ガイドラインおよびレビュー チェックリスト](#)』

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月