*Application Note***TPS61287 に最適化された MOSFET の選択**

Nathan Ding

### 概要

昇圧コンバータの性能、効率、信頼性において、適切なパワースイッチ（通常は MOSFET）を選択することは極めて重要です。不適切な選択は効率の低下や、貫通電流などの障害につながる可能性があります。このアプリケーションノートは、パワー MOSFET を選択するエンジニアを支援するための基本的なガイドラインです。各種 MOSFET パラメータがコンバータの動作に及ぼす影響と、専用の計算ツールについて説明します。ケーススタディとして、これらの選択ガイドラインと計算ツールの適用例を示します。

### 目次

|                                   |    |

|-----------------------------------|----|

| <b>1 概要</b>                       | 2  |

| <b>2 パワー MOSFET 選択における主要パラメータ</b> | 3  |

| 2.1 静的特性                          | 3  |

| 2.2 動的特性                          | 3  |

| 2.3 熱パラメータ                        | 5  |

| <b>3 MOSFET 選択ツールの概要</b>          | 6  |

| 3.1 計算ツールへ MOSFET パラメータを入力する      | 6  |

| 3.2 結果の確認                         | 7  |

| <b>4 計算ツール MOSFET の選択例とベンチ評価</b>  | 8  |

| <b>5 まとめ</b>                      | 10 |

| <b>6 参考資料</b>                     | 10 |

| <b>7 改訂履歴</b>                     | 11 |

### 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 概要

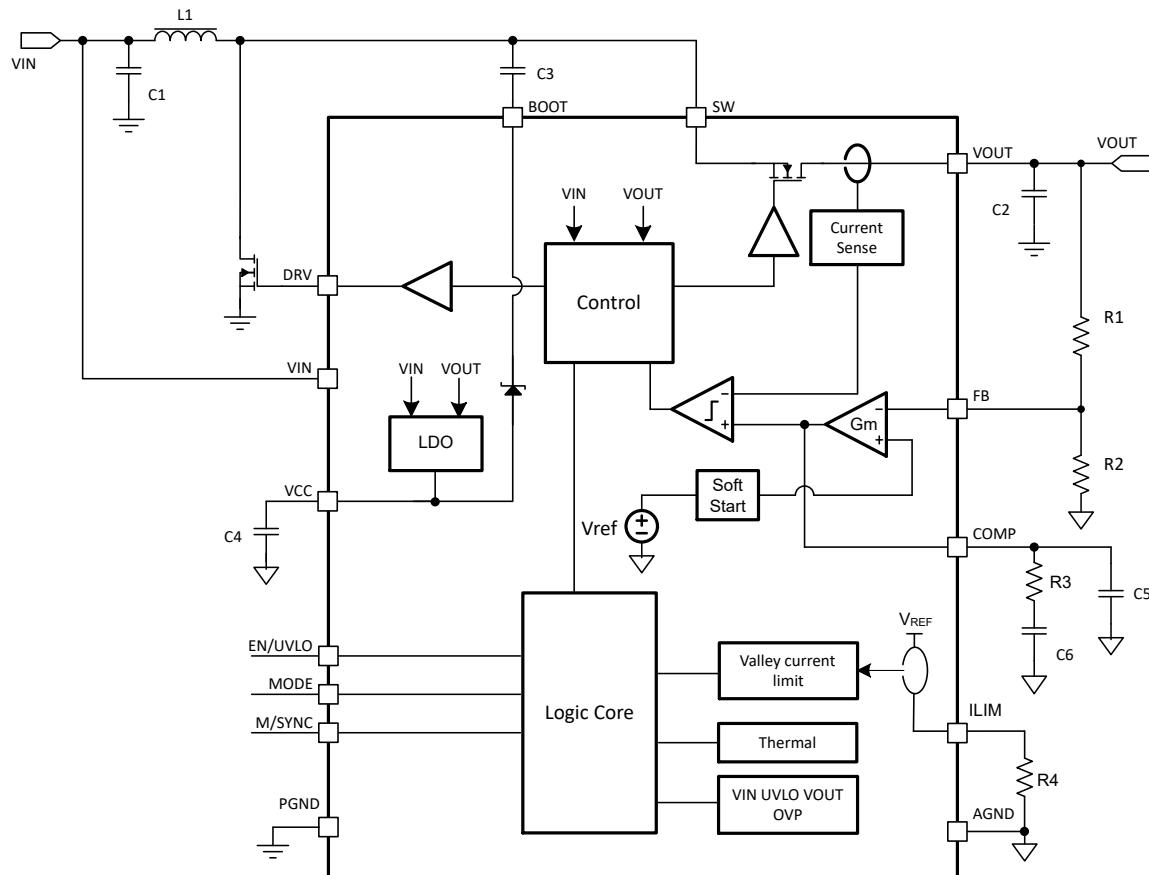

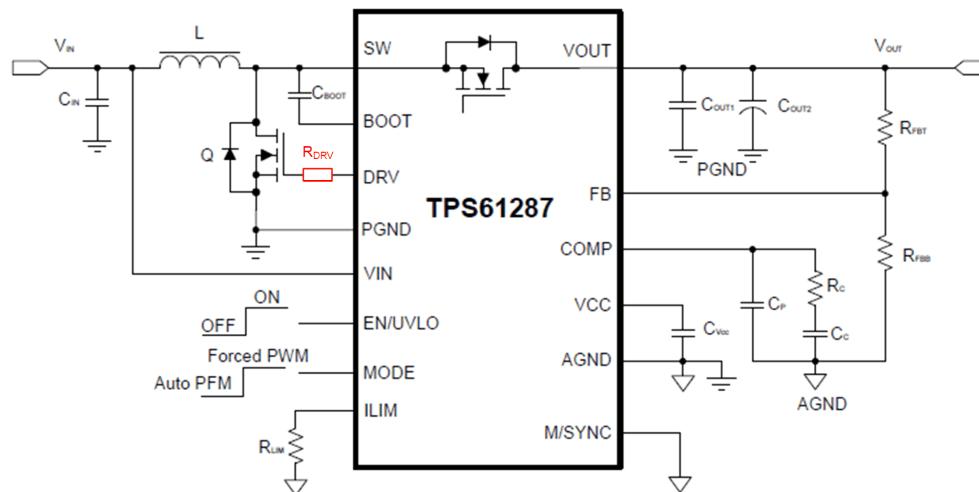

TPS61287 は、高電力密度の同期整流昇圧コンバータであり、ハイサイド同期整流 MOSFET を内蔵し、外付けローサイド MOSFET を使用して高効率で小型の設計を実現します。TPS61287 は、入力電圧範囲が 2V～23V と広く、出力電圧は最大 25V に対応し、20A のスイッチング バレー電流能力を備えています。TPS61287 は、適応型一定オン時間バレー電流制御トポロジを使用して、出力電圧をレギュレートします。TPS61287 は、中負荷～重負荷時には、パルス幅変調 (PWM) モードで動作します。軽負荷時には、MODE ピンの設定により 2 つのモードを選択できます。1 つは、軽負荷時の効率向上のための自動 PFM モードです。もう 1 つは、低いスイッチング周波数によって生じる可聴ノイズなどの問題を回避する強制 PWM モードです。PWM モードのスイッチング周波数は 320kHz です。TPS61287 には 27V の出力過電圧保護、サイクル単位の過電流保護、サーマル シャットダウン保護の機能が搭載されています。

図 1-1. TPS61287 の機能ブロック図

このアプリケーション ノートは、ブーストデバイス TPS61287 と組み合わせて使用する外付け MOSFET の選択についてのガイドです。

## 2 パワー MOSFET 選択における主要パラメータ

### 2.1 静的特性

通常、静的パラメータは、スイッチの絶対最大定格とオン状態性能を定義します。

- ドレン - ソース間電圧 ( $V_{DSS}$ ):これは、MOSFET で観測される最大電圧よりも高い定格が必要です。昇圧コンバータの場合、これは少なくとも最大出力電圧 ( $V_{OUT}$ ) です。寄生インダクタンスに起因する電圧スパイクを考慮するため、30 ~ 50% の安全マージンを推奨します。

- 連続ドレン電流 ( $I_D$ ):MOSFET は、RMS 入力電流と平均入力電流に対応する必要があります。昇圧コンバータの RMS 電流は、入力電流 ( $I_{IN}$ ) とほぼ等しくなります。

- オン抵抗 ( $R_{DS(on)}$ ):このパラメータは、導通損失 ( $P_{cond} = I_{RMS}^2 \times R_{DS(on)}$ ) を直接決定します。 $R_{DS(on)}$  が小さいことが望ましいですが、多くの場合、ゲート電荷が大きいほどトレードオフになります。

- ゲートレスショルド電圧 ( $V_{GS(th)}$ )、ゲートプラトー電圧 ( $V_{plateau}$ ) またはミラー電圧 ( $V_{miller}$ )。これら二つの電圧は、MOSFET が完全にオンになるように、MOSFET のゲート駆動電圧よりも低い必要があります。

### 2.2 動的特性

動的パラメータは、スイッチング速度およびゲートドライバに必要なエネルギーに関連しています。

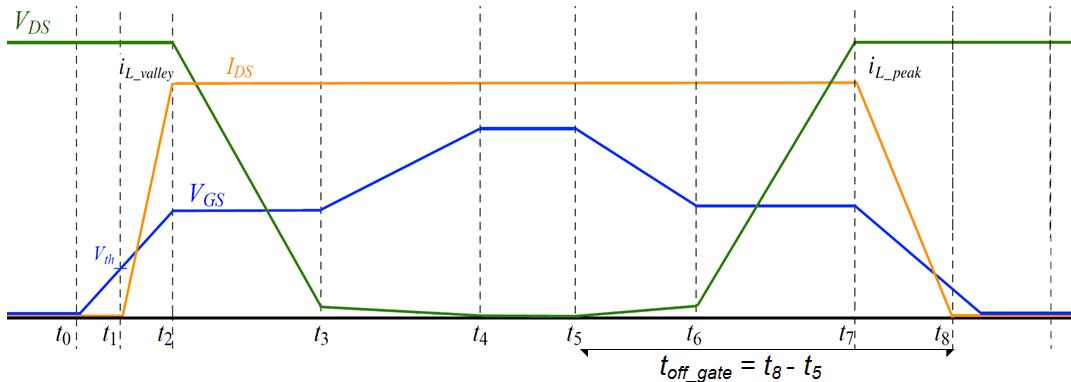

MOSFET の固有容量 ( $C_{ISS}$ ,  $C_{OSS}$ ,  $C_{RSS}$ ) によって、スイッチング動作が決まります。図 2-1 は、通常の昇圧デバイスローサイド MOSFET のスイッチングプロセスを示し、これらのコンデンサの役割について説明しています。

図 2-1. MOSFET のスイッチング波形

容量がスイッチング速度に与える影響:MOSFET がオンになるとき、ゲートドライバは MOSFET を最初にオンにするために  $C_{ISS}$  (入力容量) を充電し ( $t_0$  から  $t_2$ )、その後で MOSFET をオンにする必要があります。 $V_{GS}$  がプラトー電圧に達すると、ドライバ電流が  $C_{RSS}$  を放電するために消費され、これにより  $V_{DS}$  が低下します ( $t_2$  から  $t_3$ )。総ゲート電荷 ( $Q_g$ ) と容量が大きい場合は、スイッチングにより大きな駆動電流と時間が必要になります。

通常、静電容量が大きいと、次の二つの悪影響が生じます。

- スイッチング損失の増加:スイッチング遷移が遅いと、高電圧と大電流のオーバーラップ時間 ( $t_1$  から  $t_3$ ,  $t_6$  から  $t_8$  図 2-1) が長くなり、スイッチング損失 ( $P_{sw}$ ) が高くなり、効率が低くなります。

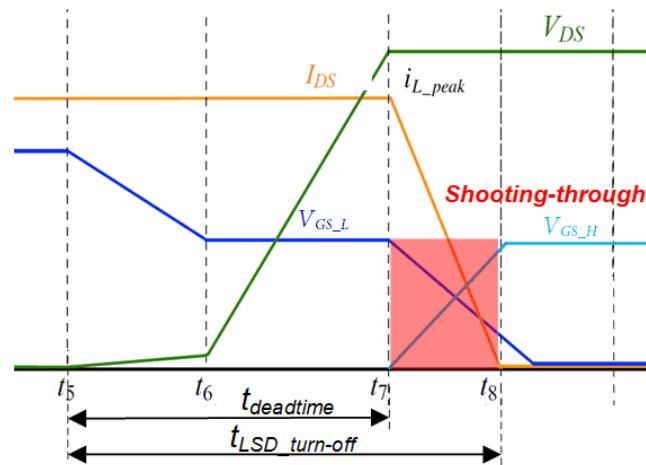

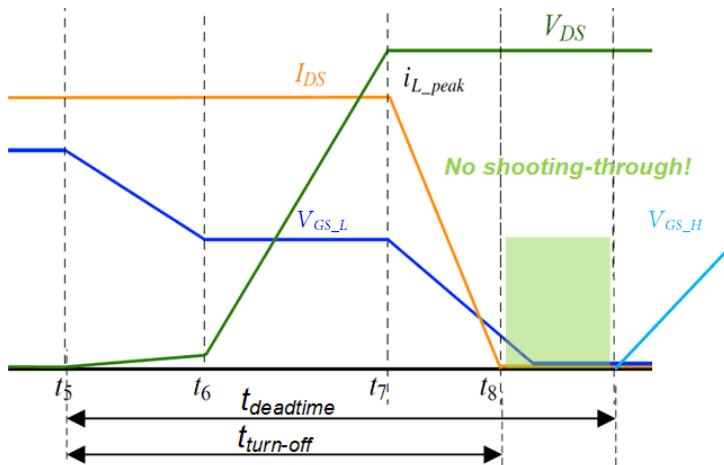

- 貫通電流のリスク:スイッチのターンオフが遅すぎると、ハイサイドとローサイドの両方のスイッチが同時にオンになるのを防ぐ十分な時間はありません。この貫通電流条件により、出力電圧レール全体に短絡が発生し、MOSFET と昇圧コントローラが破損するリスクが高くなります。

デッドタイムが調整可能なコントローラの場合、貫通電流を防止するために、スイッチのターンオフ遅延と立ち下がり時間の合計よりも長い時間デッドタイムを設定する必要があります。TPS61287 のような固定デッドタイムを持つコントローラの場合は、スイッチング時間が固定デッドタイムよりも短くなるように、選択した MOSFET の  $Q_g$  または接合部容量を十分に小さくする必要があります。

図 2-2. 動的特性が低いスイッチング動作

図 2-3. 優れた動的特性を持つスイッチング動作

図 2-2 および 図 2-3 は、高い動的パラメータがスイッチング速度と貫通電流のリスクに悪影響を及ぼすことを明確に示しています。

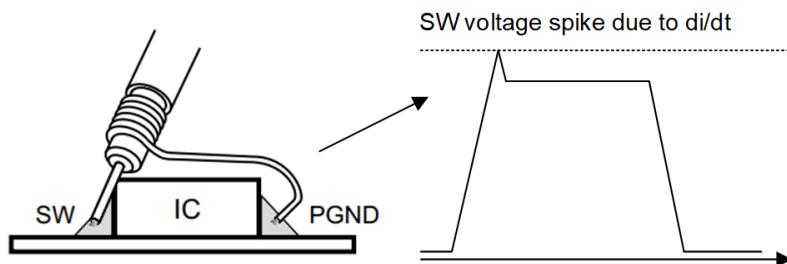

しかし、MOSFET の接合部容量は最大限小さくなつてはいません。接合部容量が小さすぎると、スイッチング速度が速すぎて、SW 電圧スパイク (ナノ秒レベルの過渡電圧) が増加し、MOSFET とチップの過電圧ストレスが発生する可能性があります。TPS61287 を安全に使用するため、テキサス・インスツルメントでは、SW の電圧スパイクを 36V 未満に制御することを推奨します。

図 2-4. 低インダクタンスプローブによる SW 電圧スパイク測定

接合部容量が非常に小さい MOSFET を選択したために、SW 電圧スパイクが大きすぎる場合は、駆動速度が遅くなり、SW 電圧スパイクが低減するため、MOSFET のゲートに直列駆動抵抗 (RDRV) を接続することを推奨します。

図 2-5. 駆動速度を遅くし、SW の電圧スパイクを低減するためのゲートドライブ抵抗

## 2.3 热パラメータ

热管理機能により、スイッチの安全動作領域 (SOA) 内での動作を検証できます。

- 接合部から周囲への热抵抗 ( $R_{\theta JA}$ ):これは、与えられた消費電力に対する、接合部から周囲の空気への温度上昇を定義します。放熱の場合、低  $R_{\theta JA}$  (より優れたパッケージまたはヒートシンクによって達成) が重要です。

- 総消費電力 ( $P_D$ ):導通損失とスイッチング損失の合計。接合部温度は次のように計算できます:  $T_J = T_A + (P_D \times R_{\theta JA})$ 、ここで  $T_A$  は周囲温度です。 $T_J$  は、常に最大定格 (通常は 150°C または 175°C) 未満に維持する必要があります。

### 3 MOSFET 選択ツールの概要

TI の TPS61287 昇圧コントローラファミリの選定プロセスを簡単化できるように、Excel ベースの計算ツールを開発しました。計算ツールを使用するには[こちら](#)に移動します。

この計算ツールは、動作条件、BOM (部品表)、システム要件に関するユーザー入力を受け取り、電力損失と効率を推定することもできます。この計算ツールでは、逆回復損失などの他のソースからの電力損失は考慮されていないことに注意してください。効率カリキュレータは、ある FET と別の FET を比較するのに最適です。

この計算ツールには、ターンオフ時間を推定するためのローサイド MOSFET 選択セクションが含まれています。このセクションを使用して、適切な動的特性を持つ MOSFET を選択できます。

#### 3.1 計算ツールへ MOSFET パラメータを入力する

このセクションでは、適切な MOSFET を選択するために計算ツールの入力パラメータを取得する方法についてエンジニア向けに説明します。

最初にアプリケーションの仕様を入力し、 $V_{IN}$ (min/max)、 $V_{OUT}$ 、 $I_{OUT}$ 、スイッチング周波数、LC パラメータなどのパラメータを入力します。次に、図 3-1 に示すように、候補となる MOSFET を選択し、主要なパラメータを手動で入力します。

| Step 7: Low-Side MOSFET Selection                                                                    |         |

|------------------------------------------------------------------------------------------------------|---------|

| On-State resistance, $R_{DS(on)}$                                                                    | 7 mΩ    |

| Total gate charge, $Q_G$                                                                             | 9 nC    |

| Gate resistance, $R_G$                                                                               | 0.8 Ω   |

| External gate resistance on PCB, $R_{G\_PCB}$                                                        | 0 Ω     |

| Input capacitance at $V_{ds}=0V$ , $C_{iss\_0V}$                                                     | 2000 pF |

| Input capacitance at $V_{ds}=V_{out}$ , $C_{iss\_Vout}$                                              | 1800 pF |

| Output capacitance at $V_{ds}=0V$ , $C_{oss\_0V}$                                                    | 2200 pF |

| Output capacitance at $V_{ds}=V_{out}$ , $C_{oss\_Vout}$                                             | 500 pF  |

| Reverse transfer capacitance at $V_{ds}=0V$ , $C_{rss\_0V}$                                          | 450 pF  |

| Reverse transfer capacitance at $V_{ds}=V_{out}$ , $C_{rss\_Vout}$                                   | 40 pF   |

| Low side FET gate driving voltage, $V_{LS\_gate}$                                                    | 5.1 V   |

| Gate-Source Threshold Voltage, $V_{GS(TH)}$                                                          | 1.2 V   |

| Gate plateau voltage / miller voltage, $V_{plateau}$                                                 | 2.5 V   |

| LS-GATE off to HS-GATE on deadtime, $t_{DLH}$                                                        | 30.0 ns |

| Calculated low side gate turn off time, $t_{off\_gate}$ (should be smaller than deadtime $t_{DLH}$ ) | 19.2 ns |

図 3-1. 計算ツールへ MOSFET パラメータを入力する

設計カリキュレータの最初のパラメータは、オン状態抵抗 ( $R_{DS(on)}$ ) です。この計算ツールは、5.1V の駆動電圧での  $R_{DS(on)}$  を要求します。 $R_{DS(on)}$  は通常、データシートに電気的特性セクション、または  $V_{gs}$  と  $R_{DS(on)}$  をプロットしたグラフで記載されています。

総ゲート電荷量 ( $Q_G$ ) とは、MOSFET の実際のゲート電圧が駆動電圧と一致するように、ゲート容量をオンにするのに必要な電荷 (クーロン単位) を指します。これは、スイッチング電荷とは異なります。 $Q_G$  は通常、MOSFET のデータシートに記載されています。

内部ゲート抵抗  $R_G$  は、MOSFET のゲートと直列に接続された抵抗でモデル化でき、 $R_{G\_PCB}$  は PCB の銅のパターンまたは外部抵抗による外部ゲート抵抗です。

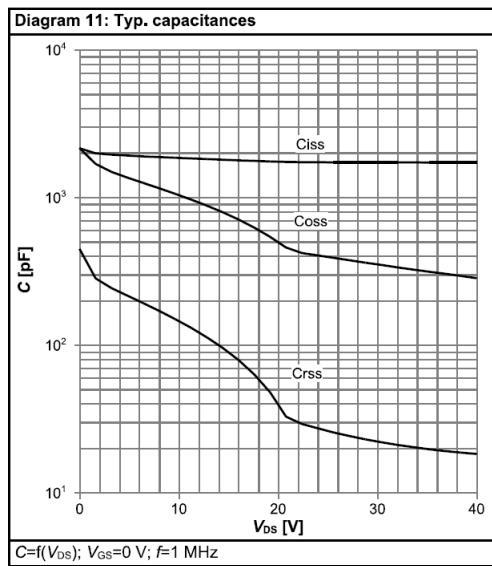

$C_{iss}$ 、 $C_{rss}$ 、 $C_{oss}$  は入力、逆方向、出力の接合部容量です。MOSFET の動的特性は主にドレインソース間電圧  $V_{DS}$  によって変化することに注意してください。図 3-2 は、 $V_{DS}$  の  $C_{iss}$ 、 $C_{rss}$ 、 $C_{oss}$  に依存していることを示しています。接合部容量は通常、 $V_{DS}$  と容量の関係をプロットしたグラフに示されます。

図 3-2. MOSFET の  $C_{iss}$ 、 $C_{rss}$ 、 $C_{oss}$  と  $V_{DS}$  との関係

ゲート—ソース間スレッショルド電圧  $V_{GSTH}$  は、MOSFET がオンになるスレッショルド電圧であり、ゲートプラトー電圧またはミラー電圧は  $C_{rss}$  が充電される電圧です。これら二つの電圧は通常、MOSFET のデータシートに記載されています。

### 3.2 結果の確認

このツールは以下の値を自動的に計算します：

- 使用条件に対する推奨 BOM です。

- ローサイドターンオフ時間の推定値がコントローラの固定デッドタイムに近づいた場合に警告します。

- 安定性を評価するためのボールドプロット、位相マージン、ゲインマージン。

- ローサイド MOSFET の電力損失の推定値、総消費電力、推定接合部温度と効率。

このツールの結果は理論による計算結果であることに注意してください。非線形の回路やコンポーネントによる影響は考慮されていません。この計算ツールは、さまざまな BOM (部品表) を比較するために使用するのが最適です。または、システムパラメータ設計の出発点を迅速に取得することができます。

## 4 計算ツール MOSFET の選択例とベンチ評価

このセクションでは、TPS61287 の設計で計算ツールを使用する方法を例示します。この例では、次の動作条件が使用されています。

他の入力パラメータはデフォルトのままにしてあります。

表 4-1. 設計カリキュレータの動作条件例

| パラメータ                  | 値   | 単位 |

|------------------------|-----|----|

| V <sub>IN</sub> (最小値)  | 3.0 | V  |

| V <sub>IN</sub> (公称値)  | 3.6 | V  |

| V <sub>IN</sub> (最大値)  | 4.2 | V  |

| V <sub>OUT</sub>       | 18  | V  |

| I <sub>OUT</sub> (最大値) | 2   | A  |

| I <sub>LIM</sub>       | 20  | A  |

| T <sub>A</sub>         | 25  | °C |

オプション A とオプション B の二つの MOSFET 候補があり、R<sub>DS(on)</sub> は同じですが、オプション A の接合部容量はオプション B よりも大きくなります。

黄色のセルを記入すると、計算ツールはローサイド MOSFET のターンオフ時間、電力損失、温度上昇、総効率を取得できます。

| Step 7: Low-Side MOSFET Selection                                                                                 |         |

|-------------------------------------------------------------------------------------------------------------------|---------|

| On-State resistance, R <sub>DS(on)</sub>                                                                          | 7 mΩ    |

| Total gate charge, Q <sub>G</sub>                                                                                 | 34 nC   |

| Gate resistance, R <sub>G</sub>                                                                                   | 0.9 Ω   |

| External gate resistance on PCB, R <sub>G_PCB</sub>                                                               | 0 Ω     |

| Input capacitance at V <sub>ds</sub> =0V, C <sub>iss_0V</sub>                                                     | 5000 pF |

| Input capacitance at V <sub>ds</sub> =V <sub>out</sub> , C <sub>iss_Vout</sub>                                    | 3527 pF |

| Output capacitance at V <sub>ds</sub> =0V, C <sub>oss_0V</sub>                                                    | 2000 pF |

| Output capacitance at V <sub>ds</sub> =V <sub>out</sub> , C <sub>oss_Vout</sub>                                   | 257 pF  |

| Reverse transfer capacitance at V <sub>ds</sub> =0V, C <sub>rss_0V</sub>                                          | 1500 pF |

| Reverse transfer capacitance at V <sub>ds</sub> =V <sub>out</sub> , C <sub>rss_Vout</sub>                         | 215 pF  |

| Low side FET gate driving voltage, V <sub>LS_gate</sub>                                                           | 5.1 V   |

| Gate-Source Threshold Voltage, V <sub>GS(th)</sub>                                                                | 2 V     |

| Gate plateau voltage / miller voltage, V <sub>plateau</sub>                                                       | 3 V     |

| LS-GATE off to HS-GATE on deadtime, t <sub>off_gate</sub>                                                         | 30.0 ns |

| Calculated low side gate turn off time, t <sub>off_gate</sub> (should be smaller than deadtime t <sub>off</sub> ) | 34.3 ns |

| Step 8: Efficiency Analyzer                                                                                    |           |

|----------------------------------------------------------------------------------------------------------------|-----------|

| Default EVM Inductor DC loss, P <sub>loss_inductor_DC</sub>                                                    | 931 mW    |

| Actually used inductor DC loss, P <sub>loss_act_inductor_DC</sub>                                              | 0 mW      |

| Default EVM Inductor AC loss, P <sub>loss_inductor_AC</sub>                                                    | 59 mW     |

| Actually used inductor AC loss, P <sub>loss_act_inductor_AC</sub>                                              | 0 mW      |

| Low-side MOSFET power loss, P <sub>loss_LS_FET</sub>                                                           | 1746 mW   |

| IC power loss, P <sub>loss_IC</sub>                                                                            | 1631 mW   |

| Low-side MOSFET Junction-to-ambient thermal resistance, R <sub>JA_FET</sub>                                    | 53 °C/W   |

| Low-side MOSFET junction temperature rise                                                                      | 92.5 °C   |

| IC Junction-to-ambient thermal resistance, R <sub>JA_IC</sub>                                                  | 36.6 °C/W |

| IC junction temperature rise                                                                                   | 59.7 °C   |

| Calculated efficiency on PWM@V <sub>IN</sub> (max), V <sub>OUT</sub> , I <sub>OUT</sub> (max), f <sub>sw</sub> | 89.2 %    |

図 4-1. オプション A の計算結果

| Step 7: Low-Side MOSFET Selection                                                                    |         |

|------------------------------------------------------------------------------------------------------|---------|

| On-State resistance, $R_{DS(on)}$                                                                    | 7 mΩ    |

| Total gate charge, $Q_g$                                                                             | 9 nC    |

| Gate resistance, $R_g$                                                                               | 0.8 Ω   |

| External gate resistance on PCB, $R_{g\_PCB}$                                                        | 0 Ω     |

| Input capacitance at $V_{ds}=0V$ , $C_{iss\_0V}$                                                     | 2000 pF |

| Input capacitance at $V_{ds}=V_{out}$ , $C_{iss\_Vout}$                                              | 1800 pF |

| Output capacitance at $V_{ds}=0V$ , $C_{oss\_0V}$                                                    | 2200 pF |

| Output capacitance at $V_{ds}=V_{out}$ , $C_{oss\_Vout}$                                             | 500 pF  |

| Reverse transfer capacitance at $V_{ds}=0V$ , $C_{rss\_0V}$                                          | 450 pF  |

| Reverse transfer capacitance at $V_{ds}=V_{out}$ , $C_{rss\_Vout}$                                   | 40 pF   |

| Low side FET gate driving voltage, $V_{LS\_gate}$                                                    | 5.1 V   |

| Gate-Source Threshold Voltage, $V_{GS(th)}$                                                          | 1.2 V   |

| Gate plateau voltage / miller voltage, $V_{plateau}$                                                 | 2.5 V   |

| LS-GATE off to HS-GATE on deadtime, $t_{DOL}$                                                        | 30.0 ns |

| Calculated low side gate turn off time, $t_{off\_gate}$ (should be smaller than deadtime $t_{DOL}$ ) | 19.2 ns |

| Step 8: Efficiency Analyzer                                                            |           |

|----------------------------------------------------------------------------------------|-----------|

| Default EVM Inductor DC loss, $P_{loss\_inductor\_DC}$                                 | 931 mW    |

| Actually used inductor DC loss, $P_{loss\_act\_inductor\_DC}$                          | 931 mW    |

| Default EVM Inductor AC loss, $P_{loss\_inductor\_AC}$                                 | 59 mW     |

| Actually used inductor AC loss, $P_{loss\_act\_inductor\_AC}$                          | 59 mW     |

| Low-side MOSFET power loss, $P_{loss\_LS\_FET}$                                        | 1023 mW   |

| IC power loss, $P_{loss\_IC}$                                                          | 1383 mW   |

| Low-side MOSFET Junction-to-ambient thermal resistance, $R_{JIA\_FET}$                 | 60 °C/W   |

| Low-side MOSFET junction temperature rise                                              | 61.4 °C   |

| IC Junction-to-ambient thermal resistance, $R_{JIA\_IC}$                               | 36.6 °C/W |

| IC junction temperature rise                                                           | 50.6 °C   |

| Calculated efficiency on PWM@ $V_{IN} = 3.0V$ ; $V_{OUT} = 1.8V$ ; $I_{OUT\_MAX} = 1A$ | 91.4 %    |

図 4-2. オプション B の計算結果

オプション A はオプション B よりも動的特性が悪いため、電力損失が大幅に大きくなり (オプション A では 1746mW、オプション B では 1023mW)、温度が高くなり (オプション A では 92.5°C、オプション B では 61.4°C)、効率が低下します (オプション A では 89.2%、オプション B では 91.4%)。

より重要な点として、オプション A のターンオフ時間は 34.3ns と計算されます。これは、LS-GATE オフから HS-GATE オンまでのデッドタイム (30ns) よりも長い時間です。貫通電流のリスクを考慮して、ここでは警告を示しています。オプション B ではターンオフ時間は 19.2ns で、デッドタイムよりもはるかに短いです。

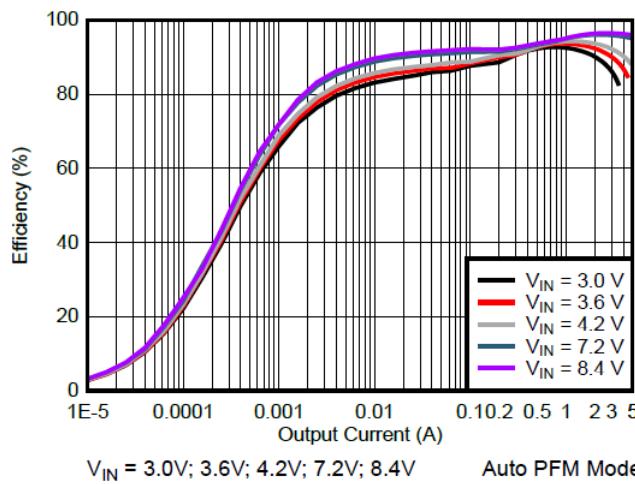

そのため、オプション B として、電力損失が小さく動的性能と熱要件の両方を満たすオプション B を選択しました。図 4-3 に、オプション B MOSFET を使用したベンチの効率曲線を示します。

図 4-3. オプション B MOSFET を使用した TPS61287 の効率曲線

## 5 まとめ

TPS61287 デバイスは、各種アプリケーション用の高効率な昇圧コンバータシステムを作成できます。これらのシステムの効率は、システムの動作条件と BOM の選択 (特に MOSFET の選択) に応じて変化します。MOSFET のデータシート パラメータを確認し、注意深く検討する必要があります。エンジニアは、MOSFET の電圧と電流定格が十分なマージンを確保してアプリケーション要件を上回っていることを検証する必要があります。重要なことに、動的パラメータ (特にゲート電荷や容量) は、スイッチング損失を最小化し、貫通電流を防止するために、コントローラのゲート駆動能力やデッドタイムと互換性を持っている必要があります。設計の信頼性を検証するには、熱計算が必須です。TI の TPS61287 デバイス向け計算ツールを活用すると、このプロセスを効率化でき、迅速で望ましい MOSFET を選択できるので、効率的で信頼性の高い昇圧設計につながります。

## 6 参考資料

1. テキサス・インスツルメンツ、[TPS61287 23V VIN, 25V VOUT 20A 同期整流昇圧コンバータ\(スタッカブルマルチフェーズ機能搭載\)](#)、データシート

2. テキサス・インスツルメンツ、[BQ2575x ファミリ向け MOSFET 選択ガイド](#)、アプリケーションノート。

3. テキサス・インスツルメンツ、『[MOSFET Support and Training Tools \(MOSFET サポートおよびトレーニングツール\)](#)』、アプリケーションノート。

4. テキサス・インスツルメンツ、SW ノードの絶対最大定格についてアプリケーションノート [SLVA494](#)

## 7 改訂履歴

### Changes from Revision \* (January 2026) to Revision A (February 2026)

|                                      | Page |

|--------------------------------------|------|

| • 計算ツールへのリンクを追加.....                 | 6    |

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... | 6    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月