## Technical Article

# 精密設計による差別化を実現する差動信号の活用

Jason Clark, Rachel Scheller

業界最新の高分解能、高精度 A/D コンバータ (ADC) は、差動入力を実装して性能を最大化しています。しかし、多くの設計者は、慣れ親しんだシングルエンドアンプを今でも選択しています。ただし、完全差動アンプ (FDA) は、精度を犠牲にせずに、多くのシステムにおける利点をもたらします。この記事では、完全差動アンプの多くの利点を実現する方法例として、2025 THS4536 超高精度、低ノイズ 80MHz FDA を使用します。

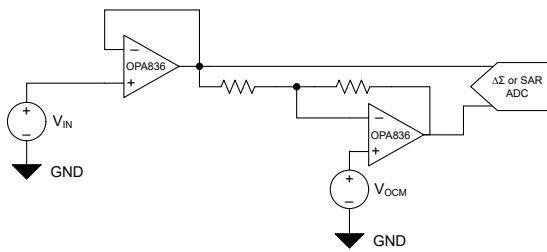

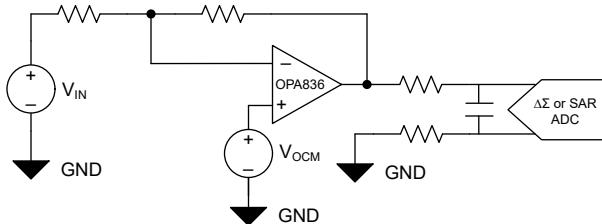

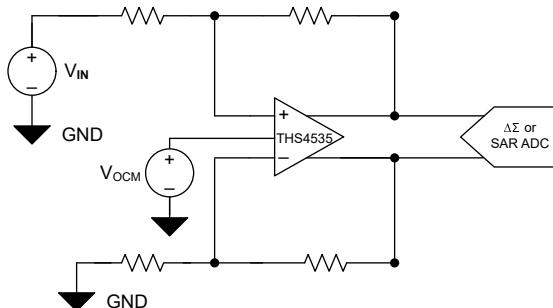

FDA は、直流 (DC) 結合により、シングルエンドから差動信号へのシンプルな変換を可能にします。図 1 から図 3 に、ADC の差動入力でシングルエンド信号を駆動する 3 つの異なる例を示します。FDA は低消費電力、低ノイズ、ダイナミックレンジの改善、回路上のその他の利点をすべて兼ね備えており、シグナル チェーン全体の簡素化を実現します。

図 1. デュアル オペアンプを使用した ADC 駆動

図 2. 疑似差動入力を使用した ADC 駆動

図 3. 完全差動アンプを使用した ADC 駆動

FDA アーキテクチャは、 $\text{HD}_2$  を低減することで全高調波歪み (THD) を大幅に低減することができます。図 3 に示す FDA 方式を実装すると、全体のシステム性能が向上したり、同じ THD を満たすために低消費電力または低帯域幅のアンプを柔軟に使用したりできます。

THD の低減に加えて、単一の FDA (図 3) はもも有しています  $\frac{1}{\sqrt{2}}$  は 1 対のシングルエンド オペアンプよりも同じ電力でのノイズが低くなります (図 1)。たとえば、入力電圧ノイズが  $4\text{nV}/\sqrt{\text{Hz}}$  のオペアンプでは、合計入力電圧ノイズはになります  $4\sqrt{2}$  デュアル オペアンプ回路構成で  $\text{nV}/\sqrt{\text{Hz}}$  です。入力電圧ノイズも約  $4\text{nV}/\sqrt{\text{Hz}}$  である THS4536 などの完全差動アンプと比較して、1 つのデバイスしかないため、入力電圧ノイズは FDA と等価です。

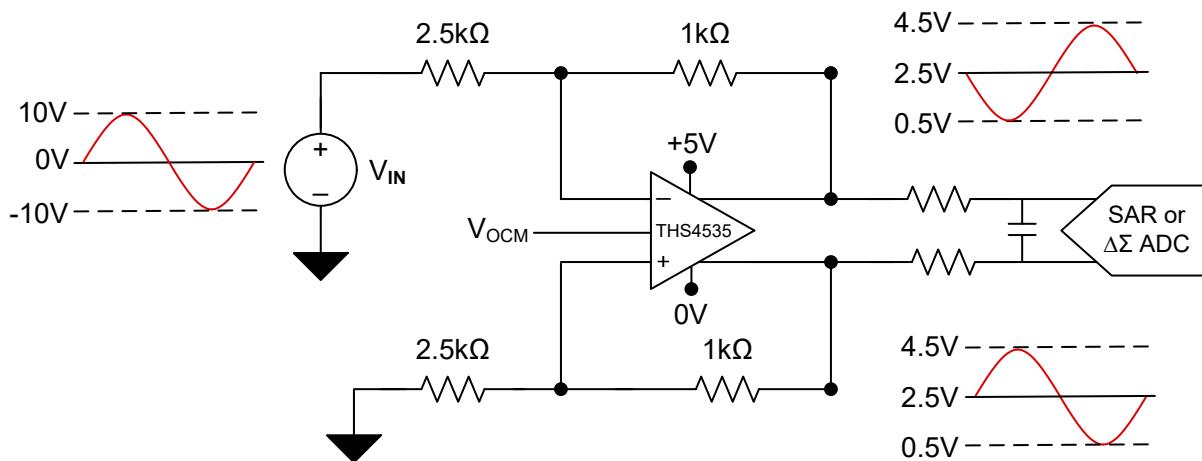

FDA は単一電源電圧で動作しながら、バイポーラ入力信号を受け入れます。図 4 に、THS4536 が  $20\text{Vpp}$  の入力 ( $0\text{V}$  同相モード) を受け入れ、 $2.5\text{V}$  の同相モードで  $8\text{Vpp}$  を出力する様子を示します。この機能により、負電源や不要な信号減衰段を排除して、システムの複雑さを低減できます。FDA には、予測される ADC 入力同相モードに完全に一致するように同相モード出力ループも含まれています。 $V_{OCM}$  ピンにより、追加補償を必要とせずに、アンプの出力同相モードが設定されます。

図 4. 減衰構成の FDA

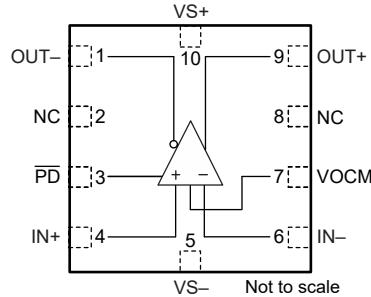

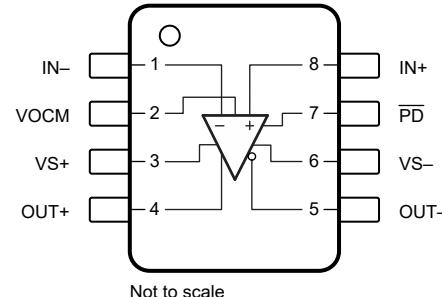

図 5 と図 6 に示すように、TI の FDA のほとんどは **2mm × 2 mm 10 ピン QFN (RUN)** など 2 つの小型パッケージで提供されているため、業界最小クラスの FDA パッケージであり、さらにスペースに制約のあるアプリケーションへの使用にも適しています。

図 5. 2mm × 2mm 10 ピン QFN

図 6. 5mm × 3 mm 8 ピン VSSOP

TI の 2025 **THS4536** は、業界トップクラスの精度を達成する FDA であり、入力オフセットは  $\pm 50\mu\text{V}$ 、オフセットドリフトは最大  $0.8\mu\text{V}/^\circ\text{C}$  です。これにより、システム性能が向上し、コストと時間のかかるシステム キャリブレーションの必要性を最小限に抑えることができます。

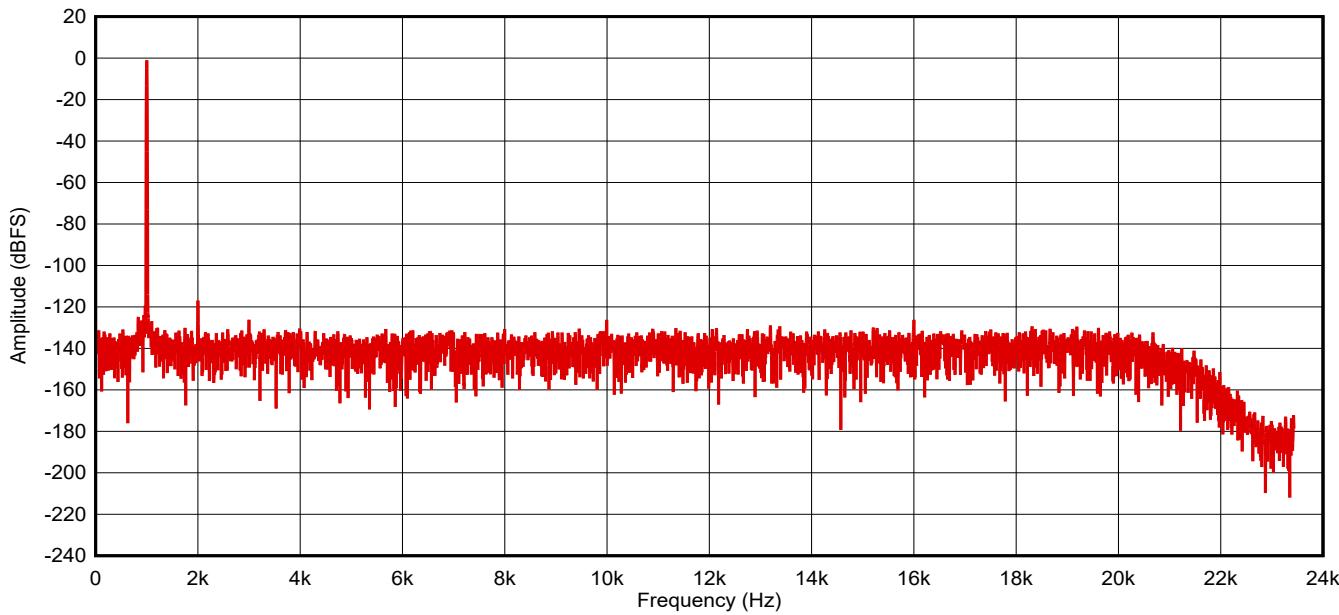

一般的に使用されている **ADS127L11** 24 ビット 400KSPS デルタシグマ ADC は、FDA の影響の一例を示しています。図 7 に示すように、ADC とドライバのペアは、1kHz の入力信号 ( $\text{OSR} = 32$ ) で 102dB の信号対雑音比 (SNR)、–115dB の THD を実現しています。このレベルの性能は、24mW 未満のシステム消費電力で達成されているため、**THS4536** は最小限の電力消費を必要としつつ、最善の高調波歪みと高精度を実現する設計において不可欠な部品となっています。

図 7. ADS127L11 と THS4536 スペクトラムの組み合わせ

お客様の ADC が差動入力を有する場合は、**THS4536** などの高精度 FDA が、システム設計を簡素化し、低ノイズ、低消費電力、低高調波歪みを実現するための適切な選択肢になる可能性があります。

## その他資料

本書に加えて、以下の参考文献を [www.ti.com](http://www.ti.com) で参照してください。

1. テキサス インスツルメンツのフィルタ設計ツール

2. 差動 ADC 向けのアクティブ フィルタ設計

3. 差動 ADC 駆動のオペアンプと完全差動アンプの比較

4. 完全差動アクティブ フィルタにおける無限ゲイン、MFB フィルタトポロジの使用

5. 差動 ADC を駆動するフロント エンドの設計

6. アクティブ ローパス フィルタ設計

7. AN-1393 で高速差動アンプを使用し、A/D コンバータを駆動する方法

8. 完全差動アンプを使用したシングル エンド入力差動出力回路

9. 完全差動オペアンプを用いた減衰器

10. Dallas Logic 社開発、高速 ADC 用高性能シングル エンド差動アクティブ インターフェイス (TIDA-00294)

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月