*Application Note***TDP0604 HDMI1.4/2.0 電気規格準拠テスト チューニング ガイド**

Kai Lai

**概要**

HDMI 2.0 は、最大 18Gbps の合計帯域幅 (チャネルあたり 6Gbps、3 つの TMDS データリンク) をサポートします。挿入損失バジェットは通常、伝送パス全体 (マザーボードの PCB パターン、ビア、コネクタ、ケーブル、および受信側のイコライゼーション機能の損失を含む) に対して計算されます。設計中、合計挿入損失が HDMI ソースおよびレシーバの補償能力を超える場合は、リドライバ プリティマなどの設計を追加することを検討します。それらの間でリドライバはコスト面での優位性から、経済的な設計プロジェクトでより一般的に使用されています。このアプリケーション ノートでは、最新の HDMI 2.0 リドライバ (TDP0604) を紹介し、使用して、HDMI 準拠テストを実行して合格結果を達成する際に正しい調整を行う方法について説明します。

**目次**

|                                                      |           |

|------------------------------------------------------|-----------|

| <b>1 はじめに</b> .....                                  | <b>2</b>  |

| <b>2 テスト設定</b> .....                                 | <b>2</b>  |

| 2.1 ブロック図.....                                       | 2         |

| 2.2 Aardvark I2C および SPI コントローラ.....                 | 3         |

| 2.3 EDID エミュレータ.....                                 | 5         |

| 2.4 I2C モードで TDP0604 を有効化し、ターゲット I2C アドレスを設定します..... | 5         |

| <b>3 TDP0604 HDMI 準拠テストのためのコントロール</b> .....          | <b>6</b>  |

| 3.1 さまざまな EQ のデータアイダイアグラム.....                       | 6         |

| 3.2 立ち上がりと立ち下がりはスルーレートの違いになります.....                  | 9         |

| 3.3 VL および VSwing.....                               | 12        |

| 3.4 HDMI1.4-2.0 合格コンプライアンス テスト パスの結果.....            | 19        |

| <b>4 ヒント</b> .....                                   | <b>21</b> |

| <b>5 まとめ</b> .....                                   | <b>22</b> |

| <b>6 参考資料</b> .....                                  | <b>22</b> |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

このアプリケーション ノートでは、HDMI の電気的コンプライアンス テストを実行する方法について説明し、イコライゼーション (EQ)、差動出力電圧 (VoD)、スルーレートなど、いくつかの TDP0604 レジスタを調整して、異なる結果を得て、最終的に合格する方法について説明します。このアプリケーション ノートには、TDP0604 I<sub>2</sub>C 制御スクリプトの例も記載されています。

## 2 テスト設定

### 2.1 ブロック図

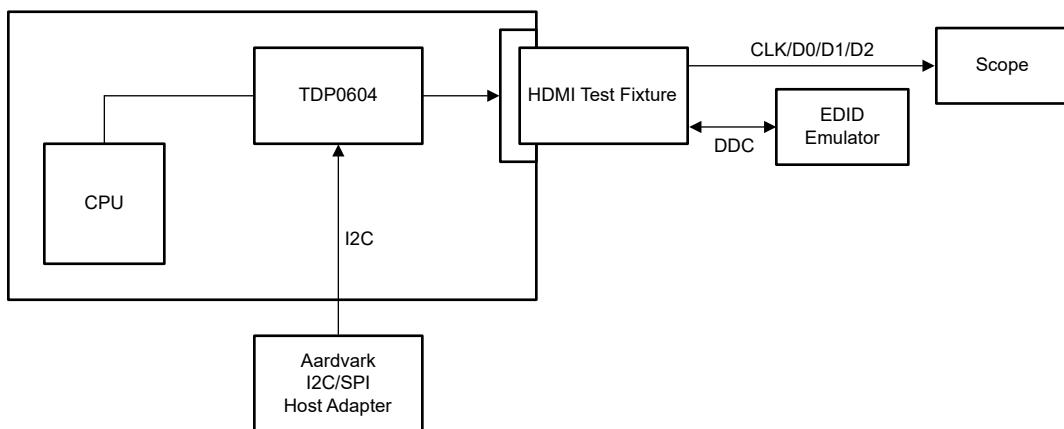

DUT は TDP0604 を搭載したマザーボード (MB) であり、Aardvark I<sub>2</sub>C/SPI コントローラを I<sub>2</sub>C ホストとして使用して TDP0604 を構成します。MB の HDMI ポートはテスト フックスチャに接続します。この装置は、HDMI 3 つの TMDS データレーン、1 つのクロック レーン、DDC バスを切り離します。3 つの TMDS データとクロック レーンは、電気規格準拠 テストのためにオシロスコープに接続されています。DDC バスは、HDMI シンクとして機能する EDID エミュレータに接続されており、MB がモニタとして検出し、ディスプレイ信号を送信します。

図 2-1. テスト プラットフォームのブロック図

## 2.2 Aardvark I2C および SPI コントローラ

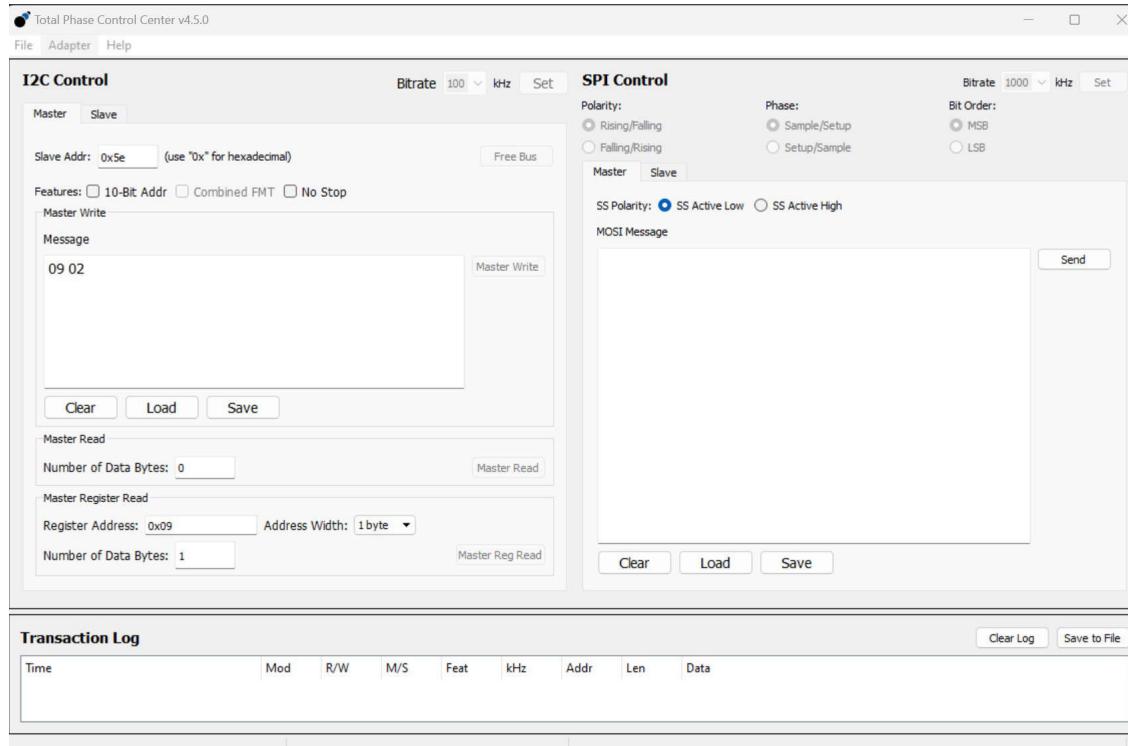

適切なソフトウェアは、Total Phase Control Center v4.5.0 および Aardvark I2C および SPI ホストアダプタを含む個人用ラップトップの Total Phase からダウンロードする必要があります。

図 2-2. Total Phase Control Center アプリのスクリーンショット

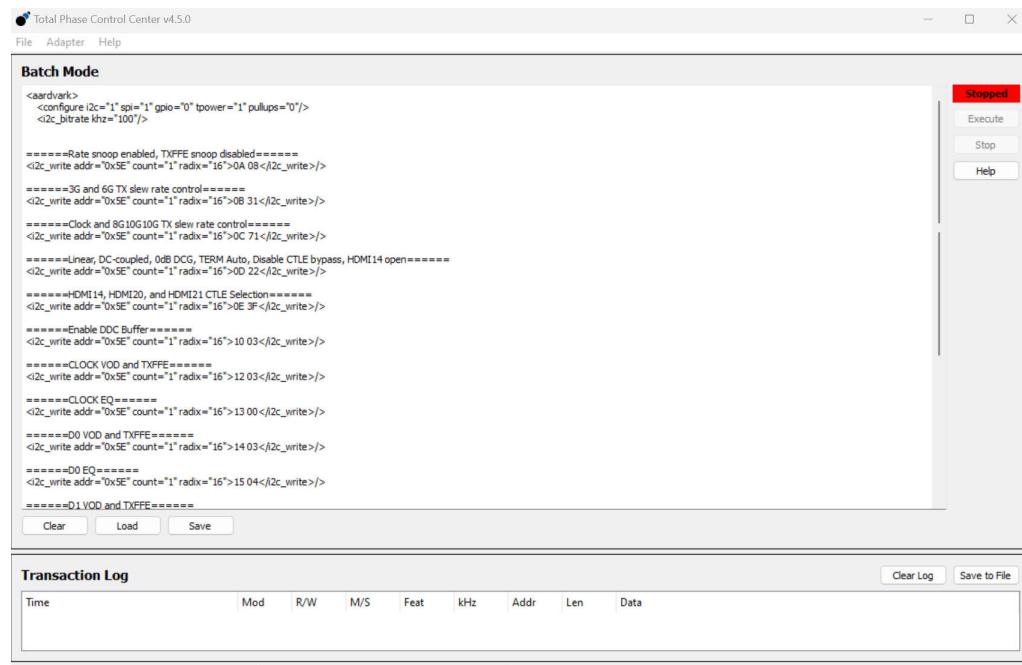

Total Phase Control Center にはバッチ モードが用意されており、ユーザーは連続して実行される一連のコマンドをロードできます。

図 2-3. Total Phase Control Center バッチ モード

TDP0604 [follower address = 5Eh(7bit)] のパッチ スクリプトの例を以下に示します。

```

<aardvark>

<configure i2c="1" spi="1" gpio="0" tpower="1" pullups="0"/>

<i2c_bitrate khz="100"/>

=====Rate snoop enabled, TXFFE snoop enabled. Enable SWAP=====

<i2c_write addr="0x5E" count="1" radix="16">0A 08</i2c_write>/>

=====3G and 6G TX slew rate control=====

<i2c_write addr="0x5E" count="1" radix="16">0B 31</i2c_write>/>

=====Clock and 8G10G10G TX slew rate control=====

<i2c_write addr="0x5E" count="1" radix="16">0C 71</i2c_write>/>

=====Linear, DC-coupled, 0dB DCG, TERM Auto, Disable CTLE bypass. HDMI14 open=====

<i2c_write addr="0x5E" count="1" radix="16">0D 22</i2c_write>/>

=====HDMI14, HDMI20, and HDMI21 CTLE Selection=====

<i2c_write addr="0x5E" count="1" radix="16">0E 3F</i2c_write>/>

=====Enable DDC Buffer=====

<i2c_write addr="0x5E" count="1" radix="16">10 03</i2c_write>/>

=====Lane enable HDMI1P4_2P0_VOD enable=====

<i2c_write addr="0x5E" count="1" radix="16">11 5F</i2c_write>/>

=====CLOCK VOD and TXFFE=====

<i2c_write addr="0x5E" count="1" radix="16">12 03</i2c_write>/>

=====CLOCK EQ=====

<i2c_write addr="0x5E" count="1" radix="16">13 00</i2c_write>/>

=====D0 VOD and TXFFE=====

<i2c_write addr="0x5E" count="1" radix="16">14 03</i2c_write>/>

=====D0 EQ=====

<i2c_write addr="0x5E" count="1" radix="16">15 04</i2c_write>/>

=====D1 VOD and TXFFE=====

<i2c_write addr="0x5E" count="1" radix="16">16 03</i2c_write>/>

=====D1 EQ=====

<i2c_write addr="0x5E" count="1" radix="16">17 04</i2c_write>/>

=====D2 VOD and TXFFE=====

<i2c_write addr="0x5E" count="1" radix="16">18 03</i2c_write>/>

=====D2 EQ=====

<i2c_write addr="0x5E" count="1" radix="16">19 04</i2c_write>/>

=====Read 0x20 to know HDMI1P4_2P0 TMDS_CLK_RATIO =====

<i2c_write addr="0x5E" count="1" radix="16">20</i2c_write>/>

<i2c_read addr="0x5E" count="1"/>

=====Take out of Power down mode. HPD_OUT is asserted high if HPD_IN is high=====

<i2c_write addr="0x5E" count="1" radix="16">09 02</i2c_write>/>

<aardvark>

```

## 2.3 EDID エミュレータ

EDID エミュレータは HDMI シンクとして機能し、適切な EDID および SCDC レジスタを提供するため、HDMI ソースをさまざまな解像度に構成できます。たとえば、HDMI2.0 の電気規格準拠試験を実行するために、EDID エミュレータは 4K (60Hz で 4096×2160) 解像度をエミュレートし、システムがこの EDID を識別して 4K 解像度のディスプレイ信号をテスト用に出力できるようにします。

## 2.4 I2C モードで TDP0604 を有効化し、ターゲット I2C アドレスを設定します

このアプリケーションノートは、TDP0604 レジスタ設定を構成するため、I2C マスターとして Aardvark を使用します。その結果、レジスタ設定には I2C モードで TDP0604 が必要です。TDP0604 には 4 レベルの入力ピンがあり、レシーバのイコライゼーション ゲイン、トランミッタ電圧スイング、プリエンファシスを制御し、TDP0604 をさまざまな動作モードに設定します。[表 2-1](#) を使用し、HW でピンをフローティングにする F レベル入力の MODE ピンを設定します。

**表 2-1. レベル制御ピンの設定**

| レベル | 設定                              |

|-----|---------------------------------|

| 0   | 1kΩ 5% を GND に接続します             |

| R   | 20kΩ 5% を GND に接続します            |

| F   | フロート (ピンはオープンのままにする)            |

| 1   | 1kΩ 5% を V <sub>CC</sub> に接続します |

**表 2-2. Mode ピンの機能**

| Mode ピンの機能 | 説明                       |

|------------|--------------------------|

| 0          | DDC バッファがイネーブルのピン ストラップ  |

| R          | DDC バッファがディセーブルのピン ストラップ |

| F          | I2C モード                  |

| 1          | 予約済み                     |

I2C モード イネーブルに加えて、I2C バスの TDP0604 にはターゲット I2C アドレスも必要です。TDP0604 が I2C モードに構成されている場合、TDP0604 には I2C プログラミングのアドレスビットを表す ADDR/EQ0 ピンがあります。そのため、このアプリケーションノートでは、1kΩ を GND に接続してこのピンをレベル 0 に設定するための例が紹介されています。[表 2-3](#) に記載されているレベル 0 は、ターゲットの I2C アドレス 0xBCh (読み出し/8 ビット) /BDH (書き込み/8 ビット)、すなわち 0x5E (7 ビット) となります。

**表 2-3. TDP0604 I2C デバイスのアドレスの説明**

| ADDR/EQ0<br>ピン | ビット 7<br>(MSB) | ビット 6 | ビット 5 | ビット 4 | ビット 3 | ビット 2 | ビット 1 | ビット 0<br>(W/R) | 16 進  |

|----------------|----------------|-------|-------|-------|-------|-------|-------|----------------|-------|

| 0              | 1              | 0     | 1     | 1     | 1     | 1     | 0     | 0/1            | BC/BD |

| R              | 1              | 0     | 1     | 1     | 1     | 0     | 1     | 0/1            | BA/BB |

| F              | 1              | 0     | 1     | 1     | 1     | 0     | 0     | 0/1            | B8/B9 |

| 1              | 1              | 0     | 1     | 1     | 0     | 1     | 1     | 0/1            | B6/B7 |

### 3 TDP0604 HDMI 準拠テストのためのコントロール

このセクションでは、さまざまな設定を調整して、HDMI1.4/2.0 解像度の異なる結果を得ることによって、いくつかの例を示します。異なる結果が観察され、テストに合格するように正しい調整値が調整されます。

#### 3.1 さまざまな EQ のデータアイダイアグラム

##### 3.1.1 解像度 4096×2160\_60p\_8bit\_444 での HDMI2.0 テスト

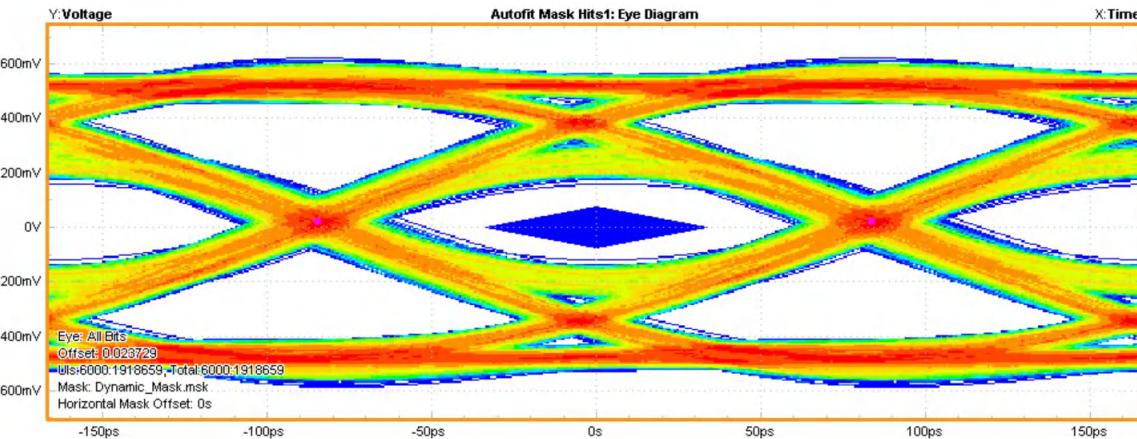

###### 3.1.1.1 D1 NegativeLane、EQ = 0

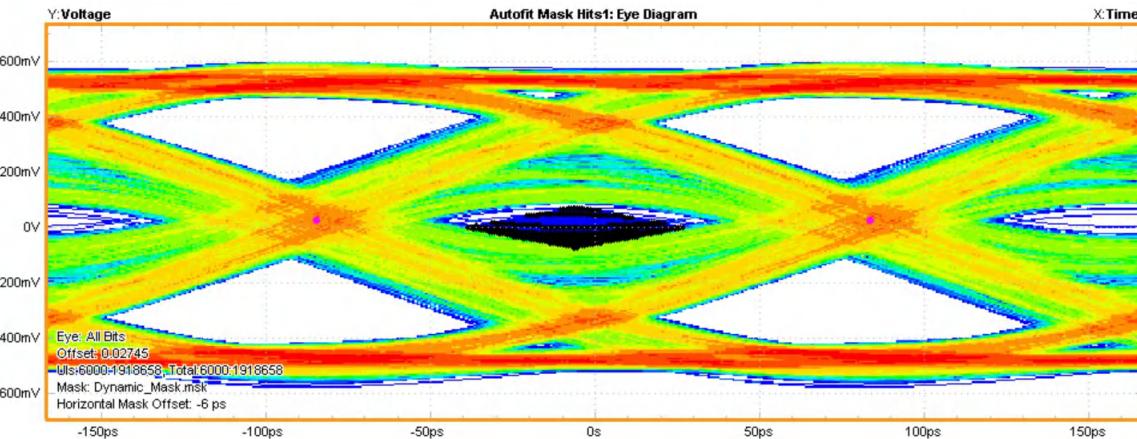

図 3-1. HDMI2.0\_4K\_60fps テスト アイ マスク (EQ = 0)

###### 3.1.1.2 D1 NegativeLane、EQ = 4

図 3-2. HDMI2.0\_4K\_60fps テスト アイ マスク (EQ = 4)

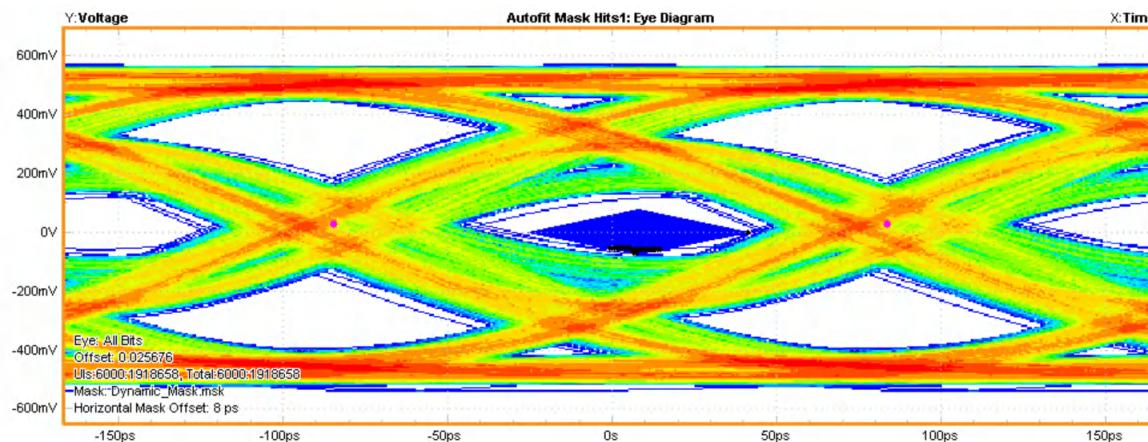

### 3.1.1.3 D1 NegativeLane、EQ = F

図 3-3. HDMI2.0\_4K\_60fps テストアイマスク (EQ = F)

### 3.1.2 解像度 4096×2160\_30p\_8bit\_444 での HDMI 1.4 テスト

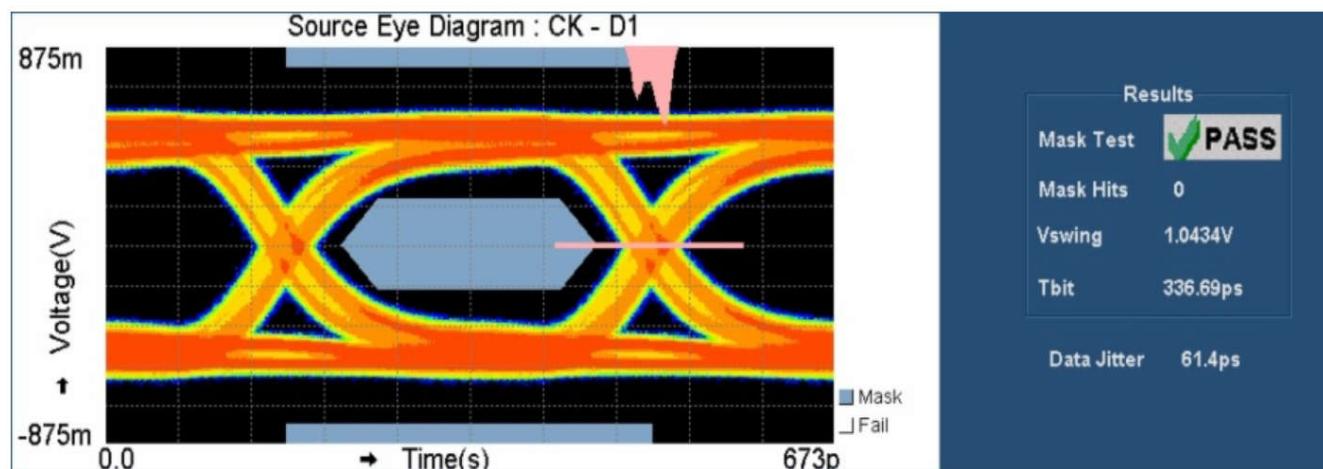

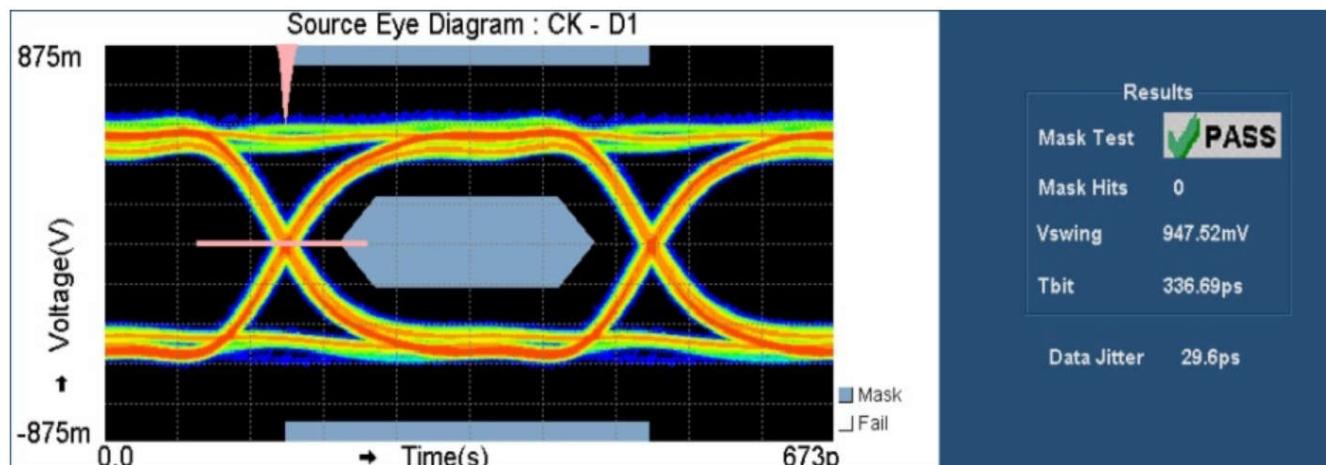

#### 3.1.2.1 ソースアイダイアグラム: CK - D1、EQ = 0

図 3-4. HDMI1.4\_4K\_30fps テストアイマスク (EQ = 0)

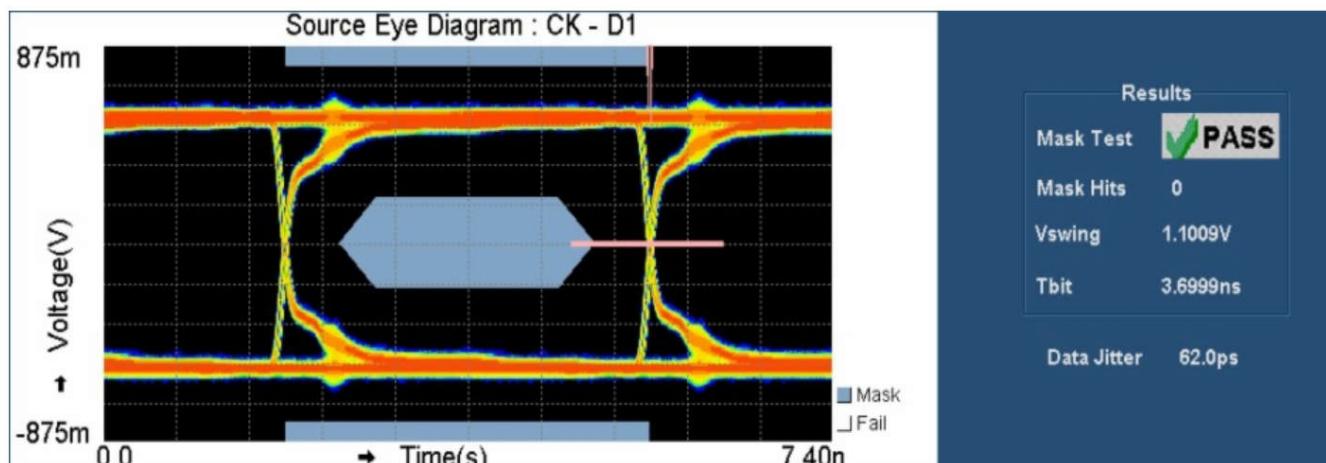

#### 3.1.2.2 ソースアイダイアグラム: CK - D1、EQ = 4

図 3-5. HDMI1.4\_4K\_30fps テストアイマスク (EQ = 4)

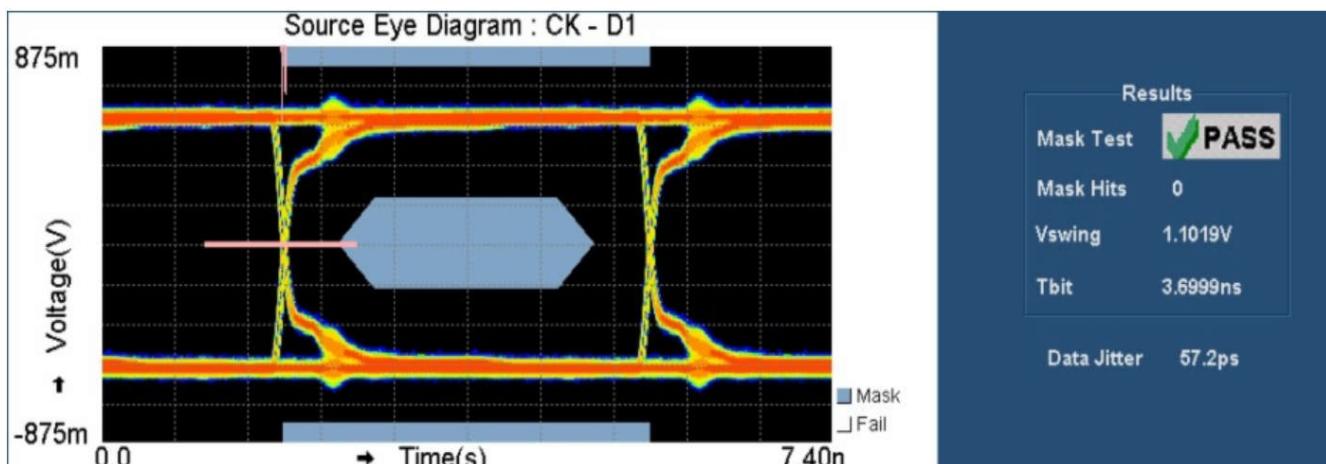

### 3.1.2.3 ソース アイ ダイアグラム: CK - D1、EQ = F

図 3-6. HDMI1.4\_4K\_30fps テスト アイ マスク (EQ = F)

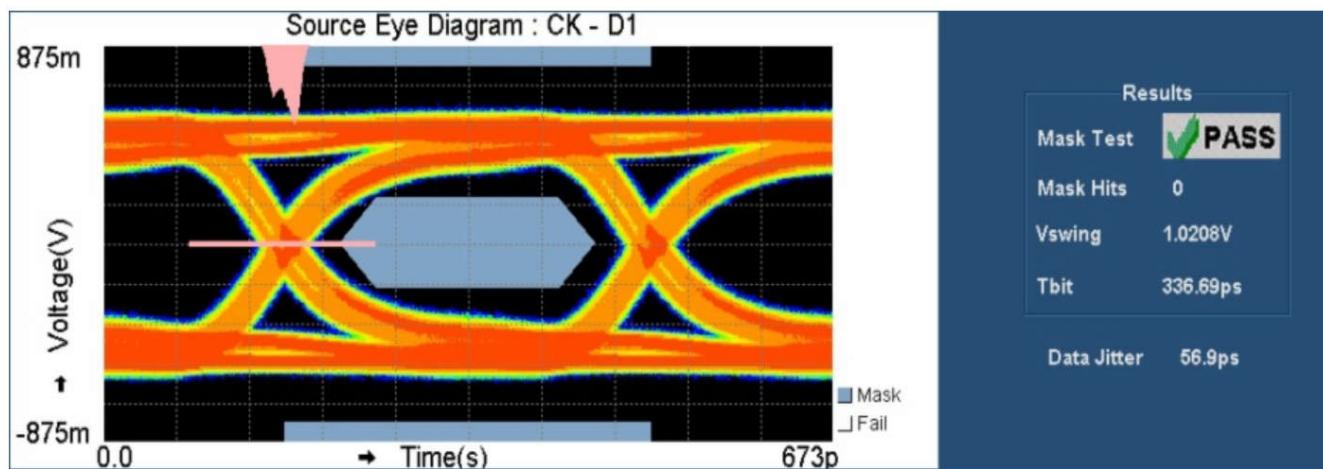

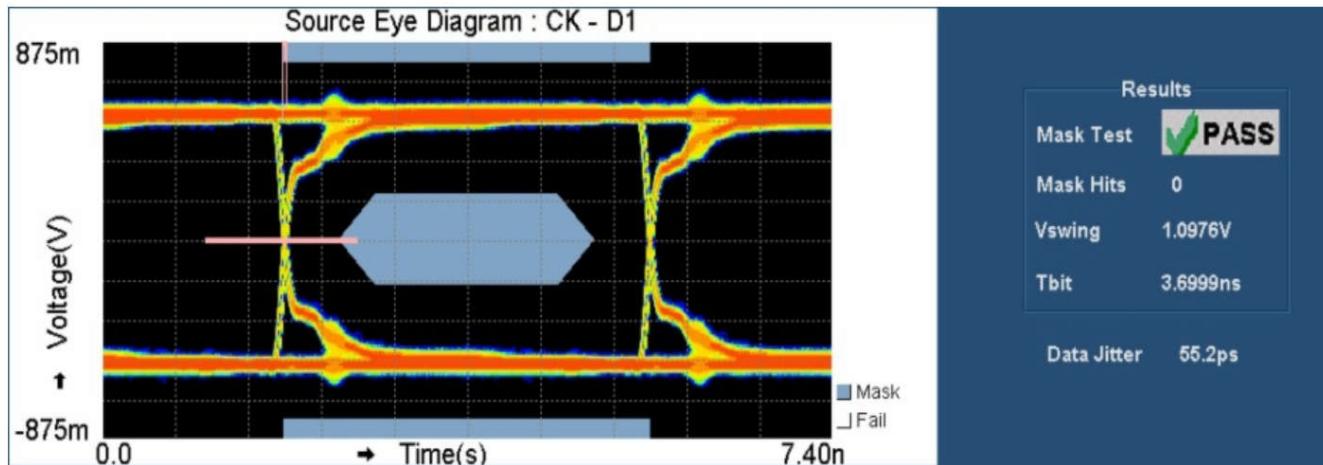

### 3.1.3 解像度 720×480\_60p\_8bit\_444 での HDMI 1.4 テスト

#### 3.1.3.1 ソース アイ ダイアグラム: CK - D1、EQ = 0

図 3-7. HDMI1.4-480p\_60fps テスト アイ マスク (EQ = 0)

#### 3.1.3.2 ソース アイ ダイアグラム: CK - D1、EQ = 4

図 3-8. HDMI1.4\_480p\_60fps テスト アイ マスク (EQ = 4)

### 3.1.3.3 ソース アイ ダイアグラム: CK - D1、EQ = F

図 3-9. HDMI1.4\_480p\_60fps テスト アイ マスク (EQ = F)

## 3.2 立ち上がりと立ち下がりはスルーレートの違いになります

### 3.2.1 解像度 4096×2160\_60p\_8bit\_444 での HDMI2.0 テスト

#### 3.2.1.1 TRISE、TFALL (SLEW\_3G = 3h、SLEW\_6G = 0h、SLEW\_CLK 0 = 0h の場合)

| HF1-2- TRISE, TFALL |                     |                |       |             |           |             |          |           |            |          |

|---------------------|---------------------|----------------|-------|-------------|-----------|-------------|----------|-----------|------------|----------|

| Lane Name           | Measurement Details | Measured Value | Units | TBit        | Data Rate | Test Result | Margin   | Low Limit | High Limit | Comments |

| Clock               | Clock Rise Time     | 179.7593       | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 104.7593 | 75.0000   | -          |          |

| Clock               | Clock Fall Time     | 179.6075       | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 104.6075 | 75.0000   | -          |          |

| D0                  | D0 Rise Time        | 80.6127        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 38.1127  | 42.5000   | -          |          |

| D0                  | D0 Fall Time        | 79.8119        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 37.3119  | 42.5000   | -          |          |

| D1                  | D1 Rise Time        | 77.4813        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 34.9813  | 42.5000   | -          |          |

| D1                  | D1 Fall Time        | 76.8607        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 34.3607  | 42.5000   | -          |          |

| D2                  | D2 Rise Time        | 82.4868        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 39.9868  | 42.5000   | -          |          |

| D2                  | D2 Fall Time        | 82.8182        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 40.3182  | 42.5000   | -          |          |

| COMMENTS            |                     |                |       |             |           |             |          |           |            |          |

図 3-10. HDMI2.0\_4K\_60fps テスト スルーレート (SLEW\_3G = 3h、SLEW\_6G = 0h、SLEW\_CLK = 0h)

#### 3.2.1.2 TRISE、TFALL (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK 0 = 1h の場合)

| HF1-2- TRISE, TFALL |                     |                |       |             |           |             |         |           |            |          |

|---------------------|---------------------|----------------|-------|-------------|-----------|-------------|---------|-----------|------------|----------|

| Lane Name           | Measurement Details | Measured Value | Units | TBit        | Data Rate | Test Result | Margin  | Low Limit | High Limit | Comments |

| Clock               | Clock Rise Time     | 170.7983       | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 95.7983 | 75.0000   | -          |          |

| Clock               | Clock Fall Time     | 171.7427       | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 96.7427 | 75.0000   | -          |          |

| D0                  | D0 Rise Time        | 80.2006        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 37.7006 | 42.5000   | -          |          |

| D0                  | D0 Fall Time        | 78.9200        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 36.4200 | 42.5000   | -          |          |

| D1                  | D1 Rise Time        | 77.9838        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 35.4838 | 42.5000   | -          |          |

| D1                  | D1 Fall Time        | 77.0102        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 34.5102 | 42.5000   | -          |          |

| D2                  | D2 Rise Time        | 86.0967        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 43.5967 | 42.5000   | -          |          |

| D2                  | D2 Fall Time        | 86.0807        | ps    | 168.3458 ps | 5.94 Gbps | Pass        | 43.5807 | 42.5000   | -          |          |

| COMMENTS            |                     |                |       |             |           |             |         |           |            |          |

図 3-11. HDMI2.0\_4K\_60fps テスト スルーレート (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK = 1h)

### 3.2.1.3 TRISE、TFALL (SLEW\_3G = 3h、SLEW\_6G = 7h、SLEW\_CLK 0 = 7h の場合)

| HF1-2- TRISE, TFALL |                     |                |       |             |           |             |         |           |            |          |

|---------------------|---------------------|----------------|-------|-------------|-----------|-------------|---------|-----------|------------|----------|

| Lane Name           | Measurement Details | Measured Value | Units | TBit        | Data Rate | Test Result | Margin  | Low Limit | High Limit | Comments |

| <u>Clock</u>        | Clock Rise Time     | 82.3938        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 7.3938  | 75.0000   | -          |          |

| <u>Clock</u>        | Clock Fall Time     | 76.7717        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 1.7717  | 75.0000   | -          |          |

| <u>D0</u>           | D0 Rise Time        | 57.2870        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 14.7870 | 42.5000   | -          |          |

| <u>D0</u>           | D0 Fall Time        | 55.0670        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 12.5670 | 42.5000   | -          |          |

| <u>D1</u>           | D1 Rise Time        | 58.0699        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 15.5699 | 42.5000   | -          |          |

| <u>D1</u>           | D1 Fall Time        | 57.2474        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 14.7474 | 42.5000   | -          |          |

| <u>D2</u>           | D2 Rise Time        | 58.4076        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 15.9076 | 42.5000   | -          |          |

| <u>D2</u>           | D2 Fall Time        | 57.5933        | ps    | 168.3460 ps | 5.94 Gbps | Pass        | 15.0933 | 42.5000   | -          |          |

| COMMENTS            |                     |                |       |             |           |             |         |           |            |          |

図 3-12. HDMI2.0\_4K\_60fps テストスルーレート (SLEW\_3G = 3h、SLEW\_6G = 7h、SLEW\_CLK = 7h)

### 3.2.2 解像度 4096×2160\_30p\_8bit\_444 での HDMI 1.4 テスト

### 3.2.3 TRISE、TFALL (SLEW\_3G = 0h、SLEW\_6G = 1h、SLEW\_CLK 0 = 0h の場合)

表 3-1. HDMI1.4\_4K\_30fps テストスルーレート (SLEW\_3G = 0h、SLEW\_6G = 1h、SLEW\_CLK = 0h)

| インデックス | テスト名称          | レーン | 仕様範囲            | 測定値      | 結果 |

|--------|----------------|-----|-----------------|----------|----|

| 1      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TRISE | 177.27ps | 合格 |

| 2      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TRISE | 184.82ps | 合格 |

| 3      | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TRISE | 176.23ps | 合格 |

| 4      | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TRISE | 167.89ps | 合格 |

| 5      | 7-4:ソース立ち下がり時間 | CK  | 75.00ps < TFALL | 180.77ps | 合格 |

| 6      | 7-4:ソース立ち下がり時間 | D0  | 75.00ps < TFALL | 181.37ps | 合格 |

| 7      | 7-4:ソース立ち下がり時間 | D1  | 75.00ps < TFALL | 170.22ps | 合格 |

| 8      | 7-4:ソース立ち下がり時間 | D2  | 75.00ps < TFALL | 176.58ps | 合格 |

### 3.2.4 TRISE、TFALL (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK 0 = 1h の場合)

表 3-2. HDMI1.4\_4K\_30fps テストスルーレート (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK = 1h)

| インデックス | テスト名称          | レーン | 仕様範囲            | 測定値      | 結果 |

|--------|----------------|-----|-----------------|----------|----|

| 8      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TRISE | 162.29ps | 合格 |

| 9      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TRISE | 129.76ps | 合格 |

| 10     | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TRISE | 128.04ps | 合格 |

| 11     | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TRISE | 125.23ps | 合格 |

| 12     | 7-4:ソース立ち下がり時間 | CK  | 75.00ps < TFALL | 167.05ps | 合格 |

| 13     | 7-4:ソース立ち下がり時間 | D0  | 75.00ps < TFALL | 126.26ps | 合格 |

| 14     | 7-4:ソース立ち下がり時間 | D1  | 75.00ps < TFALL | 126.12ps | 合格 |

| 15     | 7-4:ソース立ち下がり時間 | D2  | 75.00ps < TFALL | 126.50ps | 合格 |

### 3.2.5 TRISE、TFALL (SLEW\_3G = 7h、SLEW\_6G = 1h、SLEW\_CLK 0 = 7h の場合)

表 3-3. HDMI1.4\_4K\_30fps テストスルーレート (SLEW\_3G = 7h、SLEW\_6G = 1h、SLEW\_CLK = 7h)

| インデックス | テスト名称          | レーン | 仕様範囲           | 測定値    | 結果 |

|--------|----------------|-----|----------------|--------|----|

| 1      | 7-4:ソース立ち上がり時間 | CK  | 75.00 < TRISE; | 123.10 | 合格 |

| 2      | 7-4:ソース立ち上がり時間 | D0  | 75.00 < TRISE; | 114.85 | 合格 |

| 3      | 7-4:ソース立ち上がり時間 | D1  | 75.00 < TRISE; | 109.25 | 合格 |

| 4      | 7-4:ソース立ち上がり時間 | D2  | 75.00 < TRISE; | 105.19 | 合格 |

| 5      | 7-4:ソース立ち下がり時間 | CK  | 75.00 < TFALL; | 123.90 | 合格 |

| 6      | 7-4:ソース立ち下がり時間 | D0  | 75.00 < TFALL; | 112.03 | 合格 |

| 7      | 7-4:ソース立ち下がり時間 | D1  | 75.00 < TFALL; | 104.05 | 合格 |

| 8      | 7-4:ソース立ち下がり時間 | D2  | 75.00 < TFALL; | 103.77 | 合格 |

### 3.2.6 解像度 720×480\_60p\_8bit\_444 での HDMI 1.4 テスト

#### 3.2.6.1 TRISE、TFALL (SLEW\_3G = 0h、SLEW\_6G = 1h、SLEW\_CLK 0 = 0h の場合)

表 3-4. HDMI1.4\_480p\_60fps テストスルーレート (SLEW\_3G = 0h、SLEW\_6G = 1h、SLEW\_CLK = 0h)

| インデックス | テスト名称          | レーン | 仕様範囲             | 測定値      | 結果 |

|--------|----------------|-----|------------------|----------|----|

| 1      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TRISE; | 313.55ps | 合格 |

| 2      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TRISE; | 348.17ps | 合格 |

| 3      | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TRISE; | 352.35ps | 合格 |

| 4      | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TRISE; | 288.24ps | 合格 |

| 5      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TFALL; | 307.47ps | 合格 |

| 6      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TFALL; | 332.91ps | 合格 |

| 7      | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TFALL; | 328.74ps | 合格 |

| 8      | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TFALL; | 301.89ps | 合格 |

#### 3.2.6.2 TRISE、TFALL (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK 0 = 1h の場合)

表 3-5. HDMI1.4\_480p\_60fps テストスルーレート (SLEW\_3G = 3h、SLEW\_6G = 1h、SLEW\_CLK = 1h)

| インデックス | テスト名称          | レーン | 仕様範囲             | 測定値    | 結果 |

|--------|----------------|-----|------------------|--------|----|

| 8      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TRISE; | 291.51 | 合格 |

| 9      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TRISE; | 281.89 | 合格 |

| 10     | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TRISE; | 293.08 | 合格 |

| 11     | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TRISE; | 188.39 | 合格 |

| 12     | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TFALL; | 281.31 | 合格 |

| 13     | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TFALL; | 255.71 | 合格 |

| 14     | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TFALL; | 263.85 | 合格 |

| 15     | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TFALL; | 218.30 | 合格 |

### 3.2.6.3 TRISE、TFALL (SLEW\_3G = 7h、SLEW\_6G = 1h、SLEW\_CLK 0 = 7h の場合)

表 3-6. HDMI1.4\_480p\_60fps テストスルーレート (SLEW\_3G = 7h、SLEW\_6G = 1h、SLEW\_CLK = 7h)

| インデックス | テスト名称          | レーン | 仕様範囲             | 測定値    | 結果 |

|--------|----------------|-----|------------------|--------|----|

| 1      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TRISE; | 184.29 | 合格 |

| 2      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TRISE; | 262.69 | 合格 |

| 3      | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TRISE; | 267.06 | 合格 |

| 4      | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TRISE; | 132.94 | 合格 |

| 5      | 7-4:ソース立ち上がり時間 | CK  | 75.00ps < TFALL; | 186.67 | 合格 |

| 6      | 7-4:ソース立ち上がり時間 | D0  | 75.00ps < TFALL; | 249.81 | 合格 |

| 7      | 7-4:ソース立ち上がり時間 | D1  | 75.00ps < TFALL; | 249.70 | 合格 |

| 8      | 7-4:ソース立ち上がり時間 | D2  | 75.00ps < TFALL; | 131.29 | 合格 |

## 3.3 VL および VSwing

### 3.3.1 解像度 4096×2160\_60p\_8bit\_444 での HDMI2.0 テスト

#### 3.3.1.1 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing

| HF1-1 – VL and VSwing |                      |                |       |             |           |             |                     |           |            |          |

|-----------------------|----------------------|----------------|-------|-------------|-----------|-------------|---------------------|-----------|------------|----------|

| Lane Name             | Measurement Details  | Measured Value | Units | TBit        | Data Rate | Test Result | Margin              | Low Limit | High Limit | Comments |

| Clock                 | TMDS VLow for Clock+ | 2.6520         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.3520 & 0.4480     | 2.3       | 3.1        |          |

| Clock                 | TMDS VLow for Clock- | 2.6469         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.3469 & 0.4531     | 2.3       | 3.1        |          |

| Clock                 | VSwing for Clock+    | 383.0958       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 183.0958 & 216.9042 | 200       | 600        |          |

| Clock                 | VSwing for Clock-    | 381.6901       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 181.6901 & 218.3099 | 200       | 600        |          |

| D0                    | TMDS VLow for D0+    | 2.5759         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2759 & 0.3241     | 2.3       | 2.9        |          |

| D0                    | TMDS VLow for D0-    | 2.5458         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2458 & 0.3542     | 2.3       | 2.9        |          |

| D0                    | VSwing for D0+       | 414.5904       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 14.5904 & 185.4096  | 400       | 600        |          |

| D0                    | VSwing for D0-       | 404.7286       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 4.7286 & 195.2714   | 400       | 600        |          |

| D1                    | TMDS VLow for D1+    | 2.5156         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2156 & 0.3844     | 2.3       | 2.9        |          |

| D1                    | TMDS VLow for D1-    | 2.5022         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2022 & 0.3978     | 2.3       | 2.9        |          |

| D1                    | VSwing for D1+       | 442.1562       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 42.1562 & 157.8438  | 400       | 600        |          |

| D1                    | VSwing for D1-       | 461.6746       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 61.6746 & 138.3254  | 400       | 600        |          |

| D2                    | TMDS VLow for D2+    | 2.5806         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2806 & 0.3194     | 2.3       | 2.9        |          |

| D2                    | TMDS VLow for D2-    | 2.5565         | V     | 168.3460 ps | 5.94 Gbps | Pass        | 0.2565 & 0.3435     | 2.3       | 2.9        |          |

| D2                    | VSwing for D2+       | 419.7817       | mV    | 168.3460 ps | 5.94 Gbps | Pass        | 19.7817 & 180.2183  | 400       | 600        |          |

| D2                    | VSwing for D2-       | 389.1233       | mV    | 168.3460 ps | 5.94 Gbps | Fail        | -10.8767 & 210.8767 | 400       | 600        |          |

図 3-13. HDMI2.0\_4K\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD および D2\_VOD = 0h)

### 3.3.1.2 HDMI20\_VOD = 1h (デフォルト 1000mV)、HDMI14\_VOD = 1h (デフォルト 1000mV) での VL および VSwing

| HF1-1- VL and VSwing |                      |                |       |             |           |             |                     |           |            |          |

|----------------------|----------------------|----------------|-------|-------------|-----------|-------------|---------------------|-----------|------------|----------|

| Lane Name            | Measurement Details  | Measured Value | Units | TBit        | Data Rate | Test Result | Margin              | Low Limit | High Limit | Comments |

| Clock                | TMDS VLow for Clock+ | 2.5862         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.2862 & 0.5138     | 2.3       | 3.1        |          |

| Clock                | TMDS VLow for Clock- | 2.5866         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.2866 & 0.5134     | 2.3       | 3.1        |          |

| Clock                | VSwing for Clock+    | 414.4800       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 214.4800 & 185.5200 | 200       | 600        |          |

| Clock                | VSwing for Clock-    | 419.2105       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 219.2105 & 180.7895 | 200       | 600        |          |

| D0                   | TMDS VLow for D0+    | 2.5000         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.2000 & 0.4000     | 2.3       | 2.9        |          |

| D0                   | TMDS VLow for D0-    | 2.4717         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.1717 & 0.4283     | 2.3       | 2.9        |          |

| D0                   | VSwing for D0+       | 468.3807       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 68.3807 & 131.6193  | 400       | 600        |          |

| D0                   | VSwing for D0-       | 445.6433       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 45.6433 & 154.3567  | 400       | 600        |          |

| D1                   | TMDS VLow for D1+    | 2.4409         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.1409 & 0.4591     | 2.3       | 2.9        |          |

| D1                   | TMDS VLow for D1-    | 2.4206         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.1206 & 0.4794     | 2.3       | 2.9        |          |

| D1                   | VSwing for D1+       | 480.8352       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 80.8352 & 119.1648  | 400       | 600        |          |

| D1                   | VSwing for D1-       | 511.8712       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 111.8712 & 88.1288  | 400       | 600        |          |

| D2                   | TMDS VLow for D2+    | 2.4943         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.1943 & 0.4057     | 2.3       | 2.9        |          |

| D2                   | TMDS VLow for D2-    | 2.4844         | V     | 168.3456 ps | 5.94 Gbps | Pass        | 0.1844 & 0.4156     | 2.3       | 2.9        |          |

| D2                   | VSwing for D2+       | 474.6607       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 74.6607 & 125.3393  | 400       | 600        |          |

| D2                   | VSwing for D2-       | 436.2706       | mV    | 168.3456 ps | 5.94 Gbps | Pass        | 36.2706 & 163.7294  | 400       | 600        |          |

図 3-14. HDMI2.0\_4K\_60fps テスト VL および VSwing (HDMI20\_VOD = 1h, HDMI14\_VOD = 1h)

### 3.3.1.3 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing

| HF1-1 – VL and VSwing |                      |                |       |             |           |             |                     |           |            |          |

|-----------------------|----------------------|----------------|-------|-------------|-----------|-------------|---------------------|-----------|------------|----------|

| Lane Name             | Measurement Details  | Measured Value | Units | TBit        | Data Rate | Test Result | Margin              | Low Limit | High Limit | Comments |

| Clock                 | TMDS VLow for Clock+ | 2.4915         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.1915 & 0.6085     | 2.3       | 3.1        |          |

| Clock                 | TMDS VLow for Clock- | 2.4899         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.1899 & 0.6101     | 2.3       | 3.1        |          |

| Clock                 | VSwing for Clock+    | 482.8657       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 282.8657 & 117.1343 | 200       | 600        |          |

| Clock                 | VSwing for Clock-    | 488.1558       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 288.1558 & 111.8442 | 200       | 600        |          |

| D0                    | TMDS VLow for D0+    | 2.3917         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0917 & 0.5083     | 2.3       | 2.9        |          |

| D0                    | TMDS VLow for D0-    | 2.3681         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0681 & 0.5319     | 2.3       | 2.9        |          |

| D0                    | VSwing for D0+       | 532.3578       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 132.3578 & 67.6422  | 400       | 600        |          |

| D0                    | VSwing for D0-       | 512.2132       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 112.2132 & 87.7868  | 400       | 600        |          |

| D1                    | TMDS VLow for D1+    | 2.3357         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0357 & 0.5643     | 2.3       | 2.9        |          |

| D1                    | TMDS VLow for D1-    | 2.3060         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0060 & 0.5940     | 2.3       | 2.9        |          |

| D1                    | VSwing for D1+       | 563.9695       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 163.9695 & 36.0305  | 400       | 600        |          |

| D1                    | VSwing for D1-       | 595.9603       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 195.9603 & 4.0397   | 400       | 600        |          |

| D2                    | TMDS VLow for D2+    | 2.3966         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0966 & 0.5034     | 2.3       | 2.9        |          |

| D2                    | TMDS VLow for D2-    | 2.3826         | V     | 168.3459 ps | 5.94 Gbps | Pass        | 0.0826 & 0.5174     | 2.3       | 2.9        |          |

| D2                    | VSwing for D2+       | 536.1971       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 136.1971 & 63.8029  | 400       | 600        |          |

| D2                    | VSwing for D2-       | 502.7240       | mV    | 168.3459 ps | 5.94 Gbps | Pass        | 102.7240 & 97.2760  | 400       | 600        |          |

図 3-15. HDMI2.0\_4K\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 7h)

### 3.3.2 解像度 4096 x 2160\_30p\_8bit\_444 での HDMI 1.4 テスト

3.3.2.1 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing は、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 0h に値を使用し、-15 % を制限します

表 3-7. HDMI1.4\_4K\_30fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD および D2\_VOD = 0h)

| インデックス | テスト名称                              | レーン | 仕様範囲                 | 測定値     | 結果 |

|--------|------------------------------------|-----|----------------------|---------|----|

| 1      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1+ | 2.700V < VL < 2.900V | 2.7465V | 合格 |

| 2      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2+ | 2.700V < VL < 2.900V | 2.7939V | 合格 |

| 3      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1- | 2.700V < VL < 2.900V | 2.7366V | 合格 |

| 4      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2- | 2.700V < VL < 2.900V | 2.8848V | 合格 |

| 5      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1+ | 2.600V < VL < 2.900V | 2.7465V | 合格 |

| 6      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2+ | 2.600V < VL < 2.900V | 2.7939V | 合格 |

| 7      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1- | 2.600V < VL < 2.900V | 2.7366V | 合格 |

| 8      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2- | 2.600V < VL < 2.900V | 2.8848V | 合格 |

| 9      | 7-2: ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK+ | 2.700V < VL < 2.900V | 2.7801V | 合格 |

**表 3-7. HDMI1.4\_4K\_30fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD および D2\_VOD = 0h) (続き)**

| インデックス | テスト名称                             | レーン  | 仕様範囲                 | 測定値     | 結果 |

|--------|-----------------------------------|------|----------------------|---------|----|

| 10     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0+  | 2.700V < VL < 2.900V | 2.7966V | 合格 |

| 11     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK - | 2.700V < VL < 2.900V | 2.7634V | 合格 |

| 12     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0-  | 2.700V < VL < 2.900V | 2.7665V | 合格 |

| 13     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK+  | 2.600V < VL < 2.900V | 2.7803V | 合格 |

| 14     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0+  | 2.600V < VL < 2.900V | 2.7966V | 合格 |

| 15     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK - | 2.600V < VL < 2.900V | 2.7699V | 合格 |

| 16     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0-  | 2.600V < VL < 2.900V | 2.7633V | 合格 |

### 3.3.2.2 HDMI20\_VOD = 1h (デフォルト 1000mV)、HDMI14\_VOD = 1h (デフォルト 1000mV) での VL および VSwing

**表 3-8. HDMI1.4\_4K\_30fps テスト VL および VSwing (HDMI20\_VOD = 1h、HDMI14\_VOD = 1h)**

| インデックス | テスト名称                                  | レーン  | 仕様範囲                | 測定値     | 結果 |

|--------|----------------------------------------|------|---------------------|---------|----|

| 18     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D1+  | 2.700V < VL < 2900V | 2.7395V | 合格 |

| 19     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D2+  | 2.700V < VL < 2900V | 2.7613V | 合格 |

| 20     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D1-  | 2.700V < VL < 2900V | 2.7055V | 合格 |

| 21     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D2-  | 2.700V < VL < 2900V | 2.7587V | 合格 |

| 22     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D1+  | 2.600V < VL < 2900V | 2.7395V | 合格 |

| 23     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D2+  | 2.600V < VL < 2900V | 2.7649V | 合格 |

| 24     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D1-  | 2.600V < VL < 2900V | 2.7055V | 合格 |

| 25     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D2-  | 2.600V < VL < 2900V | 2.7587V | 合格 |

| 26     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | CK+  | 2.600V < VL < 2900V | 2.7237V | 合格 |

| 27     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D0+  | 2.700V < VL < 2900V | 2.7372V | 合格 |

| 28     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | CK - | 2.700V < VL < 2900V | 2.7075V | 合格 |

| 29     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D0-  | 2.700V < VL < 2900V | 2.7155V | 合格 |

| 30     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | CK+  | 2.600V < VL < 2900V | 2.7240V | 合格 |

| 31     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D0+  | 2.600V < VL < 2900V | 2.7372V | 合格 |

| 32     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | CK - | 2.600V < VL < 2900V | 2.7075V | 合格 |

| 33     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D0-  | 2.600V < VL < 2900V | 2.7155V | 合格 |

3.3.2.3 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing は、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 7h に値を使用、+20% を制限します)

**表 3-9. HDMI1.4\_4K\_30fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、

D0\_VOD、D1\_VOD、D2\_VOD = 7h)**

| インデックス | テスト名称                                  | レン   | 仕様範囲                 | 測定値     | 結果  |

|--------|----------------------------------------|------|----------------------|---------|-----|

| 1      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D1+  | 2.700V < VL < 2.900V | 2.6334V | 不合格 |

| 2      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D2+  | 2.700V < VL < 2.900V | 2.6755V | 不合格 |

| 3      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D1-  | 2.700V < VL < 2.900V | 2.6125V | 不合格 |

| 4      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D2-  | 2.700V < VL < 2.900V | 2.6654V | 不合格 |

| 5      | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D1+  | 2.600V < VL < 2.900V | 2.6334V | 合格  |

| 6      | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D2+  | 2.600V < VL < 2.900V | 2.6755V | 合格  |

| 7      | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D1-  | 2.600V < VL < 2.900V | 2.6125V | 合格  |

| 8      | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D2-  | 2.600V < VL < 2.900V | 2.6654V | 合格  |

| 9      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | CK+  | 2.700V < VL < 2.900V | 2.6500V | 不合格 |

| 10     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D0+  | 2.700V < VL < 2.900V | 2.6750V | 不合格 |

| 11     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | CK - | 2.700V < VL < 2.900V | 2.6328V | 不合格 |

| 12     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート)      | D0-  | 2.700V < VL < 2.900V | 2.6392V | 不合格 |

| 13     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | CK+  | 2.600V < VL < 2.900V | 2.6483V | 合格  |

| 14     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D0+  | 2.600V < VL < 2.900V | 2.6750V | 合格  |

| 15     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | CK - | 2.600V < VL < 2.900V | 2.6328V | 合格  |

| 16     | 7-2:ソース Low 振幅 + (サポートされるシンク > 165MHz) | D0-  | 2.600V < VL < 2.900V | 2.6392V | 合格  |

### 3.3.3 解像度 720 x 480\_60p\_8bit\_444 での HDMI 1.4 テスト

3.3.3.1 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing、CLK\_VOD、D0\_VOD/D1\_VOD、D2\_VOD = 0h での値を使用、-15 を制限します)

**表 3-10. HDMI1.4\_480p\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、

D0\_VOD、D1\_VOD、D2\_VOD = 0h)**

| インデックス | テスト名称                             | レン  | 仕様範囲                  | 測定値     | 結果 |

|--------|-----------------------------------|-----|-----------------------|---------|----|

| 1      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1+ | 2.700V < VL < 2.900V; | 2.8169V | 合格 |

**表 3-10. HDMI1.4\_480p\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 0h (続き)**

| インデックス | テスト名称                             | レーン  | 仕様範囲                  | 測定値     | 結果 |

|--------|-----------------------------------|------|-----------------------|---------|----|

| 2      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2+  | 2.700V < VL < 2.900V; | 2.8570V | 合格 |

| 3      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1-  | 2.700V < VL < 2.900V; | 2.8077V | 合格 |

| 4      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2-  | 2.700V < VL < 2.900V; | 2.8340V | 合格 |

| 5      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK+  | 2.700V < VL < 2.900V; | 2.8318V | 合格 |

| 6      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0+  | 2.700V < VL < 2.900V; | 2.8431V | 合格 |

| 7      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK - | 2.700V < VL < 2.900V; | 2.8260V | 合格 |

| 8      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0-  | 2.700V < VL < 2.900V; | 2.8279  | 合格 |

### 3.3.3.2 HDMI20\_VOD = 1h (デフォルト 1000mV)、HDMI14\_VOD = 1h (デフォルト 1000mV) での VL および VSwing

**表 3-11. HDMI1.4\_480p\_60fps テスト VL および VSwing (HDMI20\_VOD = 1h、HDMI14\_VOD = 1h)**

| インデックス | テスト名称                             | レーン  | 仕様範囲                 | 測定値     | 結果 |

|--------|-----------------------------------|------|----------------------|---------|----|

| 18     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK+  | 2.700V < VL < 2.900V | 2.7825V | 合格 |

| 19     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0+  | 2.700V < VL < 2.900V | 2.7928V | 合格 |

| 20     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK - | 2.700V < VL < 2.900V | 2.7701V | 合格 |

| 21     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0-  | 2.700V < VL < 2.900V | 2.7768V | 合格 |

| 22     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1+  | 2.700V < VL < 2.900V | 2.7574V | 合格 |

| 23     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2+  | 2.700V < VL < 2.900V | 2.8016V | 合格 |

| 24     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1-  | 2.700V < VL < 2.900V | 2.7452V | 合格 |

| 25     | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2-  | 2.700V < VL < 2.900V | 2.7793V | 合格 |

3.3.3.3 HDMI20\_VOD = 0h、HDMI14\_VOD = 0h での VL および VSwing は、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 7h に値を使用、+20% を制限します)

**表 3-12. HDMI1.4\_480p\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 7h)**

| インデックス | テスト名称                             | レーン | 仕様範囲                 | 測定値     | 結果  |

|--------|-----------------------------------|-----|----------------------|---------|-----|

| 1      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1+ | 2.700V < VL < 2.900V | 2.6945V | 不合格 |

**表 3-12. HDMI1.4\_480p\_60fps テスト VL および VSwing (HDMI20\_VOD = 0h、HDMI14\_VOD = 0h、CLK\_VOD、D0\_VOD、D1\_VOD、D2\_VOD = 7h) (続き)**

| インデックス | テスト名称                             | レーン  | 仕様範囲                 | 測定値     | 結果  |

|--------|-----------------------------------|------|----------------------|---------|-----|

| 2      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2+  | 2.700V < VL < 2.900V | 2.7438V | 合格  |

| 3      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D1-  | 2.700V < VL < 2.900V | 2.6834V | 不合格 |

| 4      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D2-  | 2.700V < VL < 2.900V | 2.7200  | 合格  |

| 5      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK+  | 2.700V < VL < 2.900V | 2.7054V | 合格  |

| 6      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0+  | 2.700V < VL < 2.900V | 2.7282V | 合格  |

| 7      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | CK - | 2.700V < VL < 2.900V | 2.7028V | 合格  |

| 8      | 7-2:ソース低振幅 + (シンク ≤ 165MHz をサポート) | D0-  | 2.700V < VL < 2.900V | 2.7074V | 合格  |

注:異なる解像度の VL 仕様は、HDMI 1.4 で異なりました。

シングルエンドの low レベル出力電圧、VL

取り付けられたシンク サポートのみ <= 165MHz: (AVcc – 600mV) ≤ VL ≤ (AVcc – 400mV)

取り付けられているシンク サポートのみ > 165MHz: (AVcc – 700mV) ≤ VL ≤ (AVcc – 400mV)

### 3.4 HDMI1.4-2.0 合格コンプライアンス テスト パスの結果

#### 3.4.1 解像度 4096x2160\_60p\_8bit\_444 での HDMI2.0 テスト

| TekExpress HDM<br>Source Test Report |                                 |                         |                  |

|--------------------------------------|---------------------------------|-------------------------|------------------|

| Setup Information                    |                                 |                         |                  |

| DUT ID                               | DUT001                          | Scope Model             | DPO73304SX       |

| Date/Time                            | 2025-03-21 17:14:26             | Scope Serial Number     | B010266          |

| Device Type                          | HDM Physical Layer Solution     | SPC, FactoryCalibration | PASS;PASS        |

| App Version                          | 10.3.5.6                        | Scope F/W Version       | 10.14.1 Build 15 |

| TekExpress Version                   | 4.16.0.20                       | DPOJET Version          | 10.5.0.9         |

| Spec Version                         | CTS 2.0                         | Ch1 Deskew Time (s)     | 0.000000         |

| Overall Compliance Mode              | Yes                             | Ch2 Deskew Time (s)     | 0.000000         |

| Execution Mode                       | Live                            | Ch3 Deskew Time (s)     | 0.000000         |

| Overall Execution Time               | 0:47:10                         | Ch4 Deskew Time (s)     | 0.000000         |

| Overall Test Result                  | Pass                            | Probe1 Model            | P7313SMA         |

|                                      |                                 | Probe1 Serial Number    | B022547          |

|                                      |                                 | Probe2 Model            | P7313SMA         |

|                                      |                                 | Probe2 Serial Number    | B010379          |

|                                      |                                 | Probe3 Model            | P7313SMA         |

|                                      |                                 | Probe3 Serial Number    | B022271          |

|                                      |                                 | Probe4 Model            | P7313SMA         |

|                                      |                                 | Probe4 Serial Number    | B022549          |

| DUT COMMENT:                         | General Comment – HDM2.0 Source |                         |                  |

| Test Name Summary Table                               |        |                |

|-------------------------------------------------------|--------|----------------|

| Test Name                                             | Result | Execution Time |

| <a href="#">HFI-2_TRISE, TFALL</a>                    | Pass   | 0:09:19        |

| <a href="#">HFI-5_Differential Voltage</a>            | Pass   | 0:06:20        |

| <a href="#">HFI-6_Clock Duty Cycle and Clock Rate</a> | Pass   | 0:02:01        |

| <a href="#">HFI-3_Inter-Pair Skew</a>                 | Pass   | 0:31:18        |

| <a href="#">HFI-7_Clock Jitter</a>                    | Pass   | 0:01:02        |

| <a href="#">HFI-1_VL and Vswing</a>                   | Pass   | 0:18:20        |

| <a href="#">HFI-4_Intra-Pair Skew</a>                 | Pass   | 0:12:57        |

| <a href="#">HFI-8_Data Eye Diagram</a>                | Pass   | 0:15:46        |

図 3-16. HDMI2.0\_4K\_60fps 全体のパス結果

### 3.4.2 解像度 4096x2160\_30p\_8bit\_444 での HDMI 1.4 テスト

HDMI Compliance Test Software: Measurement Report

Tektronix®

Enabling Innovation

Fri Mar 28 08:52:14 GMT 2025

## Source Tests Report

#### ▶ Configuration

##### ▶ Setup Configuration

|                   |                              |

|-------------------|------------------------------|

| Oscilloscope Info | DPO73304S - 10.14.1 Build 15 |

| TDSHT3 Version    | 5.4.0 Build 8                |

##### ▶ Device Configuration

|                      |             |

|----------------------|-------------|

| Device Details       | HDMI Device |

| Clock Frequency(Mhz) | 297.077     |

| Resolution           | 4096x2160   |

| Refresh Rate         | 30Hz        |

##### ▶ Compliance Summary

|                       |    |

|-----------------------|----|

| Total Tests Supported | 9  |

| Tests Completed       | 37 |

| Pass                  | 37 |

| Fail                  | 0  |

図 3-17. HDMI1.4\_4K\_30fps 全体のパス結果

### 3.4.3 解像度 720 x 480\_60p\_8bit\_444 での HDMI 1.4 テスト

HDMI Compliance Test Software: Measurement Report

Tektronix®

Enabling Innovation

Wed Apr 02 07:23:26 GMT 2025

## Source Tests Report

#### ▶ Configuration

##### ▶ Setup Configuration

|                   |                              |

|-------------------|------------------------------|

| Oscilloscope Info | DPO73304S - 10.14.1 Build 15 |

| TDSHT3 Version    | 5.4.0 Build 8                |

##### ▶ Device Configuration

|                      |             |

|----------------------|-------------|

| Device Details       | HDMI Device |

| Clock Frequency(Mhz) | 27.0288     |

| Resolution           | 720x480p    |

| Refresh Rate         | 60Hz        |

##### ▶ Compliance Summary

|                       |    |

|-----------------------|----|

| Total Tests Supported | 9  |

| Tests Completed       | 29 |

| Pass                  | 29 |

| Fail                  | 0  |

図 3-18. HDMI1.4\_480p\_60fps 全体のパス結果

## 4 ヒント

TDP0604 は、DDC 読み取り/書き込みまたは I<sub>C</sub> 書き込みによってスヌーピングされた最後の値を読み出します。I<sub>C</sub> ホストを使用して、SCDC\_TMDS\_CONFIG レジスタ（オフセット = 20h）の TMDS\_CLK\_RATIO [1] ビットを読み出し、正しい TMDS クロック周期比を求めます。

**表 4-1. TMDS\_CLK\_Ratio ビット**

| ビット | フィールド          | タイプ  | リセット | 説明                                                                                   |

|-----|----------------|------|------|--------------------------------------------------------------------------------------|

| 7-2 | 予約済み           | R    | 0h   | 予約済み                                                                                 |

| 1   | TMDS_CLK_RATIO | RH/W | 0h   | TMDS ビット周期と TMDS クロック周期比。DC 読み取り/書き込みまたは I <sub>C</sub> 書き込みによってスヌーピングされた最後の値を読み取ります |

| 0   | 予約済み           | R    | 0h   | 予約済み                                                                                 |

読み取り値が HDMI2.0 クロック比のとき：

|                         |                |      |   |     |     |      |   |                   |

|-------------------------|----------------|------|---|-----|-----|------|---|-------------------|

| 2025-03-28 19:30:46.191 | I <sub>C</sub> | ReqW | M | --- | 100 | 0X5E | 1 | 20 (Req. Address) |

| 2025-03-28 19:30:46.191 | I <sub>C</sub> | ReqR | M | --- | 100 | 0X5E | 1 | 02                |

**図 4-1. TMDS\_CLK\_RATIO = 1**

読み出しが HDMI 1.4 クロック比の場合：

|                         |                |      |   |     |     |      |   |                   |

|-------------------------|----------------|------|---|-----|-----|------|---|-------------------|

| 2025-03-27 19:51:40.611 | I <sub>C</sub> | ReqW | M | --- | 100 | 0X5E | 1 | 20 (Req. Address) |

| 2025-03-27 19:51:40.611 | I <sub>C</sub> | ReqR | M | --- | 100 | 0X5E | 1 | 00                |

**図 4-2. TMDS\_CLK\_RATIO = 0**

## 5 まとめ

TDP0604 は、ソースとシンクの両方のアプリケーションをサポートするハイブリッド リドライバです。ハイブリッド リドライバは、リニア リドライバ機能とリミッティング リドライバ機能のどちらでも動作できます。また、このデバイスは豊富で柔軟な調整機能を備えており、EQ、立ち上がり/立ち下がりスルーレート、VL、VSwing など、さまざまなデータレート (HDMI 1.4 または 2.0) に微調整できます。

この記事では、実際の調整を使用して、テスト中にさまざまなパラメータ調整によって生成される結果と影響を示します。これにより、認定テストに合格するためにテストの失敗が発生したときに調整できるパラメータ、または必要なパラメータを理解しやすくなります。

## 6 参考資料

1. テキサス インstrument、[TDP0604 6 Gbps DC または AC 結合 HDMI 2.0 レベルシフター ハイブリッド リドライバ](#)、データシート。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月