## Application Note

## PLL デバイスの発振器電源の考慮事項

Jennifer Bernal

Clock and Timing Solutions

## 概要

電源ノイズ除去 (PSNR) が不十分な発振器は、ノイズの多い電源の影響を受けやすく、発振器出力とアナログ フェーズ ロック ループ (APLL) 出力の両方で位相ノイズを劣化させる可能性があります。LMK6Cx や CDC6Cx などの発振器は、LDO を内蔵することで電源設計を簡素化します。発振器電源フィルタを強化すると、出力クロックの位相ノイズがさらに低減されます。電源の柔軟性が限られているシステムでは、LMK5B33216 などの高性能ネットワークシンクロナイザを使用することで、内部 LDO を使用して発振器に電力を供給することで、ノイズの多い電源でも低ジッタのクロックを生成できます。さらに、BAW ベースのジッタクリーナを使用することで、狭いループ帯域幅で APLL 構成を可能にし、発振器が APLL の出力クロックに及ぼす影響を最小限に抑えることができます。

## 目次

|                             |    |

|-----------------------------|----|

| 1はじめに.....                  | 2  |

| 2発振器ノイズが PLL 性能に及ぼす影響.....  | 3  |

| 3検討事項 1:XO PSNR.....        | 4  |

| 4検討事項 2:XO 電源フィルタ.....      | 5  |

| 5検討事項 3:APLL LBW.....       | 6  |

| 6各種 XO 電源フィルタに関するテスト結果..... | 6  |

| 6.1 テスト設定.....              | 6  |

| 6.2 電源の性能に及ぼす影響.....        | 7  |

| 6.3 XO 位相ノイズ性能への影響.....     | 8  |

| 6.4 PLL 位相ノイズ性能への影響.....    | 10 |

| 7まとめ.....                   | 12 |

## 図の一覧

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| 図 1-1. ネットワークシンクロナイザの一般的なブロック図.....                                   | 2  |

| 図 2-1. ネットワークシンクロナイザ (DPLL および APLL) 出力クロックの一般的な位相ノイズプロット.....        | 3  |

| 図 3-1. LMK6C および CDC6C 発振器の機能ブロック図.....                               | 4  |

| 図 4-1. TPS62913 の機能ブロック図.....                                         | 5  |

| 図 6-1. TPS62913 電源性能、C <sub>NR/SS</sub> 変動.....                       | 7  |

| 図 6-2. XO 位相ノイズ、C <sub>NR/SS</sub> 変動、TPS62913 電源.....                | 8  |

| 図 6-3. TPS62913 電源による XO テストのセットアップ.....                              | 8  |

| 図 6-4. XO 位相ノイズ、C <sub>NR/SS</sub> 変動、LMK5B33216 電源.....              | 9  |

| 図 6-5. LMK5B33216 電源による XO テストのセットアップ.....                            | 9  |

| 図 6-6. LMK5B33216 位相ノイズ、C <sub>NR/SS</sub> 変動、TPS62913 電源付き XO.....   | 10 |

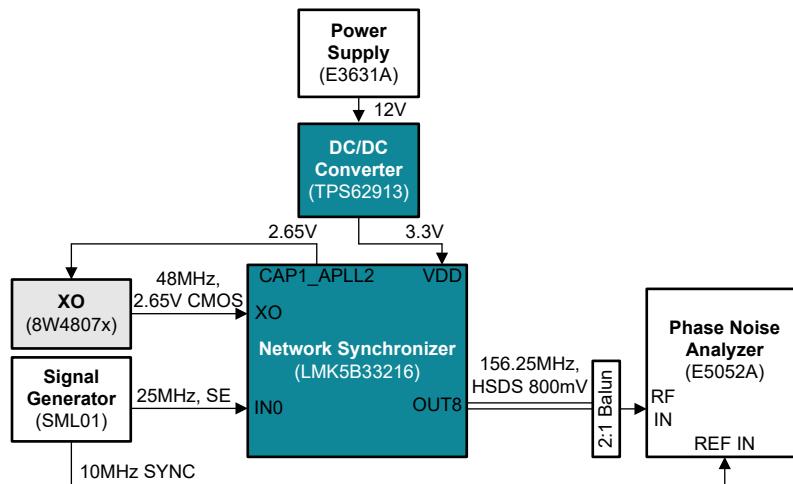

| 図 6-7. LMK5B33216 テストのセットアップ、TPS62913 電源付き XO.....                    | 10 |

| 図 6-8. LMK5B33216 位相ノイズ、C <sub>NR/SS</sub> 変動、LMK5B33216 電源付き XO..... | 11 |

| 図 6-9. LMK5B33216 テストセットアップ、LMK5B33216 電源付き XO.....                   | 11 |

## 表の一覧

|                                |   |

|--------------------------------|---|

| 表 3-1. CDC6C 発振器の PSNR 特性..... | 4 |

| 表 6-1. テストに使用した部品.....         | 6 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

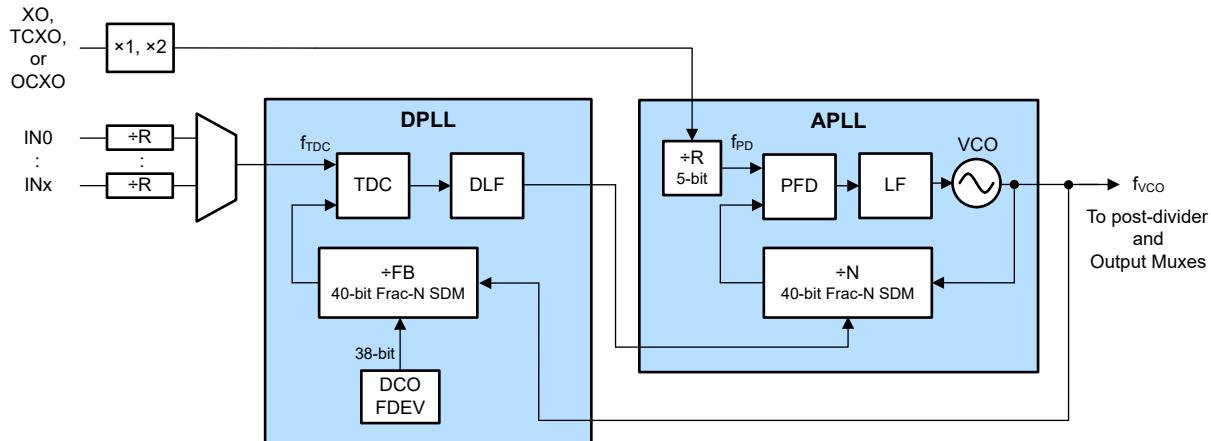

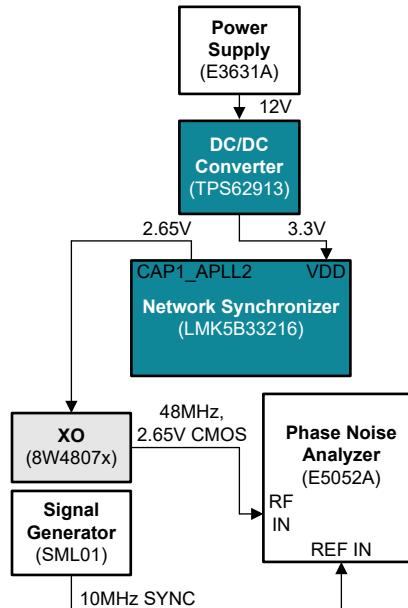

APLL は、入力に同期した出力クロックを生成するために使用されるクロッキング デバイスです。通常、APLL リファレンスは、水晶発振器 (XO)、温度制御発振器 (TCXO)、またはオーブン制御発振器 (OCXO) のいずれかによって供給されます。図 1-1 に、デジタルフェーズロックループ (DPLL) と APLL のペアで構成されるネットワークシンクロナイザのブロック図を示します。APLL 入力クロックは、フリーランまたは長期ホールドオーバー時の PLL 出力クロックの周波数精度と安定性を提供します。

図 1-1. ネットワークシンクロナイザの一般的なブロック図

PLL 出力の近接位相ノイズ (10kHz 未満のオフセット) は、APLL リファレンス (XO、TCXO、または OCXO) の品質に依存します。APLL リファレンスの電源も、出力クロックの品質に影響を及ぼす可能性があります。電源にノイズが多い場合、PLL 出力クロックの位相ノイズが劣化する可能性があります。次のセクションでは、発振器の電源が PLL の性能にどのような影響を及ぼすか、またクロック設計を最適化する方法について説明します。

### 注

このアプリケーションノートの以後の部分では、「XO」という用語を使用して説明しますが、この概念は任意の XO、TCXO、OCXO、またはその他の APLL 基準クロックソースに適用されます。

## 2 発振器ノイズがPLL性能に及ぼす影響

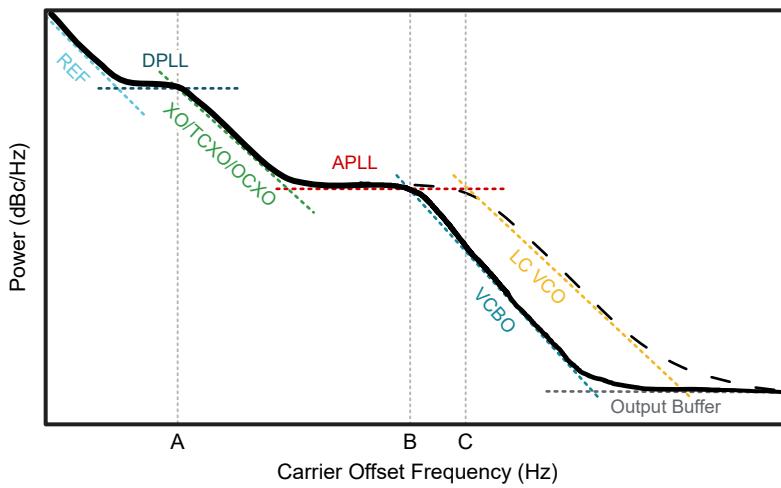

図2-1に、ネットワークシンクロナイザ出力クロックの位相ノイズの影響を示します。APLLループ帯域幅(LBW)までの範囲で、シンクロナイザ出力ノイズは、XO出力ノイズとAPLLノイズに起因します。これは、APLL出力がAPLL LBW(マークA/B/C)より低いXOノイズに敏感であることを意味します。XO出力ノイズは通常、APLL出力の近接位相ノイズを支配します。たとえば、APLL LBWが5kHzに設定されている場合、XOノイズは5kHzのオフセットよりも低いAPLL出力クロックよりも優先されます。5kHzを超えると、APLLループフィルタはXOノイズを低減します。DPLLを備えたデバイスの場合、DPLL LBWとAPLL LBWの間(マークAとB/Cの間)にXOノイズとAPLLノイズが支配的になります。

XOノイズプロファイルがVCOノイズよりも優れている場合は、広いLBW(>10kHzのオフセット)でAPLLを構成し、VCOノイズを低減します。XOノイズがVCOノイズよりも悪化するほとんどのアプリケーションでは、狭いLBW(オフセット10kHz未満)を使用します。

- A. DPLL LBWをマークします (LMK5B33216で1mHz ~ 4kHzに設定可能)

- B. VCBOのAPLL LBWをマークします (LMK5B33216で1kHz ~ 10kHzに設定可能)

- C. LC VCOのAPLL LBWをマークします (LMK5B33216で100kHz ~ 1MHzに設定可能)

図2-1. ネットワークシンクロナイザ(DPLLおよびAPLL)出力クロックの一般的な位相ノイズプロット

PLL出力クロックの位相ノイズの詳細については、[112Gおよび224G PAM4 SerDesクロッキング、高速データセンタースイッチ用](#)アプリケーションノートの位相ノイズプロファイルセクションを参照します。

### 3 検討事項 1:XO PSNR

PLL の重要な設計要素の 1 つは、XO の PSNR 性能です。PSNR は、XO 出力が電源ノイズの影響を受ける程度を定義します。PSNR が低い XO は、ノイズが大きくなり、PLL 出力ノイズが悪化する可能性があります。

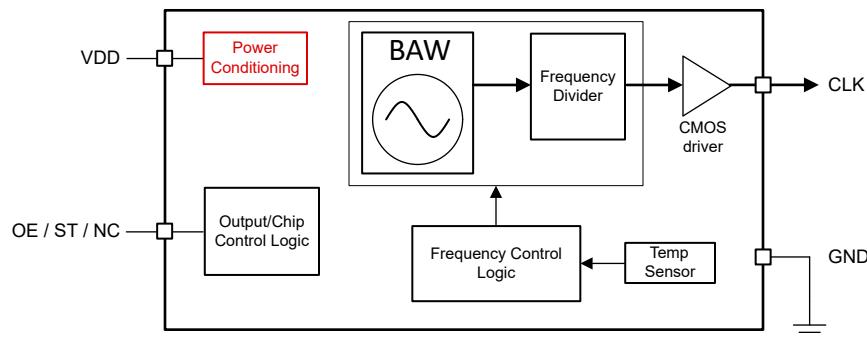

推奨される方法は、適切な PSNR または内蔵 LDO と組み合わせた XO を使用することです。たとえば、**LMK6C** および **CDC6C** 発振器には内部 LDO が内蔵されて、図 3-1 および 表 3-1 に示すように優れた PSNR が得られます。これらの機能を持つ発振器を使用すると、電源ノイズを低減し、低ノイズの出力クロックを供給できます。このアプローチは、設計の初期段階や、電源フィルタを変更できないシステムに有益です。

図 3-1. LMK6C および CDC6C 発振器の機能ブロック図

表 3-1. CDC6C 発振器の PSNR 特性

| 電源リップル周波数 <sup>(1)</sup> [kHz] | 誘導スプリアス、標準値 [dBc] |       |

|--------------------------------|-------------------|-------|

|                                | LMK6C             | CDC6C |

| 50                             | -72               | -80   |

| 100                            | -71               | -75   |

| 500                            | -70               | -63   |

| 1000                           | -69               | -59   |

(1) 50MHz LVC MOS 出力クロックに印加された 50mV 電源リップルにより誘導されるスプリアス、VDD = 2.5V (LMK6C) または 2.5V/3.3V (CDC6C)、電源デカップリング キャパシタなし

または、**LMK5B33216** は外部 XO に電力を供給し、ノイズの多い電源で低ジッタ出力を実現できます。**LMK5B33216** は、3 つの DPLL および APLL ペアを備えたネットワークシンクロナイザおよびジッタクリーナです。各 VDD および VDDO ピンには LDO が内蔵されて、PSNR の改善と出力ノイズの最小化を実現します。ピン 22 (CAP1\_APLL2) は APLL2 の LDO 出力で、XO への電力供給に使用でき、公称 2.65V を供給し、最大 20mA を供給します。

LMK5B33216 を使用した XO 位相ノイズ性能への影響に関するテストデータについては、該当するセクションで説明します。結果は、CAP1\_APLL2 が非常に優れた PSNR を備え、電源フィルタに関係なく、低ジッタの XO 出力を供給することを示しています。

## 4 検討事項 2:XO 電源フィルタ

もう 1 つの重要な要因は、XO で使用する電源フィルタ（コンデンサ、フェライトビーズなど）です。適切なフィルタ処理を行わないと、XO 位相ノイズが低下する可能性があります。

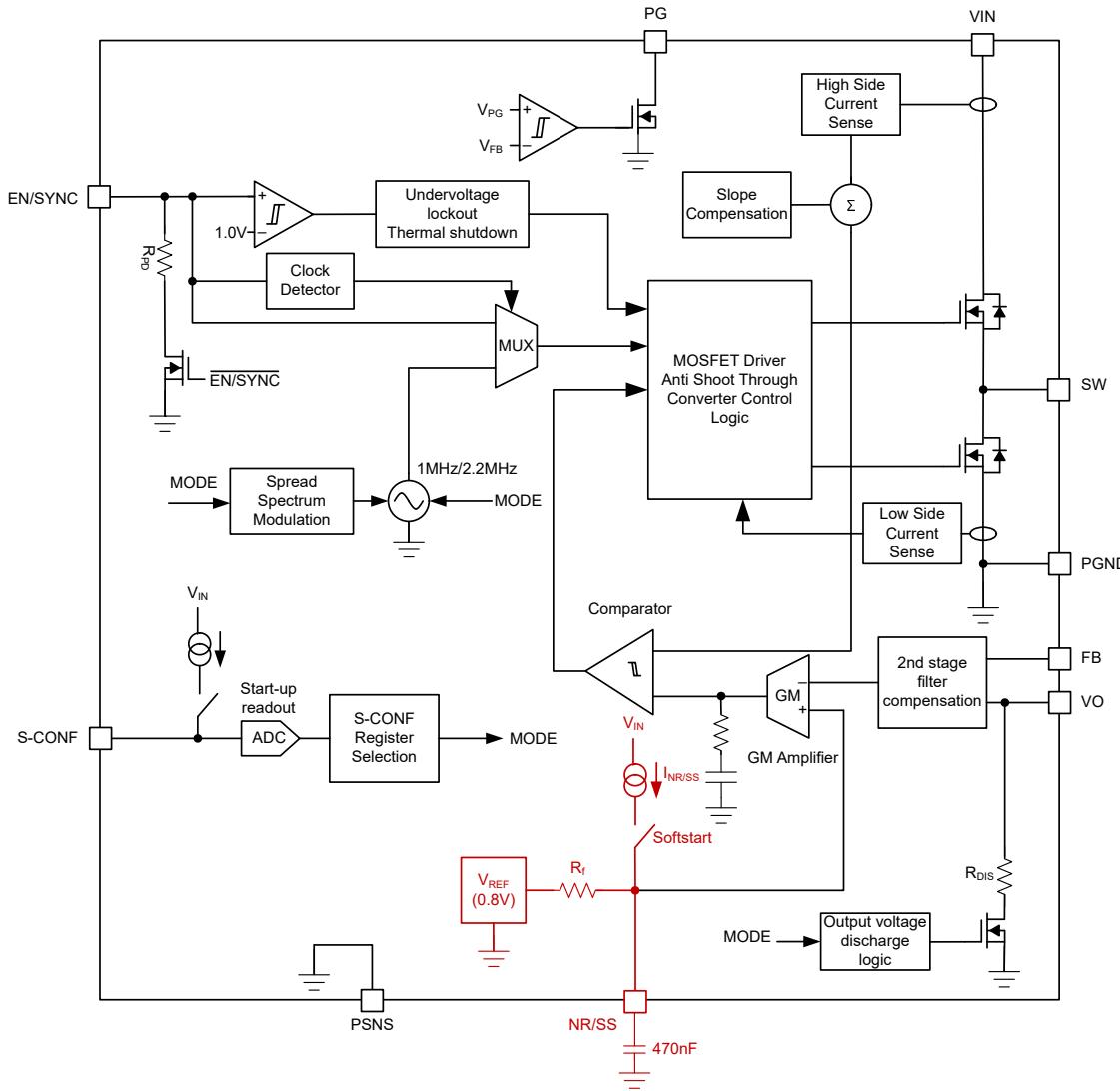

XO 電源ノイズを低減するため、ノイズリダクション（NR）ピンを持つ電源を推奨します。電源として、LDO またはスイッチング DC/DC コンバータの IC を使用できます。バイパスコンデンサを電源電圧リファレンスに接続するには、NR ピンが必要です。バイパスコンデンサから形成された RC フィルタにより、低周波（10kHz 未満）ノイズが低減されます。多くの TI 電源では、コンデンサに  $C_{NR/SS}$  というラベルが付いており、ソフトスタート（SS）時間を設定します。たとえば、TPS62913 は NR ピンを利用できる DC/DC コンバータです。図 4-1 に、ブロック図を示し、NR ピンを強調しています。

電源性能への影響 および XO 位相ノイズ性能への影響に関するテストデータについては、それぞれのセクションで説明します。これらの結果は、適切に設計された XO 電源により、最高の RMS ジッタ性能が得られることを示しています。

図 4-1. TPS62913 の機能ブロック図

## 5 検討事項 3:APLL LBW

もう 1 つのベストプラクティスは、[LMK5B33216](#) などの狭い LBW を持つ高性能 PLL を使用して、ノイズの多い XO が PLL 出力に及ぼす影響を低減することです。さらに最適化を進めるために、XO、APLL、VCO のノイズプロファイルを比較し、最適な APLL LBW 設定を決定します。

このデバイスは、電圧制御 BAW 発振器 (VCBO) を使用することで、47fs (標準値) の RMS ジッタで 156.25MHz 出力を生成できます。APLL を狭い LBW で動作させることで、低ノイズ出力が実現され、VCBO は 8kHz を超える位相ノイズオフセットで優勢です。VCBO により、このデバイスは 12kHz ~ 20MHz の範囲で PLL 出力ジッタを劣化させることなく、高ジッタの XO を使用できます。

[PLL 位相ノイズ性能への影響](#)に関するテストデータについては、該当するセクションで説明します。結果から、ノイズの多い XO を使用する場合、狭い LBW 設定で最適な RMS ジッタ性能が得られることがわかります。または、[LMK5B33216](#) を使用して XO に電力を供給する場合、ループ帯域幅に関係なくクリーンな XO 出力を実現することもできます。

## 6 各種 XO 電源フィルタに関するテスト結果

以下のサブセクションでは、3 つのテスト条件のテスト結果を示します：

1. [電源性能への影響](#)を確認するための各種 XO 電源フィルタ。

2. [XO の位相ノイズ性能への影響](#)を確認するための各種 XO 電源フィルタ。

3. [PLL の位相ノイズ性能への影響](#)を確認するための各種 XO 電源フィルタ。

### 6.1 テスト設定

各テストで、 $C_{NR/SS}$  値を調整して、各種の XO 電源フィルタをモデル化します。各値によって、固有の XO ノイズプロファイルが作成されます。[表 6-1](#) に、テストで使用されたデバイスを示します。

表 6-1. テストに使用した部品

| ベンダ | 部品番号       | 説明              | 入力電源電圧 (v) | 出力電源電圧 (v) | 出力クロック スイング (v)           | 周波数 [MHz]            |

|-----|------------|-----------------|------------|------------|---------------------------|----------------------|

| TI  | TPS62913   | DC/DC 電源        | 12         | 3.3        | —                         | 2.2 ( $f_{SW}$ )     |

| TXC | 8W48070009 | XO              | 1.8~3.3    | —          | 3.3                       | 48 ( $f_{OUT}$ )     |

| TI  | LMK5B33216 | ネットワーク シンク ロナイザ | 3.3        | —          | 0.8 ( $V_{OH} - V_{OL}$ ) | 156.25 ( $f_{OUT}$ ) |

## 6.2 電源の性能に及ぼす影響

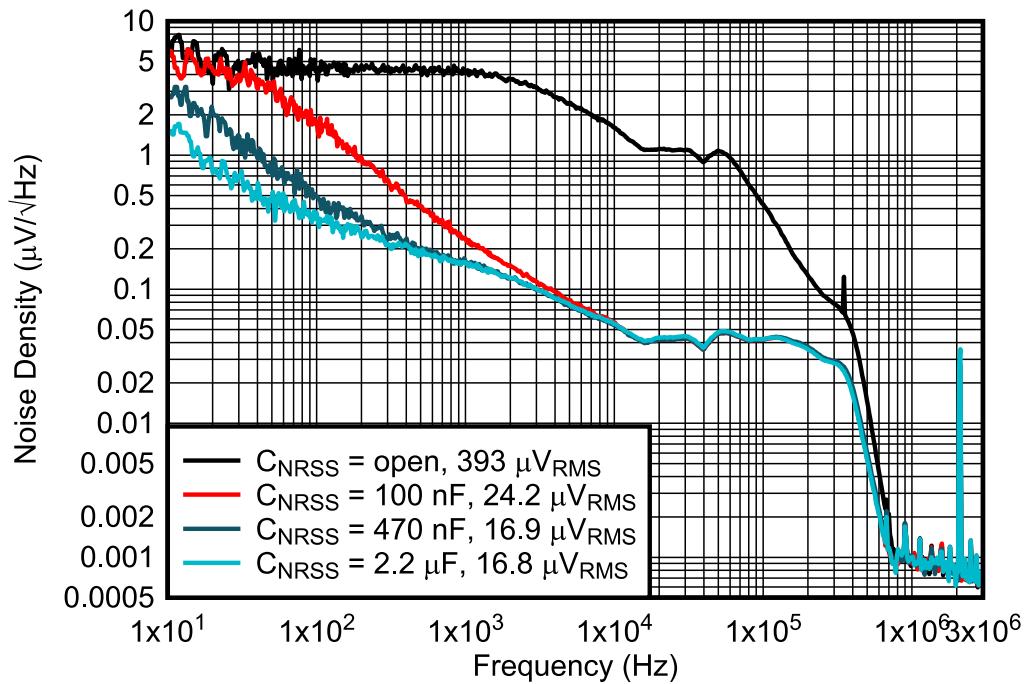

XO 電源フィルタを適切に設計して低周波ノイズを低減することにより、最良の XO および PLL 出力性能を実現しています。図 6-1 に、さまざまなノイズプロファイルにわたる出力電力ノイズ密度を示します。XO 電源フィルタがない場合 ( $C_{NR/SS}$  なし)、ノイズは 100Hz ~ 100kHz の間で大幅に増加します。推奨の 470nF のフィルタ値では、電源ノイズは  $4.6\mu V/\sqrt{Hz}$  に向上します。

$L = 2.2\mu H$ ,  $f_{SW} = 2.2\text{MHz}$ ,  $BW = 100\text{Hz} \sim 100\text{kHz}$

このデータは、12V の電源入力電圧と 3.3V の出力電圧で収集されます。

ノイズは、TPS62913 の  $V_{OUT}$  のフェライトビーズ フィルタを使用して測定します。

図 6-1. TPS62913 電源性能、 $C_{NR/SS}$  変動

### 6.3 XO 位相ノイズ性能への影響

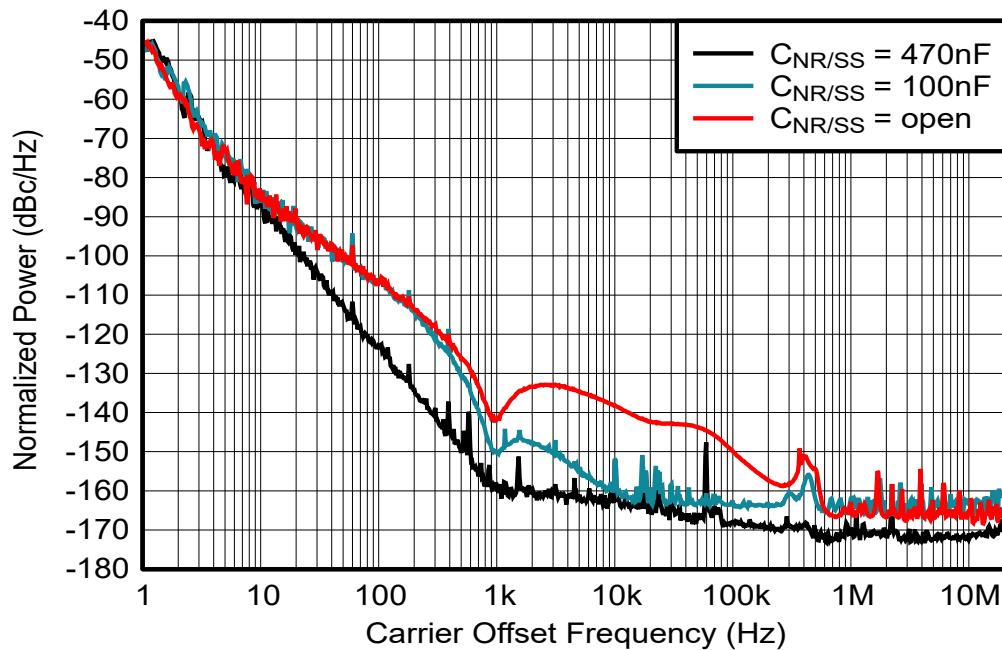

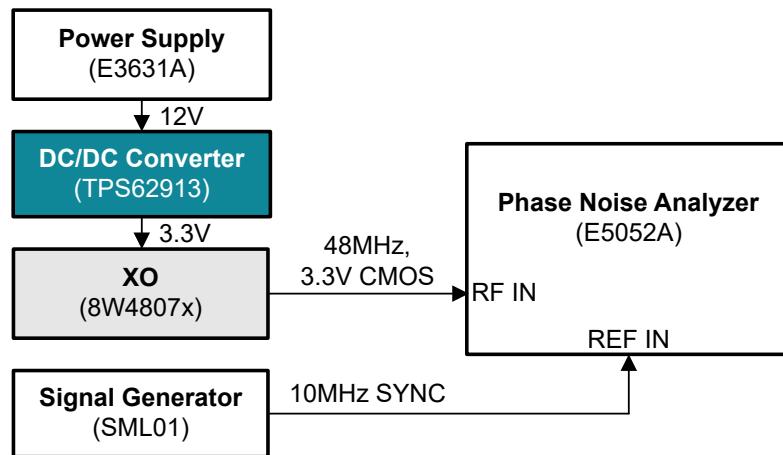

XO 出力クロックの位相ノイズを測定する方法で、XO 電源フィルタの影響をさらに調べます。図 6-2 に、さまざまなノイズプロファイルにわたる位相ノイズを示し、図 6-3 に測定の設定を示します。電源フィルタリングがほとんど、またはまったくフィルタリングされていない状態で、RMS ジッタは 2 倍以上になります。推奨の 470nF のフィルタ値により、XO 位相ノイズプロアは 1kHz ~ 100kHz のオフセットで 20dB 向上します。

| $C_{NR/SSx}$ (nF) | 12kHz ~ 20MHz (fs) の範囲での RMS ジッタ (標準値) |

|-------------------|----------------------------------------|

| 470               | 62                                     |

| 100               | 152                                    |

| 0 (オープン)          | 158                                    |

図 6-2. XO 位相ノイズ、 $C_{NR/SS}$  変動、TPS62913 電源

図 6-3. TPS62913 電源による XO テストのセットアップ

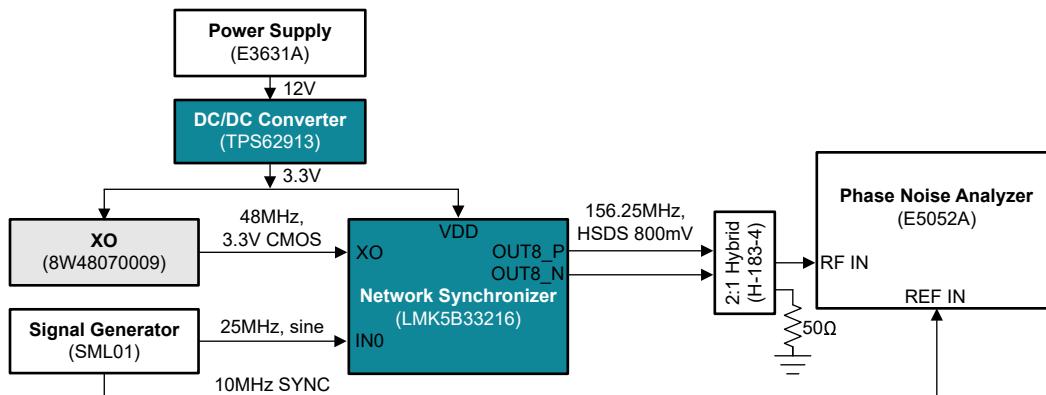

LMK5B33216 を使用して XO に電力を供給することで、電源フィルタに関係なく低ノイズ XO 出力を実現できます。図 6-4 に LMK5B33216 から電力を供給したときの XO 位相ノイズを示し、図 6-5 にテスト構成を示します。

| $C_{NR/SS_x}$ [nF] | 12kHz ~ 20MHz [fs] の範囲での RMS ジッタ (標準値) |

|--------------------|----------------------------------------|

| 470                | 61                                     |

| 100                | 61                                     |

| 0 (オープン)           | 61                                     |

図 6-4. XO 位相ノイズ、 $C_{NR/SS}$  変動、LMK5B33216 電源

図 6-5. LMK5B33216 電源による XO テストのセットアップ

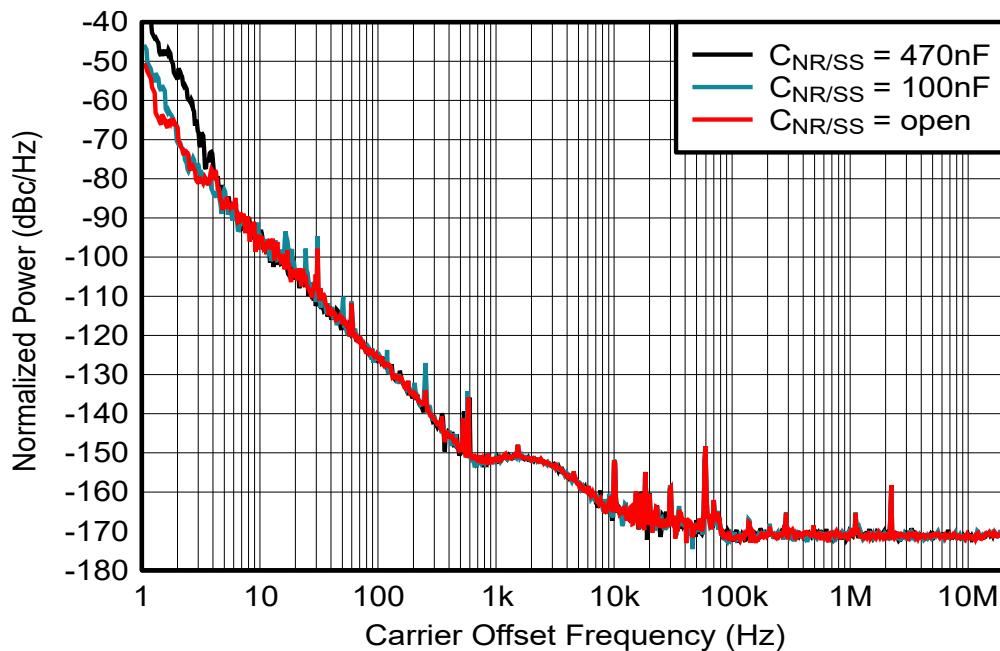

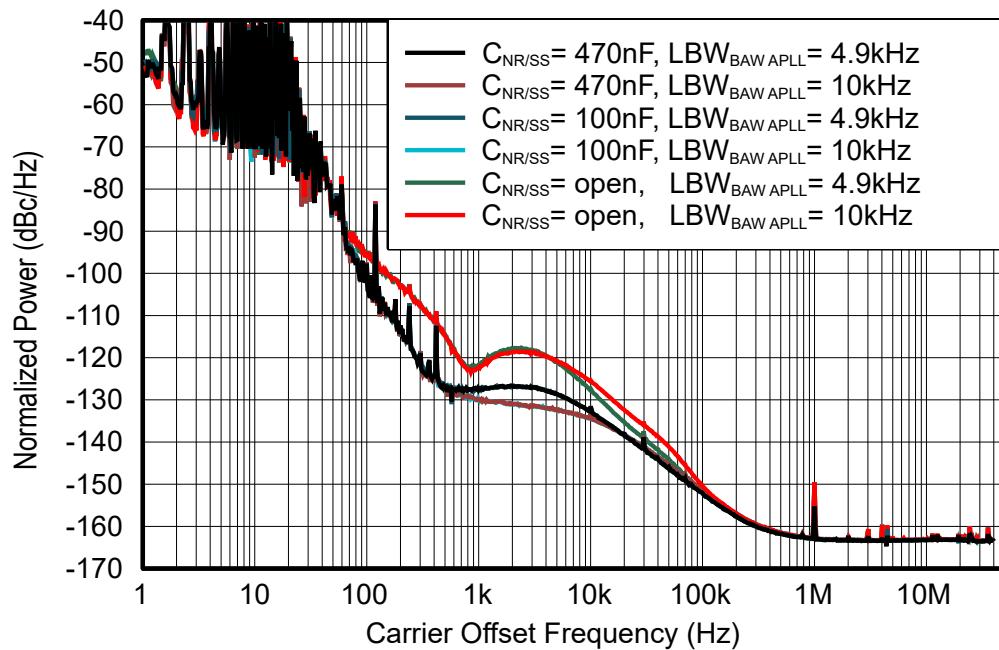

## 6.4 PLL 位相ノイズ性能への影響

図 6-6 は、APLL に APLL の LBW が狭いとき、ノイズの多い XO 電源 ( $C_{NR/SS} = \text{オープン}$ ) による RMS ジッタへの影響が最小限に抑えられることを示しています。図 6-7 に測定の設定を示します。適切な XO 電源フィルタを使用すると、PLL 出力ノイズはさらに改善されます (20fs)。

| $C_{NR/SS}$ (nF) | $LBW_{BAW APLL}$ (kHz) | 12kHz ~ 20MHz (fs) の範囲での RMS ジッタ (標準値) |

|------------------|------------------------|----------------------------------------|

| 470              | 4.9                    | 54                                     |

| 470              | 10                     | 56                                     |

| 100              | 4.9                    | 54                                     |

| 100              | 10                     | 56                                     |

| 0 (オープン)         | 4.9                    | 62                                     |

| 0 (オープン)         | 10                     | 75                                     |

図 6-6. LMK5B33216 位相ノイズ、 $C_{NR/SS}$  変動、TPS62913 電源付き XO

図 6-7. LMK5B33216 テストのセットアップ、TPS62913 電源付き XO

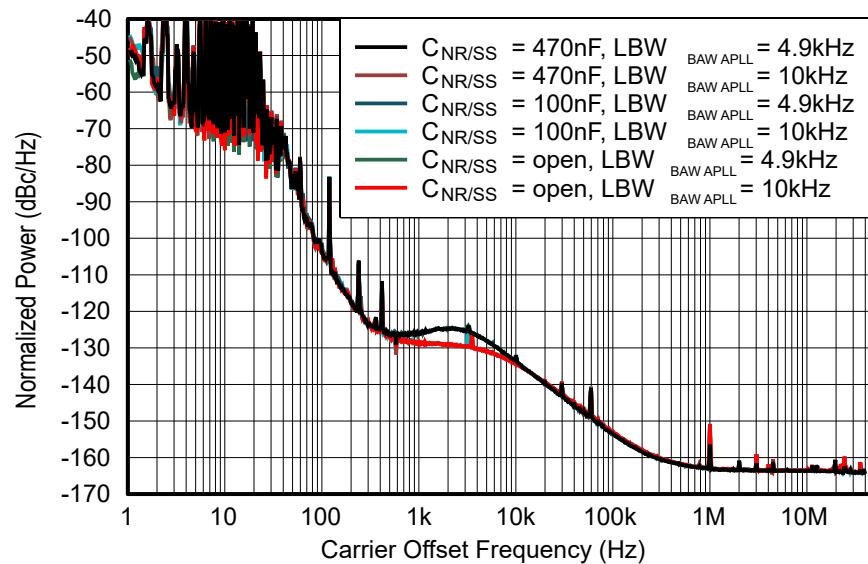

LMK5B33216 を使って XO に電力を供給することで、電源フィルタやループ帯域幅の設定に関係なく、低ノイズ PLL 出力を実現できます。図 6-8 に、LMK5B33216 から電力を供給した場合の LMK5B33216 位相ノイズを示し、図 6-9 にテスト設定を示します。これらの結果は、不適切な電源フィルタを使用した場合の PLL 出力ジッタ (12kHz ~ 20MHz オフセット) への影響が無視できる程度であることを示しています。

| $C_{NR/SS}$ [nF] | $LBW_{BAW\ APLL}$ [kHz] | 12kHz ~ 20MHz [fs] の範囲での RMS ジッタ (標準値) |

|------------------|-------------------------|----------------------------------------|

| 470              | 4.9                     | 51                                     |

| 470              | 10                      | 52                                     |

| 100              | 4.9                     | 51                                     |

| 100              | 10                      | 52                                     |

| 0 (オープン)         | 4.9                     | 51                                     |

| 0 (オープン)         | 10                      | 52                                     |

図 6-8. LMK5B33216 位相ノイズ、 $C_{NR/SS}$  変動、LMK5B33216 電源付き XO

図 6-9. LMK5B33216 テストセットアップ、LMK5B33216 電源付き XO

## 7 まとめ

XO 電源ノイズは、PLL クロックの設計で大きな役割を果たします。XO PSNR、XO 電源フィルタ、および APLL LBW は、PLL 出力位相ノイズに大きな影響を及ぼします。ノイズの多い XO 電源を回避できない場合は、CDC6C や LMK6C など、LDO を内蔵した XO を強く推奨します。LMK5B33216 などの BAW VCO を内蔵した PLL は、狭い LBW と組み合わせて使用して、XO ノイズの影響を低減することもできます。シームレスな設計を実現するには、LMK5B33216 を使用して外部 XO に電力を供給し、XO PSNR、電源フィルタ、APLL LBW に関係なく低ジッタ出力を生成します。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月