ADS1146, ADS1147, ADS1148

JAJS456G -JULY 2009-REVISED AUGUST 2016

# ADS114x 16ビット、2kSPS、センサ測定用 プログラマブル・ゲイン・アンプ(PGA)搭載のA/Dコンバータ

## 1 特長

- 最大2kSPSのデータ速度をプログラム可能

- あらゆるデータ速度において1サイクルで安定

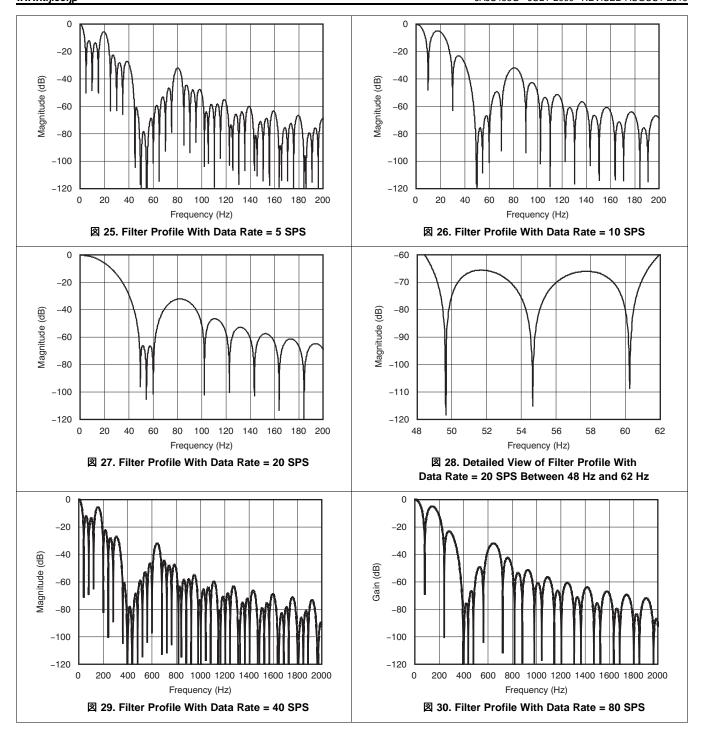

- 20SPSで50Hzと60Hzを同時に除去

- 8 (ADS1148)および4 (ADS1147)本の入力を 独立に選択可能なアナログ・マルチプレクサ

- ゲインをプログラム可能: 1V/V~128V/V

- 2つのマッチングされたプログラム可能な励起電 流源

- 低ドリフト係数の内蔵2.048V基準電圧

- センサのバーンアウト検出

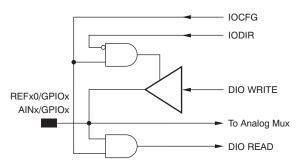

- 4または8の汎用I/O (ADS1147およびADS1148)

- 内部温度センサ

- 電源およびV<sub>RFF</sub>の監視(ADS1147およびADS1148)

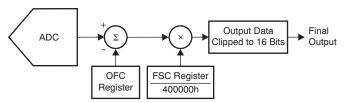

- 自己およびシステム較正

- SPI™互換のシリアル・インターフェイス

- アナログ電源: ユニポーラ(2.7V~5.25V)またはバイポーラ(±2.5V)

- デジタル電源: 2.7V~5.25V

## 2 アプリケーション

- 温度測定

- RTD、熱電対、サーミスタ

- 圧力測定

- 流量計

- ファクトリ・オートメーションとプロセス制御

## 3 概要

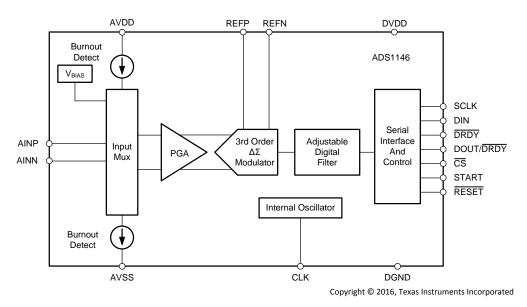

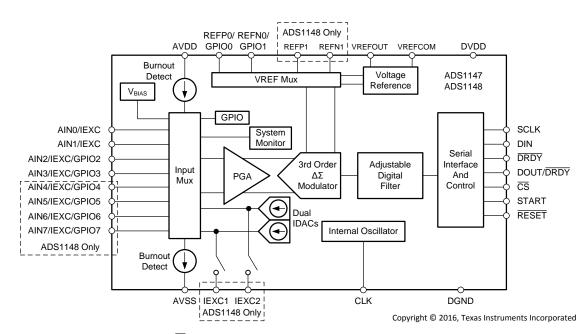

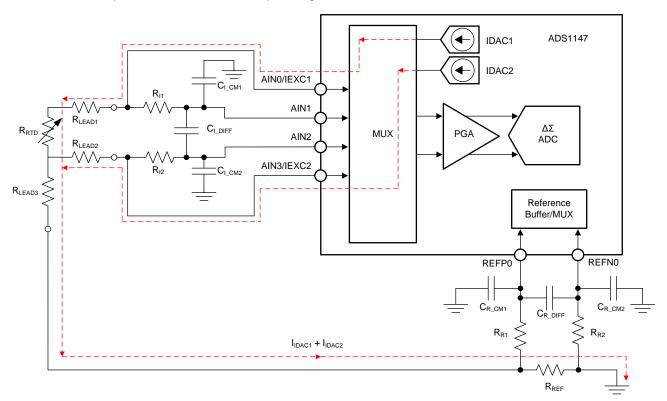

ADS1146、ADS1147、ADS1148デバイスは高精度の16 ビット・アナログA/Dコンバータ(ADC)で、多くの機能が統合されているため、センサ測定アプリケーションのシステム・コストと部品数を減らすことができます。このデバイスは、低ノイズPGA (プログラマブル・ゲイン・アンプ)、1サイクルで安定するデジタル・フィルタを備えた高精度デルタ・シグマ(ΔΣ) ADC、および内部発振回路を搭載しています。ADS1147およびADS1148デバイスには、低ドリフト係数の基準電圧と、2つのマッチングされたプログラム可能な励起電流源(IDAC)も搭載されています。

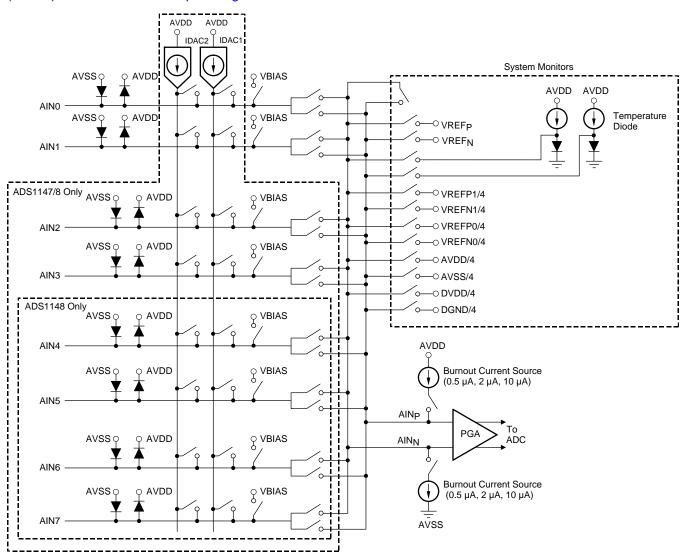

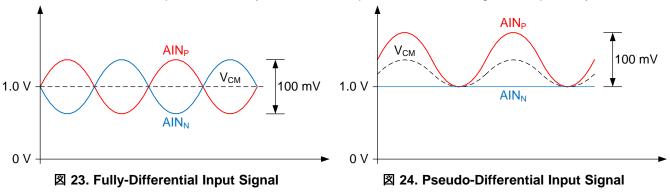

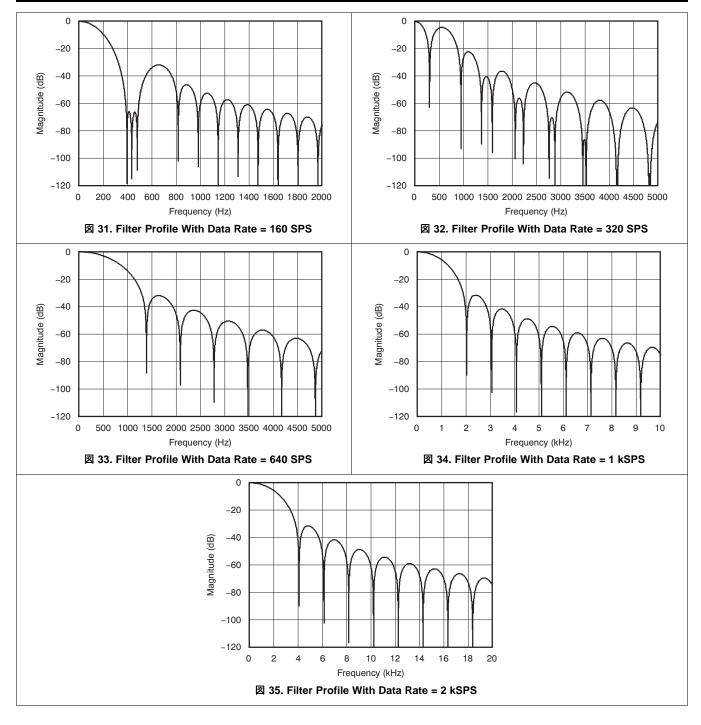

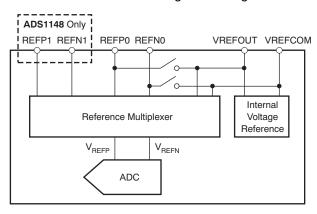

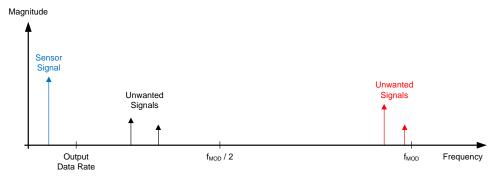

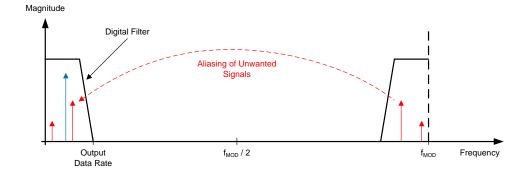

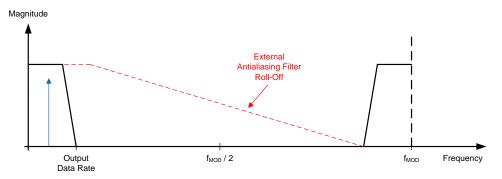

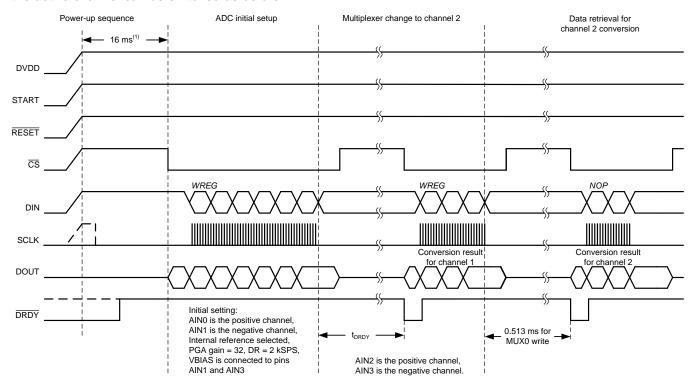

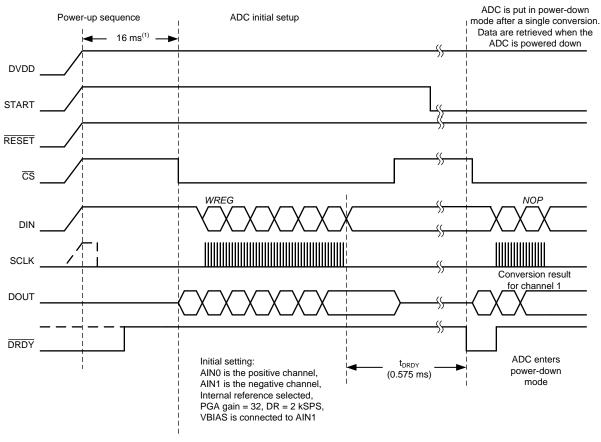

入力マルチプレクサは、ADS1148では4つ、ADS1147では2つ、ADS1146では1つの差動入力をサポートします。さらに、このマルチプレクサにはセンサのバーンアウト検出、熱電対の電圧バイアス、システム監視、汎用デジタルI/O (ADS1147およびADS1148)が組み込まれています。PGAにより、最大128VVのゲインを選択できます。これらの機能により、熱電対、サーミスタ、抵抗温度計(RTD)などの温度センサ測定アプリケーションや、その他抵抗性ブリッジ・センサなど小信号の測定用の完全なフロントエンド・ソリューションとなります。デジタル・フィルタは1サイクルで安定するため、入力マルチプレクサを使用するときに高速なチャネルのサイクリングが可能で、最大2kSPSのデータ速度を実現できます。20SPS以下のデータ速度では、50Hzと60Hzの両方の干渉がフィルタにより除去されます。

## 製品情報(1)

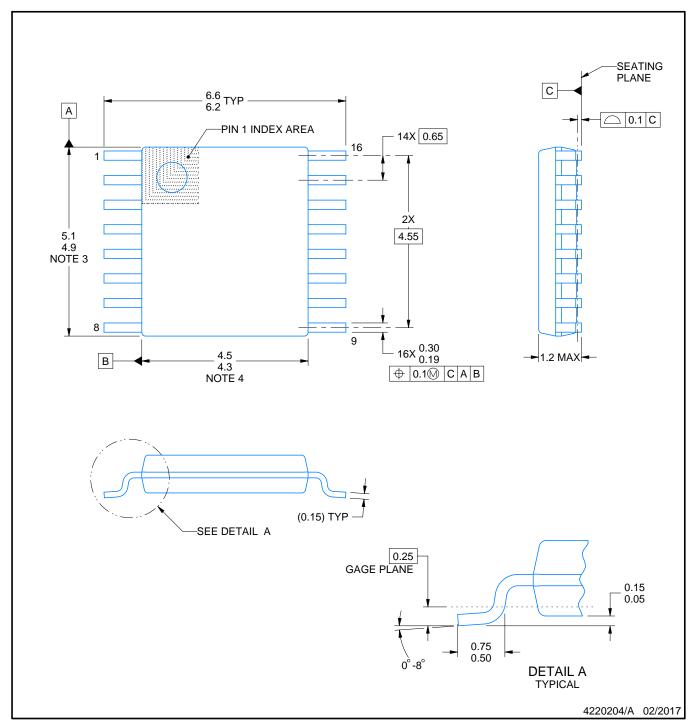

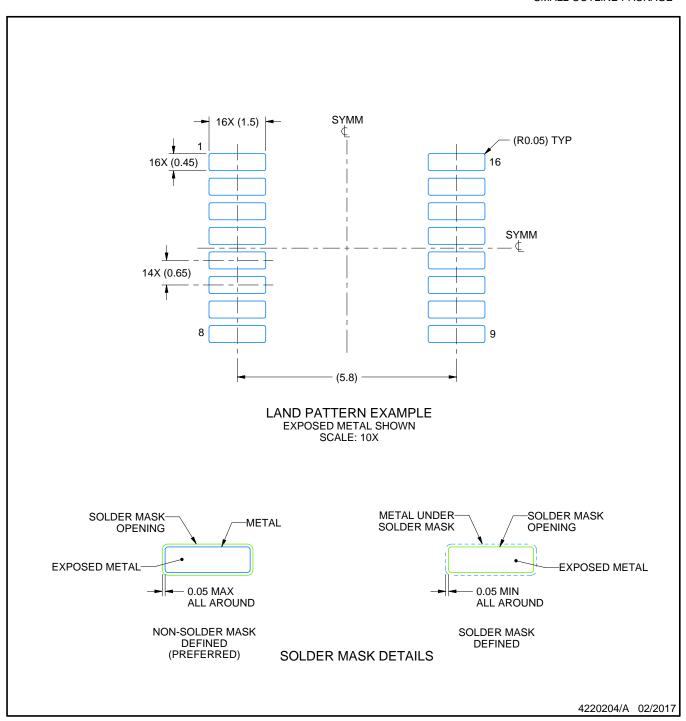

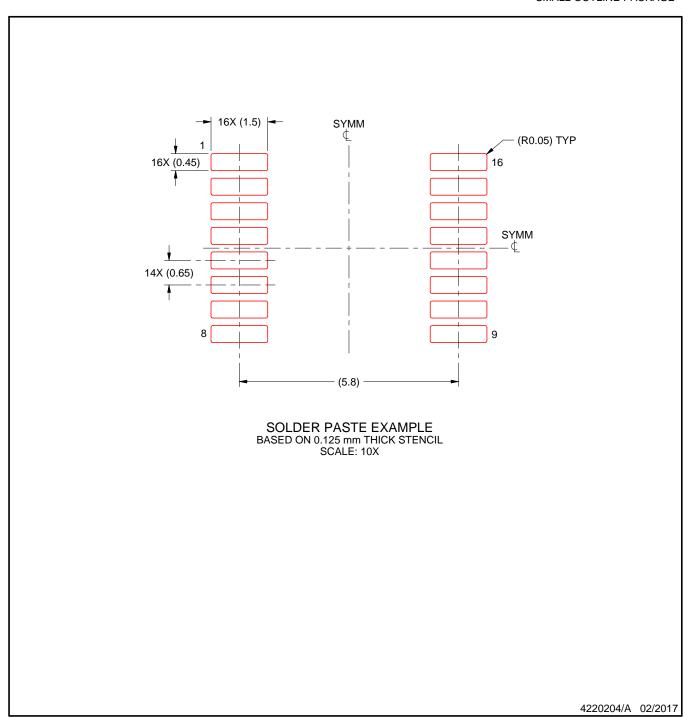

| 型番      | パッケージ      | 本体サイズ(公称)     |  |

|---------|------------|---------------|--|

| ADS1146 | TSSOP (16) | 5.00mm×4.40mm |  |

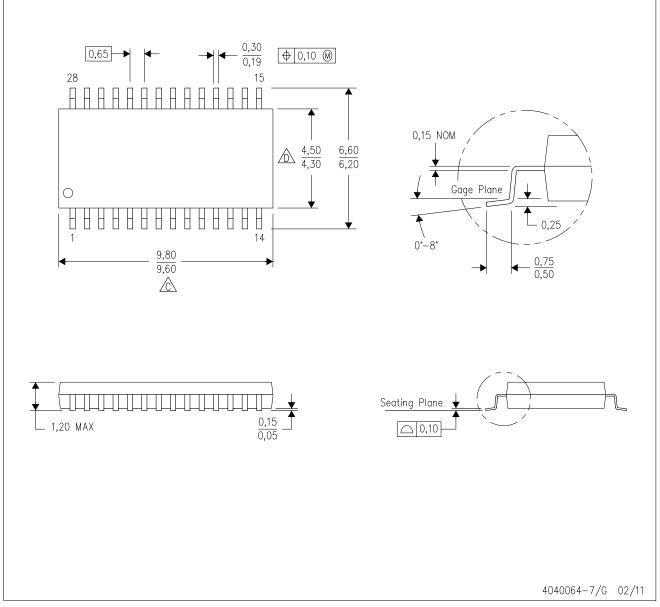

| ADS1147 | TSSOP (20) | 6.50mm×4.40mm |  |

| ADS1148 | TSSOP (28) | 9.70mm×4.40mm |  |

| ADS1146 | VQFN (32)  | 5.00mm×5.00mm |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

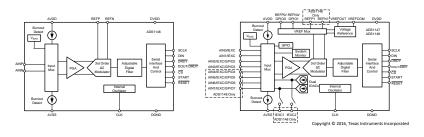

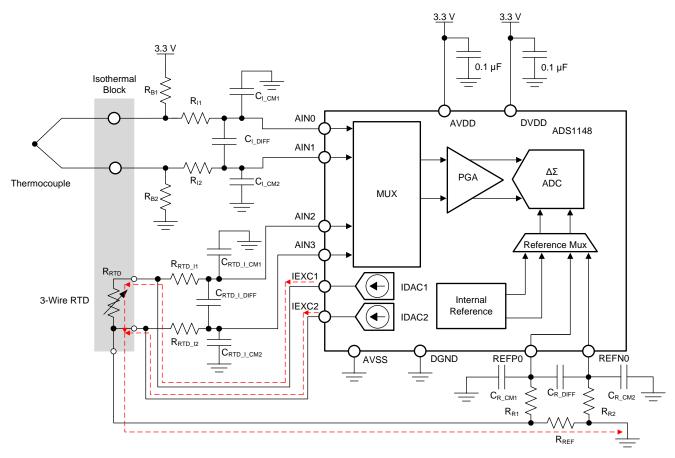

## 機能ブロック図

# 目次

| 1 | 特長1                                  |    | 9.4 Device Functional Modes    | 28 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                            |    | 9.5 Programming                | 33 |

| 3 | 概要1                                  |    | 9.6 Register Maps              | 42 |

| 4 | 改訂履歴2                                | 10 | Application and Implementation | 62 |

| 5 | Device Comparison Table 4            |    | 10.1 Application Information   | 62 |

| 6 | Pin Configuration and Functions 5    |    | 10.2 Typical Applications      | 68 |

| - | _                                    |    | 10.3 Do's and Don'ts           | 78 |

| 7 | Specifications                       | 11 | Power Supply Recommendations   | 80 |

|   | 7.1 Absolute Maximum Ratings         |    | 11.1 Power Supply Sequencing   | 80 |

|   | 7.2 ESD Ratings                      |    | 11.2 Power Supply Decoupling   | 80 |

|   | 7.3 Recommended Operating Conditions | 12 | Layout                         | 81 |

|   | 7.5 Electrical Characteristics 9     |    | 12.1 Layout Guidelines         |    |

|   |                                      |    | 12.2 Layout Example            |    |

|   |                                      | 13 | デバイスおよびドキュメントのサポート             |    |

|   | 7.7 Switching Characteristics        |    | 13.1 ドキュメントのサポート               |    |

|   | .,,                                  |    | 13.2 関連リンク                     |    |

| 8 | Parameter Measurement Information    |    | 13.3 ドキュメントの更新通知を受け取る方法        |    |

| _ | 8.1 Noise Performance                |    | 13.4 コミュニティ・リソース               |    |

| 9 | Detailed Description                 |    | 13.5 商標                        |    |

|   | 9.1 Overview                         |    | 13.6 静電気放電に関する注意事項             |    |

|   | 9.2 Functional Block Diagrams        |    | 13.7 Glossary                  |    |

|   | 9.3 Feature Description              | 14 | メカニカル、パッケージ、および注文情報            |    |

|   |                                      |    |                                |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision F (April 2012) から Revision G に変更

Page

| • | 「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関                                                                                                                                                 |    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケー                                                                                                                                                 |    |

|   | ジ、および注文情報」セクションを追加                                                                                                                                                                                              | 1  |

| • | 「特長」および「概要」セクションを更新し、温度測定以外の用途での使用を追加                                                                                                                                                                           | 1  |

| • | Merged all Pin Functions into one table                                                                                                                                                                         | 6  |

| • | Changed values in the Thermal Information table to align with JEDEC standards                                                                                                                                   | 8  |

| • | 追加 Absolute input current specification to Electrical Characteristics                                                                                                                                           | 9  |

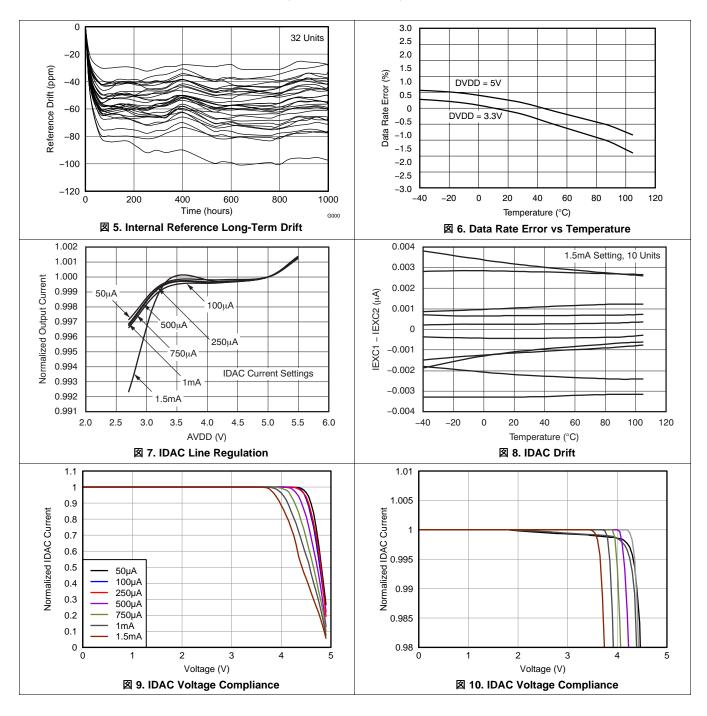

| • | Changed compliance voltage for excitation current sources in <i>Electrical Characteristics</i> , now refers to 🗵 9 and 🗵 10; changed initial error and initial mismatch to absolute error and absolute mismatch | 9  |

| • | 変更 IDAC mismatch specification in Electrical Characteristics table to reflect proper distribution                                                                                                               | 9  |

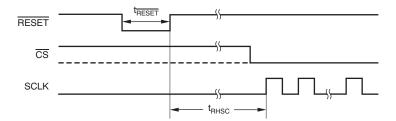

| • | Re-ordered elements in <i>Timing Requirements</i> tables, changed timing references to t <sub>CLK</sub>                                                                                                         | 11 |

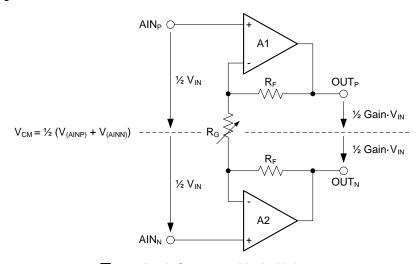

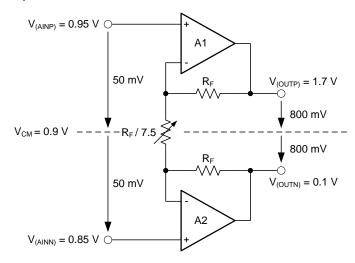

| • | 変更 Low-Noise PGA section                                                                                                                                                                                        | 18 |

| • | Modified 🗵 20 to show variable resistor position                                                                                                                                                                | 18 |

| • | Added f <sub>CLK</sub> /f <sub>MOD</sub> column to 表 5                                                                                                                                                          | 22 |

| • | 変更 Chip Select (CS) section                                                                                                                                                                                     | 33 |

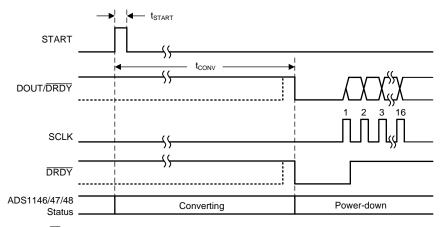

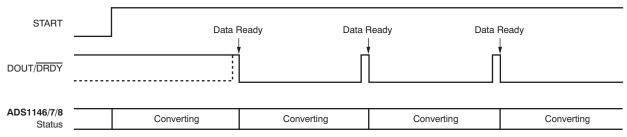

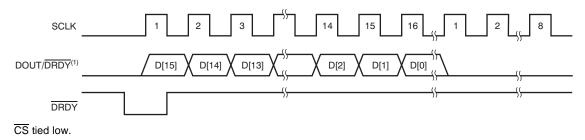

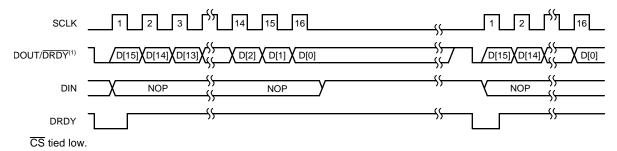

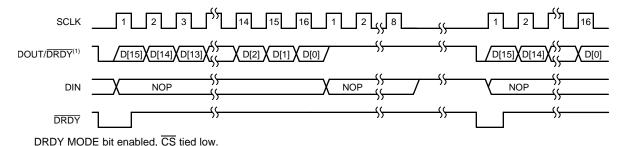

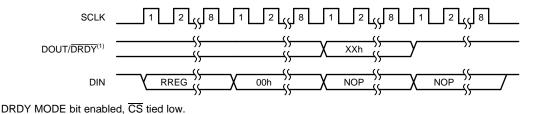

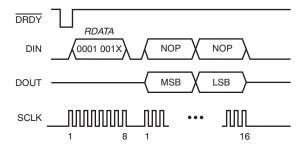

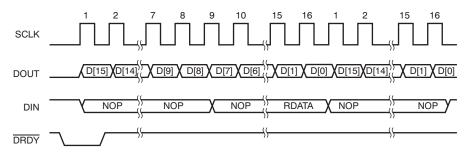

| • | 変更 Data Output and Data Ready (DOUT/DRDY) section                                                                                                                                                               | 34 |

| • | 変更 Figure 42, 43, and 44                                                                                                                                                                                        | 35 |

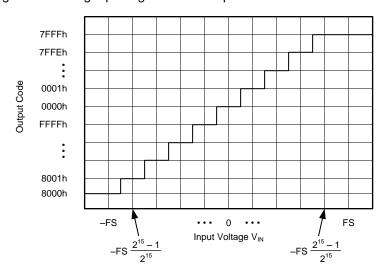

| • | Added more infomation to Data Format section; added 🗵 45                                                                                                                                                        | 36 |

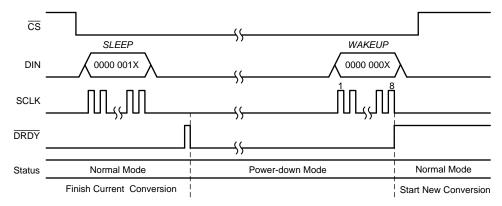

| • | Modified ☑ 46 to include CS status through SLEEP and WAKEUP command                                                                                                                                             | 38 |

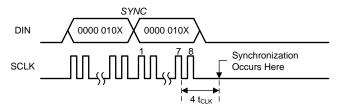

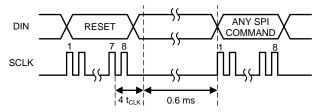

| • | Updated ☑ 47 and ☑ 48 to show start of command execution                                                                                                                                                        | 38 |

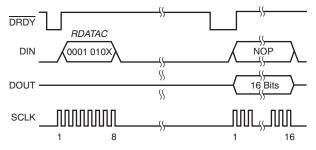

| • | Removed figure for SDATAC (0001 011x) (Stop Read Data Continuous) command                                                                                                                                       | 40 |

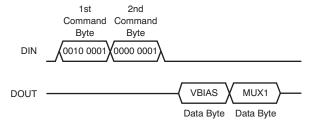

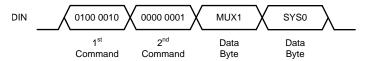

| • | Updated ☑ 53 to show MUX1 as the start of the data byte for the given command and register location                                                                                                             | 40 |

# 改訂履歴 (continued)

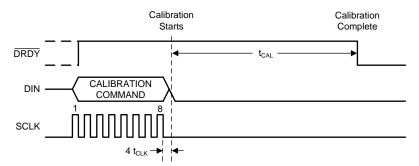

| Updated ☑ 54 to show start of calibration timing                                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ·                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision E (April 2012) から Revision F に変更                                                                  | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Added ADS1148, QFN-32 row to Package/Ordering Information table                                            | Page Control to Analog Inputs, Full-scale input voltage parameter typical specification in Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Inputs, Mux leakage current parameter from Electrical Characteristics table analog Figure 1 and Electrical Characteristics table analog Figure 1 analog Input Inpedance section analog Input Impedance section analog Input Impedanc |

| Revision D (October 2011) から Revision E に変更                                                                | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Added RHB pin configuration                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision C (April 2010) から Revision D に変更                                                                  | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| • 追加 footnote to Analog Inputs, <i>Full-scale input voltage</i> parameter typical specification in Electri | cal Characteristics table . 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| • 削除 Analog Inputs, Mux leakage current parameter from Electrical Characteristics table                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

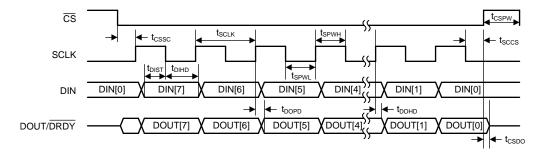

| • 追加 t <sub>CSPW</sub> to minimum specification in Timing Characteristics for Figure 1                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

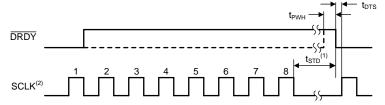

| • 変更 t <sub>DTS</sub> minimum specification in <i>Timing Requirements</i>                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Updated    1 to show t <sub>CSPW</sub> timing                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ● 追加 図 6, 図 5, 図 9, and 図 10                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

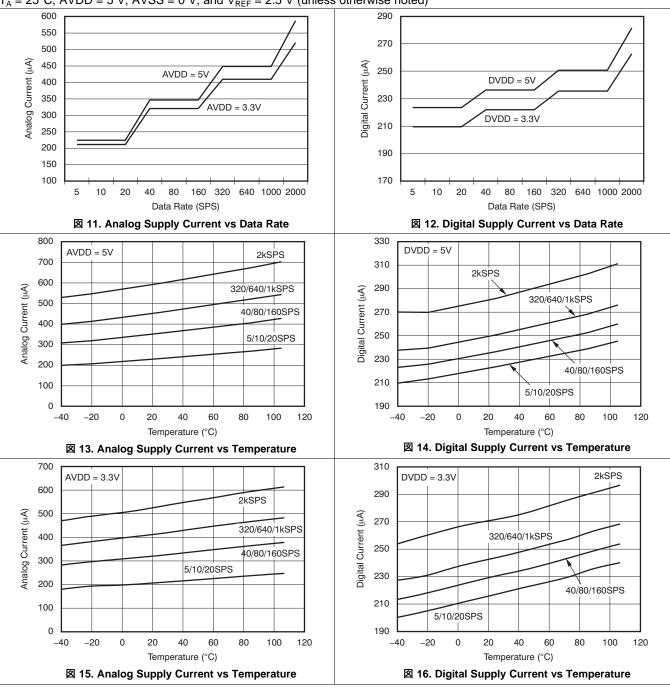

| ● 追加 図 15, 図 16, 図 11, and 図 12                                                                            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Corrected   19 to remove constant short                                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 表 4 to Analog Input Impedance section                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Corrected 図 29 and 図 30                                                                                    | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 details to Bias Voltage Generation section                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 Channel Cycling and Overload Recovery section                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • Corrected 表 10                                                                                           | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 式 18 to Calibration section                                                                           | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 details to Calibration Commands section                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • 追加 details to <i>Digital Interface</i> section                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • 追加 Restricted command to 表 15                                                                            | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **5 Device Comparison Table**

| PRODUCT | RESOLUTION<br>(BITS) | NUMBER OF INPUTS    | VOLTAGE<br>REFERENCE | EXCITATION CURRENT SOURCES | PACKAGE<br>(PINS) |

|---------|----------------------|---------------------|----------------------|----------------------------|-------------------|

| ADS1246 | 24                   | 1 Differential      | External             | No                         | TSSOP (16)        |

| ADS1247 | 24                   | 4-Input Multiplexer | Internal or External | Yes                        | TSSOP (20)        |

| ADS1248 | 24                   | 8-Input Multiplexer | Internal or External | Yes                        | TSSOP (28)        |

| ADS1146 | 16                   | 1 Differential      | External             | No                         | TSSOP (16)        |

| ADS1147 | 16                   | 4-Input Multiplexer | Internal or External | Yes                        | TSSOP (20)        |

| ADS1148 | 16                   | 8-Input Multiplexer | Internal or External | Yes                        | TSSOP (28)        |

| AD31146 | 16                   | 8-Input Multiplexer | Internal or External | Yes                        | VQFN (32)         |

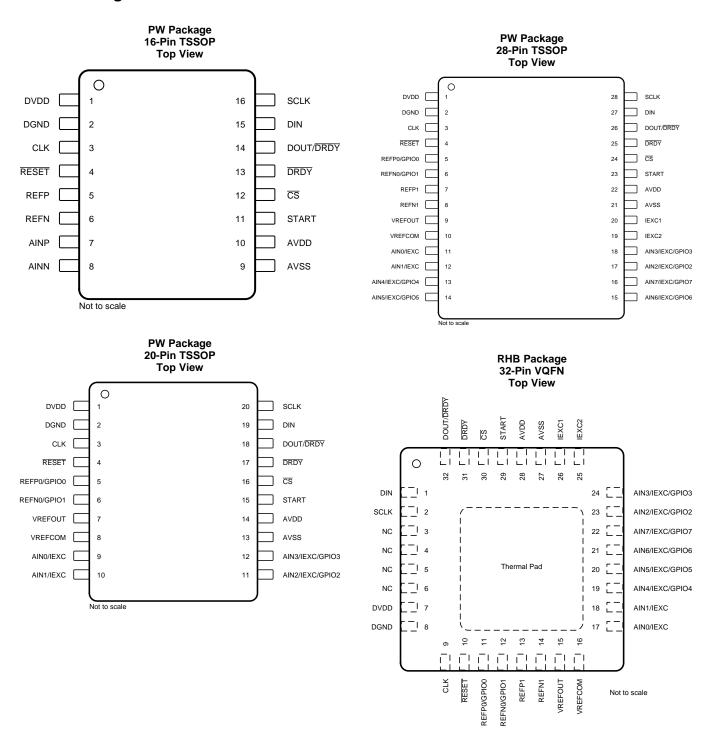

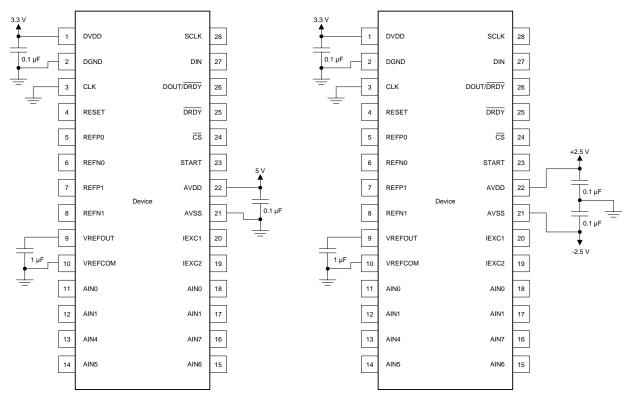

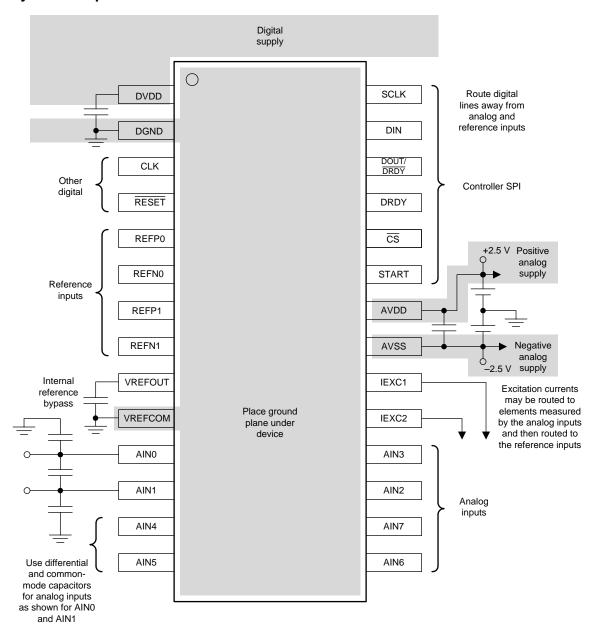

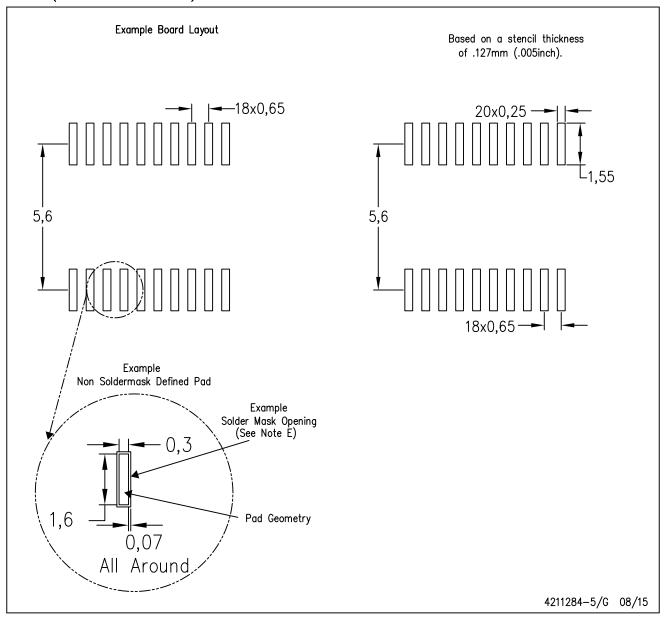

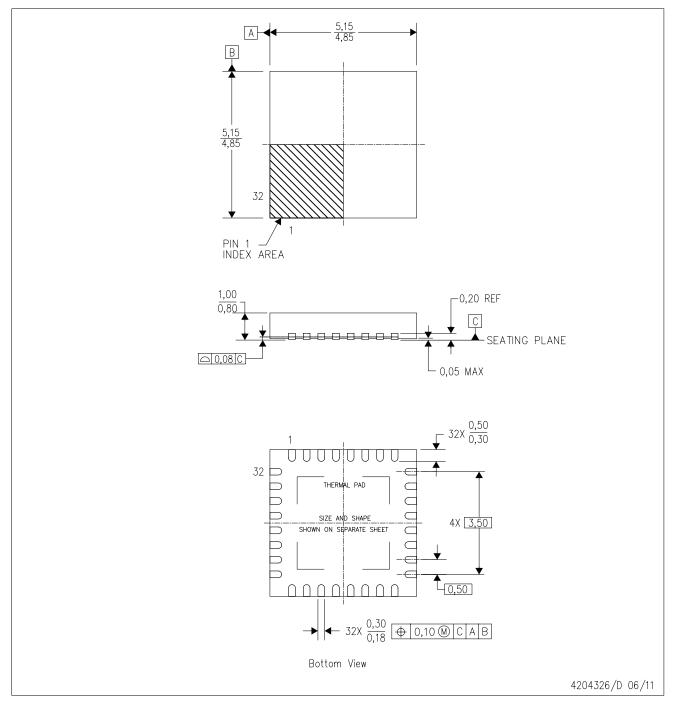

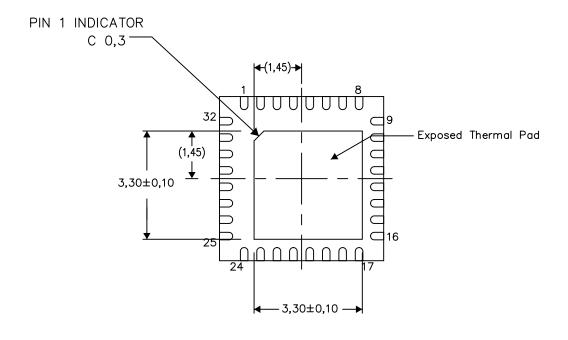

## 6 Pin Configuration and Functions

## **Pin Functions**

|                 | Pin Functions |            |            |            |                     |                                                                                                                                                   |  |  |

|-----------------|---------------|------------|------------|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 |               | PIN        |            |            |                     |                                                                                                                                                   |  |  |

| NAME            | ADS1146       | ADS1147    | ADS        | 1148       | TYPE <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup>                                                                                                                        |  |  |

| NAME            | TSSOP (16)    | TSSOP (20) | TSSOP (28) | VQFN (32)  |                     |                                                                                                                                                   |  |  |

| AIN0/IEXC       | _             | 9          | 11         | 17         | I                   | Analog input 0, optional excitation current output                                                                                                |  |  |

| AIN1/IEXC       | _             | 10         | 12         | 18         | I                   | Analog input 1, optional excitation current output                                                                                                |  |  |

| AIN2/IEXC/GPIO2 | _             | 11         | 17         | 23         | I/O                 | Analog input 2, optional excitation current output, or general-purpose digital input/output pin 2                                                 |  |  |

| AIN3/IEXC/GPIO3 | _             | 12         | 18         | 24         | I/O                 | Analog input 3, optional excitation current output, or general-purpose digital input/output pin 3                                                 |  |  |

| AIN4/IEXC/GPIO4 | _             | _          | 13         | 19         | I/O                 | Analog input 4, optional excitation current output, or general-purpose digital input/output pin 4                                                 |  |  |

| AIN5/IEXC/GPIO5 | _             | _          | 14         | 20         | I/O                 | Analog input 5, optional excitation current output, or general-purpose digital input/output pin 5                                                 |  |  |

| AIN6/IEXC/GPIO6 | _             | _          | 15         | 21         | I/O                 | Analog input 6, optional excitation current output, or general-purpose digital input/output pin 6                                                 |  |  |

| AIN7/IEXC/GPIO7 | _             | _          | 16         | 22         | I/O                 | Analog input 7, optional excitation current output, or general-purpose digital input/output pin 7                                                 |  |  |

| AINN            | 8             | _          | _          | _          | I                   | Negative analog input                                                                                                                             |  |  |

| AINP            | 7             | _          | _          | _          | I                   | Positive analog input                                                                                                                             |  |  |

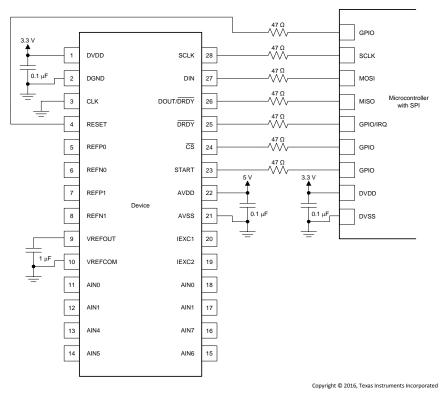

| AVDD            | 10            | 14         | 22         | 28         | Р                   | Positive analog power supply, connect a 0.1-µF capacitor to AVSS                                                                                  |  |  |

| AVSS            | 9             | 13         | 21         | 27         | Р                   | Negative analog power supply                                                                                                                      |  |  |

| CLK             | 3             | 3          | 3          | 9          | I                   | External clock input, tie to DGND to activate the internal oscillator.                                                                            |  |  |

| CS              | 12            | 16         | 24         | 30         | I                   | Chip select (active low)                                                                                                                          |  |  |

| DGND            | 2             | 2          | 2          | 8          | G                   | Digital ground                                                                                                                                    |  |  |

| DIN             | 15            | 19         | 27         | 1          | I                   | Serial data input                                                                                                                                 |  |  |

| DOUT/DRDY       | 14            | 18         | 26         | 32         | 0                   | Serial data output, or data out combined with data ready                                                                                          |  |  |

| DRDY            | 13            | 17         | 25         | 31         | 0                   | Data ready (active low)                                                                                                                           |  |  |

| DVDD            | 1             | 1          | 1          | 7          | Р                   | Digital power supply, connect a 0.1-µF capacitor to DGND                                                                                          |  |  |

| IEXC1           | _             | _          | 20         | 26         | 0                   | Excitation current output 1                                                                                                                       |  |  |

| IEXC2           | _             | _          | 19         | 25         | 0                   | Excitation current output 2                                                                                                                       |  |  |

| NC              | _             | _          | _          | 3, 4, 5, 6 | _                   | Connect pin to AVSS or leave floating                                                                                                             |  |  |

| REFN            | 6             | _          | _          | _          | I                   | Negative external reference input                                                                                                                 |  |  |

| REFN0/GPIO1     | _             | 6          | 6          | 12         | I/O                 | Negative external reference input 0, or general-purpose digital input/output pin 1                                                                |  |  |

| REFN1           | _             | _          | 8          | 14         | I                   | Negative external reference input 1                                                                                                               |  |  |

| REFP            | 5             | _          | _          | _          | I                   | Positive external reference input                                                                                                                 |  |  |

| REFP0/GPI00     | _             | 5          | 5          | 11         | I/O                 | Positive external reference input 0, or general-purpose digital input/output pin 1                                                                |  |  |

| REFP1           | _             | _          | 7          | 13         | I                   | Positive external reference input 1                                                                                                               |  |  |

| RESET           | 4             | 4          | 4          | 10         | I                   | Reset (active low)                                                                                                                                |  |  |

| SCLK            | 16            | 20         | 28         | 2          | I                   | Serial clock input                                                                                                                                |  |  |

| START           | 11            | 15         | 23         | 29         | I                   | Conversion start                                                                                                                                  |  |  |

| Thermal Pad     | _             | _          | _          | 33         | _                   | Connect pin to AVSS or leave floating                                                                                                             |  |  |

| VREFCOM         | _             | 8          | 10         | 16         | 0                   | Negative internal reference voltage output, connect to AVSS when using a unipolar supply or to the mid-voltage ground when using a bipolar supply |  |  |

| VREFOUT         | _             | 7          | 9          | 15         | 0                   | Positive internal reference voltage output, connect a capacitor in the range of 1 µF to 47 µF to VREFCOM                                          |  |  |

<sup>(1)</sup> G = Ground, I = Input, O = Output, P = Power

(2) See *Unused Inputs and Outputs* for unused pin connections.

# 7 Specifications

## 7.1 Absolute Maximum Ratings

See<sup>(1)</sup>

|                                                          |                                                    | MIN        | MAX        | UNIT |

|----------------------------------------------------------|----------------------------------------------------|------------|------------|------|

| analog input voltage Digital input voltage Diput current | AVDD to AVSS                                       | -0.3       | 5.5        |      |

| Power-supply voltage                                     | AVSS to DGND                                       | -2.8       | 0.3        | V    |

|                                                          | DVDD to DGND                                       | -0.3       | 5.5        |      |

| Analog input voltage                                     | AINx, REFPx, REFNx, VREFOUT, VREFCOM, IEXC1, IEXC2 | AVSS - 0.3 | AVDD + 0.3 | V    |

| Digital input voltage                                    | SCLK, DIN, DOUT/DRDY, DRDY, CS, START, RESET, CLK  | DGND - 0.3 | DVDD + 0.3 | V    |

| Innut ourrant                                            | Continuous, any pin except power supply pins       | -10        | 10         | A    |

| input current                                            | Momentary, any pin except power supply pins        | -100       | 100        | mA   |

| Tamparatura                                              | Junction, T <sub>J</sub>                           |            | 150        | °C   |

| Temperature                                              | Storage, T <sub>stg</sub>                          | -60        | 150        | 30   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                                                                   |                                                                     | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> |                                                                     | V     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over operating ambient temperature range (unless otherwise noted)

|                      |                                      |                                                  | MIN                        | NOM MAX                    | UNIT |

|----------------------|--------------------------------------|--------------------------------------------------|----------------------------|----------------------------|------|

| POWER                | SUPPLY                               |                                                  |                            |                            |      |

|                      |                                      | AVDD to AVSS                                     | 2.7                        | 5.25                       |      |

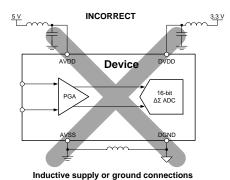

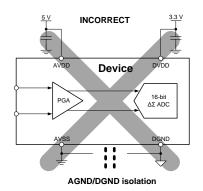

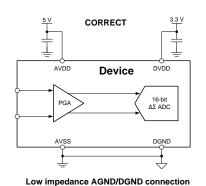

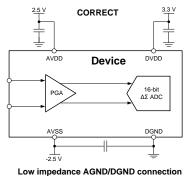

|                      | Analog power supply                  | AVSS to DGND                                     | -2.65                      | 0.1                        | V    |