LM5180-Q1

**ADVANCE INFORMATIO**

JAJSFS7B - JULY 2018-REVISED FEBRUARY 2019

# LM5180-Q1 100V、1.5A の MOSFET を内蔵した 65V<sub>IN</sub> PSR フライバッ ク DC/DC コンバータ

# 特長

- 車載用に AEC-Q100 認定済み

- デバイス温度グレード 1: 周囲温度範囲 -40°C~125°C

- 高信頼性の堅牢なアプリケーション用に設計

- 4.5V~65V の広い入力電圧範囲

- 絶縁バリアと交差する部品は 1 つだけの堅牢なソ リューション

- 総出力レギュレーション精度: ±1%

- (オプション) V<sub>OUT</sub> 温度補償

- 6ms の内部ソフトスタート、プログラムも可能

- 入力 UVLO およびサーマル・シャットダウン保護 機能

- ヒカップ・モード過電流フォルト保護

- -40℃~150℃ の接合部温度範囲

- 統合によりソリューションのサイズとコストを低

- 100V、0.35Ω のパワー MOSFET を内蔵

- Voutの レギュレーションにフォトカプラや変圧器の 補助巻線が不要

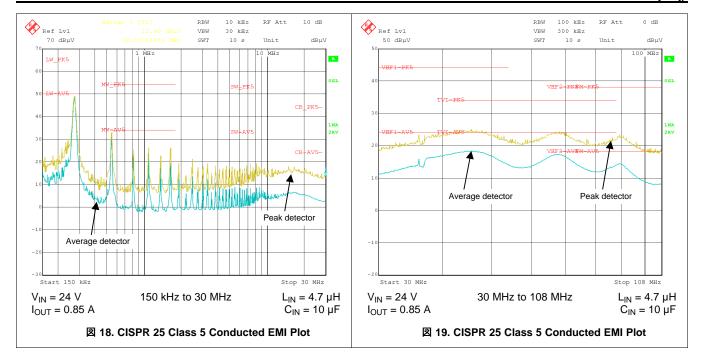

- CISPR 25 に適合する低 EMI での動作

- 高効率の PSR フライバック動作

- 重負荷時の境界導通モード (BCM) での疑似共振 スイッチング

- 低い入力静止電流

- 外部バイアス・オプションによる効率向上

- WEBENCH® Power Designer を使用して、カスタ 代表的なアプリケーション

# ムのレギュレータ設計を作成

# 2 アプリケーション

- 車体用電子機器

- 車載用パワー・トレイン・システム

- 絶縁バイアス電源レール

# 概要

LM5180-Q1は1次側レギュレーション(PSR)のフライバッ ク・コンバータで、4.5V~65Vの広い入力電圧範囲にわ たって高い効率を実現します。絶縁出力電圧は1次側フラ イバック電圧からサンプリングされるため、出力電圧のレ ギュレーションを行うためにフォトカプラ、基準電圧、変圧 器からの3次巻線を必要としません。高いレベルの統合に より、絶縁バリアと交差する部品は1つだけで、単純で信頼 性が高く、高密度の設計が実現されています。境界導通 モード(BCM)スイッチングにより、小型の磁気的ソリュー ションと、**±1%**以内の負荷およびライン・レギュレーション 性能を実現できます。内蔵の100VパワーMOSFETは最 大7Wの出力電力を供給でき、ライン過渡に対する余裕が 拡大されています。

# 製品情報(1)

| 型番        | パッケージ    | 本体サイズ(公称)     |

|-----------|----------|---------------|

| LM5180-Q1 | WSON (8) | 4.00mm×4.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

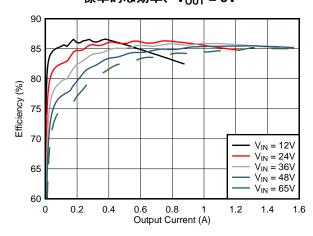

# 標準的な効率、V<sub>out</sub> = 5V

# 目次

| 1 | 特長 1                                 | 9 Application and Implementation 13 |

|---|--------------------------------------|-------------------------------------|

| 2 | アプリケーション1                            | 9.1 Application Information         |

| 3 | 概要 1                                 | 9.2 Typical Applications 13         |

| 4 | 改訂履歴                                 | 10 Power Supply Recommendations 30  |

| 5 | 概要(続き)                               | 11 Layout 31                        |

| 6 | Pin Configuration and Functions 4    | 11.1 Layout Guidelines 31           |

| 7 | Specifications5                      | 11.2 Layout Examples32              |

| • | 7.1 Absolute Maximum Ratings 5       | 12 デバイスおよびドキュメントのサポート               |

|   | 7.2 ESD Ratings                      | 12.1 デバイス・サポート33                    |

|   | 7.3 Recommended Operating Conditions | 12.2 ドキュメントのサポート                    |

|   | 7.4 Thermal Information5             | 12.3 ドキュメントの更新通知を受け取る方法34           |

|   | 7.5 Electrical Characteristics       | 12.4 コミュニティ・リソース34                  |

| 8 | Detailed Description 7               | 12.5 商標34                           |

|   | 8.1 Overview                         | 12.6 静電気放電に関する注意事項34                |

|   | 8.2 Functional Block Diagram         | 12.7 Glossary34                     |

|   | 8.3 Feature Description              | 13 メカニカル、パッケージ、および注文情報              |

|   | 8.4 Device Functional Modes          |                                     |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Revision A (August 2018) から Revision B に変更 ・ Vin-maxを65Vに 変更 1 ・ 追加 CISPR 25 class 5 EMI plots 19 2018年7月発行のものから更新 Page ・ 製品プレビューから量産データ・リリースに 1 ・ 「特長」の一覧を更新、「アプリケーション」セクションを追加 3 ・ 削除 soft-start capacitor in 図 5, 図 20, and 図 33 13 ・ Updated transformer part number in 表 2 14

# 5 概要(続き)

LM5180-Q1コンバータには、対象の最終機器に合わせて性能を最適化するオプション機能があるため、絶縁DC/DC電源の実装が簡単になります。出力電圧を1つの抵抗で設定でき、オプションの抵抗を使用するとフライバック・ダイオードの電圧降下の温度係数を打ち消して電圧精度を向上できます。追加機能として、内部的に固定または外部的にプログラム可能なソフトスタート、オプションの高効率用バイアス電源接続、可変ラインUVLO用のヒステリシス付き高精度イネーブル入力、ヒカップ・モード過負荷保護、自動復元機能付きのサーマル・シャットダウン保護機能があります。

LM5180-Q1は車載用AEC-Q100グレード1に認定済みで、8ピン、0.8mmピン・ピッチ、ウェッタブル・フランク付きのWSONパッケージで供給されます。

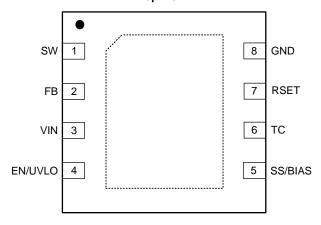

# 6 Pin Configuration and Functions

#### NGU Package 8-Pin WSON With Wettable Flanks Top View

# **Pin Functions**

|     | PIN                                                                                                                   |                                                                                                                                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                                                                                                                  | I/O <sup>(1)</sup>                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                       |

| 1   | SW                                                                                                                    | Р                                                                                                                                                                                                                      | Switch node that is internally connected to the drain of the N-channel power MOSFET. Connect to the primary-side switching terminal of the flyback transformer.                                                                                                                                                                                                                                   |

| 2   | FB                                                                                                                    | I                                                                                                                                                                                                                      | Primary side feedback pin. Connect a resistor from FB to SW. The ratio of the FB resistor to the resistor at the RSET pin sets the output voltage.                                                                                                                                                                                                                                                |

| 3   | VIN                                                                                                                   | P/I                                                                                                                                                                                                                    | Input supply connection. Source for internal bias regulators and input voltage sensing pin. Connect directly to the input supply of the converter with short, low impedance paths.                                                                                                                                                                                                                |

| 4   | EN/UVLO                                                                                                               | I                                                                                                                                                                                                                      | Enable input and undervoltage lockout (UVLO) programming pin. If the EN/UVLO voltage is below 1.1 V, the converter is in shutdown mode with all functions disabled. If the EN/UVLO voltage is greater than 1.1 V and below 1.5 V, the converter is in standby mode with the internal regulator operational and no switching. If the EN/UVLO voltage is above 1.5 V, the start-up sequence begins. |

| 5   | SS/BIAS                                                                                                               | I                                                                                                                                                                                                                      | Soft-start or bias input. Connect a capacitor from SS/BIAS to GND to adjust the output start-up time and input inrush current. If SS/BIAS is left open, the internal 6-ms soft-start timer is activated. Connect an auxiliary winding through a low leakage diode to SS/BIAS to supply bias to the internal voltage regulator and enable internal soft start.                                     |

|     |                                                                                                                       | Temperature compensation pin. Tie a resistor from TC to RSET to compensate for the temperature coefficient of the forward voltage drop of the secondary diode, thus improving regulation at the secondary-side output. |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7   | RSET I Reference resistor tied to GND to set the reference current for FB. Connect a 12.1-kΩ resist from RSET to GND. |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8   | GND                                                                                                                   | G                                                                                                                                                                                                                      | Analog and power ground. Ground connection of internal control circuits and power MOSFET.                                                                                                                                                                                                                                                                                                         |

(1) P = Power, G = Ground, I = Input, O = Output.

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)<sup>(1)</sup>

|                                                |                                       | MIN  | MAX  | UNIT |

|------------------------------------------------|---------------------------------------|------|------|------|

|                                                | VIN to GND                            | -0.3 | 70   |      |

|                                                | EN/UVLO to GND                        | -0.3 | 70   |      |

|                                                | TC to GND                             | -0.3 | 6    |      |

| Input voltage                                  | SS/BIAS to GND                        | -0.3 | 14   | V    |

|                                                | FB to GND                             | -0.3 | 70.3 |      |

|                                                | FB to VIN                             | -0.3 | 0.3  |      |

|                                                | RSET to GND                           | -0.3 | 3    |      |

| Output voltage                                 | SW to GND                             | -1.5 | 100  | V    |

| Output voltage                                 | SW to GND (20-ns transient)           | -3   |      | V    |

| Operating junction temperature, T <sub>J</sub> |                                       | -40  | 150  | °C   |

| Storage temperatu                              | Storage temperature, T <sub>stg</sub> |      | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                           |                                | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------|--------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC Q100-002<br>HBM ESD Classification Level 2 <sup>(1)</sup> |                                | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011                                              | All pins except 1, 4, 5, and 8 | ±500  | V    |

|                    |                         | CDM ESD Classification Level C4B                                                          | Pins 1, 4, 5, and 8            | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)

|                      |                                | MIN | NOM MAX | UNIT |

|----------------------|--------------------------------|-----|---------|------|

| V <sub>IN</sub>      | Input voltage                  | 4.5 | 65      | V    |

| $V_{SW}$             | SW voltage                     |     | 100     | V    |

| V <sub>EN/UVLO</sub> | EN/UVLO voltage                |     | 65      | V    |

| $V_{BIAS}$           | SS/BIAS voltage                |     | 13      | V    |

| TJ                   | Operating junction temperature | -40 | 150     | °C   |

#### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | LM5180     |      |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | NGU (WSON) | UNIT |

|                               |                                              | 8 PINS     |      |

| $R_{\Theta JA}$               | Junction-to-ambient thermal resistance       | 41.3       | °C/W |

| R <sub>⊕JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 34.7       | °C/W |

| $R_{\Theta JB}$               | Junction-to-board thermal resistance         | 19.1       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 19.2       | °C/W |

| R <sub>@JC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 3.2        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits aaply over the full –40°C to 150°C junction temperature range unless otherwise indicated.  $V_{IN}$  = 24 V and  $V_{EN/UVLO}$  = 2 V unless otherwise stated.

|                                 | PARAMETER                         | TEST CONDITIONS                                         | MIN   | TYP  | MAX   | UNIT |

|---------------------------------|-----------------------------------|---------------------------------------------------------|-------|------|-------|------|

| SUPPLY CU                       | RRENT                             |                                                         |       |      |       |      |

| SHUTDOWN                        | VIN shutdown current              | V <sub>EN/UVLO</sub> = 0 V                              |       | 3    |       | μA   |

| I <sub>ACTIVE</sub>             | VIN active current                | V <sub>EN/UVLO</sub> = 2.5 V, V <sub>RSET</sub> = 1.8 V |       | 290  |       | μΑ   |

| I <sub>ACTIVE_BIAS</sub>        | VIN current with BIAS connected   | V <sub>SS/BIAS</sub> = 6 V                              |       | 25   |       | μΑ   |

| ENABLE AN                       | ID INPUT UVLO                     |                                                         |       |      |       |      |

| V <sub>SD-RISING</sub>          | Standby threshold                 | V <sub>EN/UVLO</sub> rising                             |       | 0.65 | 1.1   | V    |

| V <sub>SD-FALLING</sub>         | Shutdown threshold                | V <sub>EN/UVLO</sub> falling                            | 0.3   |      |       | V    |

| V <sub>UV-RISING</sub>          | Enable threshold                  | V <sub>EN/UVLO</sub> rising                             | 1.47  | 1.5  | 1.53  | V    |

| I <sub>UV-HYST</sub>            | Enable current hysteresis         | V <sub>EN/UVLO</sub> = 1.6 V                            |       | 5    |       | μΑ   |

| V <sub>UV-HYST</sub>            | Enable voltage hysteresis         | V <sub>EN/UVLO</sub> falling                            |       | 0.05 |       | V    |

| FEEDBACK                        |                                   |                                                         |       |      |       |      |

| I <sub>RSET</sub>               | RSET current                      | $R_{RSET} = 12.1 \text{ k}\Omega$                       |       | 100  |       | μΑ   |

| V <sub>RSET</sub>               | RSET regulation voltage           | $R_{RSET} = 12.1 \text{ k}\Omega$                       | 1.198 | 1.21 | 1.222 | V    |

| V <sub>FB-VIN1</sub>            | FB to VIN voltage                 | $I_{FB} = 80 \mu A$                                     | -40   |      |       | mV   |

| V <sub>FB-VIN2</sub>            | FB to VIN voltage                 | $I_{FB} = 120 \mu A$                                    |       |      | 40    | mV   |

| SWITCHING                       | FREQUENCY                         |                                                         |       |      |       |      |

| F <sub>SW-MIN</sub>             | Minimum switching frequency       |                                                         |       | 10   |       | kHz  |

| F <sub>SW-MAX</sub>             | Maximum switching frequency       |                                                         |       | 350  |       | kHz  |

| t <sub>ON-MIN</sub>             | Minimum switch on-time            |                                                         |       | 150  |       | ns   |

| DIODE THEF                      | RMAL COMPENSATION                 |                                                         |       |      |       |      |

| $V_{TC}$                        | TC voltage                        | $I_{TC} = \pm 10 \ \mu A, \ T_J = 25^{\circ}C$          |       | 1.2  |       | V    |

| POWER SW                        | ITCHES                            |                                                         |       |      |       |      |

| R <sub>DS(on)</sub>             | MOSFET on-state resistance        | I <sub>SW</sub> = 100 mA                                |       | 0.35 |       | Ω    |

| SOFT-STAR                       | T AND BIAS                        |                                                         |       |      |       |      |

| I <sub>SS</sub>                 | SS ext capacitor charging current |                                                         |       | 5    |       | μΑ   |

| t <sub>SS</sub>                 | Internal SS time                  |                                                         |       | 6    |       | ms   |

| V <sub>BIAS-UVLO-</sub><br>RISE | BIAS enable voltage               | V <sub>SS/BIAS</sub> rising                             |       | 5.68 | 5.9   | V    |

| V <sub>BIAS-UVLO-</sub><br>HYST | BIAS UVLO hysteresis              | V <sub>SS/BIAS</sub> falling                            |       | 180  |       | mV   |

| CURRENT L                       | IMIT                              |                                                         |       |      |       |      |

| I <sub>PEAK</sub>               | Peak current limit threshold      |                                                         | 1.35  | 1.5  | 1.65  | Α    |

| THERMAL S                       | SHUTDOWN                          |                                                         |       |      |       |      |

| T <sub>SD</sub>                 | Thermal shutdown threshold        | T <sub>J</sub> rising                                   |       | 180  |       | °C   |

| T <sub>SD-HYS</sub>             | Thermal shutdown hysteresis       |                                                         |       | 20   |       | °C   |

# 8 Detailed Description

#### 8.1 Overview

The LM5180-Q1 primary-side regulated (PSR) flyback converter is a high-density, cost-effective solution for automotive and industrial systems requiring less than 7 W of isolated DC/DC power. This compact, easy-to-use flyback converter with low I<sub>Q</sub> can be applied over a wide input voltage range from 4.5 V to 65 V, with operation down to 3.5 V after startup. Innovative frequency and current amplitude modulation enables high conversion efficiency across the entire load and line range. Primary-side regulation of the isolated output voltage using sampled values of the primary winding voltage eliminates the need for an opto-coupler or an auxiliary transformer winding for feedback. Regulation performance that rivals that of traditional opto-coupler solutions is achieved without the associated cost, solution size and reliability concerns. The LM5180-Q1 converter services a wide range of applications including automotive on-board chargers and IGBT-based motor drives for HEV/EV systems.

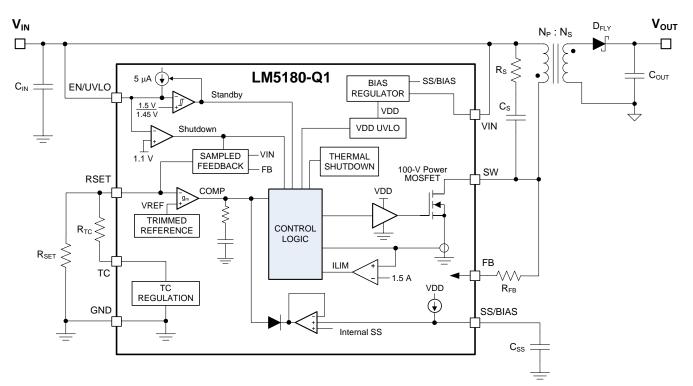

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Integrated Power MOSFET

The LM5180-Q1 is a flyback dc/dc converter with integrated 100-V, 1.5-A N-channel power MOSFET. During the MOSFET on-time, the transformer primary current increases from zero with slope  $V_{IN}$  /  $L_{MAG}$  (where  $L_{MAG}$  is the transformer primary-referred magnetizing inductance) while the output capacitor supplies the load current. When the high-side MOSFET is turned off by the control logic, the SW voltage  $V_{SW}$  swings up to approximately  $V_{IN}$  + ( $N_{PS} \times V_{OUT}$ ), where  $N_{PS} = N_P/N_S$  is the primary-to-secondary turns ratio of the transformer. The magnetizing current flows in the secondary side through the flyback diode, charging the output capacitor and supplying current to the load. Duty cycle D is defined as  $t_{ON}$  /  $t_{SW}$ , where  $t_{ON}$  is the MOSFET conduction time and  $t_{SW}$  is the switching period.

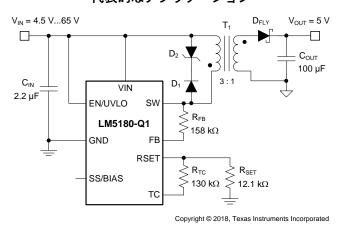

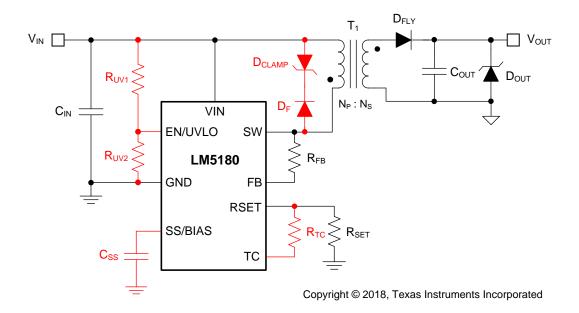

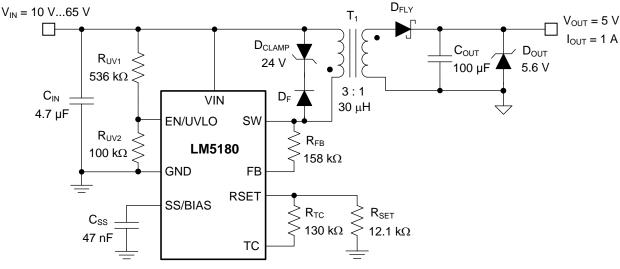

☑ 1 shows a typical schematic of the LM5180-Q1 PSR flyback circuit. Components denoted in red are optional depending on the application requirements.

☑ 1. LM5180-Q1 Flyback Converter Schematic (Optional Components in Red)

## 8.3.2 PSR Flyback Modes of Operation

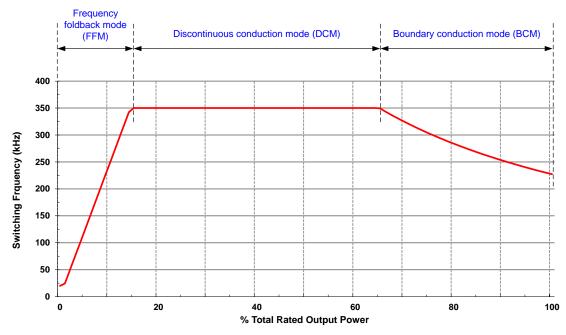

The LM5180-Q1 uses a variable-frequency, peak current-mode (VFPCM) control architecture with three possible modes of operation as illustrated in ☑ 2.

図 2. Three Modes of Operation Illustrated by Variation of Switching Frequency With Load

**ADVANCE INFORMATION**

The LM5180-Q1 operates in boundary conduction mode (BCM) at heavy loads. The power MOSFET turns on when the current in the secondary winding reaches zero, and the MOSFET turns off when the peak primary current reaches the level dictated by the output of the internal error amplifier. As the load is decreased, the frequency increases in order to maintain BCM operation. The duty cycle of the flyback converter is given  $\pm$  1, where  $V_D$  is the forward voltage drop of the flyback diode as its current approaches zero.

$$D_{BCM} = \frac{\left(V_{OUT} + V_{D}\right) \cdot N_{PS}}{V_{IN} + \left(V_{OUT} + V_{D}\right) \cdot N_{PS}}$$

(1)

The output power in BCM is given by  $\pm 2$ , where the applicable switching frequency and peak primary current in BCM are specified by  $\pm 3$  and  $\pm 4$ , respectively.

$$P_{OUT(BCM)} = \frac{L_{MAG} \cdot I_{PRI-PK(BCM)}^{2}}{2} \cdot F_{SW(BCM)}$$

(2)

$$F_{SW(BCM)} = \frac{1}{I_{PRI-PK(BCM)} \cdot \left(\frac{L_{MAG}}{V_{IN}} + \frac{L_{MAG}}{N_{PS} \cdot \left(V_{OUT} + V_{D}\right)}\right)}$$

(3)

$$I_{PRI-PK(BCM)} = \frac{2 \cdot \left(V_{OUT} + V_{D}\right) \cdot I_{OUT}}{V_{IN} \cdot D}$$

(4

As the load decreases, the LM5180-Q1 clamps the maximum switching frequency to 350 kHz, and the converter enters discontinuous conduction mode (DCM). The power delivered to the output in DCM is proportional to the peak primary current squared as given by  $\pm$  5 and  $\pm$  6. Thus, as the load decreases, the peak current reduces to maintain regulation at 350-kHz switching frequency.

$$P_{OUT(DCM)} = \frac{L_{MAG} \cdot I_{PRI-PK(DCM)}^{2}}{2} \cdot F_{SW(DCM)}$$

(5)

$$I_{PRI-PK(DCM)} = \sqrt{\frac{2 \cdot I_{OUT} \cdot (V_{OUT} + V_D)}{L_{MAG} \cdot F_{SW(DCM)}}}$$

$$D_{DCM} = \frac{L_{MAG} \cdot I_{PRI-PK(DCM)} \cdot F_{SW(DCM)}}{V_{IN}}$$

(7)

At even lighter loads, the primary-side peak current set by the internal error amplifier decreases to a minimum level of 0.3 A, or 20% of its 1.5-A peak value, and the MOSFET off-time extends to maintain the output load requirement. The system operates in frequency foldback mode (FFM), and the switching frequency decreases as the load current is reduced. Other than a fault condition, the lowest frequency of operation of the LM5180-Q1 is 12 kHz, which sets a minimum load requirement of approximately 0.5% full load.

#### 8.3.3 Setting the Output Voltage

To minimize output voltage regulation error, the LM5180-Q1 senses the reflected secondary voltage when the secondary current reaches zero. The feedback (FB) resistor, which is connected between SW and FB as shown in  $\mathbb{Z}$  1, is determined using  $\mathbb{Z}$  8, where R<sub>SET</sub> is nominally 12.1 kΩ.

$$R_{FB} = \left(V_{OUT} + V_{D}\right) \cdot N_{PS} \cdot \frac{R_{SET}}{V_{RSET}}$$

(8)

#### 8.3.3.1 Diode Thermal Compensation

The LM5180-Q1 employs a unique thermal compensation circuit that adjusts the feedback setpoint based on the thermal coefficient of the flyback diode's forward voltage drop. Even though the output voltage is measured when the secondary current is effectively zero, there is still a non-zero forward voltage drop associated with the flyback diode. Select the thermal compensation resistor using  $\pm$  9.

$$R_{TC} = \frac{R_{FB}}{N_{PS}} \cdot \frac{3mV/^{\circ}C}{TC_{Diode}}$$

(9)

The temperature coefficient of the diode voltage drop may not be explicitly provided in the diode datasheet, so the effective value can be estimated based on the measured output voltage shift over temperature when the TC resistor is not installed.

### 8.3.4 Control Loop Error Amplifier

The inputs of the error amplifier include a level-shifted version of the FB voltage and an internal 1.21-V reference set by the resistor at RSET. A type-2 internal compensation network stabilizes the converter. In BCM operation when the output voltage is in regulation, an on-time interval is initiated when the secondary current reaches zero. The power MOSFET is subsequently turned off when an amplified version of the peak primary current exceeds the error amplifier output.

#### 8.3.5 Precision Enable

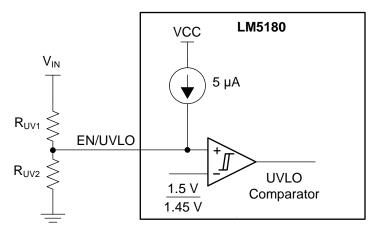

The precision EN/UVLO input supports adjustable input undervoltage lockout (UVLO) with hysteresis for application specific power-up and power-down requirements. EN/UVLO connects to a comparator with a 1.5-V reference voltage and 50-mV hysteresis. An external logic signal can be used to drive the EN/UVLO input to toggle the output on and off for system sequencing or protection. The simplest way to enable the LM5180-Q1 is to connect EN/UVLO directly to  $V_{IN}$ . This allows the LM5180-Q1 to start up when  $V_{IN}$  is within its valid operating range. However, many applications benefit from using a resistor divider  $R_{UV1}$  and  $R_{UV2}$  as shown in  $\boxed{2}$  3 to establish a precision UVLO level.

#### 図 3. Programmable Input Voltage UVLO With Hysteresis

Use  $\pm$  10 and  $\pm$  11 to calculate the input UVLO voltages turn-on and turn-off voltages, respectively, where  $V_{UV-RISING}$  and  $V_{UV-FALLING}$  are the UVLO comparator thresholds and  $I_{UV-HYST}$  is the hysteresis current.

$$V_{IN(on)} = V_{UV-RISING} \left( 1 + \frac{R_{UV1}}{R_{UV2}} \right)$$

(10)

$$V_{\text{IN(off)}} = V_{\text{UV-FALLING}} \left( 1 + \frac{R_{\text{UV1}}}{R_{\text{UV2}}} \right) - I_{\text{UV-HYST}} \cdot R_{\text{UV2}}$$

(11)

The LM5180-Q1 also provides a low- $I_Q$  shutdown mode when the EN/UVLO voltage is pulled below a base-emitter voltage drop (approximately 0.6 V at room temperature). If the EN/UVLO voltage is below this hard shutdown threshold, the internal LDO regulator powers off, and the internal bias-supply rail collapses, shutting down the bias currents of the LM5180-Q1. The LM5180-Q1 operates in standby mode when the EN/UVLO voltage is between the hard shutdown and precision-enable thresholds.

### 8.3.6 Configurable Soft Start

The LM5180-Q1 has a flexible and easy-to-use soft-start control pin, SS/BIAS. The soft-start feature prevents inrush current impacting the LM5180-Q1 and the input supply when power is first applied. This is achieved by controlling the voltage at the output of the internal error amplifier. Soft start is achieved by slowly ramping up the target regulation voltage when the device is first enabled or powered up. Selectable and adjustable start-up timing options include a 6-ms internally-fixed soft start and an externally-programmable soft start.

The simplest way to use the LM5180-Q1 is to leave SS/BIAS open. The LM5180-Q1 employs an internal soft-start control ramp and starts up to the regulated output voltage in 6 ms.

However, in applications with a large amount of output capacitance, higher  $V_{OUT}$  or other special requirements, the soft-start time can be extended by connecting an external capacitor  $C_{SS}$  from SS/BIAS to GND. A longer soft-start time further reduces the supply current needed to charge the output capacitors while sourcing the required load current. When the EN/UVLO voltage exceeds the UVLO rising threshold and a delay of 20  $\mu$ s expires, an internal current source  $I_{SS}$  of 5  $\mu$ A charges  $C_{SS}$  and generates a ramp to control the primary current amplitude. Calculate the soft-start capacitance for a desired soft-start time,  $T_{SS}$ , using  $\vec{\pm}$  12.

$$C_{SS}(nF) = 5 \cdot T_{SS}(ms) \tag{12}$$

C<sub>SS</sub> is discharged by an internal FET when switching is disabled by EN/UVLO or thermal shutdown.

#### 8.3.7 External Bias Supply

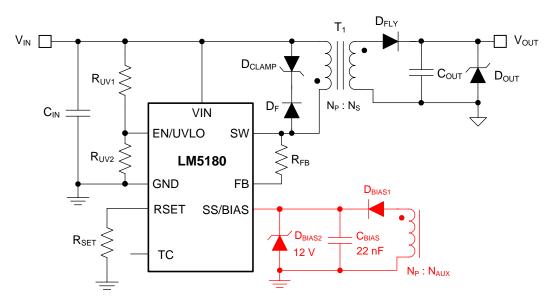

The LM5180-Q1 has an external bias supply feature that reduces input quiescent current and increases efficiency. When the voltage at SS/BIAS exceeds a rising threshold of 5.9 V, bias power for the internal LDO regulator can be derived from an external voltage source or from a transformer auxiliary winding as shown in 24. With a bias supply connected, the LM5180-Q1 then uses its internal soft-start ramp to control the primary current during start-up.

Copyright © 2018, Texas Instruments Incorporated

図 4. External Bias Supply Using Transformer Auxiliary Winding

When using a transformer auxiliary winding for bias power, the total leakage current related to  $D_{BIAS1}$  and  $D_{BIAS2}$  should be less than 1  $\mu$ A across the full operating temperature range.

#### 8.3.8 Minimum On-Time and Off-Time

When the internal power MOSFET is turned off, the leakage inductance of the transformer resonates with the SW node parasitic capacitance. The resultant ringing behavior can be excessive with large transformer leakage inductance and may corrupt the secondary zero-current detection. In order to prevent such a situation, a minimum switch off-time, designated as t<sub>OFF-MIN</sub>, of maximum 500 ns is set internally to ensure proper functionality. This sets a lower limit for the transformer magnetizing inductance as discussed in Detailed Design Procedure.

Furthermore, noise effects as a result of power MOSFET turn-on can impact the internal current sense circuit measurement. To mitigate this effect, the LM5180-Q1 provides a blanking time after the MOSFET turns on. This blanking time forces a minimum on-time, t<sub>ON-MIN</sub>, of 150 ns.

#### 8.3.9 Overcurrent Protection

In case of an overcurrent condition on the isolated output(s), the output voltage drops lower than the regulation level since the maximum power delivered is limited by the peak current capability on the primary side. The peak primary current is maintained at 1.5 A until the output decreases to the secondary diode voltage drop to impact the reflected signal on the primary side. At this point, the LM5180-Q1 assumes the output cannot be recovered and re-calibrates its switching frequency to 9 kHz until the overload condition is removed. The LM5180-Q1 responds with similar behavior to an output short circuit condition.

#### 8.3.10 Thermal Shutdown

Thermal shutdown is an integrated self-protection to limit junction temperature and prevent damage related to overheating. Thermal shutdown turns off the device when the junction temperature exceeds 180°C to prevent further power dissipation and temperature rise. Junction temperature decreases after shutdown, and the LM5180-Q1 restarts when the junction temperature falls to 160°C.

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

EN/UVLO facilitates ON and OFF control for the LM5180-Q1. When  $V_{\text{EN/UVLO}}$  is below approximately 0.6 V, the device is in shutdown mode. Both the internal LDO and the switching regulator are off. The quiescent current in shutdown mode drops to 3  $\mu$ A at  $V_{\text{IN}}=24$  V. The LM5180-Q1 also employs internal bias rail undervoltage protection. If the internal bias supply voltage is below its UV threshold, the converter remains off.

#### 8.4.2 Standby Mode

The internal bias rail LDO regulator has a lower enable threshold than the converter itself. When  $V_{EN/UVLO}$  is above 0.6 V and below the precision-enable threshold (1.5 V typically), the internal LDO is on and regulating. The precision enable circuitry is turned on once the internal VCC is above its UV threshold. The switching action and voltage regulation are not enabled until  $V_{EN/UVLO}$  rises above the precision enable threshold.

## 8.4.3 Active Mode

The LM5180-Q1 is in active mode when  $V_{\text{EN/UVLO}}$  is above the precision-enable threshold and the internal bias rail is above its UV threshold. The LM5180-Q1 operates in one of three modes depending on the load current requirement:

- 1. Boundary conduction mode (BCM) at heavy loads.

- 2. Discontinuous conduction mode (DCM) at medium loads.

- 3. Frequency foldback mode (FFM) at light loads.

Refer to PSR Flyback Modes of Operation for more detail.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

The LM5180-Q1 requires only a few external components to convert from a wide range of supply voltages to one or more isolated output rails. To expedite and streamline the process of designing of a LM5180-Q1-based converter, a comprehensive LM5180-Q1 quick-start calculator is available for download to assist the designer with component selection for a given application. WEBENCH® online software is also available to generate complete designs, leveraging iterative design procedures and access to comprehensive component databases. The following sections discuss the design procedure for both single- and dual-output implementations using specific circuit design examples.

As mentioned previously, the LM5180-Q1 also integrates several optional features to meet system design requirements, including precision enable, input UVLO, programmable soft start, output voltage thermal compensation, and external bias supply connection. Each application incorporates these features as needed for a more comprehensive design.

The application circuits detailed in *Typical Applications* show LM5180-Q1 configuration options suitable for several application use cases. Refer to the *LM5180EVM-S05* and *LM5180EVM-DUAL* EVM user's guides for more detail.

## 9.2 Typical Applications

For step-by-step design procedures, circuit schematics, bill of materials, PCB files, simulation and test results of LM5180-Q1-powered implementations, refer to the *TI Designs* reference design library.

#### 9.2.1 Design 1: Wide V<sub>IN</sub>, Low I<sub>Q</sub> PSR Flyback Converter Rated at 5 V, 1 A

The schematic diagram of a 5-V, 1-A PSR flyback converter is given in **≥** 5.

Copyright © 2018, Texas Instruments Incorporated

$\boxtimes$  5. Schematic for Design 1 With  $V_{IN(nom)} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $I_{OUT} = 1 \text{ A}$

# 9.2.1.1 Design Requirements

The required input, output, and performance parameters for this application example are shown in 表 1.

表 1. Design Parameters

| DESIGN PARAMETER                           | VALUE               |

|--------------------------------------------|---------------------|

| Input voltage range                        | 10 V to 65 V        |

| Input UVLO thresholds                      | 9.5 V on, 6.5 V off |

| Output voltage                             | 5 V                 |

| Rated load current, V <sub>IN</sub> = 24 V | 1 A                 |

| Output voltage regulation                  | ±1%                 |

| Output voltage ripple                      | < 100 mV            |

The target full-load efficiency is 86% based on a nominal input voltage of 24 V and an isolated output voltage of 5 V. The LM5180-Q1 is chosen to deliver a fixed 5-V output voltage set by resistor  $R_{FB}$  connected between the SW and FB pins. The input voltage turn-on and turn-off thresholds are established by  $R_{UV1}$  and  $R_{UV2}$ . The required components are listed in 表 2.

表 2. List of Components for Design 1

| REF DES            | QTY | SPECIFICATION                                        | VENDOR            | PART NUMBER          |

|--------------------|-----|------------------------------------------------------|-------------------|----------------------|

|                    |     | 4.7 μF, 100 V, X7R, 1206, ceramic                    | Murata            | GRM31CZ72A475KE11    |

| 0                  |     |                                                      | TDK               | CGA6M3X7S2A475K200AB |

| C <sub>IN</sub>    | 1   | 4.7 μF, 100 V, X7S, 1210, ceramic, AEC-Q200          | Murata            | GCM32DC72A475ME01    |

|                    |     |                                                      | Taiyo Yuden       | HMK325C7475MMHPE     |

|                    |     | 400 v.F. 6.2 V. V70, 4040, comparis                  | Murata            | GRM32EC70J107ME15    |

|                    |     | 100 μF, 6.3 V, X7S, 1210, ceramic                    | Taiyo Yuden       | JMK325AC7107MM-P     |

|                    |     | 100 F 00 W V00 1010                                  | TDK               | C3225X6S0J107M250AC  |

| C <sub>OUT</sub>   | 1   | 100 μF, 6.3 V, X6S, 1210, ceramic                    | Murata            | GRM32EC80J107ME20L   |

|                    |     | 100 μF, 6.3 V, X5R, 1210, ceramic                    | TDK               | C3225X5R0J107M250AC  |

|                    |     |                                                      | Murata            | GRT32ER60J107ME13    |

|                    |     |                                                      | Würth Electronik  | 885012109004         |

| C <sub>SS</sub>    |     | 47 nF, 16 V, X7R, 0402                               | Std               | Std                  |

| D <sub>CLAMP</sub> | 1   | Zener, 24 V, 1 W, PowerDI-123, AEC-Q101              | DFLZ24Q-7         | Diodes Inc.          |

| D <sub>F</sub>     | 1   | Switching diode, 75 V, 0.25 A, SOD-323               | CMDD4448          | Central Semi         |

| D <sub>FLY</sub>   | 1   | Schottky diode, 40 V, 2 A, SOD-123                   | FSV340FP          | ONsemi               |

| D <sub>OUT</sub>   | 1   | Zener, 5.6 V, 5%, SOD-523, AEC-Q101                  | BZX585-C5V6       | Nexperia             |

| R <sub>FB</sub>    | 1   | 158 kΩ, 1%, 0402                                     | Std               | Std                  |

| R <sub>SET</sub>   | 1   | 12.1 kΩ, 1%, 0402                                    | Std               | Std                  |

| R <sub>TC</sub>    | 1   | 130 kΩ, 1%, 0402                                     | Std               | Std                  |

| R <sub>UV1</sub>   | 1   | 536 kΩ, 1%, 0603                                     | Std               | Std                  |

| R <sub>UV2</sub>   | 1   | 100 kΩ, 1%, 0402                                     | Std               | Std                  |

|                    |     | 00 v11 0 A turns v215 0 . 4 OMT 0 . 40               | Würth Electronik  | 750317605            |

| T <sub>1</sub>     | 1   | 30 μH, 2 A, turns ratio 3 : 1, SMT, 9 $\times$ 10 mm | Coilcraft         | YA8779-BL            |

|                    |     | 40 μH, 2 A, turns ratio 3 : 1, SMT, 13 × 15 mm       | Würth Electronik  | 750313974            |

| U <sub>1</sub>     | 1   | LM5180-Q1 PSR flyback converter, AEC-Q100            | Texas Instruments | LM5180QNGURQ1        |

#### 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM5180-Q1 device with WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## 9.2.1.2.2 Custom Design With Excel Quickstart Tool

Select components based on the converter specifications using the LM5180-Q1 quick-start calculator.

#### 9.2.1.2.3 Flyback Transformer - T<sub>1</sub>

Choose a turns ratio based on an approximate 60% max duty cycle at minimum input voltage using  $\pm$  13, rounding up or down as needed.

$$N_{PS} = \frac{D_{MAX}}{1 - D_{MAX}} \cdot \frac{V_{IN(min)}}{V_{OUT} + V_{D}} = \frac{0.6}{1 - 0.6} \cdot \frac{10 \text{ V}}{5 \text{ V} + 0.3 \text{ V}} = 3$$

(13)

Select a magnetizing inductance based on the minimum off-time constraint using  $\pm$  14. Choose a value of 30  $\mu$ H with a saturation current of 2 A for this application.

$$L_{MAG} \geq \frac{\left(V_{OUT} + V_{D}\right) \cdot N_{PS} \cdot t_{OFF\text{-}MIN}}{I_{PRI\text{-}PK(FFM)}} = \frac{\left(5\,V + 0.3\,V\right) \cdot 3 \cdot 500\,\text{ns}}{0.3\,A} = 26.5\,\mu\text{H} \tag{14}$$

Note that a higher magnetizing inductance provides a larger operating range for BCM and FFM, but the leakage inductance may increase based on the increase number of primary turns,  $N_P$ . The primary and secondary winding RMS currents are given by  $\pm$  15 and  $\pm$  16, respectively.

$$I_{PRI-RMS} = \sqrt{\frac{D}{3}} \cdot I_{PRI-PK}$$

(15)

$$I_{SEC-RMS} = \sqrt{\frac{2 \cdot I_{OUT} \cdot I_{PRI-PK} \cdot N_{PS}}{3}}$$

(16)

Find the maximum output power for a given turns ratio using  $\pm$  17, where the typical value for  $I_{PRI-PK(max)}$  from Electrical Characteristics is 1.5 A. Iterate by increasing the turns ratio if the output power is too low at minimum input voltage.

$$P_{OUT(max)} = \frac{L_{MAG} \cdot I_{PRI-PK}^{2}}{2} \cdot F_{SW(BCM)} = \frac{I_{PRI-PK}}{2 \cdot \left[ \frac{1}{V_{IN}} + \frac{1}{N_{PS} \cdot V_{OUT}} \right]}$$

$$(17)$$

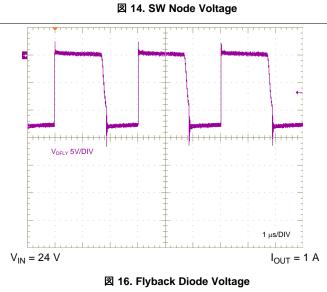

# 9.2.1.2.4 Flyback Diode - D<sub>FLY</sub>

The flyback diode reverse voltage is given by 式 18.

$$V_{D-REV} \ge \frac{V_{IN(max)}}{N_{PS}} + V_{OUT} = \frac{65 \text{ V}}{3} + 5 \text{ V} \approx 27 \text{ V}$$

(18)

Choose a 40-V, 3-A Schottky diode for this application to account for diode voltage overshoot and ringing related to transformer leakage inductance and diode parasitic capacitance. Connect an appropriate RC snubber circuit (for example,  $100 \Omega$  and 22 pF) across the diode if needed.

# 9.2.1.2.5 Clamp Circuit - D<sub>F</sub>, D<sub>CLAMP</sub>

Connect a diode-Zener clamp circuit across the primary winding to limit the peak SW node voltage after MOSFET turn-off below the maximum level of 100 V, as given by 式 19.

$$V_{\rm DZ(clamp)} < V_{\rm SW(max)} - V_{\rm IN(max)} \tag{19}$$

Choosing the zener,  $D_{CLAMP}$ , with clamp voltage of approximately 1.5 times the reflected output voltage, as specified by  $\pm$  20, provides a balance between the maximum SW voltage excursion and the leakage inductance demagnetization time.

$$V_{DZ(clamp)} = 1.5 \cdot N_{PS} \cdot (V_{OUT} + V_{D}) = 1.5 \cdot 3 \cdot (5 \text{ V} + 0.3 \text{ V}) \approx 24 \text{ V}$$

(20)

Select an ultra-fast switching diode or Schottky diode for D<sub>F</sub> with rated voltage greater than the maximum input voltage and with low forward recovery voltage drop.

#### 9.2.1.2.6 Output Capacitor - Cout

The output capacitor determines the voltage ripple at the converter output, limits the voltage excursion during a load transient, and sets the dominant pole of the converter's small-signal response. For a flyback converter specifically, the output capacitor supplies the load current when the main switch is on, and therefore the output voltage ripple is a function of load current and duty cycle.

Select an output capacitance using 式 21 to limit the ripple voltage amplitude to less than 1% of the output voltage at minimum input voltage.

$$C_{OUT} \ge \frac{I_{OUT} \cdot \left(I_{PRI-PK} - \frac{I_{OUT}}{N_{PS}}\right)^2}{I_{PRI-PK}^2 \cdot F_{SW} \cdot \Delta V_{OUT}}$$

(21)

Substituting the full load current, switching frequency, peak primary current and peak-to-peak voltage ripple specification gives  $C_{OUT}$  greater than 30  $\mu$ F. Mindful of the voltage coefficient of ceramic capacitors, select a 100- $\mu$ F, 6.3-V capacitor in 1210 case size with X5R or better dielectric. The output capacitor RMS ripple current is given by  $\pm$  22.

$$I_{\text{COUT-RMS}} = I_{\text{OUT}} \cdot \sqrt{\frac{2 \cdot N_{\text{PS}} \cdot I_{\text{PRI-PK}}}{3 \cdot I_{\text{OUT}}} - 1}$$

(22)

#### 9.2.1.2.7 Input Capacitor - CIN

Select an input capacitance using  $\pm$  23 to limit the ripple voltage amplitude to less than 5% of the input voltage when operating at nominal input voltage.

$$C_{IN} \ge \frac{I_{PRI-PK} \cdot D \cdot \left(1 - \frac{D}{2}\right)^2}{2 \cdot F_{SW} \cdot \Delta V_{IN}}$$

(23)

Substituting the input current at full load, switching frequency, peak primary current and peak-to-peak ripple specification gives  $C_{IN}$  greater than 2  $\mu F$ . Mindful of the voltage coefficient of ceramic capacitors, select a 4.7- $\mu F$ , 100-V ceramic input capacitor with X7S dielectric10- $\mu F$ , 50-V ceramic input capacitor with X7R dielectric in 1210 case size. The input capacitor RMS ripple current is given by  $\pm$  24.

$$I_{\text{CIN-RMS}} = \frac{D \cdot I_{\text{PRI-PK}}}{2} \cdot \sqrt{\frac{4}{3 \cdot D} - 1}$$

(24)

#### 9.2.1.2.8 Feedback Resistor - RFB

Select a feedback resistor, designated  $R_{FB}$ , of 158  $k\Omega$  based on the secondary winding voltage at the end of the flyback conduction interval (the sum of the 5-V output voltage and the Schottky diode forward voltage drop) reflected by the transformer turns ratio of 3 : 1. The forward voltage drop of the flyback diode is 0.3 V as its current approaches zero.

$$R_{FB} = \frac{(V_{OUT} + V_{D}) \cdot N_{PS}}{0.1 \, mA} = \frac{(5 \, V + 0.3 \, V) \cdot 3}{0.1 \, mA} = 158 \, k\Omega$$

(25)

#### 9.2.1.2.9 Thermal Compensation Resistor – R<sub>TC</sub>

Select a resistor for output voltage thermal compensation, designated R<sub>TC</sub>, based on 式 26.

$$R_{TC} = \frac{R_{FB}}{N_{PS}} \cdot \frac{3 \text{ mV/}^{\circ}C}{TC_{Diode}} = \frac{158 \text{ k}\Omega \cdot 3}{3 \cdot 1.2} = 130 \text{ k}\Omega$$

(26)

#### 9.2.1.2.10 UVLO Resistors - R<sub>UV1</sub>, R<sub>UV2</sub>

Given  $V_{IN(on)}$  and  $V_{IN(off)}$  as the input voltage turn-on and turn-off thresholds of 9.5 V and 6.5 V, respectively, select the upper and lower UVLO resistors using the following expressions:

$$R_{UV1} = \frac{V_{IN(on)} \cdot \frac{V_{UV-FALLING}}{V_{UV-RISING}} - V_{IN(off)}}{I_{UV-HYST}} = \frac{9.5 \text{ V} \cdot \frac{1.45 \text{ V}}{1.5 \text{ V}} - 6.5 \text{ V}}{5 \text{ \mu A}} = 536 \text{ k}\Omega$$

(27)

$$R_{UV2} = R_{UV1} \cdot \frac{V_{UV-RISING}}{V_{IN(on)} - V_{UV-RISING}} = 536 \text{ k}\Omega \cdot \frac{1.5 \text{ V}}{9.5 \text{ V} - 1.5 \text{ V}} = 100 \text{ k}\Omega$$

(28)

#### 9.2.1.2.11 Soft-Start Capacitor - C<sub>SS</sub>

Connect an external soft-start capacitor for a specific soft-start time. In this example, select a soft-start capacitance of 47 nF based on 式 12 to achieve a soft-start time of 9 ms.

For technical solutions, industry trends, and insights for designing and managing power supplies, please refer to TI's Power House blog series.

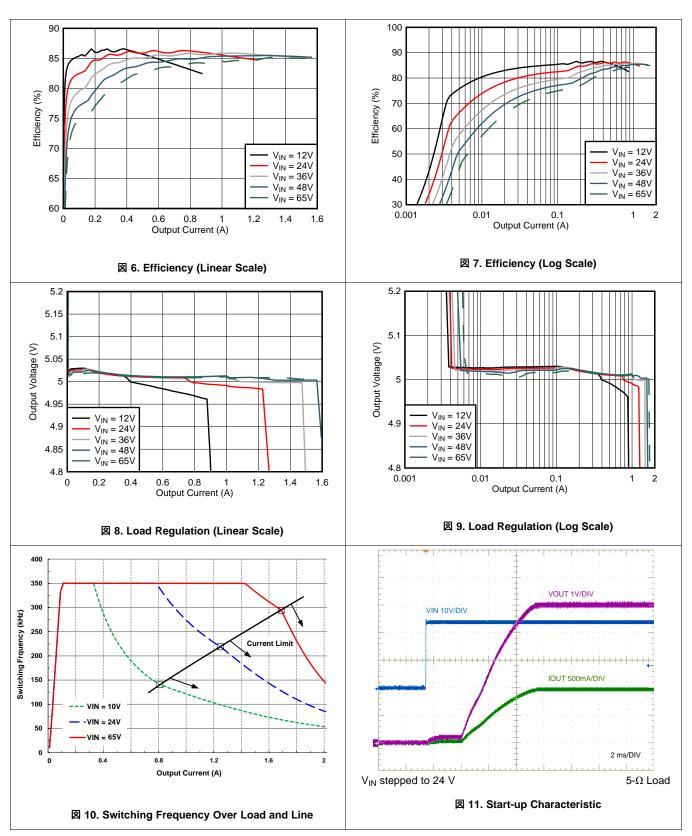

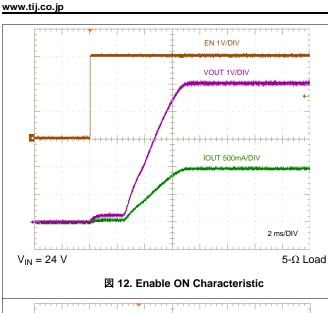

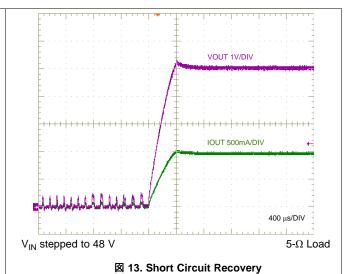

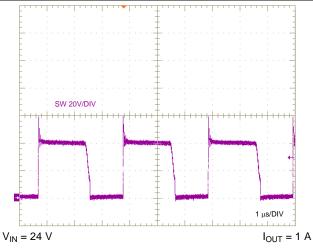

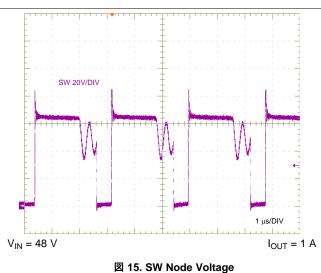

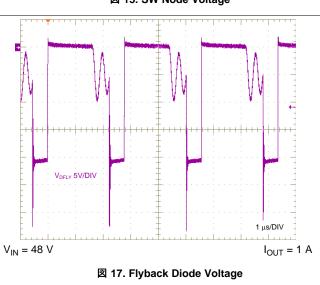

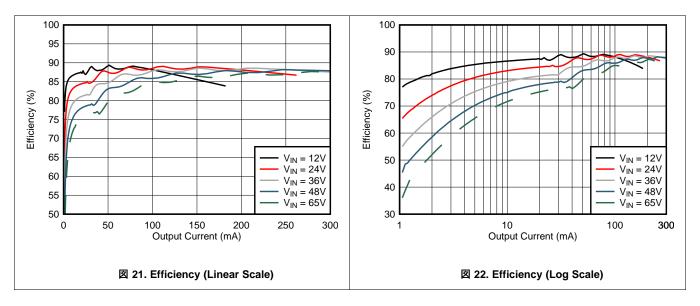

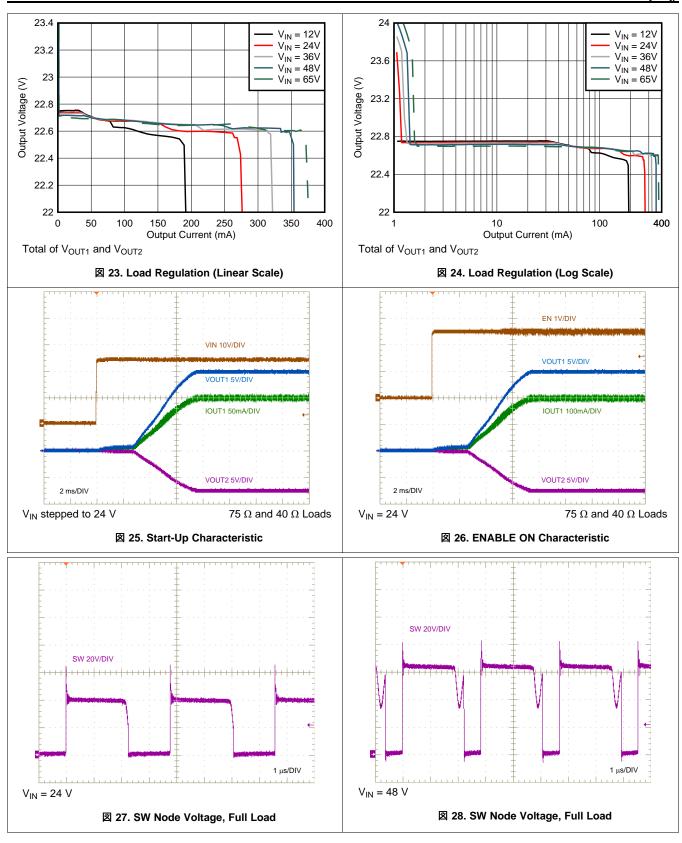

#### 9.2.1.3 Application Curves

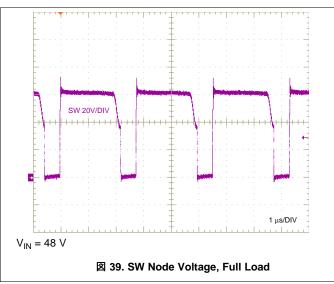

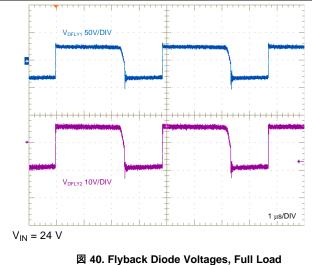

Unless otherwise stated, application performance curves were taken at  $T_A = 25$ °C.

**STRUMENTS**

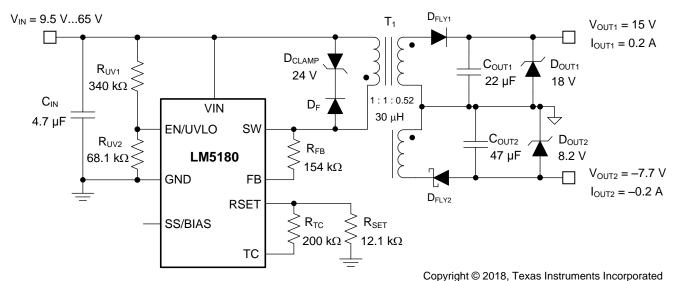

# 9.2.2 Design 2: PSR Flyback Converter With Dual Outputs of 15 V and -7.7 V at 200 mA

The schematic diagram of a dual-output flyback converter intended for isolated IGBT and SiC MOSFET gate drive power supply applications is given in

20.

$\boxtimes$  20. Schematic for Design 2 With  $V_{IN(nom)}$  = 48 V,  $V_{OUT1}$  = 15 V,  $V_{OUT2}$  = -7.7 V,  $I_{OUT}$  = 200 mA

#### 9.2.2.1 Design Requirements

The required input, output, and performance parameters for this application example are shown in 表 3.

DESIGN PARAMETER

VALUE

Input voltage range (steady state)

9.5 V to 65 V

Output 1 voltage and current

15 V, 0.2 A

Output 2 voltage and current

-7.7 V, -0.2 A

Input UVLO thresholds

9 V on, 7 V off

Output voltage regulation

±2%

表 3. Design Parameters

The target full-load efficiency of this LM5180-Q1 design is 88% based on a nominal input voltage of 24 V and isolated output voltages of 15 V and -7.7 V sharing a common return. The selected flyback converter components are cited in 表 4, including multi-winding flyback transformer, input and output capacitors, rectifying diodes and flyback converter IC.

#### 表 4. List of Components for Design 2

| REF DES            | QTY | SPECIFICATION                                       | VENDOR            | PART NUMBER          |

|--------------------|-----|-----------------------------------------------------|-------------------|----------------------|

|                    |     |                                                     | TDK               | CGA6M3X7S2A475K200AB |

| C <sub>IN</sub>    | 1   | 4.7 μF, 100 V, X7S, 1210, ceramic, AEC-Q200         | Murata            | GCM32DC72A475ME01    |

|                    |     |                                                     | Taiyo Yuden       | HMK325C7475MMHPE     |

|                    |     |                                                     | TDK               | CGA6P3X7R1E226M      |

| C <sub>OUT1</sub>  | 1   | 22 μF, 25 V, X7R, 1210, ceramic, AEC-Q200           | Murata            | GCM32EC71E226KE36    |

|                    |     |                                                     | Taiyo Yuden       | TMK325B7226KMHT      |

| C <sub>OUT2</sub>  | 1   | 47 μF, 10 V, X7S, 1210, ceramic, AEC-Q200           | Murata            | GCM32EC71H106KA03    |

| D <sub>FLY1</sub>  | 1   | Switching diode, fast recovery, 200 V, 1 A, SOD-123 | DFLU1200-7        | Diodes Inc.          |

| D <sub>FLY2</sub>  | 1   | Schottky diode, 100 V, 1 A, PowerDI-123, AEC-Q101   | DFLS1100Q-7       | Diodes Inc.          |

| D <sub>CLAMP</sub> | 1   | Zener, 24 V, 1 W, PowerDI-123, AEC-Q101             | DFLZ24Q-7         | Diodes Inc.          |

| D <sub>F</sub>     | 1   | Switching diode, 75 V, 0.3 A, SOD323, AEC-Q101      | 1N4148WSQ         | Diodes Inc.          |

| D <sub>OUT1</sub>  | 1   | Zener, 18 V, 5%, SOD523, AEC-Q101                   | BZX585-C18        | Nexperia             |

| D <sub>OUT2</sub>  | 1   | Zener, 8.2 V, 2%, SOD523, AEC-Q101                  | BZX585-B8V2       | Nexperia             |

| R <sub>FB</sub>    | 1   | 154 kΩ, 1%, 0402                                    | Std               | Std                  |

| R <sub>SET</sub>   | 1   | 12.1 kΩ, 1%, 0402                                   | Std               | Std                  |

| R <sub>TC</sub>    | 1   | 200 kΩ, 1%, 0402                                    | Std               | Std                  |

| R <sub>UV1</sub>   | 1   | 340 kΩ, 1%, 0603                                    | Std               | Std                  |

| R <sub>UV2</sub>   | 1   | 68.1 kΩ, 1%, 0402                                   | Std               | Std                  |

| T <sub>1</sub>     | 1   | 30 μH, 2 A, turns ratio 1 : 1: 0.55, 9 × 10 mm, SMT | Coilcraft         | YA8916-BL            |

| U <sub>1</sub>     | 1   | LM5180-Q1 PSR flyback converter, AEC-Q100           | Texas Instruments | LM5180QNGURQ1        |

#### 9.2.2.2 Detailed Design Procedure

Using the LM5180-Q1 quick-start calculator, components are selected based on the flyback converter specifications.

#### 9.2.2.2.1 Flyback Transformer - T<sub>1</sub>

Set the turns ratio of the transformer secondary windings using  $\pm$  29, where N<sub>S1</sub> and N<sub>S2</sub> are the number of secondary turns for the respective outputs.

$$\frac{N_{S2}}{N_{S1}} = \frac{V_{OUT2} + V_{D2}}{V_{OUT1} + V_{D1}} = \frac{7.7 \text{ V} + 0.3 \text{ V}}{15 \text{ V} + 0.3 \text{ V}} = 0.52$$

(29)

Choose a primary-secondary turns ratio for the 15-V output based on an approximate 60% max duty cycle at minimum input voltage using  $\pm$  30. The transformer turns ratio for both outputs is thus specified as 1 : 1 : 0.52.

$$N_{PS} = \frac{D_{MAX}}{1 - D_{MAX}} \cdot \frac{V_{IN(min)}}{V_{OUT} + V_{D}} = \frac{0.6}{1 - 0.6} \cdot \frac{9.5 \,\text{V}}{15 \,\text{V} + 0.3 \,\text{V}} \approx 1 \tag{30}$$

Select a magnetizing inductance based on the minimum off-time constraint using  $\pm$  31. Choose a value of 30  $\mu$ H with a saturation current of 2 A for this application.

$$L_{MAG} \ge \frac{\left(V_{OUT} + V_{D}\right) \cdot N_{PS} \cdot t_{OFF\text{-MIN}}}{I_{PRI\text{-PK(FFM)}}} = \frac{\left(15\,V + 0.3\,V\right) \cdot 1 \cdot 500\,\text{ns}}{0.3\,\text{A}} = 25.5\,\mu\text{H} \tag{31}$$

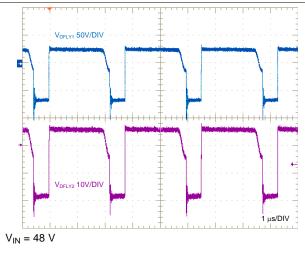

# 9.2.2.2.2 Flyback Diodes - D<sub>FLY1</sub> and D<sub>FLY2</sub>

The flyback diode reverse voltages for the positive and negative outputs are given respectively by  $\pm$  32 and  $\pm$  33.

$$V_{D1-REV} \ge \frac{V_{IN(max)}}{N_{PS}} + V_{OUT1} = \frac{65 \, V}{1} + 15 \, V = 80 \, V$$

(32)

$$V_{D2-REV} \ge \frac{V_{IN(max)}}{N_{PS}} + \left| V_{OUT2} \right| = 65 \, \text{V} \cdot 0.52 + 7.7 \, \text{V} = 41.5 \, \text{V}$$

(33)

Choose a 200-V, 1-A ultra-fast switching diode and a 100-V, 1-A Schottky diode for the positive and negative outputs, respectively, to allow some margin for inevitable voltage overshoot and ringing related to leakage inductance and diode capacitance. If needed, use a diode RC snubber circuit, for example 100  $\Omega$  and 22 pF, to mitigate such overshoot and ringing.

#### 9.2.2.2.3 Input Capacitor - CIN

The input capacitor,  $C_{IN}$ , filters the primary-side triangular current waveform. To prevent large ripple voltage, use a low-ESR ceramic input capacitor sized according to  $\pm$  23 for the RMS ripple current given by  $\pm$  24. In this design example, choose a 4.7- $\mu$ F, 100-V ceramic input capacitor with X7S dielectric10- $\mu$ F, 50-V ceramic input capacitor with X7R dielectric and 1210 footprint.

#### 9.2.2.2.4 Feedback Resistor - R<sub>FB</sub>

Install a 154-k $\Omega$  resistor from SW to FB based on an output voltage setpoint of 15 V (plus a flyback diode voltage drop) reflected to the primary by a transformer turns ratio of unity.

$$R_{FB} = \frac{\left(V_{OUT} + V_{D}\right) \cdot N_{PS}}{0.1 \text{ mA}} = \frac{\left(15 \text{ V} + 0.3 \text{ V}\right) \cdot 1}{0.1 \text{ mA}} = 154 \text{ k}\Omega$$

(34)

#### 9.2.2.2.5 UVLO Resistors - R<sub>UV1</sub>, R<sub>UV2</sub>

Given  $V_{IN(on)}$  and  $V_{IN(off)}$  as the input voltage turn-on and turn-off thresholds of 9 V and 7 V, respectively, select the upper and lower UVLO resistors using  $\pm$  35 and  $\pm$  36.

$$R_{UV1} = \frac{V_{IN(on)} \cdot \frac{V_{UV\text{-}FALLING}}{V_{UV\text{-}RISING}} - V_{IN(off)}}{I_{UV\text{-}HYST}} = \frac{9 \text{ V} \cdot \frac{1.45 \text{ V}}{1.5 \text{ V}} - 7 \text{ V}}{5 \text{ }\mu\text{A}} = 340 \text{ }k\Omega \tag{35}$$

$$R_{UV2} = R_{UV1} \cdot \frac{V_{UV-RISING}}{V_{IN(on)} - V_{UV-RISING}} = 340 \text{ k}\Omega \cdot \frac{1.5 \text{ V}}{9 \text{ V} - 1.5 \text{ V}} = 68 \text{ k}\Omega$$

(36)

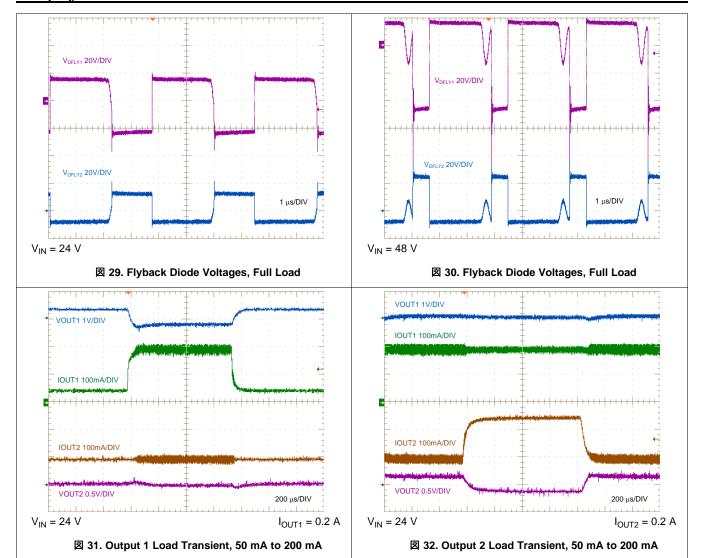

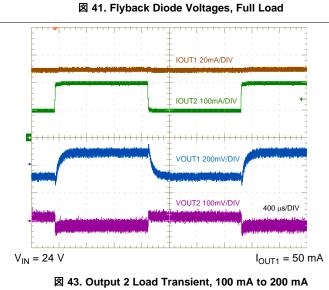

#### 9.2.2.3 Application Curves

STRUMENTS

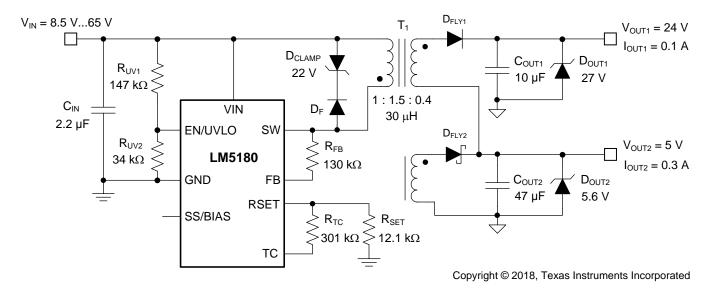

# 9.2.3 Design 3: PSR Flyback Converter With Stacked Dual Outputs of 24 V and 5 V

The schematic diagram of a dual-output flyback converter with high-voltage secondary stacked on the low-voltage secondary winding is given in 33. This configuration reduces the number of turns for the high-voltage output, resulting in lower secondary-to-secondary leakage inductance for improved output voltage cross regulation.

233. Schematic for Design 3 With  $V_{IN(nom)} = 24 \text{ V}$ ,  $V_{OUT1} = 24 \text{ V}$ ,  $V_{OUT2} = 5 \text{ V}$

#### 9.2.3.1 Design Requirements

The required input, output, and performance parameters for this application example are shown in 表 5.

DESIGN PARAMETERVALUEInput voltage range (steady state)8.5 V to 65 VOutput 1 voltage and current24 V, 0.1 AOutput 2 voltage and current5 V, 0.3 AInput UVLO thresholds8 V on, 7 V offOutput voltage regulation±1%

表 5. Design Parameters

The target full-load efficiency of this LM5180-Q1 design is 88% based on a nominal input voltage of 24 V and isolated output voltages of 24 V and 5 V. The selected flyback converter components are cited in 表 6, including multi-winding flyback transformer, input and output capacitors, rectifying diodes, and converter IC.

#### 表 6. List of Components for Design 3

| REF DES            | QTY | SPECIFICATION                                         | VENDOR            | PART NUMBER          |

|--------------------|-----|-------------------------------------------------------|-------------------|----------------------|

|                    | 0.0 | 0.0 v.E 400 V VZB 4040 paramia AEC 0000               | TDK               | CGA6N3X7R2A225K230AB |

| <u> </u>           | 4   | 2.2 μF, 100 V, X7R, 1210, ceramic, AEC-Q200           | Taiyo Yuden       | HMK325B7225KMHP      |

| C <sub>IN</sub>    | 1   | 2.2 µF, 100 V, X7S, 1206, ceramic, AEC-Q200           | TDK               | CGA5L3X7S2A225M      |

|                    |     | 2.2 μF, 100 V, λ73, 1206, ceramic, AEC-Q200           | Taiyo Yuden       | HMK316AC7225MLHTE    |

|                    |     | 10 μF, 50 V, X7R, 1210, ceramic, AEC-Q200             | Taiyo Yuden       | UMJ325KB7106KMHT     |

| C <sub>OUT1</sub>  | 1   | 40 UF FO V V7C 4240 postamin AFC 0200                 | Murata            | GCM32EC71H106KA03    |

|                    |     | 10 μF, 50 V, X7S, 1210, ceramic, AEC-Q200             | TDK               | CGA6P3X7S1H106M      |

| C <sub>OUT2</sub>  | 1   | 47 μF, 10 V, X7R, 1210, ceramic, AEC-Q200             | Murata            | GCM32EC71A476KE02    |

| D <sub>FLY1</sub>  | 1   | Switching diode, fast recovery, 200 V, 1 A, SOD-123   | DFLU1200          | Diodes Inc.          |

| D <sub>FLY2</sub>  | 1   | Schottky diode, 40 V, 1 A, SOD-123                    | B140HW            | Diodes Inc.          |

| D <sub>CLAMP</sub> | 1   | Zener, 22 V, 1 W, PowerDI-123, AEC-Q101               | DFLZ22-7          | Diodes Inc.          |

| D <sub>F</sub>     | 1   | Switching diode, 75 V, 0.25 A, SOD-323                | CMDD4448          | Central Semi         |

| D <sub>OUT1</sub>  | 1   | Zener, 27 V, 2%, SOD-523, AEC-Q101                    | BZX585-B27        | Nexperia             |

| D <sub>OUT2</sub>  | 1   | Zener, 5.6 V, 2%, SOD-523, AEC-Q101                   | BZX585-B5V6       | Nexperia             |

| R <sub>FB</sub>    | 1   | 130 kΩ, 1%, 0402                                      | Std               | Std                  |

| R <sub>SET</sub>   | 1   | 12.1 kΩ, 1%, 0402                                     | Std               | Std                  |

| R <sub>TC</sub>    | 1   | 301 kΩ, 1%, 0402                                      | Std               | Std                  |

| R <sub>UV1</sub>   | 1   | 147 kΩ, 1%, 0603                                      | Std               | Std                  |

| R <sub>UV2</sub>   | 1   | 34 kΩ, 1%, 0402                                       | Std               | Std                  |

| T <sub>1</sub>     | 1   | 30 μH, 2 A, turns ratio 1 : 1.5 : 0.4, 9 × 10 mm, SMT | Coilcraft         | YA8864-BL            |

| U <sub>1</sub>     | 1   | LM5180-Q1 PSR flyback converter, AEC-Q100             | Texas Instruments | LM5180QNGURQ1        |

#### 9.2.3.2 Detailed Design Procedure

Components are selected based on the converter specifications using the LM5180-Q1 quick-start calculator. The design procedure is similar to that outlined for Designs 1 and 2 previously.

#### 9.2.3.2.1 Flyback Transformer - T<sub>1</sub>

The 24-V output is DC stacked on top of the 5-V output as they share a common return connection. This enables lower secondary-to-secondary leakage inductance for better cross regulation and also reduced rectifier diode reverse voltage stress. Choose a primary-secondary turns ratio for the effective 19-V secondary based on an approximate 60% max duty cycle at minimum input voltage using  $\pm$  37.

$$N_{PS} = \frac{D_{MAX}}{1 - D_{MAX}} \cdot \frac{V_{IN(min)}}{V_{OUT} + V_{D}} = \frac{0.6}{1 - 0.6} \cdot \frac{8.5 \,\text{V}}{19 \,\text{V} + 0.3 \,\text{V}} = 0.66 \tag{37}$$

Set the turns ratio of the transformer secondary windings using  $\pm$  38. The transformer turns ratio for both outputs is thus specified as 1:1.5:0.4.

$$\frac{N_{S2}}{N_{S1}} = \frac{V_{OUT2} + V_{D2}}{V_{OUT1} + V_{D1}} = \frac{5 \text{ V} + 0.3 \text{ V}}{19 \text{ V} + 0.3 \text{ V}} = 0.275$$

(38)

As before, select a magnetizing inductance of 30 µH based on the minimum off-time constraint and specify a saturation current of 2 A to handle the peak primary current.

#### 9.2.3.2.2 Feedback Resistor - R<sub>FB</sub>

Install a 130-k $\Omega$  resistor from SW to FB based on the secondary winding voltage (the sum of the 5-V output voltage and the Schottky diode forward voltage drop) reflected by the relevant transformer turns ratio, which in this design is 1 : 0.4 or 2.5 : 1.

$$R_{FB} = \frac{\left(V_{OUT} + V_{D}\right) \cdot N_{PS}}{0.1 \, \text{mA}} = \frac{\left(5 \, \text{V} + 0.25 \, \text{V}\right) \cdot 2.5}{0.1 \, \text{mA}} = 130 \, \text{k}\Omega \tag{39}$$

# 9.2.3.2.3 UVLO Resistors - R<sub>UV1</sub>, R<sub>UV2</sub>

Given  $V_{IN(on)}$  and  $V_{IN(off)}$  as the input voltage turn-on and turn-off thresholds of 8 V and 7 V, respectively, select the upper and lower UVLO resistors using the following expressions:

$$R_{UV1} = \frac{V_{IN(on)} \cdot \frac{V_{UV\text{-}FALLING}}{V_{UV\text{-}HISING}} - V_{IN(off)}}{I_{UV\text{-}HYST}} = \frac{8 \ V \cdot \frac{1.45 \ V}{1.5 \ V} - 7 \ V}{5 \ \mu A} = 147 \ k\Omega \tag{40}$$

$$R_{UV2} = R_{UV1} \cdot \frac{V_{UV-RISING}}{V_{IN(on)} - V_{UV-RISING}} = 147 \text{ k}\Omega \cdot \frac{1.5 \text{ V}}{8 \text{ V} - 1.5 \text{ V}} = 34 \text{ k}\Omega$$

$$(41)$$

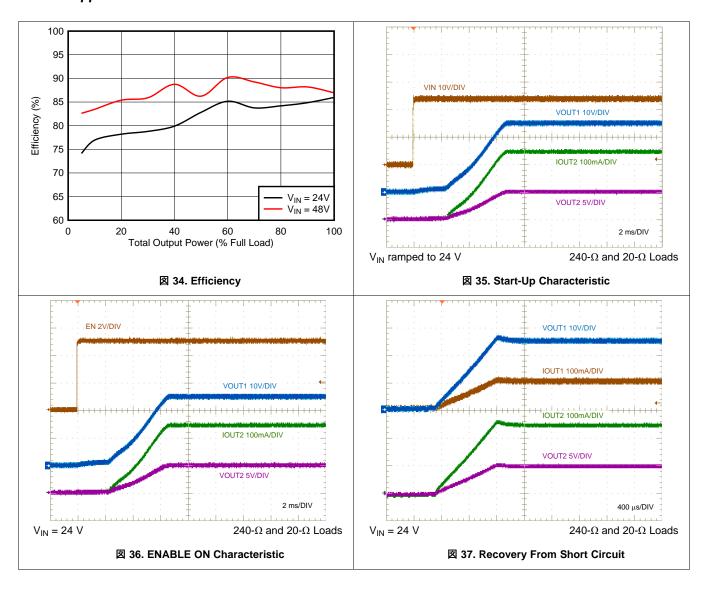

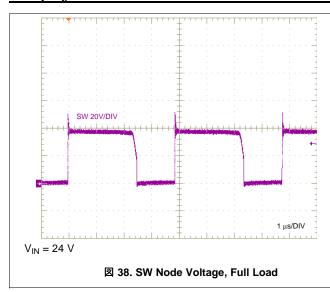

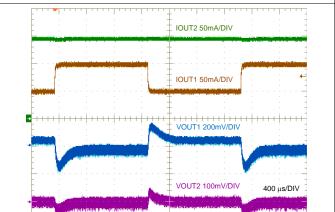

#### 9.2.3.3 Application Curves

**STRUMENTS**

29

図 42. Output 1 Load Transient, 50 mA to 100 mA

$I_{OUT2} = 150 \text{ mA}$

$V_{IN} = 24 V$

# 10 Power Supply Recommendations

The LM5180-Q1 flyback converter is designed to operate from a wide input voltage range from 4.5 V to 65 V. The characteristics of the input supply must be compatible with the Absolute Maximum Ratings and Recommended Operating Conditions. In addition, the input supply must be capable of delivering the required input current to the fully-loaded regulator. Estimate the average input current with  $\pm$  42.

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta}$$

where

If the converter is connected to an input supply through long wires or PCB traces with a large impedance, special care is required to achieve stable performance. The parasitic inductance and resistance of the input cables may have an adverse affect on converter operation. The parasitic inductance in combination with the low-ESR ceramic input capacitors form an underdamped resonant circuit. This circuit can cause overvoltage transients at VIN each time the input supply is cycled ON and OFF. The parasitic resistance causes the input voltage to dip during a load transient. If the regulator is operating close to the minimum input voltage, this dip can cause false UVLO fault triggering and a system reset. The best way to solve such issues is to reduce the distance from the input supply to the regulator and use an aluminum electrolytic input capacitor in parallel with the ceramics. The moderate ESR of the electrolytic capacitors helps to damp the input resonant circuit and reduce any voltage overshoots. A capacitance in the range of 10  $\mu$ F to 47  $\mu$ F is usually sufficient to provide input damping and helps to hold the input voltage steady during large load transients. A typical ESR of 0.25  $\Omega$  provides enough damping for most input circuit configurations.

An EMI input filter is often used in front of the regulator that, unless carefully designed, can lead to instability as well as some of the effects mentioned above. The application report Simple Success with Conducted EMI for DC-DC Converters provides helpful suggestions when designing an input filter for any switching regulator.

# 11 Layout

The performance of any switching converter depends as much upon PCB layout as it does the component selection. The following guidelines are provided to assist with designing a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

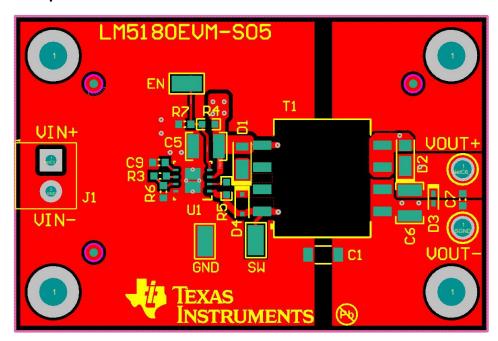

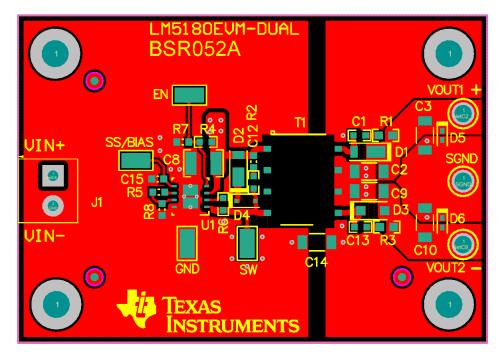

44 and 45 provide layout examples for single-output and dual-output designs, respectively.

#### 11.1 Layout Guidelines

PCB layout is a critical for good power supply design. There are several paths that conduct high slew-rate currents or voltages that can interact with transformer leakage inductance or parasitic capacitance to generate noise and EMI or degrade the power supply's performance.

- 1. Bypass the VIN pin to GND with a low-ESR ceramic capacitor, preferably of X7R or X7S dielectric. Place C<sub>IN</sub> as close as possible to the LM5180-Q1 VIN and GND pins. Ground return paths for the input capacitor(s) must consist of localized top-side planes that connect to the GND pin and exposed PAD.

- 2. Minimize the loop area formed by the input capacitor connections and the VIN and GND pins.

- 3. Locate the transformer close to the SW pin. Minimize the area of the SW trace or plane to prevent excessive e-field or capacitive coupling.

- 4. Minimize the loop area formed by the diode-Zener clamp circuit connections and the primary winding terminals of the transformer.

- 5. Minimize the loop area formed by the flyback rectifying diode, output capacitor and the secondary winding terminals of the transformer.

- 6. Tie the GND pin directly to the power pad under the device and to a heat-sinking PCB ground plane.

- 7. Use a ground plane in one of the middle layers as a noise shielding and heat dissipation path.

- 8. Have a single-point ground connection to the plane. Route the return connections for the reference resistor, soft-start, and enable components directly to the GND pin. This prevents any switched or load currents from flowing in analog ground traces. If not properly handled, poor grounding results in degraded load regulation or erratic output voltage ripple behavior.

- 9. Make V<sub>IN+</sub>, V<sub>OUT+</sub> and ground bus connections short and wide. This reduces any voltage drops on the input or output paths of the converter and maximizes efficiency.

- 10. Minimize trace length to the FB pin. Locate the feedback resistor close to the FB pin.

- 11. Locate components  $R_{\text{SET}}$ ,  $R_{\text{TC}}$  and  $C_{\text{SS}}$  as close as possible to their respective pins. Route with minimal trace lengths.

- 12. Place a capacitor between input and output return connections to route common-mode noise currents directly back to their source.

- 13. Provide adequate heatsinking for the LM5180-Q1 to keep the junction temperature below 150°C. For operation at full rated load, the top-side ground plane is an important heat-dissipating area. Use an array of heat-sinking vias to connect the exposed PAD to the PCB ground plane. If the PCB has multiple copper layers, connect these thermal vias to inner-layer ground planes. The connection to V<sub>OUT+</sub> provides heatsinking for the flyback diode.

# 11.2 Layout Examples

図 44. LM5180-Q1 Single-Output PCB Layout

図 45. LM5180-Q1 Dual-Output PCB Layout

# 12 デバイスおよびドキュメントのサポート

# 12.1 デバイス・サポート

#### 12.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供される場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワークの製品またはサービスの是認の表明を意味するものではありません。

#### 12.1.2 開発サポート

開発サポートについては、以下を参照してください。

- LM5180-Q1 クイックスタート・カリキュレータ

- LM5180-Q1 シミュレーション・モデル

- TIのリファレンス・デザイン・ライブラリについては、TIDesignsを参照してください。

- TIのWEBENCH設計環境については、WEBENCH®デザイン・センターを参照してください。

- この製品の関連デバイスについては、LM25180-Q1 を参照してください。

#### 12.1.3 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designerにより、LM5180-Q1デバイスを使用するカスタム設計を作成できます。

- 1. 最初に、入力電圧(V<sub>IN</sub>)、出力電圧(V<sub>OUT</sub>)、出力電流(I<sub>OUT</sub>)の要件を入力します。

- 2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットで出力する。

- 設計のレポートをPDFで印刷し、設計を共有する。

WEBENCHツールの詳細は、www.ti.com/WEBENCHでご覧になれます。

## 12.2 ドキュメントのサポート

#### 12.2.1 関連資料

関連資料については、以下を参照してください。

- 『LM5180EVM-S05 EVMユーザー・ガイド』(SNVU592)

- 『LM5180EVM-DUAL EVMユーザー・ガイド』(SNVU609)

- 『フライバックSMSP設計の詳細解説』(SLUP261)

- 『フライバック変圧器の設計における効率とEMIの考慮事項』(SLUP338)

- TI Designs

- スイッチ内蔵PSRフライバック・コントローラ搭載、絶縁型IGBTゲート・ドライブ向け電源のリファレンス・デザイン

- 簡略型のトランスを使用するスナバレスの非絶縁型AC/DCフライバック・コンバータのリファレンス・デザイン

- TIブログ

- 「フライバック・コンバータ: 2つの出力が1つより適切な理由」

- 「サーバーPSU用の補助電源を選択するときの一般的な課題」

- 「限られた予算でPoE PDの効率を最大化する方法」

# ドキュメントのサポート (continued)

- ホワイト・ペーパー

- 『コストが重要で、要求の厳しいアプリケーション向けの広VIN、低EMI同期整流降圧回路の評価』(SLYY104)

- 『電源の伝導EMI仕様の概要』(SLYY136)

- 『電源の放射EMI仕様の概要』(SLYY142)

- **『AN-2162: DC/DC**コンバータから伝導されるEMIでの簡単な成功』(SNVA489)

- 『車載用クランキング・シミュレータ・ユーザー・ガイド』(SLVU984)

- 『新しい熱測定基準の使用』(SBVA025)

- 『半導体とICパッケージの熱指標』(SPRA953)

## 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受 け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細に ついては、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 12.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.5 商標

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感 であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

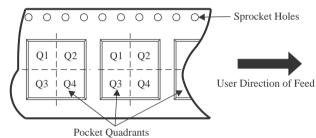

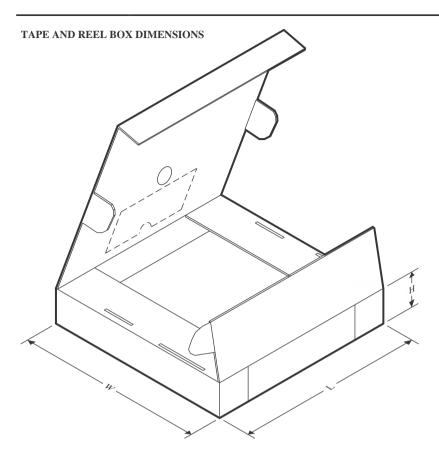

# 13 メカニカル、パッケージ、および注文情報

以下のページには、メカニカル、パッケージ、および注文の情報が記載されています。これらの情報は、指定のデバイスに 対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあり ます。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

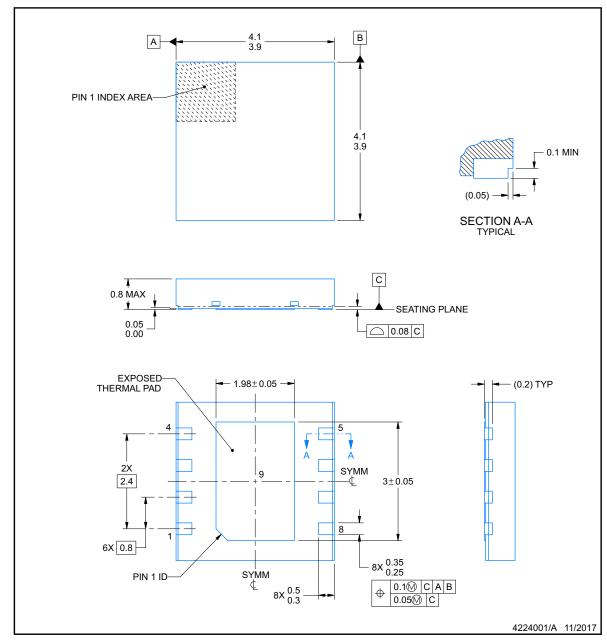

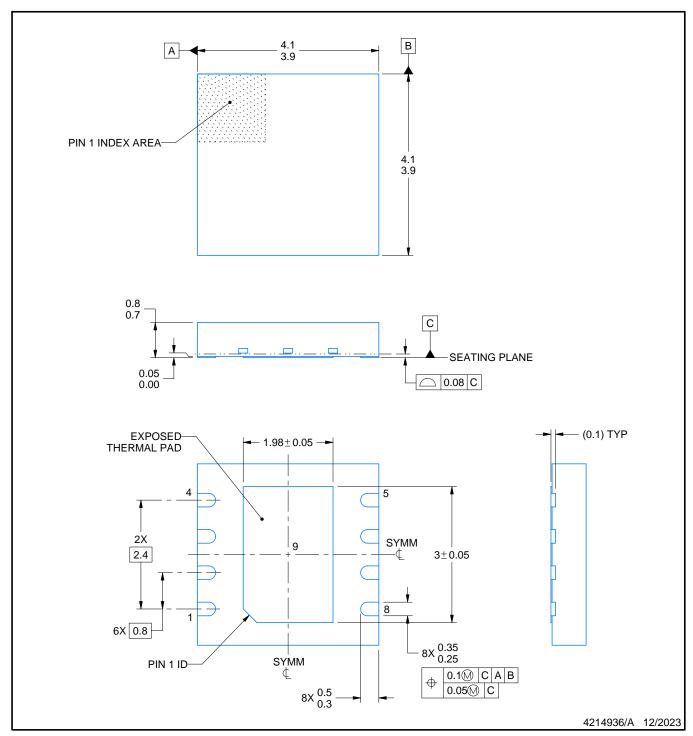

# **NGU0008C**

# **PACKAGE OUTLINE**

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

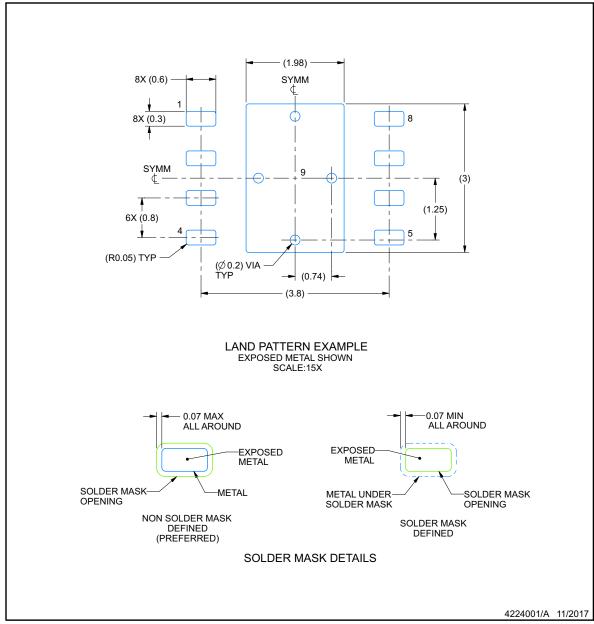

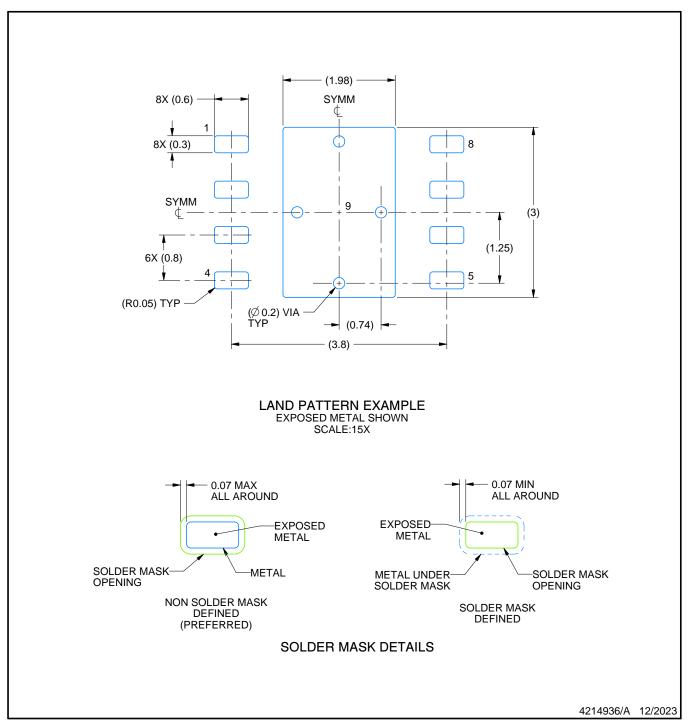

# **EXAMPLE BOARD LAYOUT**

# NGU0008C

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

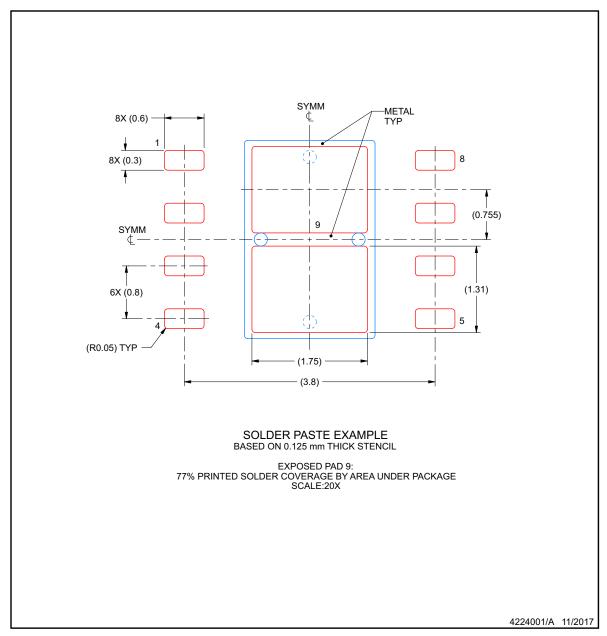

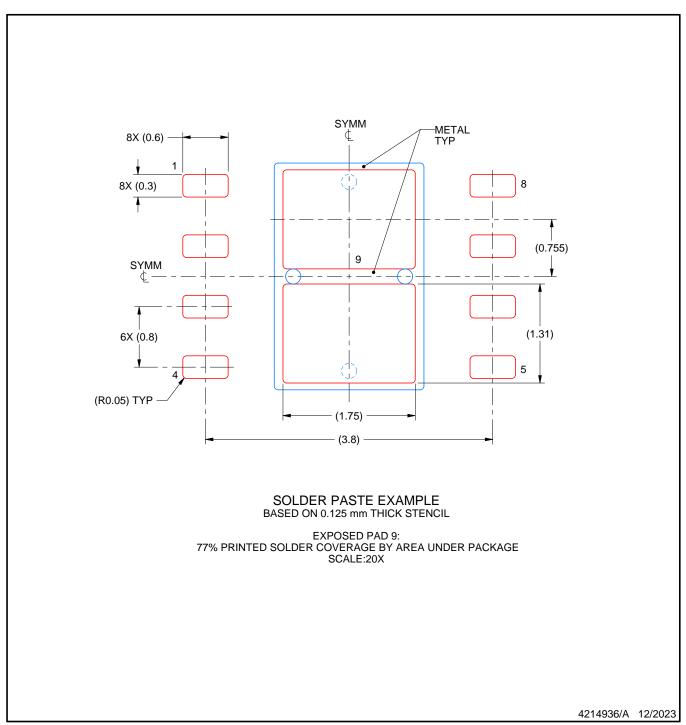

# **EXAMPLE STENCIL DESIGN**

# **NGU0008C**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

www.ti.com 28-Mar-2024

#### PACKAGING INFORMATION