*Errata***AWR2544 デバイスエラッタ****目次**

|                                      |    |

|--------------------------------------|----|

| 1 はじめに.....                          | 2  |

| 2 デバイスの命名規則.....                     | 2  |

| 3 デバイスのマーキング.....                    | 3  |

| 4 シリコン バリアント / リビジョン マップのアドバイザリ..... | 4  |

| 5 機能仕様に対する既知の設計例外.....               | 5  |

| 6 改訂履歴.....                          | 41 |

## 1 はじめに

このドキュメントでは、テキサス インstrument CMOS レーダー デバイス (AWR2544) の機能および性能仕様に関する既知の例外について説明します。

## 2 デバイスの命名規則

製品開発サイクルの段階を示すために、テキサス インstrument ではレーダー / ミリ波センサ デバイスの型番に接頭辞が割り当てられています。各レーダー デバイスには、次の 2 つのうちいずれかの接頭辞が付いています。XAx または AWR2x (例: XA2E44BGALTX)。これらの接頭辞は、エンジニアリング プロトタイプ (XAx) から完全認定された量産デバイス (AWR2x) までの製品開発の進化段階を表します。

デバイスの開発進展フロー:

- XAx** — 実験的デバイス。最終デバイスの電気的特性を必ずしも表さず、量産アセンブリ フローを使用しない可能性があります。

- AWR2x** — 認定済みのシリコン ダイの量産バージョン。

XAx デバイスには次の免責事項が添付されて出荷されます。

「開発中の製品は、社内での評価用です。」

これらのデバイスは予測される最終使用時の故障率が未定義であるため、テキサス インstrument ではそれらのデバイスを量産システムで使用しないよう推奨しています。

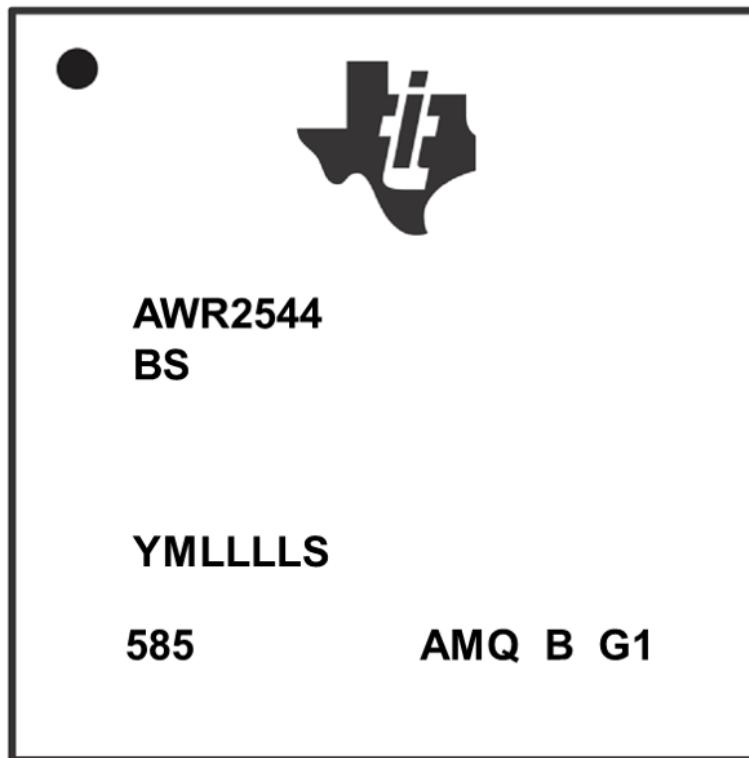

### 3 デバイスのマーキング

図 3-1 に、AWR2544 レーダー デバイスのパッケージ シンボルの例を示します。

図 3-1. デバイス部品のマーキングの例

この識別番号には、次の情報が含まれます。

- **1 行目:** デバイス番号

- **2 行目:** 安全レベルとセキュリティ グレード

- **3 行目:** ロットのトレース コード

- YM = 年 / 月 日付コード

- Z = セカンダリ サイト コード

- LLLL = アセンブリ ロット コード

- S = プライマリ サイト コード

- **4 行目:**

- 585 = のデバイス 識別子

- AMQ = パッケージ 識別子

- G1 = 「Green」パッケージ ビルド (下線付きにする必要があります)

## 4 シリコン バリアント / リビジョン マップのアドバイザリ

表 4-1. シリコン バリアント / リビジョン マップ

| アドバイザリ番号    | アドバイザリタイトル                                                                                        | AWR2544 |

|-------------|---------------------------------------------------------------------------------------------------|---------|

| メイン サブシステム  |                                                                                                   |         |

| MSS 第 25 章  | システム リセットが発生すると、デバッガはメモリ ブラウザ ウィンドウに予期しないデータを表示することがあります                                          | X       |

| MSS 第 27 章  | 低速 SPICLK 周波数およびクロック位相 = 1 の場合、ペリフェラル モードの 3 ピンまたは 4 ピン通信の MibSPI がデータを正しく送信しない                   | X       |

| MSS 第 28 章  | IO ループバックが有効化されている場合、ペリフェラル モードでデータ長エラーが繰り返し生成される                                                 | X       |

| MSS 第 29 章  | ペリフェラル モード MibSPI からのスプリアス RX DMA REQ                                                             | X       |

| MSS 第 30 章  | 読み取り後、MibSPI RX RAM RXEMPTY ビットがクリアされない                                                           | X       |

| MSS 第 33 章  | MibSPI RAM ECC は DIAG モードで正しく読み取られません。                                                            | X       |

| MSS 第 40 章  | ハードウェアアクセラレータの ACCEL_MEM1 + ACCEL_MEM2 メモリにまたがる EDMA 転送は、SoC からのエラー通知なしにデータ破損を引き起こす可能性があります。      | X       |

| MSS 第 49 章  | Aurora 64B/66B プロトコルにおけるオーバーフロー メッセージ送信時に、厳密整列ユーザーフロー コントロール ストリッピングのみをサポートする受信機との潜在的な相互運用性に関する問題 | X       |

| MSS 第 52 章  | DSS L2 パリティの問題: DSP が構成済みメモリ サイズを超えるアクセスを送信した場合                                                   | X       |

| MSS 第 53 章  | HWA 2.0 の最後のパラメータ セットでコンテキスト スイッチが発生したときの不正な動作                                                    | X       |

| MSS 第 54 章  | Aurora TX UDP サイズ <= 4 は無効です                                                                      | X       |

| MSS 第 55 章  | チャーブからチャーブへの階段モードでの PMIC CLKOUT ディザリングはサポートされていません。                                               | X       |

| MSS 第 56 章  | CR4 STC ブートモニター障害                                                                                 | X       |

| MSS 第 57 章  | フラッシュ / マーカーで観測されたデータの損失、または MDO インターフェイスでパケットの完了。                                                | X       |

| MSS 第 58 章  | ePWM: チョッパ動作モード中のグリッチ                                                                             | X       |

| MSS 第 59 章  | CRC: CAN モジュールでは CRC 8 ビット データ幅と CRC8-SAE-J1850 および CRC8-H2F がサポートされない                            | X       |

| MSS 第 60 章  | PCR の 6 つの内部レジスタの読み出しおよび書き込みアドレスの不一致                                                              | X       |

| MSS 第 61 章  | 構成されている MPU 領域の最後の 24 バイトへのアクセスが行われ、キヤッシュが有効になっている時のデータの打ち切り                                      | X       |

| MSS 第 62 章  | FFT3X パラメータセットの双方向使用での、HWA の停止                                                                    | X       |

| MSS 第 63 章  | ブロックコヒーレンス操作中に L2 キヤッシュが破損する可能性がある問題                                                              | X       |

| MSS 第 64 章  | シングル MFENCE の問題                                                                                   | X       |

| MSS 第 65 章  | ブロックおよびグローバルコヒーレンス操作中の L2 キヤッシュ破損の問題                                                              | X       |

| MSS 第 68 章  | HWA の Real2X FFT モードでは、0 番目の BCNT の FFT データが破損する可能性があります。                                         | X       |

| MSS 第 71 章  | シングル ビット ECC (エラー訂正) メカニズムにより、メモリの誤った更新が発生する可能性                                                   | X       |

| アナログ / ミリ波  |                                                                                                   |         |

| ANA 第 12A 章 | レシーバに存在する第 2 高調波 (HD2)                                                                            | X       |

| ANA 第 37A 章 | LO 周波数全体での RX ゲインの大幅きく低下                                                                          | X       |

| ANA 第 39 章  | HPF カットオフ周波数を 2800kHz に設定すると、RX IFA ゲインとフィルター コーナー周波数が不正確になる可能性があります。                             | X       |

| ANA 第 43 章  | シンセサイザ周波数ライブモニターに表示されるエラー                                                                         | X       |

| ANA 第 44 章  | 3.3V IO モードでは、3.3V レールから 1.8V レールに逆電力が供給されます。                                                     | X       |

| ANA 第 45 章  | デジタル動作によるスプリアスが発生しました。                                                                            | X       |

| ANA 第 47 章  | アイドル チャネル シナリオで RX 全体で観測された RX スプリアス                                                              | X       |

| ANA 第 59 章  | OSC_CLK_OUT_ETH 動作にリスプリアスが発生します                                                                   | X       |

## 5 機能仕様に対する既知の設計例外

### MSS 第 25 章

システムリセットが発生すると、デバッガはメモリブラウザウィンドウに予期しないデータを表示することがあります

### 影響を受けるリビジョン:

... AWR2544

#### 説明:

デバッガがシステムビューを使用してシステムリソースにアクセスしているときにシステムリセット (nRST が Low) が発生した場合、デバッガにはペリフェラルエラーが応答されるはずです。アクセスが読み取りだった場合、応答はアクセスが正常に完了したことを示し、予期しないデータを返す可能性があります。

この問題は、デバッガがシステムビューを使用してシステムへのアクセスを完了しているときに、特定のサイクルでシステムリセットがアサート (nRST が Low) された場合に発生します。例としては、CCS-IDE メモリブラウザウィンドウなどのデバッガがシステムビューを使用してコンテンツを更新している場合が挙げられます。これは、CPU のみのリセットでは問題にならず、パワーオンリセット (nPORRST) でも問題にはなりません。

#### 回避方法:

デバイスがリセット状態にある間は、デバッグの読み取りと書き込みを実行しないでください。

**MSS 第 27 章**

低速 **SPICLK** 周波数およびクロック位相= 1 の場合、ペリフェラル モードの 3 ピンまたは 4 ピン通信の **MibSPI** がデータを正しく送信しない

**影響を受けるリビジョン:**

AWR2544

**説明:**

MibSPI モジュールを、3 つの機能ピン (CLK、SIMO、SOMI) または 4 つの機能ピン (CLK、SIMO、SOMI、nENA) でマルチバッファ ペリフェラル モードに構成している場合、以下のすべての条件が満たされると誤ったデータを送信する可能性があります。

- MibSPI モジュールは、マルチバッファモードに構成されています。

- モジュールは、SPI 通信のペリフェラルとして設定されています。

- SPI 通信は nENA を使用して 3 ピンモードまたは 4 ピンモードに設定されています。

- SPICLK のクロック位相は 1 です。

- SPICLK 周波数が MSS\_VCLK 周波数/12 以下

**回避方法:**

この問題は、TX RAM (マルチバッファ RAM 送信データレジスタ) の制御フィールドの CSHOLD ビットをセットすることによって回避できます。この通信では、nCS を機能信号として使用しないため、CSHOLD ビットをセットしても SPI 通信にこれ以外の影響は発生しません。

**MSS 第 28 章** *IO ループバックが有効化されている場合、ペリフェラル モードでデータ長エラーが繰り返し生成される*

**影響を受けるリビジョン:** AWR2544

**説明:** IO ループバック テスト モードの nSCS ピンを使用して SPI のペリフェラル モードで DLEN エラーが生成された場合、SPI モジュールは現在の転送を中止し停止する代わりに、DLEN エラーのあるデータを再送信します。これは、CTRLDLENERR (IOLPBKTSTCR.16) を使用して意図的なエラー生成機能がトリガされた場合に、アナログ ループバック構成の IOLPBK モード ペリフェラルでのみ問題になります。

**回避方法:** IOLPBK モードで DLEN\_ERR 割り込みが検出された後、SPIGCR1 レジスタの SPIEN (ビット 24) をクリアして転送を無効化してから、SPIEN ビットをリセットして転送を再度有効化します。

**MSS 第 29 章****ペリフェラル モード *MibSPI* からのスプリアス RX DMA REQ****影響を受けるリビジョン:**

AWR2544

**説明:**

SPI ペリフェラルが次の条件シーケンスでデータを転送していない場合でも、スプリアス DMA 要求が生成される可能性があります。

- MIBSPI が、標準(非マルチバッファ) SPI モードで、ペリフェラルとして構成される

- DMAREQEN ビット (SPIINT0.16) が、DMA 要求を有効にするように設定される

- チップセレクト (nSCS) ピンがアクティブ状態であるながら、転送がアクティブでない

- SPI は、SPIEN (SPIGCR1.24) ビットを「1」から「0」にクリアすることによって無効化される

上記のシーケンスでは、SPIEN ビットが「1」から「0」にクリアされるとすぐに、受信 DMA 要求に誤った要求パルスがトリガれます。

**回避方法:**

SPIEN ビット (SPIGCR1.24) をクリアして SPI を無効化する場合は常に、最初に DMAREQEN ビット (SPIINT0.16) を「0」にクリアし、次に SPIEN ビットをクリアします。

## MSS 第 30 章

### 読み取り後、*MibSPI RX RAM RXEMPTY* ビットがクリアされない

影響を受けるリビジョン:

AWR2544

**説明:**

以下の条件が満たされている場合、CPU または DMA の読み取り後、RXEMPTY フラグが自動的にクリアされない可能性があります。

- 現在アクティブな転送グループについて、シーケンサが RAM 送信から読み取った最新のバッファの TXFULL フラグが 0 である。

- より優先度の高い転送グループが現在の転送グループに割り込むと、シーケンサは RAM 送信から新しい転送グループの最初のバッファの読み取りを開始する。

- 同時に、ホスト (CPU / DMA) は、以前の転送から有効な受信データを含む RAM 受信の位置を読み取っている。

**回避方法:**

転送グループが相互に割り込むことを避けてください。

ダミーバッファが優先度の低い転送グループで使用されている場合は、「サスPEND」モードを使用する必要がある場合を除き、適切な「BUFMODE」を選択します (SKIP/DISABLED など)。

**MSS 第 33 章** *MibSPI RAM ECC は DIAG モードで正しく読み取られません。***影響を受けるリビジョン:** AWR2544

**説明:** 拡張バッファ サポートが実装されていても、特定の MibSPI インスタンスで拡張モードが無効化されている場合、DIAG モードの MibSPI RAM の ECC アドレス空間に対する読み取り動作は、最初の 128 バッファの正しい ECC 値を返しません。

**回避方法:** なし

## MSS 第 40 章

ハードウェアアクセラレータの **ACCEL\_MEM1 + ACCEL\_MEM2** メモリにまたがる **EDMA 転送** は、**SoC** からのエラー通知なしにデータ破損を引き起こす可能性があります。

### 影響を受けるリビジョン:

AWR2544

#### 説明:

TPTC IP 仕様によると、転送要求 (TR) はシングル ペリフェラル エンドポイントにアクセスするものとされています。HWA の ACCEL\_MEM0 / ACCEL\_MEM1 メモリバンクはシングルフェラル ポイント経由でアクセスでき、HWA の ACCEL\_MEM2 / ACCEL\_MEM3 メモリバンクは別のペリフェラルポイント (ACCEL\_MEM0 / ACCEL\_MEM1 とは異なる) として利用できます。したがって、シングル TR を使用して HWA の ACCEL\_MEM1 と ACCEL\_MEM2 メモリにまたがるバッファ (つまり、2 つの異なるペリフェラルポイントにまたがるシングルバッファ) にアクセスする場合、仕様に準拠していません。このエラッタは、この仕様要件を明確に示しています。

#### 注

ACCEL\_MEM1 および ACCEL\_MEM2 メモリは、SoC レベルでは DSS\_HWA\_DMA0 および DSS\_HWA\_DMA1 と呼ばれます。

#### 回避方法:

アクセスを 2 つの TR に分割し、1 つの TR が ACCEL\_MEM1 と ACCEL\_MEM2 にまたがらないようにします。2 つの TR はチェーン接続できます。

**MSS 第 49 章**

**Aurora 64B/66B** プロトコルでのオーバーフロー メッセージ送信中に、**厳密整列** ユーザーフロー コントロール ストリッピングのみをサポートする受信機との潜在的な相互運用性で問題が発生しています。

**影響を受けるリビジョン**

AWR2544

**詳細**

測定データ出力 (MDO) は、デバイスのさまざまなインターフェイスから接続されたバス上の送信をキャプチャし、Aurora LVDS インターフェイス (4 データレーン) を介して外部に送信するためを使用されます。MDO は、スニファ、FIFO、アグリゲータで構成されます。MDO スニファ モジュールは、チップ内のハードウェア インターフェイスを監視し、監視対象となっている構成されたアドレス領域内でのバス上のトランザクションをキャプチャします。

オーバーフローによるデータ損失は、スニファで発生する可能性があります。このオーバーフロー情報は、CPU および Aurora Tx IP に割り込みとして送信されます。このエラー状態をユーザーに通知するために、データ オーバーフロー状態の場合には、Aurora TX IP によって User-Flow-Control (UFC) パケットが生成されます。これはエラーシナリオであり、通常の転送機能では発生しないと想定されています。この段階では、データの整合性はすでに損なわれています。

Aurora IP は、Aurora 64B/66B プロトコル仕様のセクション 6.6 に従った UFC パケット生成のみをサポートしています。つまり、UFC ヘッダー ブロックは UFC データ ブロックの前にあります。**厳密整列** ユーザーフロー コントロール ストリッピング (Aurora 64B/66B プロトコル仕様のセクション 6.7 を参照) は現在サポートされていません。

**回避方法**

MDO の場合、オーバーフロー状態を完全に回避するために、実効データレートを適切な範囲内に維持するために、入力データレートは出力データレートよりも低くする必要があります。

**注**

Aurora 64B/66B プロトコルでは、オーバーフローなしで UFC パケットを送信するために `TOP_AURORA_TX:AURORA_TX_UFC_MSG_REQ` レジスタを使用することは推奨されません。

## MSS 第 52 章

### DSS L2 パリティの問題:DSP が構成済みメモリ サイズを超えるアクセスを送信した場合

影響を受けるリビジョン:

AWR2544

説明:

DSP IP は、設定された DSP L2 メモリ サイズ 384 KB (予約領域アクセス) を超える、つまり 0x8085 FFFC を超えるアクセスのために L2 メモリへのアクセスを送信しています。

パリティが有効になっている場合、0x80860000 ~ 0x8087FFFC を超える予約領域への読み取りで L2 パリティエラーが発生します。

注

0x80860000 ~ 0x8087FFFC の予約済みメモリ位置は、読み取りおよび書き込みができます。0x80860000 ~ 0x8087FFFC のメモリ位置は 0x80840000 ~ 0x8085FFFC にエイリアスされ、0x80850000 ~ 0x8085FFFC は 0x80870000 ~ 0x8087FFFC にレプリケートされるため、実際の L2RAM は 384KB のみとなります。

回避方法:

#### MPU:(L2MPPA24 - L2MPPA31) を 0 に設定

予約済み領域への書き込みアクセスはブロックされます。エイリアシング エラーも L2 パリティ エラーもありません。これにより、有効な L2 領域のデータ整合性が維持されます。

予約領域への読み取りアクセスは、L2 パリティ エラー (パリティが有効になっている場合) を引き起こします。

デバッグ アクセス (読み取り / 書き込み) はブロックされません: 引き続き、エイリアシング + L2 パリティ エラーが生じます: 保護用の MPU を有効化するよう設定しているにもかかわらず、デバッグ アクセスをブロックすることは不可能です

メモリ保護フォルト アドレス レジスタ (0184 A000h:: L2MPFAR/0184 AC00h:: L1DMPFAR) には、ブロックされたアドレス (この場合は 384KB 境界を越えるアドレス) が入力され、アクセスされたままになります

アドレス (L2MPFAR/L1DMPFAR) およびステータス (L2MPFSR/L1DMPFSR) レジスタは、値が 1 のクリア レジスタ (L2MPFCR/L1DMPFCR) を用いて、次の読み取りのためにクリアする必要があります

結果 (L1D キャッシュが有効の場合と無効の場合の両方)

読み取りの場合:L1MPFAR レジスタへのアドレス アクセスがブロックされた状態で、L1D において MPU 保護エラーが発生します

書き込みの場合:L2MPFAR レジスタへのアドレス アクセスがブロックされた状態で、L2 において MPU 保護エラーが発生します

**MSS 第 53 章**

ハードウェアアクセラレータ(HWA 2.1) の最後のパラメータセットでコンテキストスイッチが発生した場合に発生する不正な動作

**影響を受けるリビジョン:**

、 AWR2544 のみ

**説明:**

低優先度コンテキストの最後のループの最終パラメータセットの終了時に、高優先度コンテキストへのコンテキストスイッチが発生した場合、低優先度コンテキストに戻る際に不正な動作が観察されます。この不正な動作は、低優先度ループの完了後に、新たに(意図せずに)再開されるという形で現れる可能性があります。エラーが発生する条件は次のとおりです。

- 低優先度スレッドの最後のパラメータセットに CONTEXT\_SW\_EN または FORCED\_CONTEXT\_SW\_EN が設定されている。

同様に、高優先度スレッドの最終パラメータセットでは、強制コンテキストスイッチ(FORCED\_CONTEXT\_SW\_EN)を有効にしないでください。

**回避方法:**

上記の条件における最終パラメータセットでは、コンテキストスイッチを有効にしないことを推奨します。最終パラメータセットでコンテキストスイッチをイネーブルにする必要がある場合、コンテキストスイッチを無効にしたダミーのパラメータセットを最終パラメータセットとして追加することができます。

## MSS 第 54 章

### Aurora TX UDP サイズ <= 4 は無効です

影響を受けるリビジョン:

AWR2544

**説明:**

転送中、Aurora TX UDP サイズ <= 4 は無効です。

Aurora 8b/10b および Aurora 64b/66b で有効な UDP サイズは次のとおりです。

1. AURORA\_TX\_UDP\_CONFIG\_PACK\_MODE\_SEL = 0 (バイト): 有効な udp サイズ - AURORA\_TX\_UDP\_SIZE = 8, 12, 16, 20 など

2. AURORA\_TX\_UDP\_CONFIG\_PACK\_MODE\_SEL = 1 (TWP): 有効な udp サイズ - AURORA\_TX\_UDP\_SIZE = 5, 6, 7, 8 など

**回避方法:**

上記の有効な UDP サイズのみを使用することをお勧めします。

**MSS 第 55 章**

チャーブからチャーブへの階段モードでの **PMIC CLKOUT** ディザリングはサポートされていません。

**影響を受けるリビジョン:**

AWR2544

**説明:**

PMIC CLKOUT には、CLK スプリアスの影響を軽減するために、CLK 周波数にディザリングを追加するオプションがあります。連続モードのディザリングはサポートされていますが、チャーブからチャーブへの階段波モードのディザリングはサポートされていません。これは、DFE リセットが PMIC CLKOUT ブロックに届かないためです。

**回避方法:**

PMIC CLKOUT では連続ディザリング モードを使用することを推奨します。

## MSS 第 56 章

### CR4 STC ブートモニター障害

影響を受けるリビジョン:

、 AWR2544 のみ

説明:

デバイスで Cortex CR4 STC ブートモニタ障害が発生しています。

回避方法:

セカンダリブートローダ (SBL) で CR4 (BSS) の実行を開始する前に、シーケンス (MSS\_CTRL:MSS\_PBIST\_KEY\_RST[3:0] = 0) を実行して PBIST レジスタをクリアすることを推奨します。テキサス インstrumentation が提供する SBL サンプルコードを参照してください。

**MSS 第 57 章** フラッシュ / マーカーで観測されたデータの損失、または **MDO** インターフェイスでパケットの完了。

**影響を受けるリビジョン:** AWR2544

**説明:** 421-24008 : MDO 経由で送信されたデータフレームは、フレーム末尾の最後の 6 バイトを破棄します。

MDO 経由の `data_size = 6` のデータ転送で、データが欠落することが観測されています。完全なデータ転送を確実に行うには、データサイズを 4 バイトおよび 8 バイトに揃える必要があります。そうでない場合、フラッシュ / マーカートリガー時またはパケット完了時に、最後の 6 バイトのデータが失われる可能性があります。

データフロー: EDMA -> スニファー -> FIFO -> アグリゲータ -> STM -> TPIU -> AURORA TX。

MSS\_TPCC を使用して MDO\_DSS\_FIFO に 6 バイトのデータ転送を行うと、6 バイトが欠落します。STM モジュールには、WSTRB に基づいてデータをサンプリングする `cxstm500_axislvif_write` ブロックがあります。STM モジュールには、6 バイトの受信データを処理できるケースはありません。

**STM** モジュールには、6 バイトのデータを処理するための設計上の制限があります。

1、2、4、8 バイトのデータが処理されます。しかし、6 バイトの場合、データはドロップされます。

**回避方法:** WSTRB が 8 バイトを処理できるように、転送中に 2 つのダミー バイトを含めることをお勧めします。

## MSS 第 58 章

### ePWM: チョッパ動作モード中のグリッチ

#### 影響を受けるリビジョン

、AWRL6432、、、、AWR2544

#### 詳細

チョッパ動作モード中、ePWM モジュールからの ePWMA および ePWMB 出力信号にグリッチが見られることがあります。

#### 回避方法

グリッチの影響を受ける使用事例では、LPRADAR:APP\_PWM:PCCTL:CHPEN レジスタ ビットを 0 に設定して、PWM チョッパ制御機能を無効にすることを推奨します。

次の表は、上記の回避方法のレジスタ アドレスを示しています。

| ビット | 名称                            | アドレス        |

|-----|-------------------------------|-------------|

| 0   | LPRADAR:APP_PWM:PCCTL:CHPEN、、 | 0X57F7 FC3C |

**MSS 第 59 章**

**CRC:CAN** モジュールでは **CRC 8 ビット データ幅** と **CRC8-SAE-J1850** および **CRC8-H2F** がサポートされない

**影響を受けるリビジョン**

AWR2544

**詳細**

1. 8 ビット データ幅はサポートされていません。サポートされている最小データ幅は 16 ビットです。

2. CRC タイプ CRC8-SAE-J1850 および CRC8-H2F はサポートされていません。

**回避方法**

1. 16/32/64 ビットのデータ幅がサポートされています。

2. 上記のようなサポートされていない多項式は使用しないことをお勧めします。

## MSS 第 60 章

## PCR の 6 つの内部レジスタの読み出しおよび書き込みアドレスの不一致

### 影響を受けるリビジョン

AWR2544

### 詳細

以下は、デバイス内のすべての PCR の共通レジスタと、それに対応する読み出しアドレス オフセットおよび書き込みアドレス オフセットのセットです。

| 登録         | 書き込みアドレス オフセット | 読み取りアドレス オフセット |

|------------|----------------|----------------|

| PPROTSET_2 | 0x0000 0028    | 0x0000 002C    |

| PPROTSET_3 | 0x0000 002C    | 0x0000 0040    |

| PPROTCLR0  | 0x0000 0040    | 0x0000 0044    |

| PPROTCLR1  | 0x0000 0044    | 0x0000 0048    |

| PPROTCLR2  | 0x0000 0048    | 0x0000 004C    |

| PPROTCLR3  | 0x0000 004C    | 0x0000 00260   |

### 回避方法

上記のマッピングは、これらの特定のレジスタセットに対するリード・モディファイ・ライトまたはリードバック チェックを実行する際に使用されます。

**MSS 第 61 章**

構成された MPU 領域の最後の 24 バイトにアクセスし、キャッシングが有効になっているときに、データの停止が発生します。

**影響を受けるリビジョン**

AWR2544

**詳細**

R5F がキャッシング可能領域内のバイトまたはワードにアクセスする場合、キャッシングからのアクセスは 32 バイト長 (1 キャッシュ ライン サイズ) となり、開始アドレスはフェッチされる重要なワードになります。

MPU は、進行中のトランザクションの終了アドレスがクリティカルワード + 32 バイトであると (誤つて) 想定し、これを MPU にプログラムされた終了アドレスと比較します。MPU はこれをアクセス違反として扱い、トランザクションをフォールトします (例: 0x701FFFF8 + 32 バイト = 0x7020 0018 > 0x70FF FFFF)。

MPU 領域がキャッシング不可としてマークされている場合、この問題は発生しません。

**回避方法**

キャッシングが有効になっている場合、MPU 領域の最後の 32 バイトにはデータがありません。

## MSS 第 62 章 FFT3X パラメータセットの双方向使用での、HWA の停止

### 影響を受けるリビジョン AWR2544

#### 詳細

FFT3X が双方向パラメータセットで有効になっている場合、またはループの最初と最後のパラメータセットとして有効になっている場合、最初の FFT3X パラメータセットが実行された後、パラメータ完了割り込みが発生せずに HWA ステートマシンが停止します。

#### 回避方法

FFT3X が有効なパラメータセットを使用する前に、FFT3X が無効なパラメータセットを使用してください (ACCEL\_MODE = 0b111 で No Operation パラメータセットを選択することもできます)。

**MSS 第 63 章****ブロックコヒーレンス操作中に L2 キャッシュが破損する可能性がある問題****影響を受けるリビジョン:**

AWR2544

**説明:**

ブロックコヒーレンス操作中に L2 キャッシュが破損する可能性があることが判明しました。特定の状況下では、L1D または L2 ブロックコヒーレンス操作によって L2 キャッシュが破損する可能性があります。この問題は、同じ L2 キャッシュセット内で以下の 4 つのアクションが連続して発生した場合に発生します。

1. L1D 書き込みミス

2. ブロックコヒーレンス操作による被害者ライトバック

3. 特定のアドレスへの書き込み割り当て

4. 特定のアドレスへの読み取りまたは書き込み割り当て

この問題は、以下にリストされているすべてのブロックコヒーレンス操作に当てはまります。

- L1D ライトバック

- L1D 無効

- 無効化を伴う L1D ライトバック

- L2 ライトバック

- L2 無効

- 無効化を伴う L2 ライトバック

**回避方法:**

この回避策では、ブロックコヒーレンス操作中はメモリシステムがアイドル状態である必要があります。したがって、プログラムは、ブロックコヒーレンス操作が完了するまで待機してから続行する必要があります。これは、L1D および L2 メモリブロックのコヒーレンス動作に適用されます。ブロックコヒーレンス操作を発行するには、以下の手順に従ってください。

1. 割り込みを無効にします。

2. 対応する BAR レジスタに開始アドレスを書き込みます。

3. 対応する WC レジスタにワードカウントを書き込みます。

4. 以下のいずれかの方法で完了を待機します。

- a. MFENCE instruction を発行します (推奨)。

- b. ワードカウントフィールドが 0 になるまで WC レジスタをポーリングします。

5. 16 回の NOP を実行します。

6. 割り込みを復元します。

キャッシュコントロール レジスタ (BAR および WC) の詳細については、TMS320C66x DSP CorePac ユーザーガイド (SPRUGW0) を参照してください。MFENCE instruction は C66x DSP の新機能です。この新機能は、未処理のメモリ操作がすべて完了するまで DSP を停止させます。MFENCE 命令の詳細については、「C66x DSP および命令セットリファレンスガイド」(SPRUGH7) を参照してください。

## MSS 第 64 章

### ブロックおよびグローバルコヒーレンス操作中の L2 キャッシュ破損の問題

#### 影響を受けるリビジョン:

AWR2544

#### 説明:

特定の状況下では、L1D または L2 のブロックおよびグローバルコヒーレンス操作によって L2 キャッシュの破損が発生する可能性があります。この問題は、同じ L2 セット内で以下の 4 つのアクションが連続して発生した場合に発生します。

1. L1D 書き込みミス

2. ブロックおよびグローバルコヒーレンス操作による無効化または無効化付きライトバック

3. 特定のアドレスへの書き込み割り当て

4. 特定のアドレスへの読み取りまたは書き込み割り当て

この問題は、以下の操作を除くすべてのブロックおよびグローバルコヒーレンス操作に当てはまります。

- L1D ブロック ライトバック

- L1D グローバル ライトバック

- L2 ブロック ライトバック

- L2 グローバル ライトバック

以下も参照してください。[アドバイザリ 63 - ブロックコヒーレンス操作中に発生する可能性のある L2 キャッシュ破損の問題](#)

#### 回避方法:

##### 一般的な回避策:

以下の回避策は非常に一般的なため、パフォーマンスに影響する可能性があります。アプリケーションを理解し、どの回避策がより適しているかを判断する必要があります。

##### 回避方法 1:

この回避策では、ブロックコヒーレンス操作およびグローバルコヒーレンス操作の実行中、メモリシステムがアイドル状態である必要があります。したがって、プログラムはブロックコヒーレンス操作およびグローバルコヒーレンス操作が完了するまで待機し、処理を続行する必要があります。これは、L1D および L2 メモリのブロックコヒーレンス操作およびグローバルコヒーレンス操作に適用されます。

ブロックコヒーレンス操作を実行するには、以下の手順に従ってください。

1. 割り込みを無効にします。

2. 対応する BAR レジスタに開始アドレスを書き込みます。

3. 対応する WC レジスタにワードカウントを書き込みます

4. 以下のいずれかの方法で完了を待機します。

- a. MFENCE 命令を発行する (推奨)

- b. ワードカウントフィールドが 0 になるまで WC レジスタをポーリングします

5. 16 回の NOP を実行します

6. 割り込みを復元します

グローバルコヒーレンス操作を発行するには、以下の手順に従います。

1. 割り込みを無効にします。

2. 対応するグローバルコヒーレンスレジスタ (L1DINV, L1DWBINV, L2DINV, L2DWBINV) に 1 を書き込みます。

3. 以下のいずれかの方法で完了を待機します

- a. MFENCE 命令を発行する (推奨)

## MSS 第 64 章 (続き) ブロックおよびグローバルコヒーレンス操作中の L2 キャッシュ破損の問題

- b. 対応するグローバルコヒーレンスレジスタ (L1DINV, L1DWBINV, L2DINV, L2DWBINV) をポーリングし、ビット [0] フィールドが 0 になるまで待ちます。

4. 16 回の NOP を実行します

5. 割り込みを復元します

### 回避方法 2:

この回避方法も一般的ですが、CPU トライックをキャッシュコーヒーレンス操作と並列して実行できるようになります。ブロックコヒーレンス操作を実行するには、以下の手順に従ってください。

1. MFENCE コマンドを発行します。

2. L1D キャッシュをフリーズします。

3. L1D WBINV を開始します。

4. CPU トライックを再開します (CPU 操作は WBINV と並列で行われるため、キャッシュコヒーレンス操作の完了を待つ必要はありません)。

5. ワードカウントフィールドが 0 になるまで WC レジスタをポーリングします。

6. ワードカウントフィールドが 0 になると WBINV が完了します。

7. MFENCE コマンドを発行します。

8. L1D キャッシュをフリーズ解除します。

キャッシュ制御レジスタ (BAR, WC, L1DINV, L1DWBINV, L2DINV, および L2DWBINV) の詳細については、TMS320C66x DSP CorePac ユーザーガイド ([SPRUGW0](#)) を参照してください。MFENCE instruction は C66x DSP の新機能です。この新機能は、未処理のメモリ操作がすべて完了するまで DSP を停止させます。MFENCE 命令の詳細については、「C66x DSP および命令セットリファレンスガイド」 ([SPRUGH7](#)) を参照してください。

**MSS 第 65 章****シングル MFENCE の問題****影響を受けるリビジョン:**

AWR2544

**説明:**

MFENCE 命令は、CPU がトリガーするすべてのメモリトランザクションが完了するまで、命令フェッチパイプラインを停止するために使用されます。

非常に特殊な状況下では、MFENCE 命令により、先行する STORE 命令が完了する前に、MFENCE 命令後のトランザクションを続行できる場合があります。

たとえば、

1. ストア A における

2. MFENCE との関係

3. トランザクション B

MFENCE 実装は、メモリシステムが「実行中の」トランザクションがない、つまりアイドル状態であるとアサートするまで CPU をストールします。これにより、ストア A が完了する前に CPU がトランザクション B に進むことを防ぎます。ストア A が L1D から L2 に移動すると、メモリシステムがアイドル状態であると早期にアサートする小さなウインドウが存在します。このウインドウは、通常はアイドル状態です。トランザクション B がストア A の直後に実行する必要がある場合、プログラムが不正な動作をする可能性があります。例えば、ストア A が DDR3 に書き込み、トランザクション B が EDMA をトリガーし、その EDMA がストア A によって書き込まれた位置を読み取るとします。MFENCE は、EDMA が実行される前にストア A がコミットすることを保証し、EDMA が更新された値を認識するようにします。このアドバイザリの問題により、トランザクション B がストア A にコミットする前に EDMA をトリガーし、EDMA が古いデータを認識する可能性があります。

**回避方法:**

シングル FENCE を 2 つの MFENCE に連続して置き換えます。これにより、ストア A が L1D から L2 に渡されたときにメモリシステムがアイドル状態であると早めに示した場合に、ストールを再開することで問題が解決されます。

1. ストア A における

2. MFENCE との関係

3. MFENCE との関係

4. トランザクション B

コヒーレンス操作に関する注意:以下のアドバイザリについては、既に記載されている回避策に加えて、二重 MFENCE も回避策として使用できます。

- [アドバイザリ 63 - ブロックコヒーレンス操作中に L2 キャッシュが破損する可能性がある問題](#)

- [アドバイザリ 64 - ブロックおよびグローバルコヒーレンス操作中に L2 キャッシュが破損する問題](#)

上記の 2 番目のアドバイザリは、L1D および L2 ブロックとグローバルのライトバックには適用されないことに注意してください。L1D および L2 ブロックとグローバルのライトバックの後に MFENCE が実行され、ライトバックの完了に依存するトランザクションが発生する場合は、二重 MFENCE の回避策を使用する必要があります。

また、MCSDK ソフトウェアパッケージの現在のリリースには、この回避策は含まれていません。将来的なリリースに含まれる予定です。

## MSS 第 65 章 (続き) シングル MFENCE の問題

---

### 注

トレースに関する特別な検討事項。MFENCE を使用するソフトウェアでトレース生成が想定される場合、回避策には追加の要件があります。MFENCE のトレース生成には、MFENCE 命令の後に必ず NOP 命令と MARK 命令を実行する必要があります。回避策については、このホワイトペーパーで説明しています。

---

## MSS 第 68 章

**HWA の Real2X FFT モードでは、0 番目の BCNT の FFT データが破損する可能性があります。**

### 影響を受けるリビジョン:

AWR2544

#### 説明:

FFT パラメータ セットで Real2X FFT モードが有効になっており、ダイナミック クロック ゲーティングが無効になっている他のパラメータ セットと組み合わせて FFT パラメータ セットを使用すると、0 番目の BCNT に不良データが生成される可能性があります。

#### 回避方法:

データ破損の可能性を減らすために、HWA MMR 空間でダイナミック クロック ゲーティングを有効にするか、Real2X モードを無効にして Real1X モードで実行してください。

**MSS 第 71 章****シングルビット ECC (エラー訂正) メカニズムにより、メモリの誤った更新が発生する可能性****影響を受けるリビジョン:**

,,, AWR2544,

**説明:****注**

この問題は、シミュレーションの誤ったメモリアクセスシーケンスのデバッグ中に発見されました。現在までに、フィールドと導入シナリオにおいて同様の問題が報告されたことはありません。

SoC 内の表形式以下のメモリ範囲で、特定のメモリアクセスシーケンスの組み合わせの下で、シングルビットアップセットイベントが発生することは珍しく、シングルビット誤り訂正メカニズムによってメモリ更新が誤ったものになる可能性があります。

AWR294x の RAM メモリは、シングルビット誤り訂正、ダブルビットエラー検出 (SECDED) メカニズムによって ECC 保護されています。特定のイベントシーケンスが発生した場合、シングルビット誤り訂正メカニズムによってメモリ更新が不正に発生することがあります。

この問題がアプリケーションに影響を与えるには、以下のすべての条件を満たす必要があります。

- 環境条件やその他の要因によるランダムなハードウェア故障によってシングルビットアップセットイベントが発生、および

- シングルビットアップセットイベントが影響を受けるメモリ範囲への影響、および

- シングルビットエラーのあるメモリ位置への読み取り、または部分書き込みアクセスが発生 (シングルビット誤り訂正メカニズムが作動する)、および

- シングルビット誤り訂正の発生後に特定のメモリアクセスシーケンスの組み合わせが発生、および

- 誤り訂正メカニズムによるメモリの誤更新が、アプリケーションプログラムフローに影響を与えるほど重大であり、他の安全メカニズムでは検出されない場合です。

シングルビット誤り訂正の発生後、影響を受けるメモリ範囲への以下のアクセスの組み合わせ (上記の条件 3 および 4) が問題を引き起こす可能性があります。

- 読み取り / 部分書き込みアクセス (SEC のある位置 A から / へ) から (その後) 完全書き込み (同じメモリ範囲内の 1 つ以上のメモリ位置へ)、(その後) 部分書き込み (同じメモリ範囲内の任意の位置へ) へと最後の完全書き込み位置への誤更新につながります。

- 部分的な書き込みアクセス (SEC を使用した A 番地へ) から (その後に続く) 部分的な書き込み (同じメモリ範囲内の他の番地へ)、A 番地への誤更新につながります。

**注**

この問題は、他のすべてのメモリアクセスシーケンスの組み合わせでは発生しません。

**回避方法:**

シングルビットアップセットイベントはまれであり、発生確率も低いです。

- このシナリオはシングルビットエラーのみにつながる必要があります。ダブルビットエラーが検出され発生した場合は、その重大度に応じてデバイスがセーフ状態に移行します。

部分的な書き込みメモリアクセス (問題の原因となるために必要なアクセス) は、以下の理由で制限されます。

- キャッシュされたメモリ範囲は、キャッシュラインへの書き込みが常に完全書き込みであるため、部分的な書き込みアクセスにはつながりません。

## MSS 第 71 章 (続き) シングルビット ECC (エラー訂正) メカニズムにより、メモリの誤った更新が発生する可能性

- 例:MSS L2 メモリ

- コードセクションは読み取り専用です (したがって、コードセクション全体へのアクセスは、問題を引き起こす条件を満たしません)。

- 例:MSS L2 メモリ

- 部分的な書き込みアクセスによって影響を受けたメモリには、このようなランダムエラーを検出または回避できる他の安全メカニズムが備わっている場合があります。

- レーダー データキューブの高レベル処理アルゴリズムには、追跡機能 (時間的および論理的モニタリング) による異常値除去機能が組み込まれています。

- 例:DSS L3

- メールボックスなどの影響メモリでは、エラーを検出するために情報冗長化技術が使用される場合があります。

- 例:メールボックスのメモリ

影響を受けるメモリ範囲において、部分的なメモリ書き込みアクセスの可能性がないか確認してください。特定された部分的な書き込みが発生するメモリ範囲に対して、対策を講じる必要性の重要度を判断します。以下に、考えられる対応策を示します。

- 動作環境においてシングルビットアップセットイベントが発生する可能性が低い場合。

- このようなスプリアス ランダムエラーを検出または回避できる他の安全機構がある場合。

- 動作:以下のオプションのうち 1 つ以上を検討してください。

- これらのメモリ範囲への部分的な書き込みアクセスパターンを回避する。

- シングルビットメモリ訂正イベントが発生した場合、影響を受けるメモリバンクを再初期化する。

- シングルビットメモリ訂正イベントを訂正不能エラーとして扱い、安全状態に移行する。

- これは機能安全の検出可能性に関する主張には影響せず、シングルビット反転が発生した場合の可用性に影響する可能性があります。

対策 (2-b-ii) を講じる必要がある場合は、メモリ範囲とそれに対応する ESM ラインおよび ECC アグリゲータビットについては、以下の表を参照してください。

この表には、影響を受けるメモリリストと、それに対応する詳細情報のみが記載されています。

| メモリ名         | 開始アドレス     | 終了アドレス     | ESM ライン                  | ECC アグリゲータステータスピット                                |

|--------------|------------|------------|--------------------------|---------------------------------------------------|

| DSS L3 Bank0 | 0x88000000 | 0x880BFFFF | DSS_ESM: グループ 1 のライン 92  | DSS_ECC_AGG::SEC_STATUS_REG0::DSS_L3RAM0_PEND     |

| DSS L3 Bank1 | 0x8800C000 | 0x8817FFFF | DSS_ESM: グループ 1 のライン 92  | DSS_ECC_AGG::SEC_STATUS_REG0::DSS_L3RAM1_PEND     |

| DSS L3 Bank2 | 0x88180000 | 0x881FFFFF | DSS_ESM: グループ 1 のライン 92  | DSS_ECC_AGG::SEC_STATUS_REG0::DSS_L3RAM2_PEND     |

| DSS L3 Bank3 | 0x88200000 | 0x8827FFFF | DSS_ESM: グループ 1 のライン 92  | DSS_ECC_AGG::SEC_STATUS_REG0::DSS_L3RAM3_PEND     |

| MSS L2 Bank0 | 0xC0200000 | 0xC027FFFF | MSS_ESM:: グループ 1 のライン 18 | MSS_ECC_AGG_MSS::SEC_STATUS_REG0::MSS_L2SLV0_PEND |

**MSS 第 71 章 (続き) シングルビット ECC (エラー訂正) メカニズムにより、メモリの誤った更新が発生する可能性**

| メモリ名         | 開始アドレス     | 終了アドレス     | ESM ライン                  | ECC アグリゲータステータスピット                                |

|--------------|------------|------------|--------------------------|---------------------------------------------------|

| MSS L2 Bank1 | 0xC0280000 | 0xC02FFFF  | MSS_ESM:: グループ 1 のライン 18 | MSS_ECC_AGG_MSS::SEC_STATUS_REG0::MSS_L2SLV1_PEND |

| MSS メールボックス  | 0xC5000000 | 0xC5001FFF | MSS_ESM:: グループ 1 のライン 18 | MSS_ECC_AGG_MSS::SEC_STATUS_REG0::MSS_MBOX_PEND   |

| MSS_RETRAM   | 0xC5010000 | 0xC50107FF | MSS_ESM:: グループ 1 のライン 18 | MSS_ECC_AGG_MSS::SEC_STATUS_REG0::MSS_RETRAM_PEND |

| DSS メールボックス  | 0x83100000 | 0x83100FFF | DSS_ESM: グループ 1 のライン 92  | DSS_ECC_AGG::SEC_STATUS_REG0::DSS_MAILBOM_PEND    |

**注**

上記でキャプチャした MSS\_L2 アドレスは、DSS および EDMA アドレスビューから取得されています。MSS-R5 から取得した MSS\_L2\_BANK0 および MSS\_L2\_BAK1 アドレスビューは、それぞれ 0x10200000 ~ 0x1027FFFF、および 0x10280000 ~ 0x102EFFFF です。

アプリケーションでは使用されないが BSS で使用される他のメモリ (BSS\_Mailbox や BSS\_Static\_RAM など) も、このエラッタの影響を受けます。

- BSS メールボックスは、主に mmWaveLink を使用して BSS と MSS / DSS 間の通信に使用され、データ整合性のために CRC を組み込んだメッセージプロトコルに従います。BSS メールボックスを介したメッセージ交換中に CRC を使用すると、このメモリに関するリスクが軽減されます。

- 故障が発生すると (この場合は ECC SEC)、BSS は ESM 故障非同期イベントメッセージを MSS / DSS に通知として送信します。アプリケーションは、BSS の AWR\_AE\_RF\_ADV\_ESMFAULT\_STATUS\_SB 非同期イベントから b20:ECC\_AGG\_SEC\_ERROR を読み取る必要があります。このシングルビットメモリ訂正イベントを訂正不可能なエラーとして扱い、安全な状態に移行してください。

- この回避策は、アプリケーションが DFP バージョン 2.4.14 以前の BSS パッチを使用している場合にのみ有効です。

## ANA 第 12A 章 レシーバに存在する第 2 高調波 (HD2)

影響を受けるリビジョン: AWR2544

**説明:** RF ピン / パッケージと FMCW シンセサイザーの間には有限の絶縁耐圧があります。これにより、シンセサイザー出力にスプリアストーンが発生し、RX ADC 出力に 2 次高調波や予想される IF 周波数の相互変調が発生する可能性があります。2 次高調波の振幅は、LNA 入力における意図したトーンの電力レベルを基準として、最大 -55 dBc ~ に達する可能性があります。

**回避方法:** 現時点では回避策はありません。ただし、多くの一般的なレーダー使用例では、以下の 2 つの理由により、HD2 がシステム性能に影響を与えることはありません。

1. HD2 は LO 信号への結合によって発生するため、セルフミキシング効果 (つまり、ミキサーにおける位相ノイズと位相スプリアスの抑制効果) により、HD2 レベルは本質的に抑制されます。

2. 実際のシナリオでは、ターゲットから反射されたレーダー信号が二重反射する現象がしばしば発生し、実際の物体の 2 倍の距離にゴースト物体が現れます。この影響は、HD2 自体の影響と区別がつかないことがよくあります。

**ANA 第 37A 章 LO 周波数全体での RX ゲインの大幅きく低下****影響を受けるリビジョン** AWR2544**詳細**

RX ゲインの低下は、デバイスの動作周波数範囲全体にわたって約 4.5dB です。。

**回避方法**

ゲインの低下によるノイズ指数への影響はわずかであるため、システム性能への影響はごくわずかです。

## ANA 第 39 章

**HPF カットオフ周波数を 2800kHz に設定すると、RX IFA ゲインとフィルターコーナー周波数が不正確になる可能性があります。**

### 影響を受けるリビジョン

AWR2544

#### 詳細

アナログ IF 段には、以下の -6dB コーナー周波数に設定可能な 2 次ハイパスフィルタが含まれています。

フィルタは、300、350、700、1400、2800 kHz です。

これらのうち、HPF のカットオフ周波数を 2800kHz に設定すると、RX IFA ゲインとフィルタのコーナー周波数が不正確になる可能性があります。

#### 回避方法

2800kHz カットオフ設定の使用は推奨されません。

**ANA 第 43 章** シンセサイザ周波数ライブモニターに表示されるエラー**影響を受けるリビジョン:** AWR2544**説明:** 80.5 GHz ~ 81 GHz のランプ波構成で、スロープが 50 MHz/us を超える場合、100°C を超えるとシンセサイザ周波数ライブモニターで 20 MHz を超える大きな誤差が発生します。**回避方法:** スロープが 50 MHz/us を超える場合は、80.5 GHz 未満のチャープを使用することをお勧めします。

## ANA 第 44 章

3.3V IO モードでは、3.3V レールから 1.8V レールに逆電力が供給されます。

### 影響を受けるリビジョン:

AWR2544

#### 説明:

3.3V 電源レールが立ち上がり 1.8V がまだ供給されていない場合、IO セル内のリーケージ パスにより 1.8V VIOIN レールで電圧上昇が見られます。

#### 回避方法:

以下の回避策を推奨します。

1. 適切な電源シーケンスを使用してください。最初に 1.8V を供給し、次に 3.3V を供給します。

2. PMIC が出力に既存の電圧を検知したために起動に失敗した場合は、PMIC のこの電圧検出方式を無効にする必要があります。

**ANA 第 45 章**

デジタル動作によるスプリアスが発生しました。

**影響を受けるリビジョン:**

AWR2544

**説明:**

デジタル フィルタリング動作はアナログ回路と結合して LO にスプリアスを発生させる可能性があり、Rx データにも現れる可能性があります。このような Rx データにおけるスプリアスは、強い物体の周囲のスプリアス周波数オフセットで観測されます。

観測される可能性のあるさまざまなスプリアスを以下に示します。

1. 20 Msps 付近のサンプリングレート  $\pm 0.5$  Msps における、IF 周波数 (2Fs-40) MHz でのスプリアス。

2. 30 Msps 付近のサンプリング レート  $\pm 0.5$  Msps における、IF 周波数 (2Fs-60) MHz でのスプリアス。

3. 35 Msps 付近のサンプリング レート  $\pm 0.3$  Msps における、IF 周波数 (4Fs-140) MHz でのスプリアス。

4. 22 ~ 23.5 Msps および 26.5 ~ 28 Msps の範囲のサンプリング レートにおける、IF 周波数 (4Fs-100) MHz でのスプリアス。

(Fs = プロファイル サンプリング レート)

**回避方法:**

上記の範囲内のサンプリング レートを避けるか、サンプリング レート範囲のちょうど中央 (スプリアスが 0 Hz となるように) を使用する必要があります。

**ANA 第 47 章****アイドル チャネル シナリオで RX 全体で観測された RX スプリアス****影響を受けるリビジョン:**

AWR2544

**説明:**

物体が存在しない場合や、付近に非常に弱い物体が存在する場合、シグマデルタ ADC 出力で RX スペクトルにスプリアスが発生する可能性があります。これは、低 RX ゲイン設定の場合のみに観測されます。スプリアス周波数は RX チャネルによって異なる可能性があります。実際の物体が存在する場合、これは観測されません。

**回避方法:**

- **回避策 1:** このような状況では、より高い Rx ゲイン ( $>40\text{dB}$ ) を使用します。

- **回避策 2:** アイドル チャネル スプリアスは、スプリアス範囲ビンで 2DFFT のすべてのドップラービンに分散されます。2D-FFT でピークを検出する際に、2D 近傍ピーク探索 (例: 2D CFAR-CA) を適用できます。これは、レベルを周囲の全ビンと比較するものです。これにより、アイドル チャネル スプリアスがゴースト オブジェクトとして検出されるのを防ぐことができます。

**ANA 第 59 章****OSC\_CLK\_OUT\_ETH 動作にリスプリアスが発生します****影響を受けるリビジョン:**

AWR2544、

**説明:**

XTAL/2 周波数オプションで OSC\_CLK\_OUT\_ETH を有効にすると、イーサネットクロック信号と LO 信号の結合により、XTAL/2 IF オフセットで弱いスプリアスが発生する可能性があります。強力な実ターゲットが存在する場合、 $IF = (XTAL/2 - \text{実ターゲット IF 周波数})$  で RX データに潜在的なゴーストターゲットが存在する可能性があります。

**回避方法:**

以下の回避策を 1 つ以上検討してください。

1. OSC\_CLK\_OUT\_ETH = XTAL/2 オプションの使用を避け、代わりに XTAL/1 オプションを使用してください。必要な  $1/2$  分周は、AWR2544 チップの外部 (例えば、イーサネット PHY チップ内) で実装してください (そのオプションが利用可能な場合)。

2. 強力な実ターゲットが存在する場合、帯域内ゴーストターゲットを回避するために、IF BW  $< XTAL/4$  を使用してください。

3. IF BW  $> XTAL/4$  を使用する場合、強力な実ターゲットを検出した後、IF オフセット (XTAL/2 - 実ターゲット IF 周波数) でより厳しい検出スレッショルドを使用して、OSC\_CLK\_OUT\_ETH によって誘発されるゴーストターゲットの検出を回避します。

4. スプリアスレベルを下げるには、OSC\_CLK\_OUT\_ETH の駆動強度を下げます。駆動強度を 0.5 倍にすると、スプリアスレベルが 3dB 低下することが予想されます。

5. OSC\_CLK\_OUT\_ETH の代わりに OSC\_CLK\_OUT を使用してください。

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 6 改訂履歴

### Changes from DECEMBER 24, 2024 to OCTOBER 1, 2025 (from Revision \* (December 2024) to Revision A (October 2025))

|                                                                                                        | Page |

|--------------------------------------------------------------------------------------------------------|------|

| • シリコンバリアント/リビジョンマップのアドバイザリ:「メインサブシステム」に MSS 第 68 章および MSS 第 71 章のアドバイザリの追加.....                       | 4    |

| • シリコンバリアント/リビジョンマップのアドバイザリ:ANA 第 46 章を削除.....                                                         | 4    |

| • CRC: CRC 8 ビットデータ幅、および CAN モジュールで使用可能な CRC8-SAE-J1850 および CRC8-H2F はサポートされていません。詳細と回避策を書き換えました。..... | 20   |

| • MSS 第 68 章:HWA の実数 2X FFT モードにおける 0 番目の BCNT の FFT データが破損する可能性があります。.....                            | 29   |

| • MSS 第 71 章:シングルビット ECC (誤り訂正) メカニズムにより、メモリの誤更新が発生する可能性があります。....                                     | 30   |

| • ANA 第 59 章:影響のあるデバイスを AWR2544 に更新しました。整合性のため ANA 第 48 章を ANA 第 59 章に変更しました。.....                     | 40   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月