# TM4C1294 interface to ADS7142 software library

Peggy Liska and William Santos

Precision Analog-to-Digital Converters

### ABSTRACT

This application report describes how to communicate with the ADS7142 using the TM4C1294NCPDT as the host device. The communication is performed via inter-integrated circuit (I2C) protocol and the ADS7142 is enabled to operate in each of its functional modes. The accompanying software contains a function library allowing quick prototyping of ADS7142 setup and control. This framework is designed with the intention of minimal function modification required to operate the ADS7142 as a sensor monitor. The functional modes of the ADS7142 include manual mode, autonomous mode, and high precision mode. Additional features of the ADS7142 include sampling speed control, oscillator selection, and selection of input channel type (single-ended or pseudo-differential).

### Contents

| 1 | Introduction                | . 3 |

|---|-----------------------------|-----|

| 2 | Hardware                    | . 3 |

| 3 | Software                    | . 5 |

| 4 | Using the Software          | 18  |

| 5 | Main Routines and Test Data | 22  |

| 6 | References                  | 58  |

### List of Figures

| 1  | TM4C1294 Connected LaunchPad                                                   | . 3 |

|----|--------------------------------------------------------------------------------|-----|

| 2  | ADS7142 BoosterPack <sup>™</sup>                                               | . 4 |

| 3  | ADS7142 BoosterPack <sup>™</sup> Connection to TM4C1294 LaunchPad <sup>™</sup> | . 4 |

| 4  | TM4C1294NCPDT Multi-Byte Transmit Flowchart                                    | . 8 |

| 5  | Writing a Single Register in the ADS7142 Over I <sup>2</sup> C                 | . 9 |

| 6  | Setting Register Address for a Single Register Read From the ADS7142           | 11  |

| 7  | TM4C1294NCPDT Single-Byte Receive Flowchart                                    | 12  |

| 8  | ADS7142 Single Register Read                                                   | 13  |

| 9  | TM4C1294NCPDT Multi-Byte Receive Flowchart                                     | 15  |

| 10 | Reading ADS7142 Conversion Data in Manual Mode                                 | 16  |

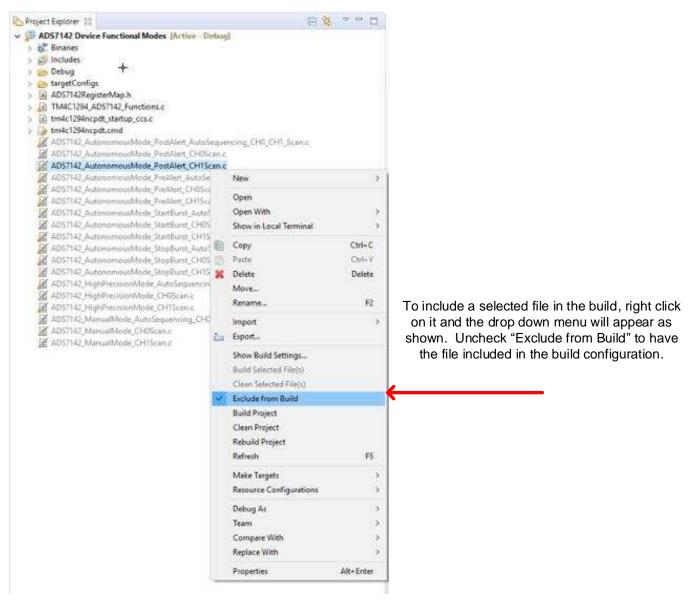

| 11 | Project Explorer                                                               | 20  |

| 12 | Including a File in the Project Build                                          | 21  |

| 13 | Excluding a File From the Project Build                                        | 22  |

| 14 | Manual Mode Dual Channel Sampling Test Data                                    | 25  |

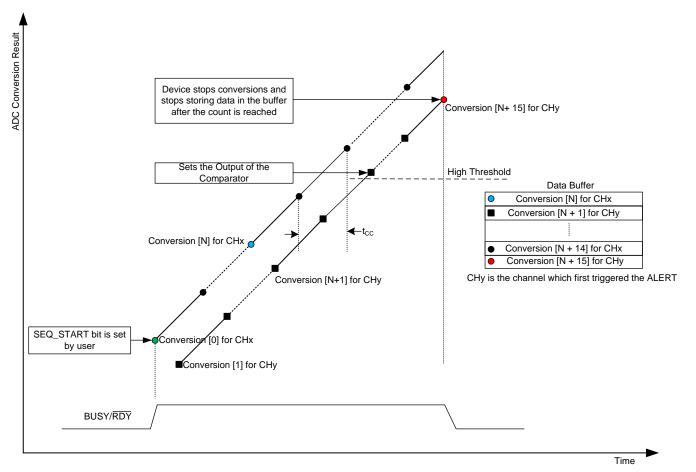

| 15 | Pre Alert Data for Dual-Channel Configuration                                  | 26  |

| 16 | Autonomous Mode Pre-Alert Dual Channel Sampling Test Data 1                    | 29  |

| 17 | Autonomous Mode Pre-Alert Dual Channel Sampling Test Data 2                    | 30  |

| 18 | Autonomous Mode Pre-Alert Dual Channel Sampling Test Data 3                    | 31  |

| 19 | Autonomous Mode Pre-Alert Dual Channel Sampling Test Data 4                    | 32  |

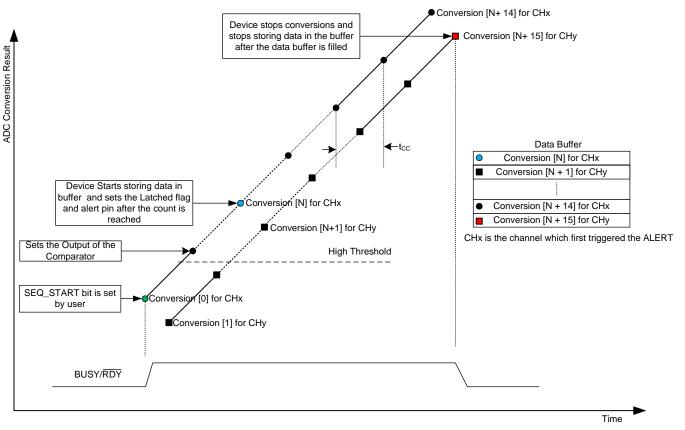

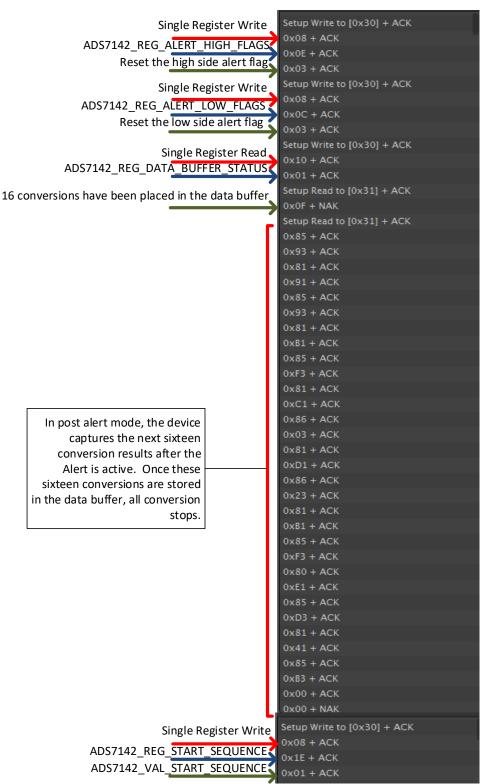

| 20 | Post Alert Data for Dual-Channel Configuration                                 | 33  |

| 21 | Autonomous Mode Post Alert Dual-Channel Sampling Test Data 1                   | 36  |

| 22 | Autonomous Mode Post Alert Dual-Channel Sampling Test Data 2                   | 37  |

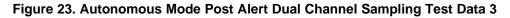

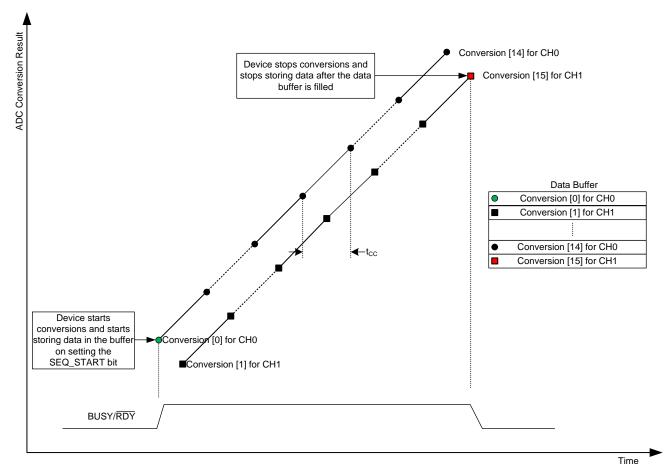

| 23 | Autonomous Mode Post Alert Dual Channel Sampling Test Data 3  | 38 |

|----|---------------------------------------------------------------|----|

| 24 | Autonomous Mode Post Alert Dual-Channel Sampling Test Data 4  |    |

| 25 | Start Burst With Dual-Channel Configuration                   | 40 |

| 26 | Autonomous Mode Start Burst Dual-Channel Sampling Test Data 1 | 43 |

| 27 | Autonomous Mode Start Burst Dual-Channel Sampling Test Data 2 | 44 |

| 28 | Autonomous Mode Start Burst Dual-Channel Sampling Test Data 3 | 45 |

| 29 | Stop Burst With Dual-Channel Configuration                    | 46 |

| 30 | Autonomous Mode Stop Burst Dual-Channel Sampling Test Data 1  | 49 |

| 31 | Autonomous Mode Stop Burst Dual-Channel Sampling Test Data 2  | 50 |

| 32 | Autonomous Mode Stop Burst Dual-Channel Sampling Test Data 3  | 51 |

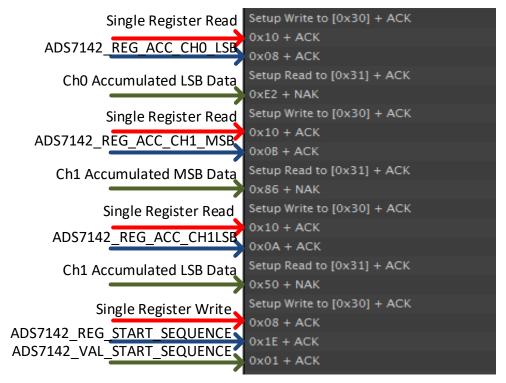

| 33 | High Precision Mode With Dual-Channel Configurations          | 52 |

| 34 | High Precision Mode Dual-Channel Sampling Test Data 1         | 55 |

| 35 | High Precision Mode Dual-Channel Sampling Test Data 2         | 56 |

| 36 | High Precision Mode Dual-Channel Sampling Test Data 3         | 57 |

| 37 | High Precision Mode Dual-Channel Sampling Test Data 4         | 58 |

|    |                                                               |    |

### List of Tables

| 1 | Hardware Definition Files                     | 5 |

|---|-----------------------------------------------|---|

| 2 | Driver Library Files                          | 5 |

| 3 | ADS7142 Device Functional Modes Main Routines | 6 |

| 4 | Functions Used in Main                        | 7 |

|   |                                               |   |

### Trademarks

2

LaunchPad, BoosterPack are trademarks of Texas Instruments. ARM, Cortex are registered trademarks of Arm Limited. All other trademarks are the property of their respective owners.

### 1 Introduction

Sensor monitoring technology is an integral piece of systems that seek to gather copious amounts of data and process that data in a meaningful way. Because of the differences in sensor monitoring techniques, the system designer must choose the best sensor monitor for a given application. In this application report the ADS7142 SAR ADC is paired with a TM4C1294NCPDT microcontroller (MCU) to provide accurate sampling data after the device is configured to operate in one of its functional modes.

### 2 Hardware

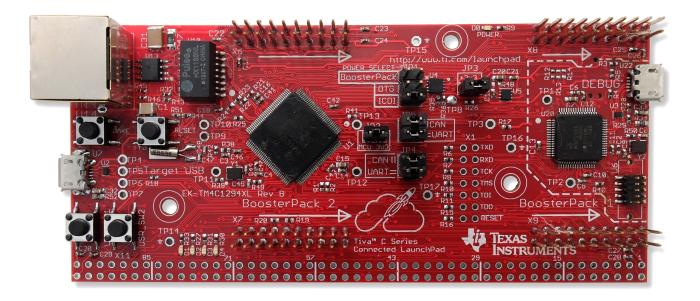

The TM4C1294NCPDT is a high performance MCU solution that combines complex integration with a suite of features. The device contains eight UART interfaces and ten I<sup>2</sup>C modules with several clocking options. The ARM® Cortex®-M4F-Based MCU TM4C1294 Connected LaunchPad<sup>™</sup> Evaluation Kit breaks out two of the MCU I<sup>2</sup>C modules for use with standardized BoosterPack boards. Figure 1 shows a TM4C1294 LaunchPad<sup>™</sup> development kit with connectors already in place.

Figure 1. TM4C1294 Connected LaunchPad

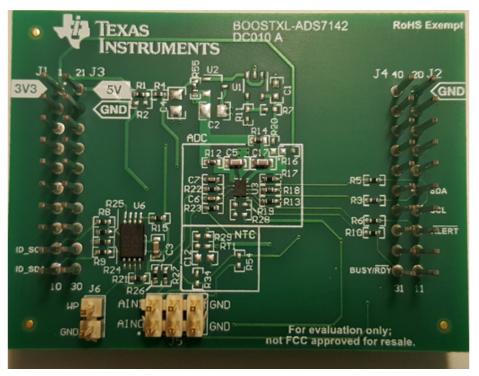

The ADS7142 nanopower, dual-channel, programmable sensor monitor BoosterPack<sup>™</sup> plug-in module (see Figure 2) hosts features specific to sensor monitoring. This module is ideally suited for a sensor node system architecture where one or two sensor outputs can be monitored as part of a central gateway, with the host MCU being the router to the cloud in an internet of things (IoT) application. The code examples provided in this application report can be used for software development on MCUs or digital processors other than the TM4C1294, allowing the designer maximum flexibility in choosing the best digital host for the application.

3

Introduction

Figure 2. ADS7142 BoosterPack™

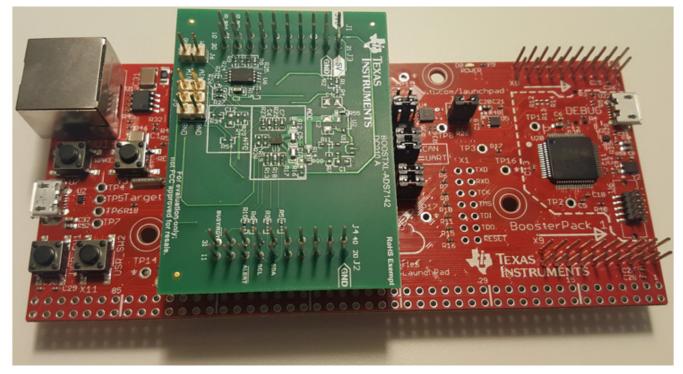

As shown in Figure 3, the ADS7142 BoosterPack<sup>™</sup> connects to the TM4C1294 connected LaunchPad<sup>™</sup>.

Figure 3. ADS7142 BoosterPack™ Connection to TM4C1294 LaunchPad™

4

### 3 Software

### 3.1 Header Files

To aid in interfacing the ADS7142 device, TI has produced a source code library that eliminates the need to write low-level interface functions that configure the core of the TM4C1294NCPDT. This library provides a boost in the development of a TM4C/ADS7142-based product, saving time and quickly progressing an applications project. This library is designed to be used with any TM4C device after appropriate software changes. An I<sup>2</sup>C master can be implemented using one of ten modules within the TM4C1294. The library provides a number of header files that define digital masks to access each piece of hardware on the device.

The library has been implemented so that digital masks are interchangeable. If a piece of hardware must be accessed, simply find the correct global variable name for that mask and place that name as an argument in the desired function calls. The software designer must then be thorough in replacing all instances of these masks to reflect the desired access to a certain piece of hardware. There are header files specific to each of the hardware components.

Table 1 describes the hardware definition header files.

| Filename             | Description                                                                                                                                                                                                                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hw_i2c.h             | This file contains macros used specifically to access the TM4C master and slave hardware, including register locations and commonly used masks for use with these registers.                                                                                                                          |

| hw_memmap.h          | This file contains definitions specific to the TM4C device. Primarily, the port and pin masks used to access all of the device peripherals. Definitions for UART0-UART7, I2C0-I2C9, TIMER, and GPIO are included among others.                                                                        |

| hw_types.h           | This file contains helper macros for determining silicon revisions for TM4C devices. These macros are used by the driver library at <i>run-time</i> to create necessary conditional blocks that allow a single version of the Driverlib binary code to support multiple (all) Tiva silicon revisions. |

| hw_ints.h            | This file contains the interrupt assignments on TIVA C series devices. Class interrupts and fault interrupts are included for user enable in firmware.                                                                                                                                                |

| hw_gpio.h            | This file contains the definitions and macros for the GPIO hardware. A set of register offset masks define the GPIO capabilities and features.                                                                                                                                                        |

| ADS7142RegisterMap.h | This file contains all of the register masks and value masks to interface and configure the ADS7142 using the host MCU. This file contains all of the command opcodes and function declarations used to develop the device functional modes main routines.                                            |

### Table 1. Hardware Definition Files

Hardware definition files are important for defining hardware attributes and mapping them to callable system variables in software. In order to enable communication with the target MCU, driver files must be implemented. Table 2 describes the driver library files to be used for communication with the TM4C1294.

### **Table 2. Driver Library Files**

| Filename  | Description                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gpio.h    | This file contains values that can be passed to application programming interfaces (APIs) that configure the GPIO modules.                                                                                                    |

| i2c.h     | This file contains important I <sup>2</sup> C Master Command masks used to perform I <sup>2</sup> C transmission and receive. It also contains macros and APIs for advanced I <sup>2</sup> C module features on the host MCU. |

| pin_map.h | This driver file contains the mapping of peripherals to pins for all the TIVA C series parts.                                                                                                                                 |

| sysctl.h  | This file contains system control directives for selection of clocks/pll and crystal frequencies as well as values to be used with control APIs. API prototypes for system control are also included in this file.            |

| i2c.c     | Driver file for the I <sup>2</sup> C block. Contains low-level functions that allow the user to configure the I <sup>2</sup> C modules on the core of the host device.                                                        |

Software

### 3.2 ADS7142 Device Functional Modes Overview

The ADS7142 contains three primary modes: manual mode, autonomous mode, and high precision mode. Each mode requires a set of register configurations before the device can operate in that mode. Table 3 describes the main code routines that place the device in each of its functional modes.

| Filename                                                       | Description                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TM4C_ADS7142_Functions.c                                       | Uses the low-level functions in i2c.c to configure th<br>host TM4C MCU and develop the ADS7142 register<br>configuration functions. The function prototypes in<br>the ADS7142RegisterMap.h file are explicitly<br>declared in this file.                              |  |  |  |  |

| ADS7142_ManualMode_CH0Scan.c                                   | These routines configure the ADS7142 into Manual                                                                                                                                                                                                                      |  |  |  |  |

| ADS7142_ManualMode_CH1Scan.c                                   | Mode (I <sup>2</sup> C command mode) in both single channel and dual-channel configuration. In manual mode, 12-                                                                                                                                                       |  |  |  |  |

| ADS7142_ManualMode_AutoSequencing_CH0_CH1_Scan.c               | bit conversions are clocked out continuously.                                                                                                                                                                                                                         |  |  |  |  |

| ADS7142_AutonomousMode_PreAlert_CH0Scan.c                      | These routines configure the ADS7142 into                                                                                                                                                                                                                             |  |  |  |  |

| ADS7142_AutonomousMode_PreAlert_CH1Scan.c                      | autonomous pre-alert mode in both single channel<br>and dual-channel configuration. In pre-alert mode,                                                                                                                                                                |  |  |  |  |

| ADS7142_AutonomousMode_AutoSequencing_PreAlert_CH0_CH1Scan.c   | the ADS7142 stores the sixteen conversions prior to<br>the activation of the alert in a data buffer.                                                                                                                                                                  |  |  |  |  |

| ADS7142_AutonomousMode_PostAlert_CH0Scan.c                     | These routines configure the ADS7142 into                                                                                                                                                                                                                             |  |  |  |  |

| ADS7142_AutonomousMode_PostAlert_CH1Scan.c                     | autonomous post-alert mode in both single-channel<br>and dual-channel configuration. In post-alert mode,                                                                                                                                                              |  |  |  |  |

| ADS7142_AutonomousMode_AutoSequencing_PostAlert_CH0_CH1Scan.c  | the ADS7142 stores the next 16 conversions after<br>the alert is active.                                                                                                                                                                                              |  |  |  |  |

| ADS7142_AutonomousMode_StartBurst_CH0Scan.c                    | These routines configure the ADS7142 into                                                                                                                                                                                                                             |  |  |  |  |

| ADS7142_AutonomousMode_StartBurst_CH1Scan.c                    | <ul> <li>autonomous start burst mode in both single channel<br/>and dual-channel configuration. In start burst mode<br/>the device starts filling the data buffer upon starting<br/>channel sequencing: conversions stop once the da<br/>buffer is filled.</li> </ul> |  |  |  |  |

| ADS7142_AutonomousMode_AutoSequencing_StartBurst_CH0_CH1Scan.c |                                                                                                                                                                                                                                                                       |  |  |  |  |

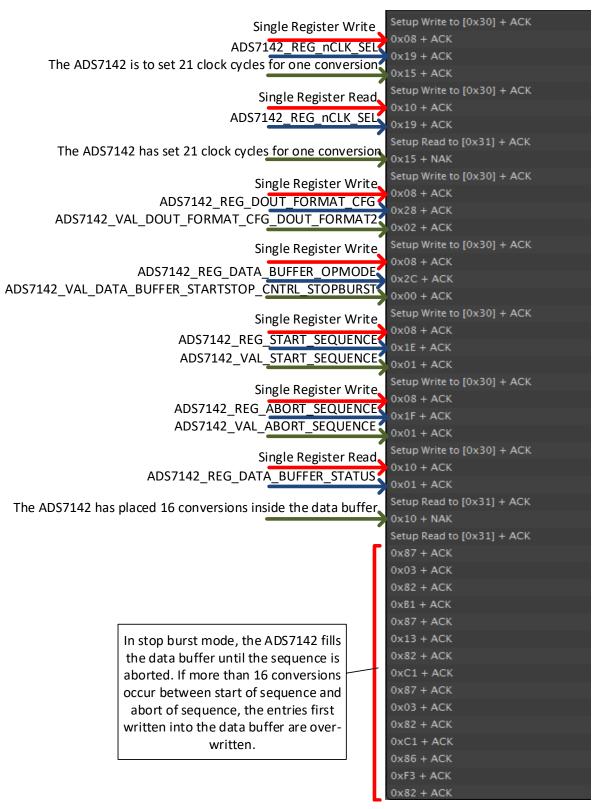

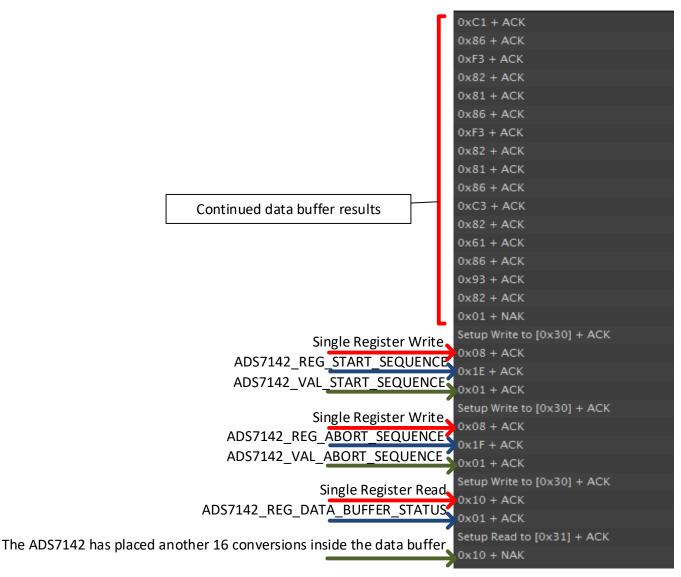

| ADS7142_AutonomousMode_StopBurst_CH0Scan.c                     | These routines configure the ADS7142 into                                                                                                                                                                                                                             |  |  |  |  |

| ADS7142_AutonomousMode_StopBurst_CH1Scan.c                     | autonomous stop burst mode in both single-channel<br>and dual-channel configuration. In stop burst mode,                                                                                                                                                              |  |  |  |  |

| ADS7142_AutonomousMode_AutoSequencing_StopBurst_CH0_CH1Scan.c  | the device continues to fill the data buffer until the<br>channel sequencing is aborted. Data buffer entries<br>are continually overwritten until the sequence is<br>aborted.                                                                                         |  |  |  |  |

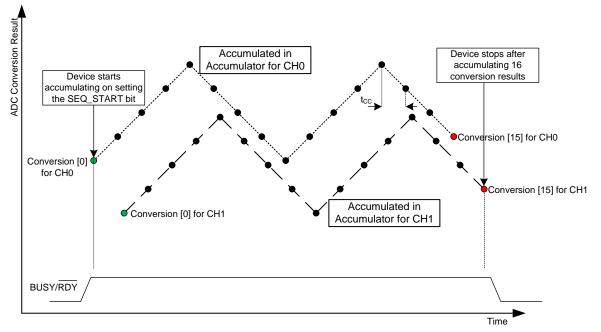

| ADS7142_HighPrecisionMode_CH0Scan.c                            | These routines configure the ADS7142 into high                                                                                                                                                                                                                        |  |  |  |  |

| ADS7142_HighPrecisionMode_CH1Scan.c                            | precision mode in both single-channel and dual-<br>channel configuration. In high precision mode, 16                                                                                                                                                                  |  |  |  |  |

| ADS7142_HighPrecisionMode_AutoSequencing_CH0_CH1_Scan.c        | 12-bit conversions are stored in an accumulator.<br>When the accumulator is filled, the 12-bit<br>conversions are added to form one 16-bit reading.                                                                                                                   |  |  |  |  |

### Table 3. ADS7142 Device Functional Modes Main Routines

6

### 3.3 Software Functions

The main routines that place the ADS7142 into one of its functional modes call a set of functions that configure the registers of the device. Each function excluding *TM4C1294Init()*, *ADS7142Calibrate()*, *ADS7142Reset()*, and *ADS7142HighSpeedEnable()* is developed from pseudocode software flows in the TM4C1294 datasheet. Table 4 provides a brief description of these functions.

| Function Name                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| int TM4C1294Init (uint8_t bFast)                                               | Configures the TM4C1294 as the target device for the compiler, sets the clocking of the device, and enables peripherals to be used in this application. The bFast variable sets the I <sup>2</sup> C frequency (100kHz or 400kHz).                                                                                                                                                                             |

| int ADS7142SingleRegisterWrite(uint8_t RegisterAddress,<br>uint8_RegisterData) | Writes RegisterData to RegisterAddress in order to configure the ADS7142. The ADS7142 slave address is set by hardware on the BoosterPack <sup>™</sup> and is defined in ADS7142RegisterMap.h.                                                                                                                                                                                                                 |

| int ADS7142SingleRegisterRead(uint8_t RegisterAddress,<br>uint32_t *read)      | Reads the data at RegisterAddress and places this data into the read variable for local use.                                                                                                                                                                                                                                                                                                                   |

| void TM4C1294_ArbitrationLost_ErrorService(void)                               | This function performs an I <sup>2</sup> C SDA bus clear in the case that the host MCU loses arbitration. Arbitration loss in a single-master system is usually due to the slave device holding the bus at some undesirable state while the host attempts to perform some I <sup>2</sup> C function. This function configures SCL as a GPIO and toggles SCL nine times, after which the slave releases the bus |

| int ADS7142Calibrate(void)                                                     | This function is called right after <i>TM4C1294Init()</i> to abort the present conversion sequence and calibrate any offset error out of the device.                                                                                                                                                                                                                                                           |

| int ADS7142Reset(void)                                                         | This function gives the user the option of a software reset of the ADS7142. This function is not called in the functional modes firmware because the device calibrates its own offset and I <sup>2</sup> C address upon power-up.                                                                                                                                                                              |

| int ADS7142HighSpeedEnable(uint8_t HighSpeedMask)                              | This function enables the host MCU and ADS7142 to communicate at high speed I <sup>2</sup> C frequencies (1.7 MHz to 3.4 MHz).                                                                                                                                                                                                                                                                                 |

| int ADS7142DataRead_count(uint64_t SampleCount)                                | This function takes a sample count as a user input: the ADS7142 only samples this specified number of samples from the desired input channels. This function is used in high precision mode and autonomous mode to count 16 12-bit conversions before placing them in either the data buffer or channel accumulators.                                                                                          |

| int ADS7142DataRead_infinite(void)                                             | Similar to <i>ADS7142DataRead_count()</i> , this function samples data from the ADS7142 input channels. However, this function infinitely provides sample data as opposed to a specified number of data samples.                                                                                                                                                                                               |

| int ADS7142DataRead_autonomous(void)                                           | This sampling function is specific to the pre-alert and post-alert<br>autonomous modes of the ADS7142. Upon sampling, this<br>function compares the digitized value of the sample to the digital<br>window comparator settings for the high and low threshold<br>alerts.                                                                                                                                       |

### Table 4. Functions Used in Main

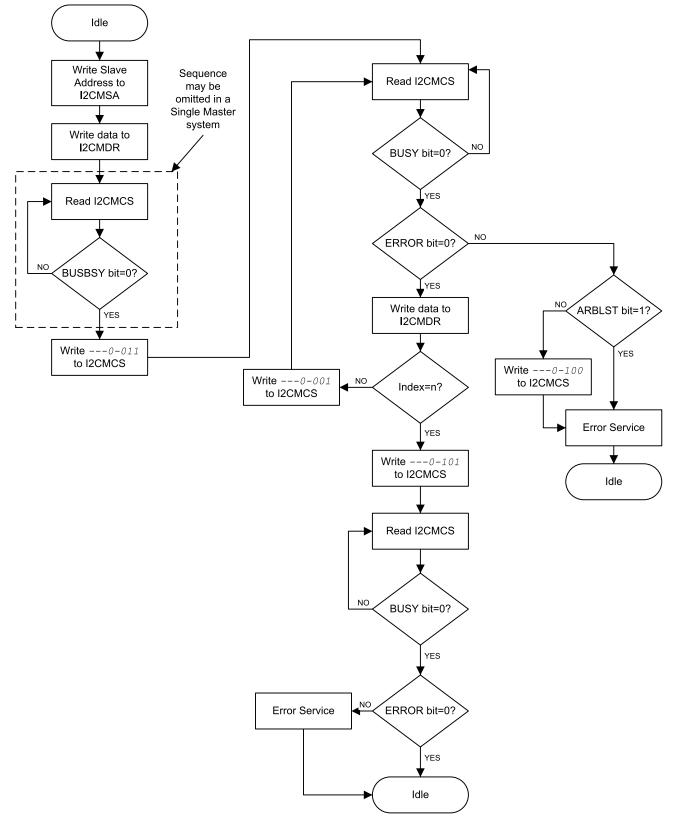

The development of the functions ADS7142SingleRegisterWrite(), ADS7142SingleRegisterRead(), TM4C1294\_ArbitrationLost\_ErrorService, and ADS7142DataRead\_infinite() are crucial to effectively placing the ADS7142 in the user's desired functional mode. ADS7142SingleDataRead\_count() and ADS7142DataRead\_autonomous() are derivatives of ADS7142DataRead\_infinite(). Within each I<sup>2</sup>C module of the master TM4C1294 there is an I2CMasterSlaveAddress (I2CMSA) register that contains the slave address of the device that the host must communicate with over I<sup>2</sup>C. A low-level function named *MasterSlaveAddrSet()* in *i2c.c* is called to configure this address. When the slave address is properly configured, the first data byte can be put into the I2CMasterDataRegister (I2CMDR) via a call of the function *MasterDataPut()*. The I2CMasterDataRegister can be used to either write to or read from the slave device. A master command is then provided to the I2CMasterControlStatus (I2CMCS) register via function call *I2CMasterControl()* to send the data byte. A specific master command is used for multi-byte transmission.

Software

#### Software

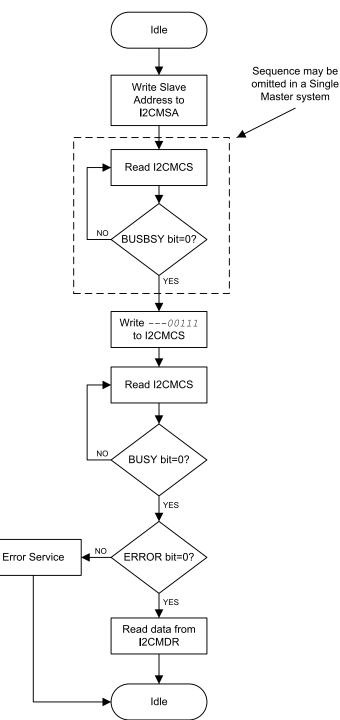

The TM4C1294NCPDT datasheet provides a software flow that is used to develop the function *ADS7142SingleRegisterWrite()*. Figure 4 shows this flow.

8

Figure 5 shows that to write to a single register in the ADS7142 device, the I<sup>2</sup>C master (TM4C1294) must transmit four bytes over I<sup>2</sup>C.

| s | Device Address (7 Bits) W A Write Register or Set Bit or Clear Bit<br>Opcode (8 Bits) |  | A | Register Address (8 Bits) | A | Register Data (8 Bits) | A | P/Sr |  |

|---|---------------------------------------------------------------------------------------|--|---|---------------------------|---|------------------------|---|------|--|

|   |                                                                                       |  |   |                           |   |                        |   |      |  |

|   | Data from Host to Device                                                              |  |   |                           |   |                        |   |      |  |

|   | Data from Device to Host                                                              |  |   |                           |   |                        |   |      |  |

### Figure 5. Writing a Single Register in the ADS7142 Over I<sup>2</sup>C

```

The ADS7142SingleRegisterWrite() function code is the following:

int

ADS7142SingleRegisterWrite (uint8_t RegisterAddress, uint8_t RegisterData)

{

11

//ADS7142SingleRegisterWrite writes data to an ADS7142 register address

//ADS7142registermap.h contains all the device datasheet register map

//register addresses and register values for configuration.

11

11

// Tell the master module what address it will place on the bus when

// communicating with the slave. Set the address to ADS7142_I2C_ADDRESS

// (as set in the slave module). The receive parameter is set to false

// which indicates the I2C Master is initiating a write to the slave. If

// the receive parameter is true, that would indicate that the I2C Master

// is initiating reads from the slave.

11

I2CMasterSlaveAddrSet(I2C8_BASE, ADS7142_I2C_ADDRESS, false);

//Place the first byte to be transmitted into the I2CMDR Register of the TM4C1294

//The first byte to be transmitted following the SLAVE Address is the Single Register Write

opcode

I2CMasterDataPut(I2C8_BASE, SINGLE_REG_WRITE);

//Check the I2C Bus to ensure it is not busy (Read I2CMCS)

//while(I2CMasterBusBusy(I2C8_BASE));

//I2C Master Command for the Start BURST Send of 3 bytes

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_START);

//Implement delay

SysCtlDelay(100);

//Read I2CMCS

//Wait for the I2CMaster to finish transmitting before moving to next byte

while(I2CMasterBusy(I2C8_BASE));

//Check for errors in the I2C8 Module

while (I2CMasterErr(I2C8_BASE))

//Error branching

{

//Check for I2C Bus arbitration loss error condition

if(I2CMasterErr(I2C8_BASE) == I2C_MASTER_ERR_ARB_LOST)

{

```

9

```

Software

```

```

//Error Service

TM4C1294 ArbitrationLost ErrorService();

//Return the error status

return -1;

}

//Write I2C Master Command for error stop if the error

//is not due to i2c bus arbitration loss

else I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_ERROR_STOP);

}

//Place the next byte into I2CMDR, which is the ADS7142 register address for the desired data

write

I2CMasterDataPut(I2C8_BASE, RegisterAddress);

//I2C Master Command for continued BURST send of the next byte

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_CONT);

//Implement Delay

SysCtlDelay(100);

//Read I2CMCS

//Wait for the I2CMaster to finish transmitting before moving to next byte

while(I2CMasterBusy(I2C8_BASE));

//Check for errors in the I2C8 Module

while (I2CMasterErr(I2C8_BASE))

//Error branching

{

//Check for I2C Bus arbitration loss error condition

if(I2CMasterErr(I2C8_BASE) == I2C_MASTER_ERR_ARB_LOST)

{

//Error Service for loss of bus arbitration

TM4C1294_ArbitrationLost_ErrorService();

//Return the error status

return -1;

}

//\ensuremath{\mathsf{Write}} I2C Master Command for receive error stop if the error

//is not due to i2c bus arbitration loss

else I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_ERROR_STOP);

}

//Place the final byte into I2CMDR, which is the register data to be placed in the desired

register address

I2CMasterDataPut(I2C8_BASE, RegisterData);

//I2C Master Command for the finished BURST send of the data

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_FINISH);

//Implement delay

SysCtlDelay(100);

//Read I2CMCS (I2C Master Control/Status)

//Wait for the I2C Master to finish transmitting

while(I2CMasterBusy(I2C8_BASE));

```

Software

www.ti.com

}

```

//Check the error flag in the I2C8 Module

while (I2CMasterErr(I2C8_BASE));

//Return no errors

return 0;

```

To read a single register from the ADS7142, the desired register address must first be set through a series of I<sup>2</sup>C writes. The *ADS7142SingleRegisterRead()* function first performs the multi-byte transmit software flow in Figure 4 to set the register that will be read from the ADS7142. Figure 6 shows the required I<sup>2</sup>C writes prior to register read.

| s | Device Address (7 Bits)  | W | A | Register Read or Block Read<br>Opcode (8 Bits) | A | Register Address (8 Bits) | A | P/Sr |

|---|--------------------------|---|---|------------------------------------------------|---|---------------------------|---|------|

|   | Data from Host to Device |   |   |                                                |   |                           |   |      |

|   | Data from Device to Host |   |   |                                                |   |                           |   |      |

Figure 6. Setting Register Address for a Single Register Read From the ADS7142

Software

www.ti.com

When the required write operations are complete, the host MCU can read the register data. This operation is outlined as a master single byte receive software flow in the TM4C1294NCPDT datasheet. Figure 7 shows the TM4C1294NCPDT single byte receive software flow.

As Figure 8 shows, this software flow is also represented using I<sup>2</sup>C frames.

| s | Device Address (7 Bits)  | R | A | Register Data (8 Bits) | A | P/Sr |

|---|--------------------------|---|---|------------------------|---|------|

|   | Data from Host to Device |   |   |                        |   |      |

|   | Data from Device to Host |   |   |                        |   |      |

### Figure 8. ADS7142 Single Register Read

The function code for the operations required to perform a single register read is the following: int ADS7142SingleRegisterRead(uint8\_t RegisterAddress, uint32\_t \*read) { //ADS7142SingleRegisterRead reads data from a single register //in the ADS7142. 11 11 // Tell the master module what address it will place on the bus when // communicating with the slave. Set the address to ADS7142\_I2C\_ADDRESS // (as set in the slave module). The receive parameter is set to false // which indicates the I2C Master is initiating a write to the slave. // To perform a register read, the Master must first transmit the desired I2C address for communication. // Following the I2C address transmission, the single register read opcode will be transmitted. // The receive parameter is then set to true for read of register contents. 11 I2CMasterSlaveAddrSet(I2C8\_BASE, ADS7142\_I2C\_ADDRESS, false); //Place the Single Register Read opcode into the I2CMDR Register I2CMasterDataPut(I2C8\_BASE, SINGLE\_REG\_READ); //Initiate the BURST Send of two data bytes I2CMasterControl(I2C8\_BASE, I2C\_MASTER\_CMD\_BURST\_SEND\_START); //Implement Delay SysCtlDelay(100); //Wait for the I2C Master to finish transmitting while(I2CMasterBusy(I2C8\_BASE)); //Check for errors in the I2C8 Module while (I2CMasterErr(I2C8\_BASE)) //Error branching { //Check for I2C Bus arbitration loss error condition if(I2CMasterErr(I2C8\_BASE) == I2C\_MASTER\_ERR\_ARB\_LOST) {

//Error service for loss of bus arbitration

```

Software

```

```

TM4C1294_ArbitrationLost_ErrorService();

//Return the error status

return -1;

}

//Write I2C Master Command for receive error stop if the error

//is not due to i2c bus arbitration loss

else I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_ERROR_STOP);

}

//Place the Register Address to be communicated with into the I2CMDR Register

I2CMasterDataPut(I2C8_BASE,RegisterAddress);

//I2C Master Command for finished Burst Send of the two bytes required for register read

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_FINISH);

//Implement Delay

SysCtlDelay(100);

//Wait for the I2C Master to finish transmitting the data

while(I2CMasterBusy(I2C8_BASE));

//Check the error flag in the I2C8 Module

while(I2CMasterErr(I2C8_BASE))

//Error service for address ACK or data ACK

}

//Set the receive parameter to true in order to receive data from the desired register address

I2CMasterSlaveAddrSet(I2C8_BASE, ADS7142_I2C_ADDRESS, true);

//Check the I2C Bus to ensure it is not busy

while(I2CMasterBusBusy(I2C8_BASE));

//I2C Master Command for the Single Byte Receive from the register address

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_SINGLE_RECEIVE);

//Implement Delay

SysCtlDelay(100);

//Wait for the I2C Master to finish transmitting the data

while(I2CMasterBusy(I2C8_BASE));

//Check the error flag in the I2C8 Module

while(I2CMasterErr(I2C8_BASE))

{

//Error service for address ACK or data ACK

}

//Get the data placed into the I2CMDR Register from the ADS7142

//Place data into the read flag that contains the data for local use

read[0] = I2CMasterDataGet(I2C8_BASE);

//Return no errors

return 0;

```

}

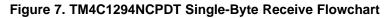

In order for conversion data to be read continuously from the ADS7142, the TM4C1294 must perform a multi-byte receive operation over I<sup>2</sup>C. This software flow is the basis for the functions *ADS7142DataRead\_infinite(), ADS7142DataRead\_count(),* and *ADS7142DataRead\_autonomous().* Figure 9 shows the pseudocode flow.

## Figure 9. TM4C1294NCPDT Multi-Byte Receive Flowchart

#### Software

www.ti.com

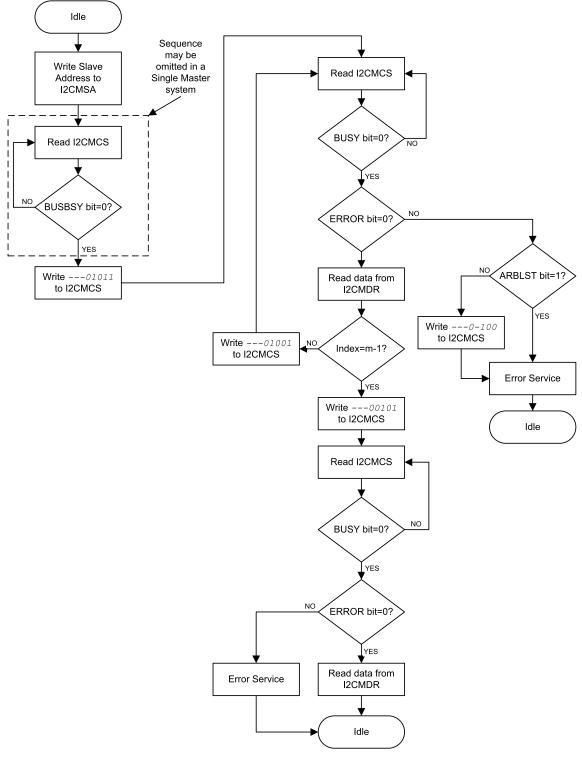

Let's take a look at the development of *ADS7142DataRead\_continuous()*. This function is only used in manual mode because in this mode, the ADS7142 is continuously outputting sample data from the desired input channels. Figure 10 shows the continuous read of sample bytes.

Figure 10. Reading ADS7142 Conversion Data in Manual Mode

The ADS7142DataRead\_continuous() function code is the following:

```

int.

ADS7142DataRead_continuous(void)

{

11

//ADS7142DataRead_continuous() continuously clocks out the data sampled by the ADS7142

//once it is placed in manual mode. The function provides

//continuous SCL to clock out the data

11

//Provide Device Address and Read Bit to Start Conversions

I2CMasterSlaveAddrSet(I2C8 BASE, ADS7142 I2C ADDRESS, true);

//Check the I2C Bus to ensure it is not busy

//while(I2CMasterBusBusy(I2C8_BASE));

//Write the Burst receive I2C Master Command to I2CMCS

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_START);

//Implement Delay

SysCtlDelay(100);

//Allow the Master to finish receiving the first byte

while(I2CMasterBusy(I2C8_BASE));

//Check for errors in the I2C8 Module

while (I2CMasterErr(I2C8_BASE))

//Error branching

{

//Check for I2C Bus arbitration loss error condition

if (I2CMasterErr(I2C8_BASE) == I2C_MASTER_ERR_ARB_LOST)

{

//Error service for loss of bus arbitration

TM4C1294_ArbitrationLost_ErrorService();

//Return the error status

return -1;

```

}

#### Software

```

TEXAS

INSTRUMENTS

```

```

www.ti.com

```

```

//Write I2C Master Command for receive error stop if the error

//is not due to i2c bus arbitration loss

else

{

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_ERROR_STOP);

//Error service for address ACK or data ACK

}

}

}

//Read data from I2CMDR

I2CMasterDataGet(I2C8_BASE);

//Provide Continuous SCL

while(1)

{

//Continue receiving the burst data

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_RECEIVE_CONT);

//Implement Delay

SysCtlDelay(100);

//Allow the Master to finish receiving each byte

while(I2CMasterBusy(I2C8_BASE));

//Check for errors in the I2C8 Module

while (I2CMasterErr(I2C8_BASE))

//Error branching

{

//Check for I2C Bus arbitration loss error condition

if(I2CMasterErr(I2C8_BASE) == I2C_MASTER_ERR_ARB_LOST)

{

//Error service for loss of bus arbitration

TM4C1294_ArbitrationLost_ErrorService();

//Return the error status

return -1;

}

//Write I2C Master Command for receive error stop if the error

//is not due to i2c bus arbitration loss

else

{

I2CMasterControl(I2C8_BASE, I2C_MASTER_CMD_BURST_SEND_ERROR_STOP);

//Error Service for address ACK or data ACK

}

```

}

```

Using the Software

```

}

```

}

//Receive data in I2CMDR

I2CMasterDataGet(I2C8_BASE);

}

//Return no errors

return 0;

```

The ADS7142DataRead\_count() and ADS7142DataRead\_autonomous() functions are discussed and presented in Section 5 for sake of coherence to the functional modes they are used in.

## 4 Using the Software

## 4.1 Prerequisites

To successfully compile the project, download and run the software described in this document, the following hardware and software is required:

- ARM Cortex-M4F-based MCU TM4C1294 connected LaunchPad™ evaluation kit

- ADS7142 nanopower, dual-channel, programmable sensor monitor BoosterPack™ plug-in module

- Code composer studio (CCS) integrated development environment (IDE) (version 7.4.0.00015)

- TivaWare (version 2.1.4.178)

## 4.2 Getting Started

Follow these steps to get the ADS7142 device functional modes firmware up and running:

- 1. Install Code Composer Studio version 7.4.0.00015.

- 2. In order to reach TivaWare, go to the MSP430Ware page and click on the *Start Development* button to download the MSP430Ware-cloud tool and the TI Resource Explorer will open in your browser.

- 3. On the left hand side of the screen under *Software* click on *TM4C ARM Cortex-M4F MCU v*:2.1.3.156.

- 4. Under Libraries click on Driver Library.

- 5. Click on the *Download all* button on the right hand side of the screen to download both the user's guide and driverlib files.

- 6. After the driver files have been downloaded, move them to the workspace folder. This folder should be located in *C://Users/workspacev7*.

- 7. Download the ADS7142 device functional modes firmware from ti.com, located under Software. Unzip the files into your working Code Composer Studio Directory. Your working directory is normally located under *C://Users/workspacev7*.

- 8. Open Code Composer Studio and start a new project by clicking on  $File \rightarrow New \rightarrow CCS$  Project.

- a. Name the project as desired. At the top of this window, ensure that the Target device is selected to be the Tiva TM4C1294NCPDT.

- b. Right click on the project in the project explorer and click on Add Files.

- c. Select all of the files that were downloaded into the workspace from ti.com and click Open.

- 9. Right click the project name in the workspace window and click on *Properties*. A window should appear.

- a. Under *General options*, select the TIVA TM4C1294NCPDT. In the *Connection* drop down menu select the *Stellaris In-Circuit Debug Interface*.

- b. Under *Tool-Chain* select the appropriate device endianness *little* for the TM4C1294NCPDT. In the *Linker command file* field browse your directory for the .cmd file for your device. In this case, this file is *tm4c1294ncpdt.cmd*.

- c. On the left hand side there is a side menu. Click on the expansion arrow next to *Build*. Click on *ARM Compiler*.

- i. Under *Include Options* click on the paper icon with a green plus to add an include directory. Add the directory in which the *TivaWare\_C\_Series-2.1.4.178* folder is located.

- ii. Under *Predefined Symbols* click on the paper icon with a green plus to add the appropriate predefined NAMEs for your target device. Add *TARGET\_IS\_TM4C129\_RA0* and *PART\_TM4C1294NCPDT* exactly as shown.

- d. Click on *File Search Path*. Add a library that points to the *driverlib.lib file* within the *TivaWare\_C\_Series 2.1.4.178* folder. This path should be *C://Users/workspacev7/TivaWare\_C\_Series-2.1.4.178/driverlib/ccs/Debug/driverlib.lib*.

- 10. Click OK to close the Project Properties window.

- 11. Select  $Project \rightarrow Build Project$ .

- 12. Delete the main.c file that was created when the project was created.

- 13. Choose one device functional mode C file you would like to build. There should be three C files included in the project build: TM4C1294\_ADS7142\_Functions.c, tm4c1294ncpdt\_startup\_ccs.c, and your desired ADS7142 functional mode C file. The ADS7142RegisterMap.h file should also be included in the project build. Select all undesired functional mode C files and once highlighted, right click then click on Exclude from build.

- 14. Rebuild the project and only warnings should appear.

- 15. As illustrated in Figure 3, connect the ADS7142BoosterPack to the TM4C1294 target board.

### 4.3 Using the Library

The project explorer in the Code Composer Studio should look like Figure 11 when the software is downloaded. There should be numerous main routine files that are not included in the current build. This directory appearance is normal, as only one routine should run at a given time.

|                                                                       | Pro  | ject     | Explorer 🛛                                                      | \$₽\$ | ~ ' | - 8 |  |

|-----------------------------------------------------------------------|------|----------|-----------------------------------------------------------------|-------|-----|-----|--|

|                                                                       | v (# | AD:      | S7142 Device Functional Modes [Active - Debug]                  |       |     |     |  |

|                                                                       | >    | 紧        | Binaries                                                        |       |     |     |  |

|                                                                       |      | <u>j</u> | Includes                                                        |       |     |     |  |

|                                                                       | >    | ē        | Debug                                                           |       |     |     |  |

| Ensure that only one of the functional                                | >    | B        | targetConfigs                                                   |       |     |     |  |

| mode main routine files is included in the project. Exclude all other | >    | .C       | ADS7142_ManualMode_CH0Scan.c                                    |       |     |     |  |

| functional modes from the build                                       | >    | .h       | ADS7142RegisterMap.h                                            |       |     |     |  |

|                                                                       | >    | C        | TM4C1294_ADS7142_Functions.c                                    |       |     |     |  |

|                                                                       | → >  | .C       | tm4c1294ncpdt_startup_ccs.c                                     |       |     |     |  |

|                                                                       | >    |          | tm4c1294ncpdt.cmd                                               |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PostAlert_AutoSequencing_CH0_CH1_Scan.c  |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PostAlert_CH0Scan.c                      |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PostAlert_CH1Scan.c                      |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PreAlert_AutoSequencing_CH0_CH1_Scan.c   |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PreAlert_CH0Scan.c                       |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_PreAlert_CH1Scan.c                       |       |     |     |  |

|                                                                       |      | _        | ADS7142_AutonomousMode_StartBurst_AutoSequencing_CH0_CH1_Scan.c |       |     |     |  |

|                                                                       |      | _        | ADS7142_AutonomousMode_StartBurst_CH0Scan.c                     |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_StartBurst_CH1Scan.c                     |       |     |     |  |

|                                                                       |      | _        | ADS7142_AutonomousMode_StopBurst_AutoSequencing_CH0_CH1_Scan.c  |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_StopBurst_CH0Scan.c                      |       |     |     |  |

|                                                                       |      |          | ADS7142_AutonomousMode_StopBurst_CH1Scan.c                      |       |     |     |  |

|                                                                       |      |          | ADS7142_HighPrecisionMode_AutoSequencing_CH0_CH1_Scan.c         |       |     |     |  |

|                                                                       |      |          | ADS7142_HighPrecisionMode_CH0Scan.c                             |       |     |     |  |

|                                                                       |      |          | ADS7142_HighPrecisionMode_CH1Scan.c                             |       |     |     |  |

|                                                                       |      | _        | ADS7142_ManualMode_AutoSequencing_CH0_CH1_Scan.c                |       |     |     |  |

|                                                                       |      | 15       | ADS7142_ManualMode_CH1Scan.c                                    |       |     |     |  |

Figure 11. Project Explorer

Figure 12 shows how to change the current functional mode routine. The selected functional mode must be included in the current build before excluding the current one.

Figure 12. Including a File in the Project Build

🖽 🐝 🗸 🗖 🗖 Project Explorer 53 ✓ ADS7142 Device Functional Modes [Active - Debug] Binaries To exclude a functional mode from > includes the build, right-click on the file name Debug and the drop-down menu will targetConfigs appear as shown ADS7142\_ManualMode\_CHinc-New 5 ADS7142RegisterMap.h C TM4C1294\_ADS7142\_Funct Open tm4c1294ncpdt\_startup\_cc Open With 5 tm4c1294ncpdt.cmd Show in Local Terminal , AD57142\_AutonomousMo ADS7142 AutonomousMo D Copy Ctrl+C ADS7142\_AutonomousMo Paste Ctrl+V ADS7142\_AutonomousMo 🕅 ADS7142\_AutonomousMo 💥 Delete Delete De ADS7142 AutonomousMo Source 5 ADS7142 AutonomousMo Move ... ADS7142\_AutonomousMo Rename... F2 ADS7142\_AutonomousMo ADS7142\_AutonomousMo Import з ADS7142\_AutonomousMo Export... ADS7142\_AutonomousMo ADS7142 HighPrecisionMd Show Build Settings.. ADS7142 HighPrecisionMo **Build Selected File(s)** ADS7142\_HighPrecisionMc Clean Selected File(s) ADS7142\_ManualMode\_Au Exclude from Build Click on "Exclude from Build" to have the ADS7142\_ManualMode\_CF selected file excluded from the current **Build Project** build configuration Clean Project **Rebuild Project** Refresh F5 Index з Make Targets 5 **Resource** Configurations > Team х Compare With 5 Replace With 5 Properties Alt+Enter

Figure 13 shows how to exclude and swap a file for the desired one.

Figure 13. Excluding a File From the Project Build

When including the desired files for compilation, the user can build and run the project.

### 5 Main Routines and Test Data

When developing this firmware framework, Texas Instruments used a National Instruments VirtualBench to set two DC inputs to the ADS7142 for testing of dual-channel sampling capability. One input was set slightly above the middle of the ADS7142 full-scale range, and the other set one volt above this level. The reference on the ADS7142BoosterPack<sup>™</sup> is set to 3.3 V so voltage inputs to the ADS7142 channels are limited to a maximum of 3.3 V. The output code equation in decimal for a SAR ADC is:

Output Code (decimal) =  $(\frac{V_{nput}}{V_{Ref}}) \times 2^{Resolution}$

For convenient conversion of decimal output codes to hexadecimal output codes TI recommends using the Analog Engineer's Calculator. The calculator contains an *ADC Code to Voltage* converter under the *Data Converters* calculator. The logic analyzer used to decode the I<sup>2</sup>C data provides outputs in hexadecimal form.

(1)

### 5.1 Manual Mode

At power up, the ADS7142 goes into manual mode. In this mode, the device uses the high frequency oscillator for conversions. This mode allows the external host processor to directly request and control when the data is sampled. The resolution is set to 12 bits and samples are clocked out by providing continuous SCL when the desired channels are selected.

If the device scans both channels in AUTO sequence, the first data (sample A) is from CH0 and second data (sample A+1) is from CH1. The main routine for manual mode operation with AutoSequencing of both channels is as follows:

#include "ADS7142RegisterMap.h" /\* ADS7142\_ManualMode\_AutoSequencing\_CH0\_CH1\_Scan.c \*/ int main(void) { //Initialize the master MCU (0 = 100 kHz SCL, 1 = 400 kHz SCL) TM4C1294Init(0); //Calibrate out the offset of the ADS7142 ADS7142Calibrate(); //Let's put the ADS7142 into Manual Mode with both Channels enabled in Single-Ended Configuration for AUTO Sequencing //Select the channel input configuration ADS7142SingleRegisterWrite(ADS7142\_REG\_CHANNEL\_INPUT\_CFG, ADS7142\_VAL\_CHANNEL\_INPUT\_CFG\_2\_CHANNEL\_SINGLE\_ENDED); //Confirm the input channel configuration uint32\_t channelconfig; ADS7142SingleRegisterRead(ADS7142\_REG\_CHANNEL\_INPUT\_CFG, & channelconfig); //Select the operation mode of the device ADS7142SingleRegisterWrite(ADS7142\_REG\_OPMODE\_SEL, ADS7142\_VAL\_OPMODE\_SEL\_I2C\_CMD\_MODE\_W\_AUTO\_SEQ\_EN); //Confirm the operation mode selection uint32\_t opmodeselconfig; ADS7142SingleRegisterRead(ADS7142\_REG\_OPMODE\_SEL, &opmodeselconfig); //Set the I2C Mode to High Speed (optional) //ADS7142HighSpeedEnable(ADS7142\_VAL\_OPMODE\_I2CMODE\_HS\_1); //Check the I2C Mode Status uint32\_t opmodei2cconfig; ADS7142SingleRegisterRead(ADS7142\_REG\_OPMODE\_I2CMODE\_STATUS, &opmodei2cconfig); //Configure Auto Sequencing for both channels ADS7142SingleRegisterWrite(ADS7142\_REG\_AUTO\_SEQ\_CHEN, ADS7142\_VAL\_AUTO\_SEQ\_CHENAUTO\_SEQ\_CH0\_CH1); //Confirm Auto Sequencing Register Configuration uint32\_t autoseqchenconfig; ADS7142SingleRegisterRead(ADS7142\_REG\_AUTO\_SEQ\_CHEN, &autoseqchenconfig); //Set SEQ\_START Bit to start the sampling Sequence ADS7142SingleRegisterWrite(ADS7142\_REG\_START\_SEQUENCE, ADS7142\_VAL\_START\_SEQUENCE); //Begin manual mode operation with AUTO Sequencing //Start Sampling Ch0 and Ch1

Main Routines and Test Data

Main Routines and Test Data

//Return no errors

return(0);

}

The I<sup>2</sup>C address of the ADS7142 is a 7-bit address followed by a read/write bit indicating the direction of data transfer. The I<sup>2</sup>C address of the ADS7142 is set to 0x18 (001 1000 R/W) by the hardware configuration of the ADS7142BoosterPack<sup>™</sup>. The analyzer sees an 8-bit address with the R/W bit as part of the address, and therefore reports the I<sup>2</sup>C address as 0x30 (0011 0000) for a write operation and 0x31 (0011 0001) for a read operation. Figure 14 illustrates the test data from the salae logic analyzer.

Masks that contain the letters REG refer to ADS7142 register masks, and masks that contain the letters VAL refer to ADS7142 value masks.

|                                                 | Single Register Write                                    | Setup Write to [0x30] + ACK               |                      |

|-------------------------------------------------|----------------------------------------------------------|-------------------------------------------|----------------------|

|                                                 |                                                          | 0x08 + ACK                                |                      |

|                                                 | ADS7142_REG_ABORT_SEQUENCE<br>ADS7142_VAL_ABORT_SEQUENCE | UXII T ACK                                |                      |

|                                                 | AD3/142_VAL_ABORT_SEQUENCE                               | 0x01 + ACK                                |                      |

|                                                 | Cingle Degister Write                                    | Setup Write to [0x30] + ACK               |                      |

|                                                 | Single Register Write                                    | 0x08 + ACK                                |                      |

|                                                 | ADS7142 REG_OFFSET_CAL                                   |                                           |                      |

|                                                 | ADS7142_VAL_TRIG_OFFCAL                                  | 0x01 + ACK                                |                      |

|                                                 |                                                          | Setup Write to [0×30] + ACK               |                      |

|                                                 | Single Register Write                                    | OADO TACK                                 |                      |

|                                                 | ADS7142_REG_CHANNEL_INPUT_CFG                            | 0x24 + ACK                                |                      |

| ADS7142_VAL_CHANNEL_                            | INPUT_CFG_2_CHANNEL_SINGLE_ENDED                         | 0x03 + ACK                                |                      |

|                                                 |                                                          | Setup Write to [0x30] + ACK               |                      |

|                                                 | Single Register Read                                     | 0x10 + ACK                                |                      |

|                                                 | ADS7142_REG_CHANNEL_INPUT_CFG                            | 0x24 + ACK                                |                      |

|                                                 | •                                                        | Setup Read to [0×31] + ACK                |                      |

| ADS7142_VAL_CHANNEL_I                           | NPUT_CFG_2_CHANNEL_SINGLE_ENDED                          | 0x03 + NAK                                |                      |

|                                                 |                                                          | Setup Write to [0x30] + ACK               |                      |

|                                                 | Single Register Write                                    | 0x08 + ACK                                |                      |

|                                                 | ADS7142_REG_OPMODE_SEL                                   | 0x1C + ACK                                |                      |

| ADS7142_VAL_OPMODE_S                            | EL_I2C_CMD_MODE_W_AUTO_SEQ_EN &                          | 0x04 + ACK                                |                      |

|                                                 |                                                          | Setup Write to [0x30] + ACK               |                      |

|                                                 | Single Register Read                                     |                                           |                      |

|                                                 | ADS7142_REG_OPMODE_SEL                                   | 0x1C + ACK                                |                      |

|                                                 | _SEL_I2C_CMD_MODE_W_AUTO_SEQ_EN                          | Setup Read to [0×31] + ACK                |                      |

| AD37142_VAL_011000L_                            |                                                          | 0x04 + NAK                                |                      |

|                                                 |                                                          | Setup Write to [0x30] + ACK               |                      |

|                                                 | Single Register Read                                     |                                           |                      |

| ADS                                             | S7142_REG_OPMODE_ <u>I2CMODE_STATUS</u>                  | 0x00 + ACK                                |                      |

|                                                 | Device is operating in Manual Mode                       | Setup Read to [0×31] + ACK                |                      |

|                                                 |                                                          | 0X00 T NAK                                |                      |

|                                                 | Single Register Write                                    | Setup Write to [0x30] + ACK               |                      |

|                                                 | ADS7142_REG_AUTO_SEQ_CHEN                                | 0x08 + ACK                                |                      |

| ADS71/12 VAL                                    | 0x20 + ACK                                               |                                           |                      |

|                                                 | AUTO_SEQ_CHENAUTO_SEQ_CH0_CH1 (                          | 0x03 + ACK                                |                      |

|                                                 |                                                          | Setup Write to [0x30] + ACK               |                      |

|                                                 |                                                          | 0x10 + ACK                                |                      |

| After the                                       | e device is configured for Manual Mode                   | 0x20 + ACK                                |                      |

|                                                 | annel Sampling, continuous clocks are                    | Setup Read to [0×31] + ACK<br>0×03 + NAK  |                      |

| provided to reveal the conversion data for each |                                                          |                                           |                      |

| provideo                                        | channel                                                  | Setup Write to [0x30] + ACK<br>0x08 + ACK |                      |

|                                                 |                                                          |                                           |                      |

|                                                 | $\backslash$                                             | Ox1E + ACK                                |                      |

|                                                 |                                                          | 0x01 + ACK                                |                      |

|                                                 |                                                          | Setup Read to [0x31] + ACK<br>0x81 + ACK  | CH0 Data             |

| <b>F</b> .                                      | ach channel sample is a 2-byte frame (16-                | 0x00 + ACK                                | CH0 Data             |

|                                                 | bits). In 12-bit resolution mode, the                    | 0xCC + ACK                                | CH0 Data             |

|                                                 | evice will report 0000 for the last 4 bits of            | 0x60 + ACK                                | CH1 Data<br>CH1 Data |

|                                                 | the second byte frame. The first sample                  | 0x81 + ACK                                | CHI Data             |

|                                                 | output code is 0x8100 from Channel 0                     | 0x70 + ACK                                | CH0 Data             |

|                                                 | followed by 0xCC60 from Channel 1.                       | 0xCC + ACK                                | CH1 Data             |

|                                                 |                                                          | 0x30 + ACK                                | CH1 Data             |

|                                                 |                                                          | -                                         |                      |

|                                                 | Figure 14. Manual Mode Dual Chan                         | nel Sampling Test Data                    |                      |

### Figure 14. Manual Mode Dual Channel Sampling Test Data

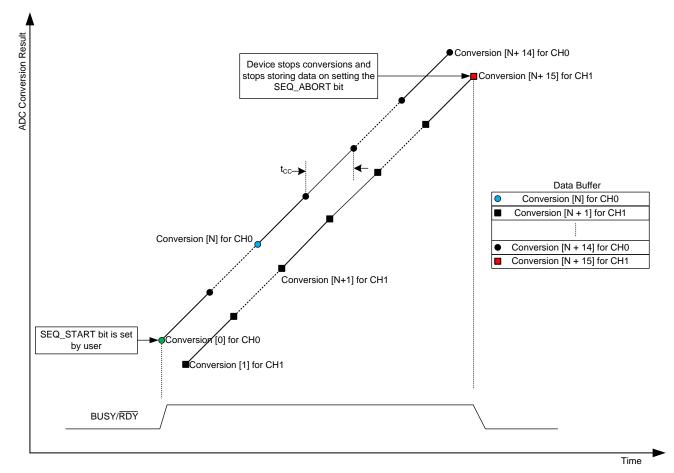

In autonomous mode with pre alert data, the ADS7142 automatically scans the input voltage on the input channels and generates a signal when the programmable high or low threshold values are crossed. The device stores the 16 conversion results prior to the activation of the alert. When the alert is activated, conversion stops and the data buffer is no longer filled. Figure 15 shows the filling of the data buffer in autonomous mode with pre alert data.

Figure 15. Pre Alert Data for Dual-Channel Configuration

### The example main routine for this mode is the following:

```

/*

ADS7142_AutonomousMode_PreAlert_AutoSequencing_CH0_CH1_Scan.c

*/

int main(void)

{

//Initialize the master MCU (0 = 100 kHz SCL, 1 = 400 kHz SCL)

TM4C1294Init(0);

//Calibrate out the offset from the ADS7142

ADS7142Calibrate();

//Let's put the ADS7142 into Autonomous Mode with both Channels enabled in Single-

Ended Configuration

```

```

//Select the channel input configuration

```

#include "ADS7142RegisterMap.h"

#### Main Routines and Test Data

```

ADS7142SingleRegisterWrite(ADS7142_REG_CHANNEL_INPUT_CFG,

ADS7142_VAL_CHANNEL_INPUT_CFG_2_CHANNEL_SINGLE_ENDED);

//Confirm the input channel configuration

uint32 t channelconfig;

ADS7142SingleRegisterRead(ADS7142_REG_CHANNEL_INPUT_CFG, & channelconfig);

//Select the operation mode of the device

ADS7142SingleRegisterWrite(ADS7142_REG_OPMODE_SEL,

ADS7142_VAL_OPMODE_SEL_AUTONOMOUS_MONITORING_MODE);

//Confirm the operation mode selection

uint32_t opmodeselconfig;

ADS7142SingleRegisterRead(ADS7142_REG_OPMODE_SEL, &opmodeselconfig);

//Set the I2C Mode to High Speed (optional)

//ADS7142HighSpeedEnable(ADS7142_VAL_OPMODE_I2CMODE_HS_1);

//Check the I2C Mode Status

uint32 t opmodei2cconfig;

ADS7142SingleRegisterRead(ADS7142_REG_OPMODE_I2CMODE_STATUS, &opmodei2cconfig);

//Select both channels for AUTO Sequencing

ADS7142SingleRegisterWrite(ADS7142_REG_AUTO_SEQ_CHEN, ADS7142_VAL_AUTO_SEQ_CHENAUTO_SEQ_CH0_CH1);

//Confirm Auto Sequencing is enabled

uint32_t autoseqchenconfig;

ADS7142SingleRegisterRead(ADS7142_REG_AUTO_SEQ_CHEN, &autoseqchenconfig);

//Select the Low Power or High Speed Oscillator

ADS7142SingleRegisterWrite(ADS7142_REG_OSC_SEL, ADS7142_VAL_OSC_SEL_HSZ_HSO);

//Confirm the oscillator selection

uint32_t oscconfig;

ADS7142SingleRegisterRead(ADS7142_REG_OSC_SEL, &oscconfig);

//Set the minimum nCLK value for one conversion to maximize sampling speed

ADS7142SingleRegisterWrite(ADS7142_REG_nCLK_SEL, 21);

//Confirm the nCLK selection

uint32_t nCLKconfig;

ADS7142SingleRegisterRead(ADS7142_REG_nCLK_SEL, &nCLKconfig);

//Select the Data Buffer output data Configuration

ADS7142SingleRegisterWrite(ADS7142_REG_DOUT_FORMAT_CFG, ADS7142_VAL_DOUT_FORMAT_CFG_DOUT_FORMAT2);

//Select the Data Buffer opmode for Pre-Alert mode

ADS7142SingleRegisterWrite(ADS7142_REG_DATA_BUFFER_OPMODE,

ADS7142_VAL_DATA_BUFFER_STARTSTOP_CNTRL_PREALERT);

//Configure CH0 High Threshold MSB

ADS7142SingleRegisterWrite(ADS7142_REG_DWC_HTH_CH0_MSB, 0x90);

//Configure CH0 High Threshold LSB

ADS7142SingleRegisterWrite(ADS7142_REG_DWC_HTH_CH0_LSB, 0x00);

//Configure CH0 Low Threshold MSB

ADS7142SingleRegisterWrite(ADS7142_REG_DWC_LTH_CH0_MSB, 0x00);

//Configure CH0 Low Threshold LSB

ADS7142SingleRegisterWrite(ADS7142_REG_DWC_LTH_CH0_LSB, 0x00);

//Set the Hysteresis for CH0

ADS7142SingleRegisterWrite(ADS7142_REG_DWC_HYS_CH0, 0x00);

//Configure CH1 High Threshold MSB

```

#### Main Routines and Test Data

ADS7142SingleRegisterWrite(ADS7142\_REG\_DWC\_HTH\_CH1\_MSB, 0xE0); //Configure CH1 High Threshold LSB ADS7142SingleRegisterWrite(ADS7142\_REG\_DWC\_HTH\_CH1\_LSB, 0x00); //Configure CH1 Low Threshold MSB ADS7142SingleRegisterWrite(ADS7142\_REG\_DWC\_LTH\_CH1\_MSB, 0x00); //Configure CH1 Low Threshold LSB ADS7142SingleRegisterWrite(ADS7142\_REG\_DWC\_LTH\_CH1\_LSB, 0x00); //Set the Hysteresis for CH1 ADS7142SingleRegisterWrite(ADS7142\_REG\_DWC\_HYS\_CH1, 0x00); //Set the Pre-Alert Event Counter ADS7142SingleRegisterWrite(ADS7142\_REG\_PRE\_ALERT\_EVENT\_COUNT, ADS7142\_VAL\_PRE\_ALERT\_EVENT\_COUNT4); //Confirm the Pre-Alert Event Counter setting uint32\_t eventcount; ADS7142SingleRegisterRead(ADS7142\_REG\_PRE\_ALERT\_EVENT\_COUNT, &eventcount); //Enable Alerts ADS7142SingleRegisterWrite(ADS7142\_REG\_ALERT\_CHEN, ADS7142\_VAL\_ALERT\_EN\_CH0\_CH1); //Enable the digital window comparator block ADS7142SingleRegisterWrite(ADS7142\_REG\_ALERT\_DWC\_EN, ADS7142\_VAL\_ALERT\_DWC\_BLOCK\_ENABLE); //Set the SEQ\_START Bit to begin the sampling sequence ADS7142SingleRegisterWrite(ADS7142\_REG\_START\_SEQUENCE, ADS7142\_VAL\_START\_SEQUENCE); //Begin Autonomous Mode Pre-Alert operation and Scan both channels 0 and 1 while (1) { //Start Scanning CH0 and CH1 //If Alert is set, device stops conversions and filling the data buffer //Read the latched flags of the Digital Window Comparator while (ADS7142DataRead\_autonomous() < 0);</pre> //Reset the alert flags ADS7142SingleRegisterWrite(ADS7142\_REG\_ALERT\_HIGH\_FLAGS, 0x03); ADS7142SingleRegisterWrite(ADS7142\_REG\_ALERT\_LOW\_FLAGS, 0x03); //Read the Data Buffer Status uint32\_t databufferstatus; ADS7142SingleRegisterRead(ADS7142\_REG\_DATA\_BUFFER\_STATUS, &databufferstatus); //Read the Data Buffer while (ADS7142DataRead\_count(16) < 0);</pre> //Restart the sequence ADS7142SingleRegisterWrite(ADS7142\_REG\_START\_SEQUENCE, ADS7142\_VAL\_START\_SEQUENCE); } //Return no errors return 0; }

Ţexas

TRUMENTS

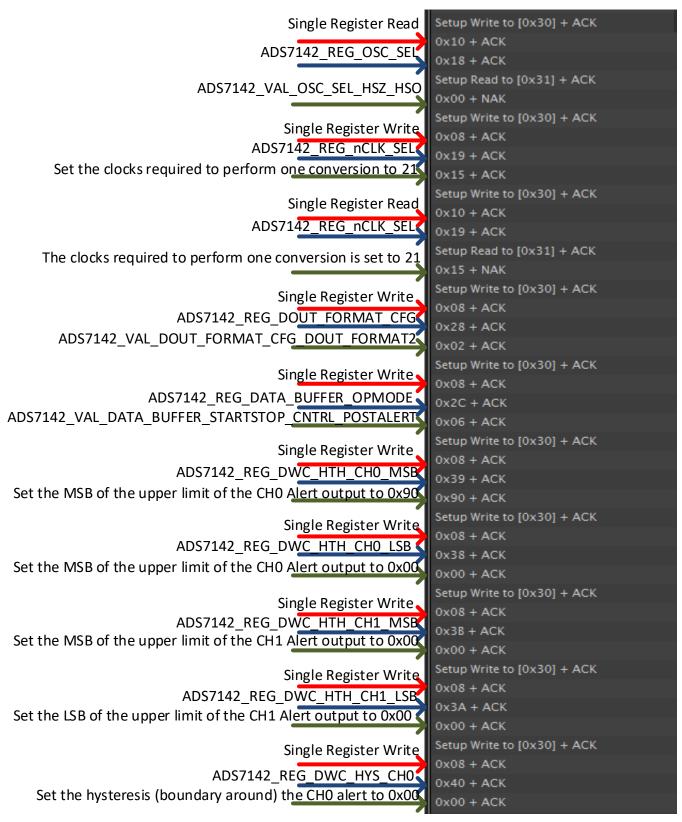

The data output seen from the logic analyzer corresponds to what is written in main. Figure 16 shows the ADS7142 configuration.

| Single Desister Write Setup Write to $10 \times 301 \pm 4$ CV                              |   |

|--------------------------------------------------------------------------------------------|---|

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

| ADS7142_REG_ABORT_SEQUENCE                                                                 |   |

| ADS7142_VAL_ABORT_SEQUENCE                                                                 |   |

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

| Single Register Write                                                                      | U |

| ADS/142_KEG_OFFSET_CAL 0x15 + ACK                                                          |   |

| ADS7142_VAL_TRIG_OFFCAL                                                                    |   |

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

| 0x08 + ACK                                                                                 |   |

| ADS7142_REG_CHANNEL_INPUT_CFG<br>ADS7142_VAL_CHANNEL_INPUT_CFG_2_CHANNEL_SINGLE_ENDED      |   |

| AD3/142_VAL_CHANNEL_INFOT_CFG_2_CHANNEL_SINGLE_ENDED 0x03 + ACK                            |   |

| Single Register Read                                                                       |   |

| ADS7142_REG_CHANNEL_INPUT_CFG<                                                             |   |

|                                                                                            |   |

| ADS7142_VAL_CHANNEL_INPUT_CFG_2_CHANNEL_SINGLE_ENDED Setup Read to [0x31] + ACK            |   |

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

|                                                                                            |   |

| ADS7142_REG_OPMODE_SEL<br>0x1C + ACK                                                       |   |

| Device is to operate in Autonomous Monitoring Mode with AUTO Sequencing enabled 0x06 + ACK |   |

| Single Register Read Setup Write to [0x30] + ACK                                           |   |

| ADS7142 REG OPMODE SEL                                                                     |   |

|                                                                                            |   |

| ADS7142_VAL_OPMODE_SEL_AUTONOMOUS_MONITORING_MODE Setup Read to [0x31] + ACK               |   |

| Single Register Read Setup Write to [0x30] + ACK                                           |   |

|                                                                                            |   |

| ADS7142_REG_OPMODE_I2CMODE_STATUS                                                          |   |

| ADS7142_VAL_OPMODE_SEL_AUTONOMOUS_MONITORING_MODE Setup Read to [0x31] + ACK               |   |

| 0x02 + NAK                                                                                 |   |

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

| ADS7142_REG_AUTO_SEQ_CHEN                                                                  |   |

| ADS7142_VAL_AUTO_SEQ_CHENAUTO_SEQ_CH0_CH1                                                  |   |

|                                                                                            |   |

| Single Register Read                                                                       |   |

| ADS7142_REG_AUTO_SEQ_CHEN                                                                  |   |

| ADS7142_VAL_AUTO_SEQ_CHENAUTO_SEQ_CH0_CH1_ Setup Read to [0x31] + ACK                      |   |

| 0x03 + NAK                                                                                 |   |

| Single Register Write Setup Write to [0x30] + ACK                                          |   |

| ADS7142 REG OSC SEL                                                                        |   |

|                                                                                            |   |

|                                                                                            |   |

| Single Register Read                                                                       |   |

| ADS7142_REG_OSC_SEL                                                                        |   |

| ADS7142_VAL_OSC_SEL_HSZ_HSO Setup Read to [0x31] + ACK                                     |   |