# Phase Noise/Phase Jitter Performance of CDCM7005 at Various UMTS, CDMA-xx, and 802.16 Frequencies

Kal Mustafa/Firoj Kabir

Clock Drivers

### ABSTRACT

This application brief presents phase-noise data taken on Texas Instruments CDCM7005 jitter cleaner and synchronizer PLL. The phase noise performance of the CDCM7005 depends on the phase noise of the reference clock, VCXO clock, and the CDC7005 itself. This applications brief shows the phase noise performance of Texas Instruments clock synthesizer CDCM7005 at most popular UMTS, CDMA, and 802.16 frequencies. It helps the user in choosing the right clocking solution for their particular applications. These test results confirm that the CDCM7005 can provide clocks better than –145 dBc/Hz phase noises at 1-MHz offset from the carrier frequency. Low phase noise is required for most base station application such as UMTS, CDMAxx, and 802.16 and their derivatives as well as many other jitter stringent applications.

### Contents

| 1 | Introduction             | 2  |

|---|--------------------------|----|

| 2 | Test Equipment and Setup | 3  |

| 3 | Summary and Conclusion   | 16 |

| 4 | Acknowledgement          | 17 |

| 5 | References               | 17 |

### List of Figures

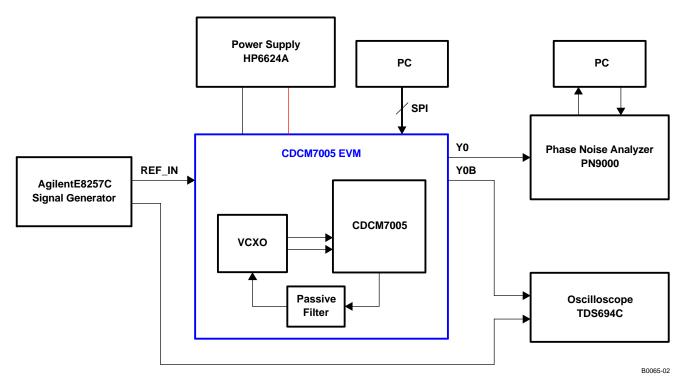

| 1  | Test Equipment Setup                                                     | 4  |

|----|--------------------------------------------------------------------------|----|

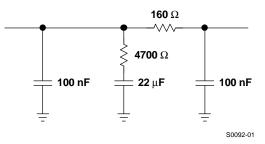

| 2  | Passive Loop Filter Circuit                                              | 4  |

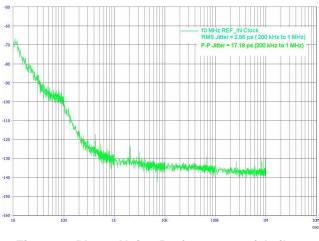

| 3  | Phase Noise Performance of Agilent E8257C 10MHz REF_IN                   | 4  |

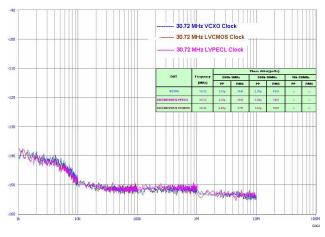

| 4  | Phase Noise Performance of CDCM7005 Outputs at 30.72 MHz                 | 4  |

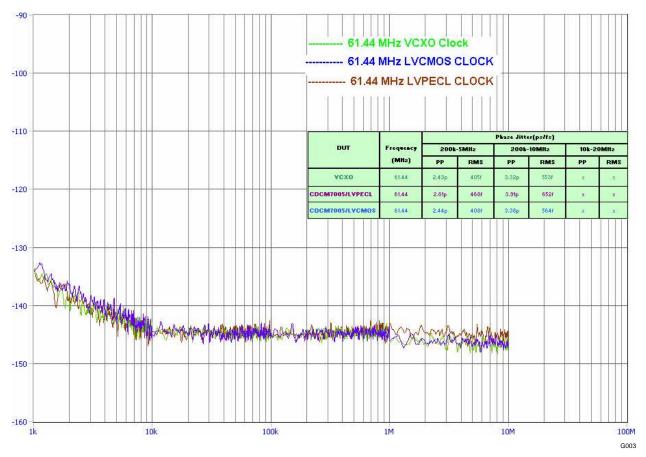

| 5  | Phase Noise Performance of CDCM7005 Outputs at 61.44 MHz                 | 5  |

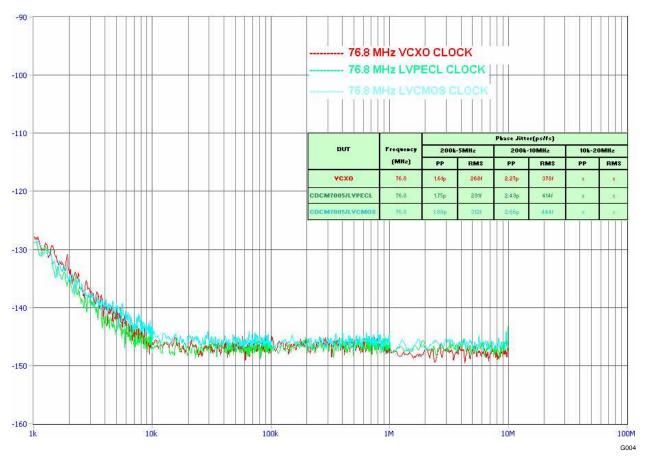

| 6  | Phase Noise Performance of CDCM7005 Outputs at 76.80 MHz                 | 6  |

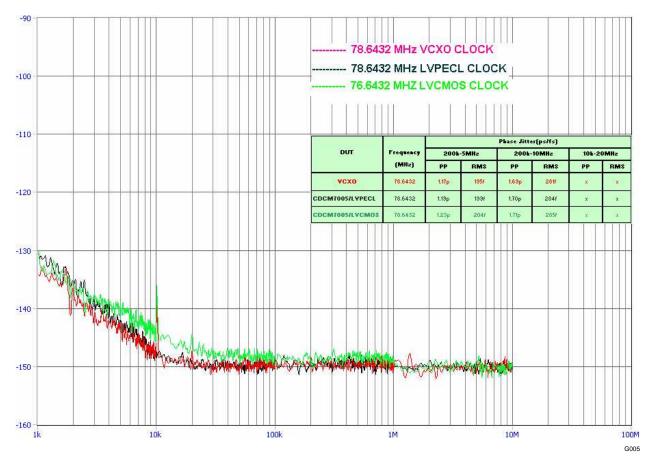

| 7  | Phase Noise Performance of CDCM7005 Outputs at 78.6432 MHz               | 7  |

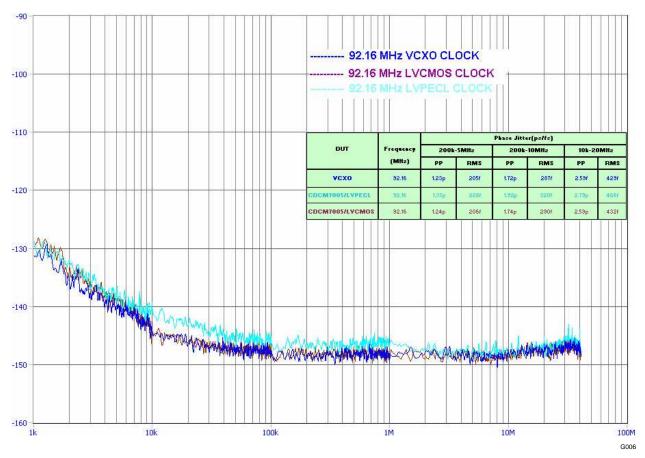

| 8  | Phase Noise Performance of CDCM7005 Outputs at 92.160 MHz                | 8  |

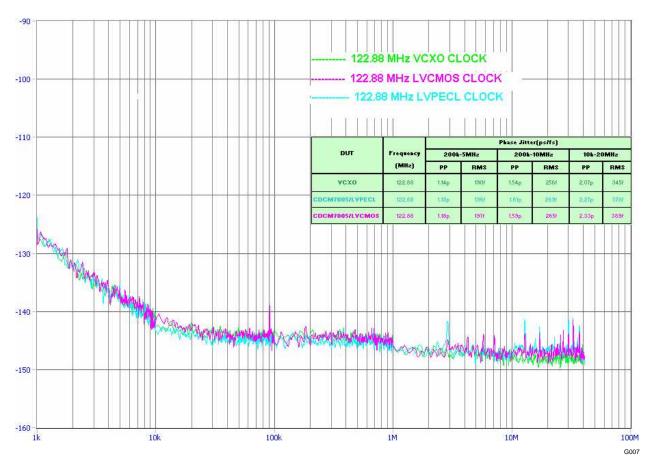

| 9  | Phase Noise Performance of CDCM7005 Outputs at 122.88 MHz                | 9  |

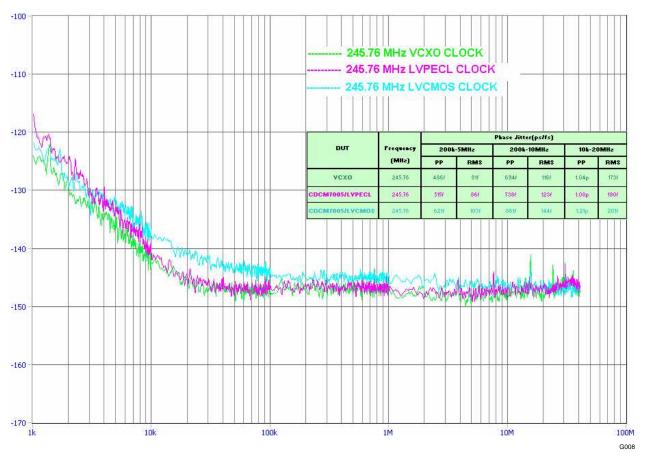

| 10 | Phase Noise Performance of CDCM7005 Outputs at 245.76 MHz                | 10 |

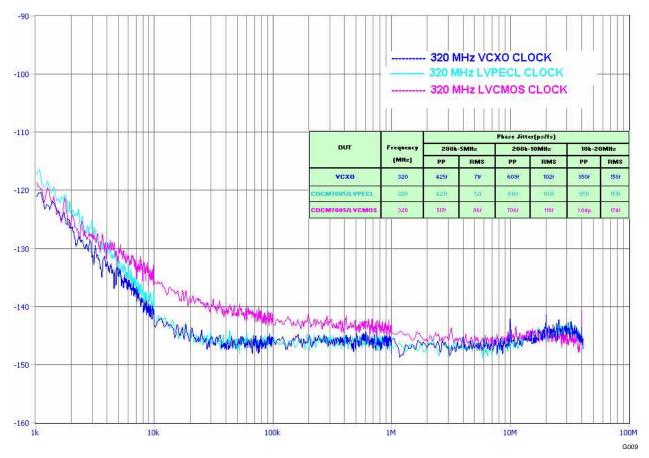

| 11 | Phase Noise Performance of CDCM7005 Outputs at 320 MHz                   | 11 |

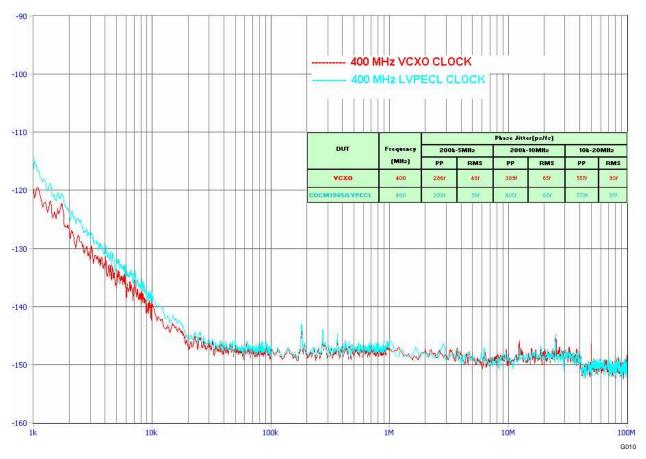

| 12 | Phase Noise Performance of CDCM7005 Outputs at 400 MHz                   | 12 |

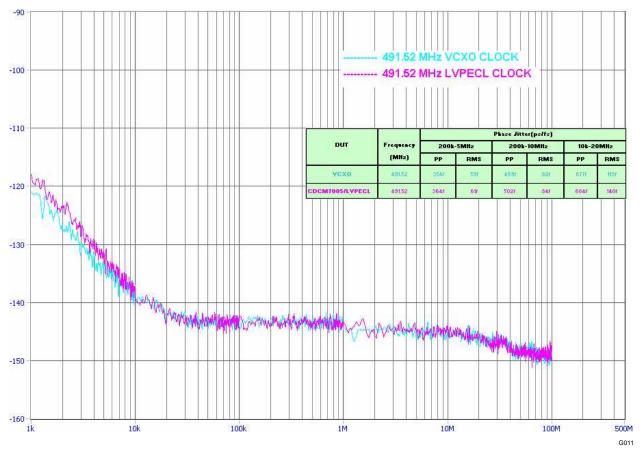

| 13 | Phase Noise Performance of CDCM7005 Outputs at 491.52 MHz                | 13 |

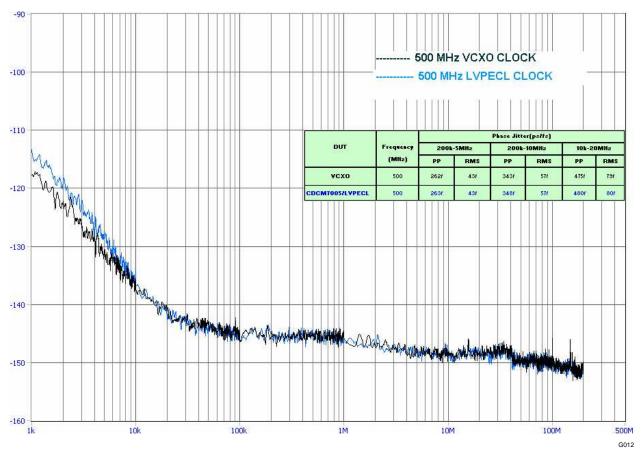

| 14 | Phase Noise Performance of CDCM7005 Outputs at 500 MHz                   | 14 |

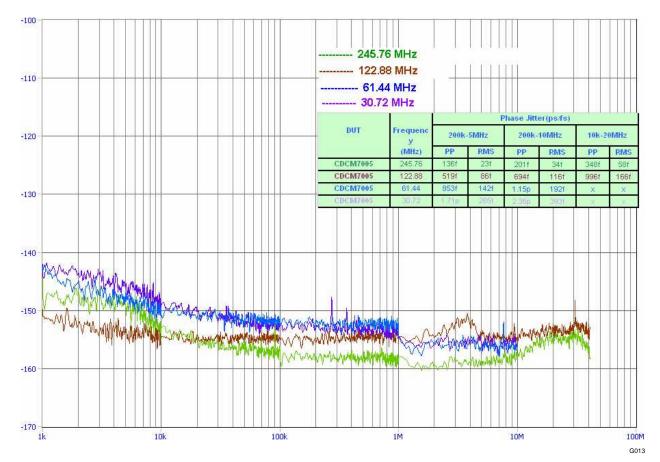

| 15 | Additive Phase Noise Performance of CDCM7005 LVPECL Output at 245.76 MHz |    |

|    | (Buffer Mode)                                                            | 15 |

|    |                                                                          |    |

### List of Tables

| 1 | Additive Phase Jitter (CDCM7005 Jitter Contribution Without REF and VCXO) | 15 |

|---|---------------------------------------------------------------------------|----|

| 2 | Summary of Phase Jitter Measurements Across Various Frequencies           | 15 |

# 1 Introduction

The CDCM7005 is a low phase noise/low jitter clock synthesizer and jitter cleaner with programmable LVPECL and LVCMOS outputs. An external low-pass loop filter in addition to an external VCXO (VCO) is required to complete the phase locked loop circuitry. Proper selection of the VCXO and loop bandwidth is critical to achieve the best performance from the CDCM7005. A loop bandwidth calculator is available on Texas Instruments website (www.ti.com).

This report includes phase noise plots of most common frequencies used in base station and customer premise equipment (CPE) applications. In addition, the phase noise of the clock source feeding the CDCM7005 is included for completeness.

The phase noise of the 10-MHz reference, the various Toyocom's VCXOs (TCO-2111), and output phase noise of the CDCM7005 are included. The peak-to-peak and the RMS jitter were calculated from the phase noise plots over a frequency band of interest using the PN9000 phase noise measurement system. In addition, additive phase jitter of the CDCM7005 is included. The jitter data is taken with a Toyocom's 245.76-MHz VCXO and a divided ratio of this frequency. This data illustrates the jitter performance of the CDCM7005 alone and precludes jitter contributions of external clock reference and the VCXO being used. Additive time/phase jitter plots are shown in Figure 13.

## 1.1 Definitions

2

**The timing budget** is defined by dynamic (jitter) and static errors (skew). Depending on the system architecture, a sub-set of parameters out of the data sheet is only affecting the timing budget. Jitter is a timing distribution of the clock signal and expresses the edge deviation from ideal. Jitter is composed of both deterministic and random (Gaussian) content.

**Jitter** is any edge deviation from the ideal. The causes of jitter include: power supply noise, thermal and mechanical noise from the input signal, reflection, EMI, and random noise. A few suggestions for reducing jitter include: power supply bypassing (10-47  $\mu$ F) to prevent voltage droop and ripple due to current surges, filtering each VCC pin (w/ 0.1  $\mu$ F) low effective series resistance capacitor, using proper termination, using differential signaling as opposed to single-ended signaling, and minimizing noise coupling by isolating other high frequency signals from the clock driver.

**Phase Noise (PN)** is the short-term instability caused by variation of frequency (phase) of a signal referenced to the carrier level and a function of the carrier offset (i.e., relative noise level within a 1-Hz bandwidth). Integration of PN over a given frequency band yields phase jitter RMS.

**Phase jitter or accumulated jitter** is the absolute deviation of a clock edge from its ideal position in timing. While period jitter only accounts for the variation between clock periods, phase jitter accumulates the error of each period and therefore is always larger. The wider the recording time window is, the more frequency bandwidth becomes integrated into the total phase jitter. Phase jitter can also be measured by integrating phase noise over the frequency band of interest. Either way, the system designer must specify the minimum and maximum frequency for the integration.

For set-up and hold-time budget calculation, the PP value of the phase jitter is important. Note that only the added phase noise by the clock driver is of interest to find the worse edge position between the master clock in the system and the subsystem. The absolute phase jitter of the master clock itself adds to all clock signals in the system, thus canceling its effect.

**Period jitter** is the deviation in cycle time of a signal with respect to an ideal period over a random sample of cycles. Period jitter is important since it includes the max/min frequency and it specifics the shortest clock period. It is important for the set-up and hold-time budget. Calculation with period jitter is sufficient for sub-systems using clock and data signals derived by the same clock source. Use phase jitter to calculate your jitter budget in case a signal comes into such subsystem from an external clock source (e.g., use of ADC, SerDes) or is generated from the clock source that feeds the clock buffer of interest. Period jitter can be measured with any oscilloscope. The trigger input and signal input both must be driven from the output of the clock driver.

**Peak-to-peak (PP) period jitter** is the total jitter range from minimum to maximum values of a clock signal. PP jitter increases indefinitely with recording time. Thus, PP jitter values are only meaningful if either the recording length or the relative bit error rate is known.

**RMS period jitter** is one standard deviation  $(1 \sigma)$  of the PP jitter of a clock signal. RMS jitter is only valid for Gaussian (normal) distribution. RMS jitter is independent of the sampling window, and thus, better suited to compare performance of two or more devices where sampling time window differs or is unknown.

**Cycle-to-cycle (CC) period jitter**, a.k.a. *adjacent cycle jitter*, is the variation in cycle time of a signal between consecutive cycles over a random sample of successive cycle pairs. CC jitter is also a good value to calculate the set-up and hold-time budget since it defines the min/max variation of the timing variation from ideal for the next clock edge.

**Crosstalk**, another name for parasitic coupling between signals, is the effect of capacitive coupling to cause a logic transition. Capacitive coupling is the transfer of energy between nearby switching integrated circuits. The coupling depends on factors such as the distance between the traces, the signal swing, the operating frequency, and the permittivity of the silicon dioxide. Coupling can be improved by physically increasing the distance between the traces. Power and ground planes can also act as shields to minimize crosstalk

# 1.2 ADC and SerDes System

When using the AD converter and SerDes transceiver, the incoming data is often sourced by a completely independent clock source and not synchronized to the main system clock (at least no short-term synchronization). Thus, the absolute phase jitter becomes important. A lower frequency band limit must be established (e.g., 12 kHz to full range). For the AD converter, the limit on the low side relates to the sampling window of the ADC that becomes further processed by digital algorithms (e.g. DSP tap size for a FFT). For a SerDes PLL, low phase jitter is critical around the PLL's bandwidth. Thus, jitter frequency has an upper and low limit (e.g., 12 kHz–20 MHz for OC-48).

# 2 Test Equipment and Setup

All measurements were taken at nominal 3.3-V power supply, room temperature, and PLL lock condition. The CDCM7005 evaluation module (EVM) in 1x mode, various Toyocom's VCXOs, the Agilent E8257C signal generator and the PN9000 phase noise test system. The below test setup were used for the all phase noise testing. The phase noise can be measured up to 100 MHz from carrier frequency. Although some measurements were taken up to 10 MHz or 1 MHz from the carrier depending upon the desired clock frequency.

The PN9000 automatic phase noise test system from Aeroflex was used to measure the phase noise and the phase jitter was calculated from phase noise plots at various bandwidths.

Several CDCM7005 EVMs was used to take the output phase noise measurement.

All LVPECL and LVCMOS outputs were properly terminated. Figure 1 shows the test setup used for all phase noise testing.

Figure 1. Test Equipment Setup

Figure 3. Phase Noise Performance of Agilent E8257C 10MHz REF\_IN

Figure 4. Phase Noise Performance of CDCM7005 Outputs at 30.72 MHz

Figure 5. Phase Noise Performance of CDCM7005 Outputs at 61.44 MHz

Figure 6. Phase Noise Performance of CDCM7005 Outputs at 76.80 MHz

Test Equipment and Setup

7

Figure 7. Phase Noise Performance of CDCM7005 Outputs at 78.6432 MHz

Figure 8. Phase Noise Performance of CDCM7005 Outputs at 92.160 MHz

Test Equipment and Setup

Figure 9. Phase Noise Performance of CDCM7005 Outputs at 122.88 MHz

9

Figure 10. Phase Noise Performance of CDCM7005 Outputs at 245.76 MHz

Test Equipment and Setup

Figure 11. Phase Noise Performance of CDCM7005 Outputs at 320 MHz

Figure 12. Phase Noise Performance of CDCM7005 Outputs at 400 MHz

Figure 13. Phase Noise Performance of CDCM7005 Outputs at 491.52 MHz

Figure 14. Phase Noise Performance of CDCM7005 Outputs at 500 MHz

Figure 15. Additive Phase Noise Performance of CDCM7005 LVPECL Output at 245.76 MHz (Buffer Mode)

| DUT      | FREQUENCY<br>(MHz) | PHASE JITTER (ps/fs) |     |                  |     |                 |     |

|----------|--------------------|----------------------|-----|------------------|-----|-----------------|-----|

|          |                    | 200 kHz – 5 MHz      |     | 200 kHz – 10 MHz |     | 10 kHz – 20 MHz |     |

|          |                    | PP                   | RMS | PP               | RMS | PP              | RMS |

| CDCM7005 | 245.76             | 136                  | 23  | 201              | 34  | 348             | 58  |

| CDCM7005 | 122.88             | 519                  | 86  | 694              | 116 | 996             | 166 |

| CDCM7005 | 61.44              | 853                  | 142 | 1.15p            | 192 | х               | х   |

| CDCM7005 | 30.72              | 1.71p                | 285 | 2.36p            | 393 | х               | х   |

Table 1. Additive Phase Jitter (CDCM7005 Jitter Contribution Without REF and VCXO)

| DUT                    | FREQUENCY<br>(MHz) | PHASE JITTER (ps/fs)  |                      |                  |     |                 |     |

|------------------------|--------------------|-----------------------|----------------------|------------------|-----|-----------------|-----|

|                        |                    | 200 kHz – 5 MHz       |                      | 200 kHz – 10 MHz |     | 10 kHz – 20 MHz |     |

|                        |                    | PP                    | RMS                  | PP               | RMS | PP              | RMS |

| Agilent E8257C Sig Gen | 10                 | 17.18p <sup>(1)</sup> | 2.68p <sup>(1)</sup> | х                | х   | х               | х   |

| VCXO                   | 30.72              | 2.19p                 | 364                  | 2.95p            | 492 | x               | x   |

| CDCM7005/LVPECL        | 30.72              | 2.21p                 | 368                  | 3.04p            | 546 | х               | х   |

| CDCM7005/LVCMOS        | 30.72              | 2.26p                 | 377                  | 3.12p            | 520 | х               | х   |

<sup>(1)</sup> This data is taken from 200 kHz to 1 MHz.

| DUT             | FREQUENCY | PHASE JITTER (ps/fs) |     |                  |     |                 |     |

|-----------------|-----------|----------------------|-----|------------------|-----|-----------------|-----|

|                 | (MHz)     | 200 kHz – 5 MHz      |     | 200 kHz – 10 MHz |     | 10 kHz – 20 MHz |     |

|                 |           | PP                   | RMS | PP               | RMS | PP              | RMS |

| VCXO            | 61.44     | 2.43p                | 405 | 3.32p            | 553 | x               | х   |

| CDCM7005/LVPECL | 61.44     | 2.81p                | 468 | 3.91p            | 652 | х               | х   |

| CDCM7005/LVCMOS | 61.44     | 2.44p                | 408 | 3.38p            | 564 | х               | х   |

| VCXO            | 76.8      | 1.61p                | 268 | 2.27p            | 378 | x               | х   |

| CDCM7005/LVPECL | 76.8      | 1.75p                | 291 | 2.49p            | 414 | х               | х   |

| CDCM7005/LVCMOS | 76.8      | 1.88p                | 312 | 2.66p            | 444 | х               | х   |

| VCXO            | 78.6432   | 1.17p                | 195 | 1.69p            | 281 | x               | х   |

| CDCM7005/LVPECL | 78.6432   | 1.19p                | 199 | 1.70p            | 284 | х               | х   |

| CDCM7005/LVCMOS | 78.6432   | 1.23p                | 204 | 1.71p            | 285 | х               | х   |

| VCXO            | 92.16     | 1.23p                | 205 | 1.72p            | 287 | 2.59p           | 429 |

| CDCM7005/LVPECL | 92.16     | 1.37p                | 228 | 1.92p            | 320 | 2.79p           | 466 |

| CDCM7005/LVCMOS | 92.16     | 1.24p                | 206 | 1.74p            | 290 | 2.59p           | 432 |

| VCXO            | 122.88    | 1.14p                | 190 | 1.54p            | 256 | 2.07p           | 345 |

| CDCM7005/LVPECL | 122.88    | 1.18p                | 196 | 1.61p            | 269 | 2.27p           | 378 |

| CDCM7005/LVCMOS | 122.88    | 1.18p                | 197 | 1.59p            | 265 | 2.33p           | 389 |

| VCXO            | 245.76    | 486                  | 81  | 694              | 116 | 1.04p           | 173 |

| CDCM7005/LVPECL | 245.76    | 515                  | 86  | 738              | 123 | 1.08p           | 180 |

| CDCM7005/LVCMOS | 245.76    | 621                  | 103 | 861              | 144 | 1.21p           | 201 |

| VCXO            | 320       | 425                  | 71  | 609              | 102 | 950             | 158 |

| CDCM7005/LVPECL | 320       | 428                  | 71  | 616              | 103 | 951             | 159 |

| CDCM7005/LVCMOS | 320       | 517                  | 86  | 706              | 117 | 1.04p           | 174 |

| VCXO            | 400       | 286                  | 48  | 389              | 65  | 557             | 93  |

| CDCM7005/LVPECL | 400       | 298                  | 50  | 405              | 68  | 579             | 97  |

| VCXO            | 491.52    | 354                  | 59  | 489              | 82  | 677             | 113 |

| CDCM7005/LVPECL | 491.52    | 364                  | 61  | 502              | 84  | 684             | 140 |

| VCXO            | 500       | 262                  | 43  | 343              | 57  | 475             | 79  |

| CDCM7005/LVPECL | 500       | 263                  | 43  | 348              | 57  | 480             | 80  |

|                 |           |                      |     |                  |     |                 |     |

### Table 2. Summary of Phase Jitter Measurements Across Various Frequencies (continued)

# 3 Summary and Conclusion

The CDC7005 PLL tracks the input reference signal up to the loop bandwidth, while it follows the VCO (here VCXO) phase noise floor at frequencies above the loop bandwidth. The VCXO performance is critical for achieving good PLL's phase noise performance and meeting stringent requirements in base station applications. From the above data it is evident that a low phase noise clock output is easily attainable from the CDCM7005 with the proper selection of VCXO. These test results confirm that the CDCM7005 can provide clocks better than –145-dBc/Hz phase noises at 1-MHz offset from the carrier frequency. Low phase noise is required for most base station applications such as UMTS, CDMAxx, and 802.16 and their derivatives as well as many other jitter stringent applications.

The additive phase-noise data clearly indicates that as a buffer, the CDCM7005 adds a few femto-second jitter to its input. The added jitter number may vary over frequency. For more information about the CDCM7005, see the device data sheet.

# 4 Acknowledgement

The authors of this application brief would like to thank the following people for proving the necessary samples and equipments in conducting these tests:

- 1. Treisch, Ron, Texas Instruments, RF Wireless Group, r-treisch@ti.com

- 2. Paul Woodley, O&M Sales, Inc., Paul, Woodley@o-m-sales.com

- 3. Kory Moser, Toyocom USA, <u>moser@toyocom.com</u>

- 4. Heather McClendon, Texas Instruments, heather.mcclendon@ti.com

# 5 References

- 1. CDCM7005 data sheet, Texas Instruments, (SCAS685)

- 2. CDC7005 EVM User's Guide, Texas Instruments, (SCAU005)

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated