# EMC Improvement Guide for MSPM0

#### Eason Zhou

#### **ABSTRACT**

This application note outlines key EMC principles, compliance standards, and design optimization strategies for MSPM0 microcontrollers. The document provides practical guidance to troubleshoot EMS issues and enhance electromagnetic performance in MSPM0-based systems, while addressing international certification requirements through effective noise suppression and emission control techniques.

# **Table of Contents**

| 1 Introduction                              |    |

|---------------------------------------------|----|

| 2 EMC and EMC Standards                     | 3  |

| 2.1 EMC                                     |    |

| 2.2 EMC Standards                           | 3  |

| 2.3 EMC and IC Electrical Reliability in TI |    |

| 3 EMC Improvement Guidelines Summary        |    |

| 3.1 PCB Design Guidelines                   | 7  |

| 3.2 Firmware Guidelines                     |    |

| 4 EMC Improvement Features on MSPM0         |    |

| 4.1 Susceptibility Protection Features      | 10 |

| 4.2 Emission Reduction Features             |    |

| 5 Analysis for EMS Test                     | 16 |

| 5.1 Root Cause Analysis                     |    |

| 5.2 Debug Flow                              | 19 |

| 6 Analysis for EMI Test                     | 21 |

| 6.1 Root Cause Analysis                     |    |

| 6.2 Debug Flow                              |    |

| 7 Summary                                   |    |

| 8 References                                |    |

| 9 Revision History                          | 26 |

## **Trademarks**

Cortex® is a registered trademark of Arm Limited.

All trademarks are the property of their respective owners.

Introduction www.ti.com

# 1 Introduction

This document presents an overview of Electromagnetic Compatibility (EMC) principles, standards, and implementation strategies for MSPM0 microcontrollers. Most of the content is provided in the checklist format.

Before product development with MSPM0, TI recommends to read these sections to have a better understanding to improve EMC in MSPM0-based systems from both software and hardware level.

- Section 2

- Section 3

- Section 4

When there is failure in EMC test, TI recommends to read these sections below to find the root cause and resolutions.

- Section 5

- Section 6

www.ti.com EMC and EMC Standards

## 2 EMC and EMC Standards

#### 2.1 EMC

Electromagnetic Compatibility (EMC) is a critical discipline in electronics engineering that verifies devices or systems to operate as intended within the electromagnetic environment without causing harmful interference to other devices (EMI) or being adversely affected by external electromagnetic disturbances (EMS). Thus, EMC encompasses two complementary aspects: Electromagnetic Interference (EMI) and Electromagnetic Susceptibility (EMS).

#### 2.1.1 EMS

EMS (also called immunity) describes the ability of the device to function correctly when exposed to external electromagnetic disturbances. This measures resilience to:

- Radiated immunity: resistance to electromagnetic fields (for example, from radio transmitters).

- Conducted immunity: resistance to noise injected into power or signal lines (for example, voltage surges or electrostatic discharge).

#### 2.1.2 EMI

EMI refers to unintentional electromagnetic energy emitted by a device or system that can disrupt the operation of nearby electronics. This is often categorized into two types:

- Radiated emissions: electromagnetic waves transmitted through the air (for example, radio frequency interference from a smartphone).

- Conducted emissions: noise propagated through power lines or cables (for example, harmonics from a motor affecting a power grid).

### 2.2 EMC Standards

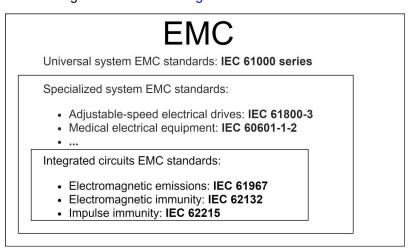

Based on the EMC compliance requirement from different application scenarios, numerous EMC standards are established by international, regional, or industry bodies to define acceptable limits and testing methodologies for electromagnetic emissions and immunity. The most common communities are International Organization for Standardization (ISO), the International Electrotechnical Commission (IEC) and International Special Committee on Radio Interference (CISPR). Although there any many standard creators, the standard coverage can be listed into three key EMC standard categories as shown in Figure 2-1.

Figure 2-1. EMC Standards

The First EMC standard category is the universal system EMC standard, which describes the EMC test standards good for general products or PCB systems and sets minimum EMC performance metrics. An example is IEC 61000 series released by IEC. As IEC 61000 is the most common EMC standard, a more detailed introduction is given to the spread standards in the Section 2.2.1.

EMC and EMC Standards www.ti.com

The second category is the specialized system EMC standards. To complement general requirements, some application-specific (for example, automotive, medical, aerospace) EMC standards are also developed to address unique EMC challenges, especially for EMI.

The third category is ICs EMC standards. Within the IEC framework, there are three core standards: IEC 61967, IEC 62132, and IEC 62215. These tests use standardized setups (for example, 100mm×100mm multilayer PCBs with predefined code) to evaluate IC behavior under controlled test environment. However, this dependency on system variables renders cross-IC comparisons statistically inconclusive, as differences in setup parameters (for example, PCB layer count, decoupling capacitor placement, or signal routing) can artificially amplify or mask intrinsic IC characteristics. As a result, this test data is provided by few semiconductor companies.

# 2.2.1 EMC Standards Category

The following section shows the EMC test coverage based on different EMC standards created by these organizations. First, use the IEC 610000 series as an example to show what EMS testing covers.

Table 2-1. EMS (Immunity) Testing Standards Overview

| Test Type                | Standard      | Purpose                                                                                | Test Method                                                                                                             | Application Scope                              |

|--------------------------|---------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| ESD Immunity             | IEC 61000-4-2 | Evaluate immunity to electrostatic discharges from human/machine contact.              | Contact discharge (approximately 2kV-8kV); air discharge (approximately 2kV-15kV). Use an ESD Gun.                      | Consumer electronics, industrial equipment.    |

| EFT/Burst<br>Immunity    | IEC 61000-4-4 | Test immunity to fast transient disturbances (for example, relay switching).           | Approximately 50ns pulse bursts (0.5kV to 4kV, 5kHz repetition). Coupled to power or signal lines by capacitive clamp.  | Power supplies, motor drives, control systems. |

| Surge Immunity           | IEC 61000-4-5 | Assess immunity to high-<br>energy surges (for example,<br>lightning, load switching). | Approximately 50µs voltage surge (line-to-line or line-to-ground, 0.5kV to 4kV). Coupled via CDN or gas discharge tube. | Telecom systems, grid-<br>connected devices.   |

| Radiated RF<br>Immunity  | IEC 61000-4-3 | Test immunity to radiated RF fields (for example, radio transmitters).                 | RF signals (80MHz–6GHz) with a uniform field area (3V/m–30V/m). Radiated by antenna at 3m distances.                    | Wireless devices, automotive electronics.      |

| Conducted RF<br>Immunity | IEC 61000-4-6 | Evaluates immunity to RF interference coupled via cables/power lines.                  | RF signals (150kHz–80MHz) with modulation (80% AM at 1kHz). Injected via CDN or current clamp.                          | Medical devices, industrial automation.        |

Here are some EMI test standards listed to show what EMI testing covers. Compared with EMS, for EMI, the test standards and protection level is related to application.

Table 2-2. EMI (Electromagnetic Interference) Testing Standards Overview

| Test Type             | Standard    | Purpose                                                  | Test Method                                                                                     | Application Scope                                |

|-----------------------|-------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Radiated<br>Emission  | CISPR 25    | Evaluates radiated emissions from automotive electronics | RF signals (30MHz–1GHz). Conducted in an anechoic chamber with antennas at 1m/3m/10m distances. | In-vehicle systems.                              |

| Conducted<br>Emission | CISPR 22/32 | Tests conducted emissions on power/signal lines.         | RF signals (150kHz–30MHz).     Uses LISN to measure quasi-peak and average values.              | Power adapters, industrial frequency converters. |

www.ti.com EMC and EMC Standards

# 2.3 EMC and IC Electrical Reliability in TI

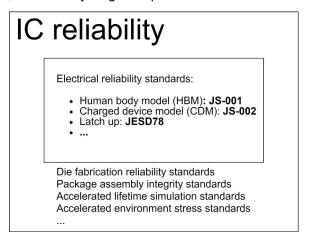

IC electrical reliability is a part of the IC reliability. The related standards are HBM, CBM and latch up, which are released by JEDEC and ESDA, aim to verify long-term performance under stress.

Figure 2-2. IC Reliability Standards

Some users confuse reliability with EMC, especially on ESD ratings. For IC electrical reliability, the related standards are JS-001 (HBM) and JS-002 (CBM). For EMC, the related standards are IEC 61000-4-2 and IEC 61967. These standards belong to two different standard categories. Table 2-3 gives an overview about the differences between EMC and IC electrical reliability.

Table 2-3. EMC and Electrical Reliability Comparison

| Table 2-3. Livio and Electrical Reliability Companison |                                                                                                                            |                                                                                                                                   |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Aspect                                                 | IC EMC Testing                                                                                                             | IC Electrical Reliability Testing                                                                                                 |  |  |

| Primary objective                                      | Check the electromagnetic compatibility of a system under an electrical environment.                                       | Verifies long-term stability and lifespan of ICs under electrical stress, preventing performance degradation or physical failure. |  |  |

| Noise injection                                        | The IC-based system                                                                                                        | IC                                                                                                                                |  |  |

| Test focus and example                                 | System-level electromagnetic interactions.  Example - ESD immunity: Validate system recovery from ESD events during usage. | IC endurance for electrical stress.  Example - HBM, CBM: Tests IC tolerance to ESD events during manufacturing and assembly.      |  |  |

| Optimization                                           | Yes. Improved with HW/SW co-design.                                                                                        | No. Require IC redesign or silicon revisions.                                                                                     |  |  |

| SW Dependency                                          | Yes. Firmware-dependent.                                                                                                   | No                                                                                                                                |  |  |

| Failure impact                                         | System-level malfunctions                                                                                                  | Irreversible chip-level damage                                                                                                    |  |  |

In the IC design flow, the primary focus is on verifying reliability through methodologies that address physical degradation, manufacturing variability, and operational stresses. While EMC is not a direct consideration in traditional IC design frameworks, the scope is an IC-based system and not purely the IC. However, on-chip components like ESD structures can still provide foundational support for EMC improvements. For the related EMC improvement features on MSPM0, refer to Section 4.

For EMC testing, TI provides an EU Declaration of Conformity for every EVM with limited ICs on board, which shows these EVM boards can meet the EN61326-1:2013 requirement. Here is an example: LP-MSPM0G3507 EU RoHS Declaration of Conformity (DoC). For IC Reliability testing, TI provide qualifications for every orderable part number devices. Under Qualification Summary, users can find data for every typical IC part number as shown in Figure 2-3.

# Qualification summary

By using this tool to "Search" or "Download", you agree to TI's Terms of use, Privacy policy (including For more information visit Qualification summary FAQ.

Enter a TI part number

M0G3505QPMRQ1

Qualification summary for: M0G3505QPMRQ1

ACTIVE Report date: 03/18/2025

TI reference number: 0

Figure 2-3. IC Reliability Entrance

For more about IC electrical reliability, refer to the Latch-Up, ESD, and Other Phenomena application report and Latch-Up white paper.

# 3 EMC Improvement Guidelines Summary

In this section, the guidelines are summarized for a quick check to help improve EMC in MSPM0-based systems at both software and hardware level. Detailed descriptions and analysis are described later in the document.

# 3.1 PCB Design Guidelines

PCB optimization is a key part for EMC improvement. The suggestions for optimization are presented as a check list format. All these suggestions are valid for both EMI and EMS.

Table 3-1. PCB Design Guidelines

| Item       | Suggestions Category      | Suggestions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

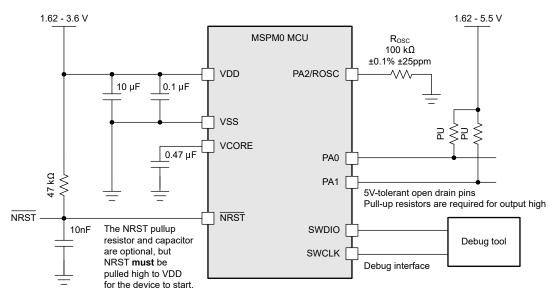

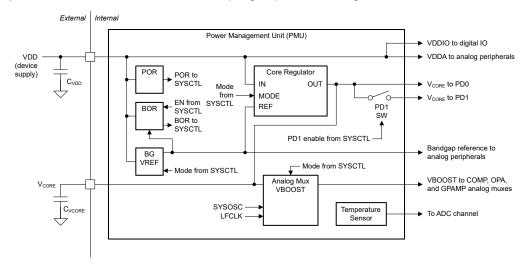

| Schematic  | MSPM0 minimum system      | Follow the guidance in the <i>Schematic</i> section of the data sheet to add resistors and capacitors on power supply, Vcore and Reset. An example is shown in Figure 3-1.                                                                                                                                                                                                                                                                                                                                                                       |

| Design     | EMC protection components | Add EMC protection components shown in Table 3-2 at I/O ports and power inputs for more robust protection                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            | Power                     | <ul> <li>Place decoupling capacitors to be closed to the MCU and the 100pF capacitor is closest.</li> <li>VDD line goes into the MCU by following this sequence: branch point-&gt;bypass capacitors-&gt; MCU</li> </ul>                                                                                                                                                                                                                                                                                                                          |

| PCB Layout | Ground                    | <ul> <li>Implement star grounding for mixed-signal systems</li> <li>Use continuous ground planes (avoid splits under high-speed traces)</li> <li>Add ground-filled zones in unused board areas</li> <li>Add a solid GND under the MCU to reduce radiative noise</li> <li>Place the GND pattern around the PCB perimeter and do not run the power supply (VDD) or signal lines</li> <li>The power supply and GND pattern corners need to be 45 degrees or curved</li> <li>Ground pins must be evenly distributed across all connectors</li> </ul> |

|            | Oscillator                | <ul> <li>Reduce external oscillator loop to MCU GND pin</li> <li>Surrounding oscillator wiring with a GND pattern</li> <li>Separate the Oscillator GND and PCB GND to reduce radiative noise</li> </ul>                                                                                                                                                                                                                                                                                                                                          |

|            | General signals           | <ul> <li>Reduce trace lengths/loop areas (critical for clock and high-speed signals)</li> <li>Signals must be curved at 45 degrees</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

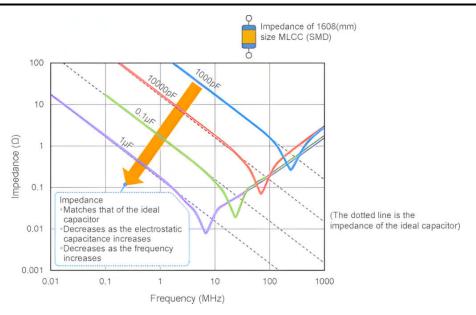

Table 3-2 are the common used passive protection components to improve the EMC. If users want to have a deep understanding for the influence of passive protection components and PCB design on EMC improvement, then the Noise Suppression Basic Course provided by Murata is a good learning resource.

**Table 3-2. Passive Protection Components**

| Table 3-2. Passive Protection Components |                |                                                        |                                                     |                                                         |                                                        |

|------------------------------------------|----------------|--------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| Category                                 | MC<br>Category | When to Use                                            | Key Advantages                                      | Critical Parameters                                     | Design Tips                                            |

| Resistor<br>(Series)                     | EMS, EMI       | High-frequency circuits requiring current control      | Limits spikes, absorbs EMI, low inductance          | Resistance value,<br>parasitic inductance (<1<br>nH)    | Use metal film; avoid carbon composition               |

| Clamping<br>Diodes                       | EMS            | ESD-sensitive high-<br>speed interfaces (USB,<br>HDMI) | Ultra-fast response (< 1ns), low clamping voltage   | Clamping voltage,<br>peak pulse current,<br>capacitance | Place near protected IC;<br>pair with series resistors |

| Capacitor                                | EMS, EMI       | Noise filtering or energy buffering                    | Ceramic (high-frequency), electrolytic (bulk)       | SRF, voltage rating, capacitance                        | Match SRF to noise; avoid overlapping SRFs             |

| TVS Diode                                | EMS            | High-energy surges<br>(lightning, inductive<br>loads)  | Ultra-fast clamping (< 1ps),<br>handles 10kA surges | Reverse standoff voltage, clamping voltage              | Standoff voltage > operating voltage by 20%            |

| Ferrite Bead                             | ЕМІ            | GHz-range noise on power or data lines                 | Frequency-specific attenuation, no DC loss          | Impedance at target frequency, DCR                      | Check impedance under DC bias                          |

| Category                | MC<br>Category | When to Use                                        | Key Advantages                                    | Critical Parameters                                     | Design Tips                                        |

|-------------------------|----------------|----------------------------------------------------|---------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|

| Common-Mode<br>Choke    | EMS/EMI        | Common-mode noise in differential lines (CAN, USB) | Blocks noise without signal distortion            | Impedance (for example, 600Ω at 100MHz), current rating | Balance winding inductance; minimize parasitics    |

| EMI Filter<br>(LC/Pi/T) | EMS/EMI        | Broadband noise in power/signal lines              | Multistage topology (Pi/T for high/low impedance) | Cutoff frequency, insertion loss                        | Pi-filter for power lines;<br>T-filter for signals |

| Gas Discharge<br>Tube   | EMS            | Extreme surges (telecom, lightning)                | Handles 20kA surges, low capacitance, durable     | Breakdown voltage, response time                        | Pair with TVS diodes for multi-stage protection    |

Here is an example of MSPM0 schematic design. For more description, refer to the data sheet of the specific MSPM0.

Figure 3-1. Basic Application Schematic of MSPM0G

# 3.2 Firmware Guidelines

Here are the MSPM0 related software configuration guidelines.

Table 3-3. MSPM0 Configuration Guidelines

| Table of the forming and a confidence of the con |              |                                                                                                |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------|--|

| Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EMS Coverage | Suggestions                                                                                    |  |

| BOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | Select higher BOR level if needed for data saving.                                             |  |

| I/O Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EMS          | Keep I/O setting to be default or output low. Need more protection for open-drain IOs if used. |  |

| Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | Control the usage of clock.                                                                    |  |

| Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EMI          | Choose a valid power mode when running MCU.                                                    |  |

| Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | Choose the smaller and thinner package.                                                        |  |

Here are the common firmware guidelines to improved EMS performance, which are also covered by applicable standards.

**Table 3-4. Common Firmware Guidelines**

| Technique                 | Key Implementation                                                                       | Applicable Standards            | Standard Requirements                                                                       |

|---------------------------|------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|

| Watchdog and time control | Use independent or window watchdogs; refresh in main loop                                | IEC 60730, ISO 26262, IEC 61508 | Mandate watchdog usage for fault detection and system recovery. ASIL D requires redundancy. |

| Securing unused memory    | Fill unused Flash or SRAM with valid instructions (for example, fault-handling routines) | IEC 60730, ISO 26262            | Require program counter integrity checks and software robustness.                           |

**Table 3-4. Common Firmware Guidelines (continued)**

| Technique                         | Key Implementation                                              | Applicable Standards | Standard Requirements                                                               |

|-----------------------------------|-----------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------|

| Input filtering and comparison    | Multistage checks with averaging or debouncing                  | IEC 60730            | Emphasize noise filtering for sensor reliability and input validation.              |

| Unused interrupt management       | Redirect unused interrupt vectors to a safe-state handler       | IEC 61508, IEC 60730 | Makes sure of controlled system states by handling all interrupt sources.           |

| ADC averaging                     | Multiple conversions with outlier rejection                     | IEC 60730, ISO 26262 | Requires periodic ADC self-tests and redundancy for critical data.                  |

| Register reprogramming and checks | Periodic reconfiguration and verification of critical registers | IEC 61508, IEC 60730 | Mandates cyclic self-tests for configuration integrity.                             |

| Redundant data storage            | Dual storage with CRC, ECC; hash validation                     | IEC 60730, ISO 26262 | Requires fault tolerance by redundancy;<br>ASIL D enforces dual-channel redundancy. |

# 4 EMC Improvement Features on MSPM0

The MSPM0 internal features are described in this section, which can be used to improve performance in EMC tests. If some features are not configured appropriately, then the features reduce the EMC performance.

## 4.1 Susceptibility Protection Features

In this section, the MSPM0 internal features protect MSPM0 against electromagnetic interference and are shown in Table 4-1.

| Table 4-1. Susceptibility Protection Features Summary |            |                                                                                                 |  |

|-------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------|--|

| Features                                              | Adjustable | Suggestions                                                                                     |  |

| POR                                                   | No         | N/A                                                                                             |  |

| BOR                                                   | Yes        | Select higher BOR level if needed for data saving.                                              |  |

| I/O ESD                                               | No         | N/A                                                                                             |  |

| I/O Settings                                          |            | Keep I/O setting to be default or output low.  Need more protection for Open-drain IOs if used. |  |

Table 4-1. Susceptibility Protection Features Summary

#### 4.1.1 POR and BOR

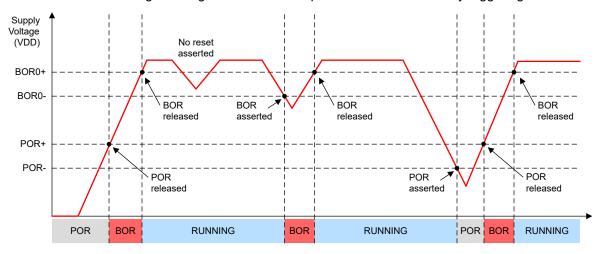

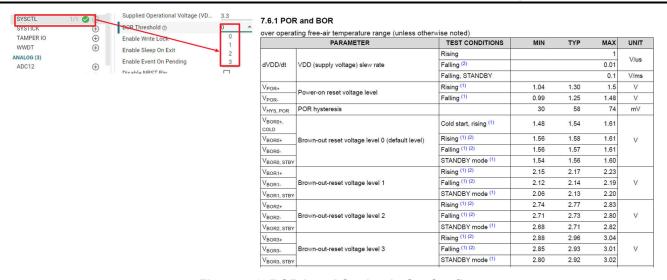

A power-on reset (POR) circuit indicates that the external supply has reached sufficient voltage to start the on-chip bandgap reference and BOR circuit. A user-programmable brownout reset (BOR) circuit makes sure that the external supply is maintained at a sufficient voltage to support correct operation of the device. In terms of EMS, the presence of the POR and BOR makes the MCU more robust. This also makes sure that if any outside disturbance affects the power supply, then the application can recover safely.

When the supply voltage (VDD) drops below POR-, the entire device state is cleared. Small variations in VDD that do not pass below the BOR0- threshold do not cause a BOR- violation, and the device continues to run. Behavior for BORx thresholds other than BOR0 (for example, BOR1-BOR3) is the same as shown for BOR0, except the BOR circuit is configured to generate an interrupt rather than immediately triggering a BOR reset.

Figure 4-1. POR, BOR vs. Supply Voltage (VDD)

There are four selectable BOR threshold levels (BOR0-BOR3). During startup, the BOR threshold is always BOR0. After booting up, the software can reconfigure the BOR to use a higher threshold level (BOR1-BOR3). When the BOR threshold is BOR0, the violation generates a BOR reset. When the BOR threshold is reconfigured to BOR1, BOR2, or BOR3, the BOR generates a SYSCTL interrupt instead. This can be used to give the application an early warning that the supply has dropped below a certain level. Users can save the data and choose to reset the device in the interrupt service routine. To enable this functions, follow the instructions in Figure 4-2.

Figure 4-2. BOR Level Setting in SysConfig

#### 4.1.2 NMI and Hard Fault

MSPM0 has two interrupt mechanisms to handle unexpected behaviors from the MCUs, which are useful to analyze the root cause of EMS failure. The first is NMI, which is designed to handle critical system events that require immediate attention. The second is hard fault, which is a nonmaskable exception triggered by severe system errors that cannot be handled by other exception mechanisms.

When NMI happens, users can track the trigger sources by checking the NMI interrupt index and find a valid resolution. An example is shown in Table 4-2.

| Table 4 E. Mor Moo Normaskable Interrupt Event |                               |                                                                                                                                                                                                    |  |  |  |

|------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Index (IIDX)                                   | Index (IIDX) Name Description |                                                                                                                                                                                                    |  |  |  |

| 0                                              | NONE                          | No NMI pending.                                                                                                                                                                                    |  |  |  |

| 1                                              | BORLVL                        | dicates that VDD has dropped below the specified VBOR- threshold.                                                                                                                                  |  |  |  |

| 2                                              | WWDT0                         | A WWDT0 violation occurred.                                                                                                                                                                        |  |  |  |

| 3                                              | WWDT1                         | A WWDT1 violation occurred.                                                                                                                                                                        |  |  |  |

| 4                                              | LFCLKFAIL                     | Indicates that the LFXT or LFCLK_IN clock source is dead. This indication is useful for handling LFCLK errors when LFCLK is not sourcing MCLK but is sourcing a peripheral (for example, the RTC). |  |  |  |

| 5                                              | FLASHDED                      | Indicates that a flash memory double-bit uncorrectable error was detected.                                                                                                                         |  |  |  |

| 6                                              | SRAMDED                       | Indicates that an SRAM double-bit uncorrectable error was detected.                                                                                                                                |  |  |  |

Table 4-2, MSPM0G Nonmaskable Interrupt Event

Hard fault serves as a last-resort handler for unrecoverable faults, such as memory access errors, unaligned memory operations, execution of undefined or illegal instructions and bus errors. Unlike higher-end Cortex®-M cores (for example, M3 and M4), the M0+ lacks configurable fault status registers (CFSR), making fault analysis more challenging and reliant on manual inspection. Hard fault generate a hard fault interrupt. Users can use this as an assert signal to adjust the system to pass the EMS test.

## 4.1.3 I/O ESD and Settings

Microcontroller input and output circuitry has been designed to take ESD and latch-up problems into account. However, self-protection is limited, especially when exposed to illegal voltages and high-current injections in EMS tests. TI strongly recommends to implement additional hardware protection if the features below do not work or the IO configuration cannot be satisfied.

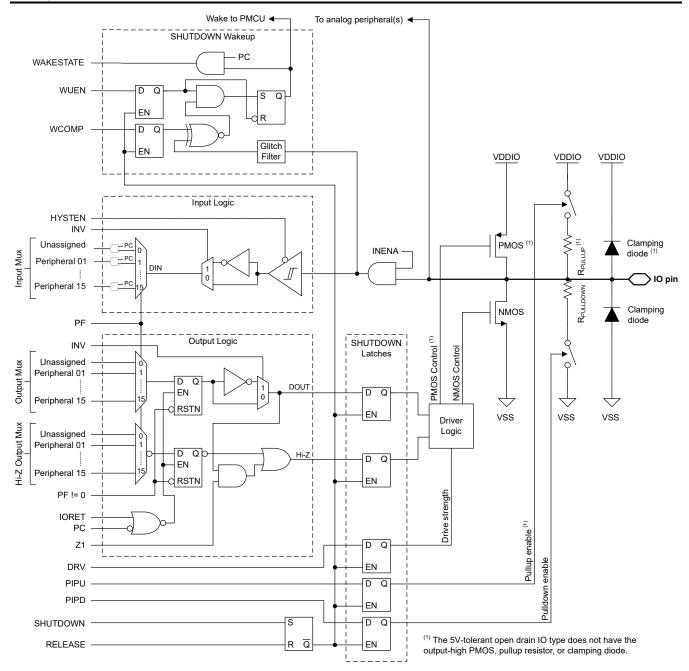

Figure 4-3 shows the I/O structure in MSPM0. There are two possible routes to dissipate the energy from illegal voltages and high-current injections. The first and the default route is the two ESD diodes. The second is the P-channel Metal-Oxide-Semiconductor (PMOS) and N-channel Metal-Oxide-Semiconductor (NMOS) near the ESD diodes.

Figure 4-3. IO Structure of MSPM0G

The ESD diodes are triggered if a signal is applied that exceeds maximum input voltage range ( $-0.3V \simeq VCC+0.3V$ ). The ESD diodes can withstand instantaneous ampere-level currents generated during typical electrostatic discharge events (per HBM or CDM standards). This ESD structure is also helpful to defend the illegal voltages and high-current injections in EMS tests.

For full featured IOs, with the output driver logic control, the PMOS and NMOS can also be a path to release the electrical stress. However, for open-drain IOs, the pull-up clamping diode and the PMOS do not exist yet. When the positive electrical stress happens, there is no route to release. The suggestions with different I/O settings are shown in Table 4-3.

Table 4-3. EMS Influence with IO Setting

| IO Type       | IO Setting                                            | IO Status   | Influence                                                                           | EMS Protection                                           |

|---------------|-------------------------------------------------------|-------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|

| General IO    | GPIO output and peripheral output (for example, UART) | Output mode | MOS and ESD structure release<br>EMC noise                                          | Best protection                                          |

|               | Default setting and analog functions                  |             | ESD structure release EMC noise                                                     | Good protection                                          |

|               | GPIO Input And Peripheral Input (for example, UART)   | Input mode  | ESD structure release EMC noise<br>Can introduce noise into MCU<br>internal circuit | Good Protection                                          |

| Open-drain IO | GPIO and peripheral output                            | Output mode | No route to dissipate the positive energy                                           | Risk for positive noise and can need external protection |

|               | Default setting and analog functions                  | Hiz mode    | No route to dissipate the positive energy                                           | Risk for positive noise and can need external protection |

|               | GPIO input/ peripheral input (for example, UART)      | Input mode  | No route to dissipate the positive energy                                           | Risk for positive noise and can need external protection |

#### 4.2 Emission Reduction Features

In this section, the MSPM0 internal features listed are shown in Table 4-4 to control the electromagnetic interference.

**Table 4-4. Emission Reduction Features Summary**

| Features Adjustable |                                                            | Suggestions                             |

|---------------------|------------------------------------------------------------|-----------------------------------------|

| Clock source        | Yes                                                        | Control the usage of clock.             |

| Power mode          | Power mode Yes Choose valid power mode for the related MCU |                                         |

| Package             | Yes                                                        | Choose the smaller and thinner package. |

#### 4.2.1 Clock Source

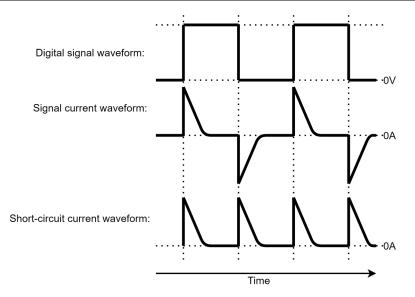

Clock signals are a primary source of EMI in microcontroller systems. Clock noise propagates through the power supply introduced into the system, and also directly emits from the MCU package, contributing to radiated EMI.

For clock noise, clock frequency and current consumption are two critical factors to evaluate influence. The clock frequency determines the noise spectrum range. The current consumption serves as a reliable indicator of overall noise strength. High clock frequency and high current consumption typically increases clock noise.

The MSPM0 microcontroller series has flexible clock selection for users. Several internal and external oscillators are provided for generating low to high frequency clocks to be used by the system. A summary of the MSPM0 clock frequency and current consumptions is provided below for users.

#### Table 4-5. Clock Sources of MSPM0G

| Clock Type | Clock Source | Clock Frequency Range                     | Test Conditions                                                                   | Typical Current<br>Consumption |

|------------|--------------|-------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|

| SYSPLL     | Internal     | Up to 80MHz fSYSPLLREF=32MHz, fVCO=160MHz |                                                                                   | 316uA                          |

| SYSOSC     |              | ≃4-32MHz                                  | f <sub>SYSOSC</sub> =4MHz                                                         | 20uA                           |

|            |              |                                           | f <sub>SYSOSC</sub> =32MHz                                                        | 80uA                           |

|            |              |                                           | f <sub>SYSOSC</sub> =32MHz, Enable ROSC                                           | 90uA                           |

| LFOSC      |              | 32.768kHz                                 | LFOSC=32.768kHz                                                                   | 300nA                          |

| HFXT       | External     | ≃4-48MHz                                  | f <sub>HFXT</sub> =4MHz, R <sub>m</sub> =300Ω, C <sub>L</sub> =12pF               | 75uA                           |

|            |              |                                           | $f_{HFXT}$ =48MHz, $R_m$ =30 $\Omega$ , $C_L$ =12pF, $C_m$ =6.26fF, $L_m$ =1.76mH | 600uA                          |

| LFXT       |              | 32.768kHz                                 | XT1DRIVE=0, LOWCAP=1                                                              | 200nA                          |

Internal clock sources have shorter circuit trace and is shielded by MCU structure compared with external clock sources. External clock sources have lower clock jitter, which is also an important emission noise source. As a result, this is hard compare the emission noise between internal and external clock sources.

The general conclusion is that lower clock frequency generates lower emission noise. Internal and external clock selection are case-by-case. To overcome the noise level in typical frequency point, users can also adjust the oscillator frequency.

#### 4.2.2 Power Modes

The power modes of a microcontroller (MCU) significantly influence EMI due to variations in clock and peripherals activities. In MCU operation, high-frequency clock signals generate strong harmonics. Discrete spectral peaks from synchronized clock networks (for example, CPU, peripherals) amplify radiation.

The MSPM0 series provide five main operating modes (power modes) to allow for optimization of the device power consumption based on application requirements. The modes are: RUN, SLEEP, STOP, STANDBY, and SHUTDOWN. Different power modes represent the different available clock sources and different available peripherals. In every power mode, there are three mode policy options generated by limiting the max system clock frequency. An example of the supported functionality in each operating mode is shown in Table 4-6. For the full table and workable peripherals under different conditions, refer to the device-specific MSPM0 data sheet.

Table 4-6. Supported Functionality by Operating Mode of MSPM0G

|                |                                  | Run   |           |       |        | Sleep  |        | Stop            |        |         | Standby    |          |

|----------------|----------------------------------|-------|-----------|-------|--------|--------|--------|-----------------|--------|---------|------------|----------|

| Operating Mode |                                  | RUNO  | RUN1      | RUN2  | SLEEP0 | SLEEP1 | SLEEP2 | STOP0           | STOP1  | STOP2   | STANDBY0   | STANDBY1 |

|                | SYSOSC                           | EN    | EN        | DIS   | EN     | EN     | DIS    | OPT             | EN     | DIS     | DIS        | DIS      |

| Oscillators    | LFOSC or LFXT EN (LFOSC or LFXT) |       |           |       |        |        |        |                 |        |         |            |          |

|                | HFXT                             | OPT   | DIS       | DIS   | OPT    | DIS    | DIS    | DIS             | DIS    | DIS     | DIS        | DIS      |

|                | SYSPLL                           | OPT   | NS        | NS    | OPT    | NS     | NS     | NS              | NS     | NS      | NS         | NS       |

|                | CPUCLK                           | 80MHz | 32k<br>Hz | 32kHz | DIS    |        |        |                 |        |         |            |          |

| Clocks         | MCLK to PD1                      | 80MHz | 32k<br>Hz | 32kHz | 80MHz  | 32kHz  | 32kHz  | DIS             |        |         |            |          |

|                | ULPCLK to<br>PD0                 | 40MHz | 32k<br>Hz | 32kHz | 40MHz  | 32kHz  | 32kHz  | 4MHz 4MHz 32kHz |        |         | 2kHz       | DIS      |

|                | LFCLK                            |       |           |       |        | 32kHz  |        |                 |        |         |            | DIS      |

|                | CPU                              |       | E         | ΞN    |        |        |        | ļ               | DIS    |         |            |          |

| Core functions | DMA                              |       |           | OPT   |        |        |        |                 | DIS (t | riggers | supported) |          |

| Core functions | Flash                            |       |           | EN    |        |        |        | DIS             |        |         |            |          |

|                | SRAM                             |       |           | EN    |        |        |        | DIS             |        |         |            |          |

Analyze the working frequency and current consumption of digital peripherals and core function to evaluate the emission noise level. To find this information, refer to the device data sheet and the MSPM0G3507 Low Power Test and Guidance.

TI recommends to choose a valid power mode level and mode policy options for the related MCU operation requirement.

#### 4.2.3 Package

In general, the EMI generated by IC packages exhibits an inverse relationship with package dimensions within the same family. Smaller packages tend to produce lower noise emissions due to reduced parasitic inductance and minimized current loop areas, which directly influence high-frequency radiation characteristics. This behavior stems from the decreased lead-frame length, optimized thermal resistance, and shorter interconnect paths inherent in miniaturized packaging technologies.

The following is a list of the package EMI contribution from the highest to the lowest:

- TSSOP (Thin Shrink Small Outline Package)

- SOT (Small Outline Transistor)

- VSSOP (Very Thin Shrink Small Outline Package)

- QFP (Quad Flat Package)

- · QFN (Quad Flat No-lead

- · BGA (Ball Grid Array)

- WCSP (Wafer-Level Chip Scale Package)

For best EMI performance, TI recommends users to choose the smaller and thinner package at the beginning.

Analysis for EMS Test Vivial T

# **5 Analysis for EMS Test**

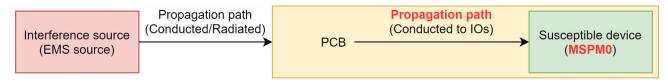

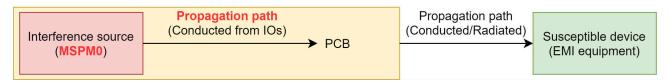

The model used to analyze EMS on MSPM0 perform improvements is shown in Figure 5-1. The EMS test first injects noise in the system, which can be a PCB or a product. Then, the noise is conducted into MSPM0 through IOs or power lines. To debug and improve focuses on the PCB optimization (propagation path) and MSPM0 configuration.

Figure 5-1. Noise Propagation Model for EMS

# 5.1 Root Cause Analysis

Considering the classification level in EMS standards, MSPM0 meets these different failure categories when doing EMC tests. Some failures can be acceptable, especially when system reset can be used in the test. More details are provided in the following sections.

**Specific EMC Test Failure Category Root Cause** Suggestions . Manifestation Acceptability IO or peripheral Metallization defect functionality loss Check whether beyond the Absolute Unacceptable Maximum ratings and Recommended Permanent damage Leakage current Oxide breakdown Operating Conditions. **DVCC-GND** short Burn-in Defect circuit MCU reset Check RSTCAUSE to know the reset Trigger POR or BOOTRST abnormally cause. Conditionally Recoverable malfunction

Trigger hard fault or

register and RAM changes

acceptable

Table 5-1. EMS Failure Category and Causes

# 5.1.1 Permanent Damage

MCU function

abnormally

From the data sheet perspective, the abnormal MCU performance is due to going over the specifications. First, is the absolute maximum ratings. If users go over this specification, then permanent damage can happen. An example from MSPM0G3507 is shown in Table 5-2. In EMS tests, the input voltage for common tolerance pins are often not satisfied and causes damage to MSPM0 when the emission noise is injected into MSPM0 through IO pins. Another issue is the constant diode current specification. This is the current limit beyond which the ESD diode turns ON and starts clamping the voltage. If the ESD diode current is not allowed, like PA24 in MSPM0C1104, then this means the ESD diode starts clamping the voltage at the beginning.

| Table 5-2. Absolute Maximum Ratings of MSPM0G |                               |                                            |      |                                    |    |  |  |

|-----------------------------------------------|-------------------------------|--------------------------------------------|------|------------------------------------|----|--|--|

|                                               | PARAMETER <sup>(1)</sup>      | TEST CONDITIONS(2)                         | MIN  | MIN MAX                            |    |  |  |

| VDD                                           | Supply voltage                | At VDD pin                                 | -0.3 | 4.1                                | V  |  |  |

| VI                                            | Input voltage                 | Applied to any 5V tolerant open-drain pins | -0.3 | 5.5                                | V  |  |  |

| VI                                            | Input voltage                 | Applied to any common tolerance pins       | -0.3 | V <sub>DD</sub> + 0.3<br>(4.1 MAX) | V  |  |  |

|                                               | Current into VDD pin (source) | -40°C ≤ Tj ≤ 130°C                         |      | 80                                 | mA |  |  |

| Current into VDD pin (source)                 |                               | -40°C ≤ Tj ≤ 85°C                          |      | 100                                | mA |  |  |

|                                               | Current out of VSS pin (sink) | -40°C ≤ Tj ≤ 130°C                         |      | 80                                 | mA |  |  |

| I <sub>VSS</sub>                              | Current out of VSS pin (sink) | -40°C ≤ Tj ≤ 85°C                          |      | 100                                | mA |  |  |

Check IPSR to know the interrupt

source.

www.ti.com Analysis for EMS Test

Table 5-2. Absolute Maximum Ratings of MSPM0G (continued)

| PARAMETER <sup>(1)</sup> |                         | TEST CONDITIONS(2)                  | MIN MAX           | UNIT |

|--------------------------|-------------------------|-------------------------------------|-------------------|------|

|                          | Current of SDIO pin     | Current sunk or sourced by SDIO pin | 6                 | mA   |

| l                        | Current of HS_IO pin    | Current sunk or sourced by HSIO pin | 6                 | mA   |

| IIO                      | Current of HDIO pin     | Current sunk or sourced by HDIO pin | 20                | mA   |

|                          | Current of ODIO pin     | Current sunk by ODIO pin            | 20                | mA   |

| I <sub>D</sub>           | Supported diode current | Diode current at any device pin     | ±2 <sup>(3)</sup> | mA   |

- (1) Stresses beyond those listed under Absolute Maximum Rating can cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods can affect device reliability.

- (2) Higher temperatures can be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

- (3) PA21 has an internal connection for testing purposes; there is no injection current allowed on this pin.

The second is the recommended operating conditions. If MSPM0 goes over this specification, then recoverable malfunction can happen. Therefore, the capacitor usages are suggested to follow the instructions.

**Table 5-3. Recommended Operating Conditions**

|                    | (3)                                               | MIN  | NOM  | MAX | UNIT |

|--------------------|---------------------------------------------------|------|------|-----|------|

| VDD                | Supply voltage                                    | 1.62 |      | 3.6 | V    |

| VCORE              | Voltage on VCORE pin (2)                          |      | 1.35 |     | V    |

| C <sub>VDD</sub>   | Capacitor connected between VDD and VSS (1)       |      | 10   |     | uF   |

| C <sub>VCORE</sub> | Capacitor connected between VCORE and VSS (1) (2) |      | 470  |     | nF   |

- (1) Connect C<sub>VDD</sub> and C<sub>VCORE</sub> between VDD and VSS and VCORE/VSS, respectively, as close to the device pins as possible. A low-ESR capacitor with at least the specified value and tolerance of ±20% or better is required for C<sub>VDD</sub> and C<sub>VCORE</sub>.

- (2) The VCORE pin must only be connected to C<sub>VCORE</sub>. Do not supply any voltage or apply any external load to the VCORE pin.

- (3) Wait states are managed automatically by the system controller (SYSCTL) and do not need to be configured by application software unless MCLK is sourced from a high speed clock source (HSCLK sourced from HFCLK or SYSPLL)

#### 5.1.2 Recoverable Malfunction

For the recoverable malfunction, MSPM0 devices include several diagnostic mechanisms to detect errors at runtime. Table 5-4 lists error sources and the corresponding handling mechanism. This can be used to give additional analysis information in EMS failure analysis.

Table 5-4. Error Sources and Handling Mechanisms

| Error Source              | Error                                         | Handling Mechanism                                                                                                                                                                                                                                                     |

|---------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash (if device has ECC) | Non-correctable ECC error (if device has ECC) | <ul> <li>For a CPU or DMA request, a FLASHDED nonmaskable interrupt is generated to the processor or a SYSRST is generated depending on configuration of the FLASHECCRSTDIS bit</li> <li>The FLASHDED sticky bit is set in the SYSSTATUS register in SYSCTL</li> </ul> |

|                           | Correctable ECC error (if device has ECC)     | A FLASHSEC interrupt is also generated in SYSCTL     The FLASHSEC sticky bit is set in the SYSSTATUS register in SYSCTL                                                                                                                                                |

Table 5-4. Error Sources and Handling Mechanisms (continued)

| Error Source                           | Error                                         | ces and Handling Mechanisms (continued)  Handling Mechanism                                                                                    |  |  |  |  |

|----------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        | -                                             | · ·                                                                                                                                            |  |  |  |  |

| SRAM                                   | Non-correctable ECC error (if device has ECC) | An SRAMDED nonmaskable interrupt is generated to the processor                                                                                 |  |  |  |  |

|                                        | Correctable ECC error (if device has ECC)     | A SYSCTL SRAMSED interrupt is generated to the processor                                                                                       |  |  |  |  |

|                                        | Parity error (if device has parity)           | Nonmaskable interrupt is generated to the processor if the request was from the CPU                                                            |  |  |  |  |

|                                        |                                               | DMA data error interrupt is generated if the request was from the DMA                                                                          |  |  |  |  |

|                                        | Address error on CPU access                   | A hard fault is generated in the CPU                                                                                                           |  |  |  |  |

|                                        | Address error on DMA access                   | A DMA address error interrupt is generated in the DMA controller                                                                               |  |  |  |  |

|                                        | ECC error on CAN SRAM (if device has CAN-FD)  | An interrupt is generated in the CAN-FD peripheral                                                                                             |  |  |  |  |

| SHUTDNSTOREX<br>Memory (if<br>present) | Parity error                                  | A POR is generated                                                                                                                             |  |  |  |  |

| CKM                                    | MCLK failure                                  | A BOOTRST is generated                                                                                                                         |  |  |  |  |

|                                        | LFCLK failure (if present)                    | A BOOTRST is generated if LFCLK is sourcing MCLK     An LFCLKFAIL nonmaskable interrupt is generated in the SYSCTL NMI registers.              |  |  |  |  |

| CPUSS (if device has MPU)              | Memory protection unit violation              | A hard fault is generated in the CPU                                                                                                           |  |  |  |  |

| WWDT                                   | WWDT0 violation                               | A BOOTRST is generated or a nonmaskable interrupt is generated in the SYSCTL NMI registers depending on configuration of the WWDTLP0RSTDIS bit |  |  |  |  |

|                                        | WWDT1 violation (if present)                  | A BOOTRST is generated or a nonmaskable interrupt is generated in the SYSCTL NMI registers depending on configuration of the WWDTLP1RSTDIS bit |  |  |  |  |

| PMU                                    | Trim parity error                             | A POR is generated                                                                                                                             |  |  |  |  |

|                                        | POR0- supply error                            | A POR is generated                                                                                                                             |  |  |  |  |

|                                        | BOR0- supply error                            | A BOR is generated                                                                                                                             |  |  |  |  |

|                                        | BOR1/2/3- supply error                        | A BORLVL nonmaskable interrupt is generated in the SYSCTL NMI registers                                                                        |  |  |  |  |

| CPUSS                                  | Memory protection unit violation (if present) | A hard fault is generated in the CPU                                                                                                           |  |  |  |  |

If MCU resets abnormally, then users can get the reset source information from RSTCAUSE register using DL\_SYSCTL\_getResetCause() software function. Then search the RSTCAUSE table to know the reset source, as shown in Table 5-5.

www.ti.com Analysis for EMS Test

Table 5-5. RSTCAUSE Field Descriptions of MSPM0G

| Bit  | Field    | Type | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|