# Single Event Effects Testing for the ADC12DJ3200QML-SP 12-bit, Dual 3.2-GSPS or Single 6.4-GSPS, RF-Sampling, JESD204B, Analog-to-Digital Converter (ADC)

Kyle Lewis, Robert Taft, Alexander Bodem, Tobias Hoehn, Philipp Schmitz, Vineethraj Nair, Filip Savic, Matthew Childs, Paul Kramer, Jered Sandner, Matthew Guibord

*Abstract*—The effects of heavy-ion irradiation on the single-event effect performance of the Texas Instruments ADC12DJ3200QML-SP and its JESD204B serialized interface were characterized using the K500 Cyclotron facility at Texas A&M University. The results demonstrate latch-up immunity up to  $\text{LET}_{\text{EFF}} = 120 \text{ MeV-cm}^2/\text{mg}$  at  $T_J = 125^{\circ}\text{C}$  while operating at the maximum recommended operating supply voltages. Dynamic cross sections for the code error rate of the device and the serialized interface are also presented.

*Index Terms*—analog-to-digital converter, heavy ion testing, JESD204B, RF-sampling, serialized interface, single event effects

# I. INTRODUCTION

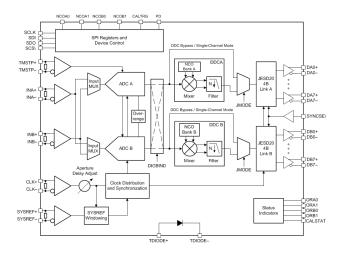

THE TEXAS INSTRUMENTS ADC12DJ3200QML-SP is the first JESD204B-compliant, RF-sampling, 12-bit analog-to-digital data converter (ADC) for aerospace and high-reliability applications. In dual channel mode the ADC can sample up to 3200-MSPS, while in single channel mode the ADC interleaves both internal cores to achieve sampling rates up to 6400-MSPS. The ADC12DJ3200QML-SP can directly sample input frequencies from DC to above 10 GHz. See Fig. 1 for the block diagram.

The ADC12DJ3200QML-SP uses a high speed JESD204B output interface with up to 16 serialized lanes and subclass-1 compliance for deterministic latency and multi-device synchronization. The serial output lanes support bit rates up to

Submitted July 26, 2019. This work was supported in full by Texas Instruments, Incorporated.

Kyle Lewis is a validation engineer with Texas Instruments, Dallas, TX USA (e-mail: kylelewis@ti.com).

Matthew Guibord is a systems engineer with Texas Instruments, Dallas, TX USA (e-mail: mattguibord@ti.com).

Robert Taft is a design engineer with Texas Instruments, Freising, Germany (e-mail: Robert.Taft@ti.com).

Alexander Bodem, Tobias Hoehn, Philipp Schmitz, Vineethraj Nair, and Filip Savic are design engineers with Texas Instruments, Freising, Germany

Matthew Childs, Paul Kramer, and Jered Sandner are design engineers with Texas Instruments, Ft. Collins, CO USA.

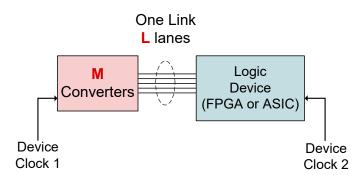

12.8 Gbps and can be configured to trade-off bit rate versus number of lanes. The JESD204B interface enables a reduction in board space and layout complexity compared to traditional LVDS data converters, while also enabling higher channel density and more cost-effective hardware (Fig. 2).

The ADC12DJ3200QML-SP is built using the Texas Instruments C021.A 65 nm CMOS process technology and utilizes a time interleaved architecture that allows for low power consumption (1.5 W per channel), high data conversion rates (up to 6400-MSPS), and high full-power (-3 dB) input bandwidth (7 GHz).

The ADC12DJ3200QML-SP provides foreground and background calibration options for gain, offset and static linearity errors. Foreground calibration is run at system startup or at specified times during which the ADC is offline and not sending data to the logic device. Background calibration allows the ADC to run continually while the cores are calibrated in the background so that the system does not experience downtime. The calibration routine is also used to match the gain and offset between sub-ADC cores to minimize spurious artifacts from time interleaving.

Fig. 1. Block diagram of the ADC12DJ3200QML-SP. The two JESD204B links enable up to 16 output lanes. The ADC cores can be interleaved to achieve 2x the sampling rate in single channel mode.

Fig. 2. Simplified block diagram of the JESD204B link. The JESD204B interface enables reduced lane counts between the converter and FPGA compared to traditional LVDS devices. There are no data clocks or strict trace length-matching requirements.

### II. MECHANISMS OF SINGLE EVENT EFFECTS

The primary concerns for the ADC12DJ3200QML-SP are its resilience against the destructive single-event effects (SEE) such as single-event latch-up (SEL) and non-destructive single-event functional interrupts (SEFI).

The ADC12DJ3200QML-SP was characterized for SEL events as the 65 nm CMOS process used for the ADC12DJ3200QML-SP introduces a potential for SEL susceptibility [1][2]. The ADC12DJ3200QML-SP exhibited no SEL with heavy-ions of up to LET<sub>EFF</sub> = 120 MeV-cm<sup>2</sup>/mg at a fluence of  $10^7$  ions/cm<sup>2</sup> and a die temperature of  $125^{\circ}$ C while operated in the recommended supply voltage range.

Another concern in a high reliability, high performance application is the SEFI characteristics of the ADC, especially in the high-speed JESD204B serialized interface which has not been used in high-reliability, radiation environment applications previously. The ADC12DJ3200QML-SP SEFI performance was characterized beyond an LET<sub>EFF</sub> = 120 MeV-cm<sup>2</sup>/mg.

# III. DUT PREPARATION & TEST SETUP

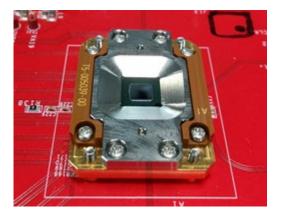

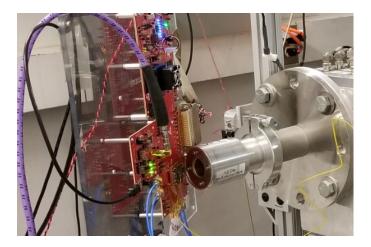

The flip-chip die of the ADC12DJ3200QML-SP must be de-capped and thinned for exposure to heavy ions. The de-capped unit exposes the Silicon substrate directly. The die were back-grinded to <40 um for proper ion penetration through the Silicon substrate and a custom open-top RF socket is utilized to mount the device on the evaluation module (EVM). This socket opening allows for large beam angles beyond 45° (Fig. 3).

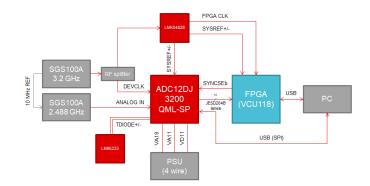

The test setup block diagram is shown in Fig. 4. We used low phase noise (LPN) signal generators to produce the clock and ADC input signals, along with band-pass filters (BFPs) to achieve the best possible ADC dynamic performance. Fourwire Kelvin-sensing power supplies were used to account for IR drops in the power supply cables and EVM power planes.

Fig. 3. ADC12DJ3200QML-SP mounted in the test socket on the DUT-EVM. The open top socket allows fast changing of devices and beam angles beyond  $45^{\circ}$ .

The test conditions for SEL testing and SEFI testing are outlined as follows:

1. For SEL testing, the ADC was operated at  $T_J = 125$  °C and datasheet maximum recommended voltage supplies ( $V_{MAX}$ ).

a. VA19 = 2.0V, VA11 = 1.15V, VD11 = 1.15V

- 2. For SEFI testing, the ADC was operated under the following conditions:

- Mission-mode "JMODE1" utilizing 16-lanes at 6.4 Gbps (JESD204B)

i. JMODE1 is a single channel mode

- b.  $F_S = 6.4 \text{ GSPS} (F_{CLK} = 3.2 \text{ GHz})$

- c.  $F_{IN} = 2.488$ GHz at -1 dBFS applied to Input Channel A

- d. Datasheet minimum recommended voltage supplies  $(V_{MIN})$

1.

$$VA19 = 1.8 V$$

;  $VA11 = VD11 = 1.05 V$

- e. Ambient room temperature (roughly 25C)

- f.  $T_J = 80C$  when running foreground calibration (FG)

- g.  $T_J = 90C$  when running background calibration (BG)

- h. SYSREF calibration and processing enabled

- i. JTIMER watchdog feature set to 10

Fig. 4. Block diagram of the SEL and SEFI test setup. The LM95233 and LMK04828 chips are on-board with the DUT. The VCU118 FPGA is mounted on a separate EVM and the DUT-EVM interfaces with the FPGA through an FMC+ connector.

# IV. IRRADIATION FACILITY

The ADC12DJ3200QML-SP was put through heavy ion testing using the TAMU 15 MeV K500 Cyclotron (Fig. 5). The device was monitored for SEL, SEFI and single-event upset (SEU).

The effective LET (LET<sub>EFF</sub>), depth and range was determined with the custom RADsim-IONS application developed at Texas Instruments and based on the latest SRIM2013 models [3]. The application accounts for energy loss through the 1-mil thick Aramica beam port window and the air gap between the DUT and the heavy-ion exit port. Table I summarizes the ions and beam angles used to achieve a wide range of LETs for the ADC12DJ3200QML-SP's SEE characterization.

All beam runs stop at a total fluence of  $10^7$  ions/cm<sup>2</sup> with a target flux of  $10^5$  ions/cm<sup>2</sup>/s (unless otherwise noted). Cross section data points represent an average of multiple runs and/or DUTs at each LET. The average Si thickness of the entire die was used to compute the effective LET.

Fig. 5. DUT-EVM and capture card mounted for heavy-ion exposure in free-air. Hot air was used to increase the junction temperature of the DUT for SEL testing.

| TABLE I                                                 |     |       |              |  |  |  |

|---------------------------------------------------------|-----|-------|--------------|--|--|--|

| IONS, ANGLES, AND AIRGAPS USED AT TAMU FOR SEFI TESTING |     |       |              |  |  |  |

|                                                         | Ion | Angle | Air gap (mm) |  |  |  |

| Angle | Air gap (mm)                                        |

|-------|-----------------------------------------------------|

| 45    | 50                                                  |

| 30    | 50                                                  |

| 0     | 50                                                  |

| 0     | 50                                                  |

| 0     | 50                                                  |

| 45    | 50                                                  |

| 0     | 50                                                  |

| 30    | 50                                                  |

| 0     | 50                                                  |

| 45    | 50                                                  |

| 0     | 50                                                  |

| 0     | 50                                                  |

|       | 45<br>30<br>0<br>0<br>45<br>0<br>30<br>0<br>45<br>0 |

# V. SINGLE-EVENT LATCH-UP TESTING

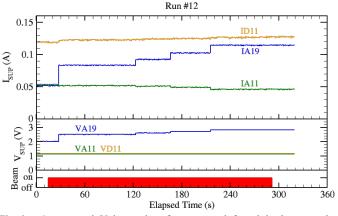

The ADC12DJ3200QML-SP has three voltage supplies. These are VA19 (1.9V nominal analog supply), VA11 (1.1V nominal analog supply), and VD11 (1.1V nominal digital supply). The product specification allows for a supply voltage variance of  $\pm$ -5% from the nominal values [4].

The supplied current to the DUT from the Kelvin-sensing power supply was constantly monitored through a LabView GUI. The junction temperature of the DUT was monitored using the on-die temperature diode through the on-board Texas Instruments LM95233 temperature sensor [5].

With the ADC in normal operating mode, no SEL was observed on any supply at  $T_J = 125^{\circ}$ C with all supplies raised simultaneously up to +10% above the datasheet max operating spec. No SEL was observed up to an LET of 120 MeV-cm<sup>2</sup>/mg at a flux of approximately 10<sup>4</sup> ions/cm<sup>2</sup>/s to 10<sup>5</sup> ions/cm<sup>2</sup>/s to a fluence of 10<sup>7</sup> ions/cm<sup>2</sup>.

The robustness of the ADC to SEL was further characterized by placing the DUT into power-down mode and elevating the voltage supplies beyond their maximum recommended operating voltages. All supplies started out at the datasheet maximum recommended operating voltage or +5% of the nominal values, e.g. VA19 = 2.0V, VA11 = 1.15V, VD11 = 1.15V, and then were slowly ramped individually during separate beam runs until latch-up was observed.

Latch-up occurred on the VA11 supply at 1.55V, and on the VD11 supply at 1.60V, each greater than +30% above the specified maximum supply voltage. No damage was observed, however, low current compliance was used on the supplies for these SEL tests to prevent damage from occurring.

The latch-up holding voltage for VD11 was 1.155V and for VA11 was 1.30V.

As seen in Fig. 6, no SEL was observed on the VA19 supply despite raising it to 2.8V (+40% above the maximum rated voltage).

Fig. 6. Current and Voltage plots for attempted forced latch-up on the VA19 supply. The maximum operating supply voltage for VA19 is 2.0 V. No latch-up was observed; the current increase shown is due to leakage currents and DUT self-heating.

In later beam runs with the device in an active missionmode and all supplies simultaneously raised to +15% above the specified maximum recommended operating voltage resulted in a higher-current latch-up of VA11 and a holding voltage of 1.160V. The device was not damaged with the VA11 supply current compliance set to 1.0A.

# VI. SINGLE-EVENT FUNCTIONAL INTERRUPT TESTING

A custom FPGA firmware image, including a fully compliant JESD204B receiver (RX), was developed to measure the code error rate (CER) of the ADC and to characterize the JESD204B transmitter (TX) of the ADC12DJ3200QML-SP in a radiation environment. The firmware image runs on a Xilinx VCU118 FPGA and is controlled by a custom LabView GUI.

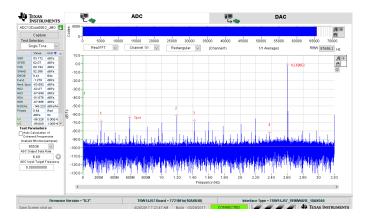

In addition to CER testing, specific SEFI tests were performed to validate ADC functionality in a radiation environment. The ADC configuration registers were programmed and stored using a serial peripheral interface (SPI) GUI. The contents of the configuration registers were read before and after beam runs and compared. No changes to user-programmed or auto-loaded (default) registers were observed. Also, as shown in Fig. 7, Fast Fourier Transforms (FFTs) were captured and calculated during beam runs at the highest LET tested in order to confirm that the dynamic performance parameters of the DUT did not degrade while the beam was running.

Fig. 7. Example FFT during SEFI testing showing a consistent ENOB > 8 for a 2.6 GHz full-scale input sample at 6.4 GSPS.

# A. Code Error Rate Testing

If the sampling frequency and input signal frequency are coherent and the number of the continuous time signal cycles after N discrete time samples is a prime number, then sample numbers n and n + N are equal if there are no code errors. However, if there are code errors in the ADC's output codes, then the difference between these two samples is non-zero. Thus any non-zero value resulting from subtracting the corresponding samples n and n + N is flagged as a code error [6]. The magnitude of the error is compared with a threshold value to determine the severity of the error and then counted by a threshold-specific error counter.

Error thresholds are set at 10 user-defined levels. We used thresholds of 16, 24, 32, 64, 128, 256, 512, 1024, 2048, and 3072 LSBs.

Due to inherent thermal and environmental noise, we observe CER errors at up to the 128-LSB threshold without the beam running. We will consider CER errors above the

256-LSB threshold as an SEE event. JESD204B transmitter errors are also included in the CER measurements.

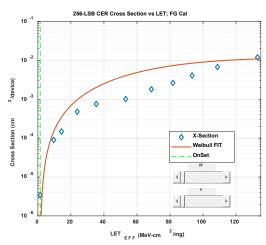

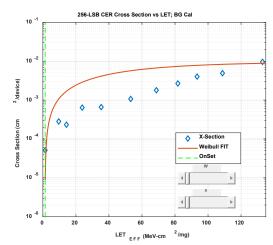

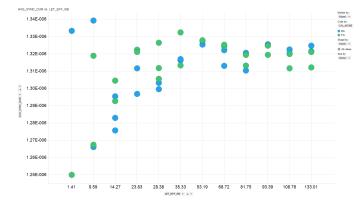

Fig. 8 and 9 show the 256-LSB CER cross-section plots for Foreground and Background calibration modes. We see roughly equivalent cross-section performance regardless of the calibration mode used. The Weibull fit parameters are shown in Table II.

It is important to note that the shape of the measured crosssection curve reflects the multiple CER contributors including analog upsets, digital upsets and JESD204B interface upsets, each with different probability distributions of CER magnitude.

Fig. 8. 256-LSB CER cross section for the device running in Foreground calibration mode.

Fig. 9. 256-LSB CER cross section for the device running in Background calibration mode.

| TABLE II<br>Weibull Parameters for the 256-LSB CER Cross Sections |                           |                           |  |  |  |

|-------------------------------------------------------------------|---------------------------|---------------------------|--|--|--|

| Parameter                                                         | Foreground<br>Calibration | Background<br>Calibration |  |  |  |

| Onset (MeV-<br>cm <sup>2</sup> /mg)                               | 1.4                       | 1.4                       |  |  |  |

| $\sigma_{SAT}$ (cm <sup>2</sup> )                                 | 1.19E-2                   | 9.64E-3                   |  |  |  |

| W                                                                 | 82.5                      | 57.5                      |  |  |  |

| S                                                                 | 1.9                       | 1.1                       |  |  |  |

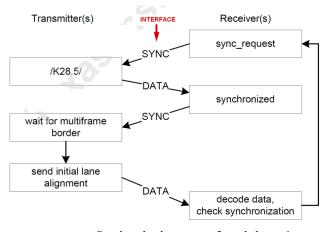

#### B. JESD204B Link Characterization

The custom FPGA firmware acts as a JESD204B compliant receiver (RX). If the RX detects an error in the transmission of data from the ADC or the ADC corrects an error in its transmission, then the link is automatically reestablished (Fig. 10). The RX will assert a signal called JESD204B "SYNC" when the link needs to be reestablished. The active-low SYNC signal is used to indicate if the RX has achieved code group synchronization (CGS) and is ready to decode data [7]. We recorded the number of times the link was reestablished in a given beam run along with the time it took to reestablish the link once an error was detected. Note that the JESD204B "SYSREF" signal will help both TX and RX recover after an upset [8]. A continuous SYSREF signal running at 16MHz is always present during our testing and is recommended in practice. The SYSREF signal was derived from the device clock by the Texas Instruments LMK04828 [9] and distributed to both the DUT and the FPGA.

Synchronization process for subclasses 1

Fig. 10. The synchronization procedure to establish the JESD204B 8b/10b link. A fully compliant receiver plays a most critical role in reestablishing the link when it is upset.

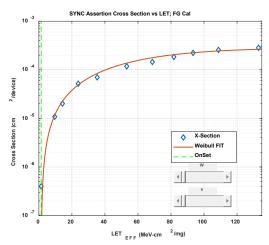

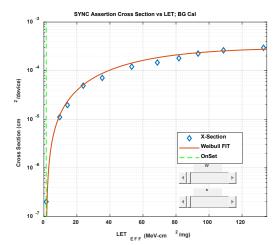

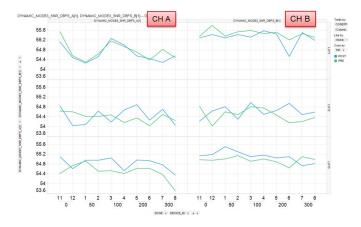

Fig. 11 and 12 show the SYNC Assert cross-section plots for Foreground and Background calibration modes. We observe no difference in the behavior of the link between ADC calibration modes. The Weibull fit parameters are shown in Table III. The JESD204B link was observed to always recover automatically from an upset without user intervention in the tested operating mode (JMODE1).

The average recovery time, once an upset or error was detected that causes SYNC to be asserted, across all tested LETs was around  $1.3 \ \mu s$  and is shown in Fig. 13.

The maximum recorded SYNC assert recovery time was 11  $\mu$ s for LET<sub>EFF</sub> = 53. This measurement was not recorded for LETs above 53 MeV-cm<sup>2</sup>/mg as this feature was unavailable when we tested with heavier ions.

Fig. 11. SYNC Assert cross section for the device running in Foreground calibration mode.

Fig. 12. SYNC Assert cross section for the device running in Background calibration mode.

TABLE III WEIBULL PARAMETERS FOR THE JESD204B SYNC ASSERT CROSS SECTIONS

| Parameter                           | Foreground<br>Calibration | Background<br>Calibration |

|-------------------------------------|---------------------------|---------------------------|

| Onset (MeV-<br>cm <sup>2</sup> /mg) | 1.4                       | 1.4                       |

| $\sigma_{SAT}$ (cm <sup>2</sup> )   | 2.83E-4                   | 2.95E-4                   |

| W                                   | 68                        | 68                        |

| S                                   | 1.5                       | 1.5                       |

Fig. 13. Average JESD204B link recovery time after an upset is detected that causes SYNC to be asserted. There is no significant difference in the average recovery time across LETs or ADC calibration modes (blue = BG, green = FG).

#### VII. TOTAL IONIZING DOSE

The ADC12DJ3200QML-SP has a TID rating of 300 krad(Si) tested according to MIL-STD-883, Test Method 1019. The device shows no performance degradation at 300 krad(Si) across multiple wafer-lots. Pre- and post-performance measurements were taken on automated test equipment (ATE). All ATE measurements meet datasheet specifications after the TID testing. Fig. 14 shows the signal-to-noise ratio (SNR) of the ADC operating in dual-channel mode with all post-TID test results meeting the datasheet specification of 52 dBFS.

Fig. 14. SNR measurements for Pre- (green) and Post- (blue) irradiation taken across three different fab-lots. Six samples per dose (two per fab-lot) were tested. All ATE measurements meet datasheet specifications after the TID testing.

### VIII. SUMMARY

A summary of the ADC12DJ3200QML-SP SEE testing is as follows:

- The ADC's JESD204B link in the tested 16-lane JMODE1 always self-recovers from radiation events and without user intervention.

- The ADC in the tested 16-lane JMODE1 exhibits no unrecoverable functional interrupts (SEFI) or permanent performance degradations under the beam.

- No user-programmable or fuse-backed device configuration registers are upset under the beam.

- Calibration vectors are not corrupted under the beam while running in either calibration mode.

- No SEL occurs up to an LET of 120 MeV-cm<sup>2</sup>/mg using the datasheet recommended maximum supply voltages and T<sub>J</sub> = 125°C.

- The total ionizing dose (TID) rating of the ADC12DJ3200QML-SP is 300 krad(Si).

#### REFERENCES

- M. Shoga and D. Binder, "Theory of Single Event Latchup in Complementary Metal-Oxide Semiconductor ICs", *IEEE Trans. Nucl. Sci.*, 33(6), Dec. 1986, pp. 1714-1717.

- [2] G. Bruguier and J.M. Palau, "Single particle-induced latchup", *IEEE Trans. Nucl. Sci.*, Vol. 43(2), Mar. 1996, pp. 522-532.

- [3] "The Stopping and Range of Ions in Matter" (SRIM) software simulation tools website. [Online]. Available: http://www.srim.org/index.htm#SRIMMENU

- [4] M. Guibord, "ADC12DJ3200QML-SP 6.4-GSPS, Single-Channel or 3.2-GSPS, Dual-Channel, 12-Bit, RF-Sampling Analog-to-Digital Converter (ADC)." [Online]. Available: http://www.ti.com/documentviewer/ADC12DJ3200QML-SP/datasheet/

- [5] Texas Instruments, "LM95233 Dual Remote Diode and Local Temp Sensor", August 2006, [Online]. Available: http://www.ti.com/product/LM95233

- [6] K. Chan and B. Ye, "Verified Design Pipeline ADC Code Error Rate Analysis and Measurement." [Online]. Available: www.ti.com/lit/ug/tidub02/tidub02.pdf

- [7] Texas Instruments, "JESD204B Start Up", October 2011, [Online]. Available: www.ti.com/lit/ug/snau139.pdf

- [8] JEDEC Standard JESD204B, July 2011, [Online]. Available: https://www.jedec.org/sites/default/files/docs/JESD204 B.pdf

- [9] Texas Instruments, "LMK04828 Ultra-low jitter synthesizer & jitter cleaner", March 2013, [Online]. Available: http://www.ti.com/product/LMK04828

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated