# TLK6002 Board Design Guide

Hassan Ali

**ICP-Communications** Interface

#### ABSTRACT

The TLK6002 is a multi-gigabit transceiver intended for use in ultra-high-speed, bidirectional, point-to-point, data transmission systems such as base station Remote Radio Head (RRH) applications as well as any other high-speed applications. All CPRI and OBSAI data rates of 0.6144, 0.768, 1.2288, 1.536, 2.4576, 3.072, 4.9152, and 6.144Gbps are supported using a single, fixed reference clock frequency of either 122.88 MHz or 153.6 MHz and non-CPRI or OBSAI serial data rates between 0.470 and 6.25 Gbps are also supported. Each channel of the TLK6002 can be operated from a single, shared reference clock or independently from separate reference clocks at different frequencies.

This document provides recommendations on successful integration of the TLK6002 in customer systems. It discusses power supplies, high-speed interfaces, as well as various control interfaces and the associated peripheral components.

#### Contents

| 1 | TLK60                               | 002 Power Supply                                  | 2 |  |  |

|---|-------------------------------------|---------------------------------------------------|---|--|--|

|   | 1.1                                 | Generating the 1-V Power Supply                   | 2 |  |  |

|   | 1.2                                 | 1-V Power Supply Filtering and Decoupling         | 2 |  |  |

|   | 1.3                                 | Generating the 1.5-V/1.8-V Power Supply           | 3 |  |  |

|   | 1.4                                 | 1.5-V/1.8-V Power Supply Filtering and Decoupling | 3 |  |  |

|   | 1.5                                 | Power Supply Ramp Order                           | 4 |  |  |

|   | 1.6                                 | AGND and DGND                                     | 4 |  |  |

| 2 | TLK60                               | TLK6002 High-Speed Data Path                      |   |  |  |

|   | 2.1                                 | Layout Recommendations for High-Speed Signals     | 4 |  |  |

|   | 2.2                                 | AC-Coupling                                       |   |  |  |

| 3 | TLK60                               | 002 Low-Speed Data Path                           |   |  |  |

|   | 3.1                                 | Layout Recommendations for Low-Speed Signals      | 7 |  |  |

| 4 | TLK60                               | 002 Clocks: REFCLK, CLK_OUT, TXCLK, and RXCLK     |   |  |  |

|   | 4.1                                 | General Information                               | 8 |  |  |

|   | 4.2                                 | External Clock Connections                        |   |  |  |

| 5 | TLK6002 Control Pins and Interfaces |                                                   |   |  |  |

|   | 5.1                                 | MDIO Interface                                    |   |  |  |

|   | 5.2                                 | JTAG Interface                                    | 9 |  |  |

|   | 5.3                                 | SPI Interface                                     |   |  |  |

|   | 5.4                                 | Provisioning for System Debug                     |   |  |  |

|   | 5.5                                 | Unused Pins                                       |   |  |  |

| 6 | Summ                                | nary                                              | 9 |  |  |

| 7 | Refere                              | ences                                             | 9 |  |  |

|   |                                     |                                                   |   |  |  |

#### List of Figures

| 1 | 1-V Power Supply Filtering and Decoupling Connections                                  | 2 |

|---|----------------------------------------------------------------------------------------|---|

| 2 | 1.5-V/1.8-V Power Supply Filtering and Decoupling Connections                          | 4 |

| 3 | Differential Microstrip PCB Trace Geometry Example                                     | 5 |

| 4 | High-Speed PCB Traces With Vias Having no Via Stubs and no Via Pads on Internal Layers | 6 |

| 5 | Differential PCB via Structure, Top View                                               | 6 |

| 6 | Reference Plane Cutout Under SFP/SFP+ Module Connector Pads                            | 7 |

|   |                                                                                        |   |

#### TLK6002 Power Supply

| 7 | HSTL Output and Input Schematic                                | 8 |  |  |  |  |

|---|----------------------------------------------------------------|---|--|--|--|--|

| 8 | External Clock Jitter Cleaner Connection Example for Channel A |   |  |  |  |  |

|   | List of Tables                                                 |   |  |  |  |  |

| 1 | TLK6002 Device 1-V Supply Specifications                       | 2 |  |  |  |  |

2

TLK6002 Device 1.5-V/1.8-V Supply Specifications

3

# 1 TLK6002 Power Supply

The TLK6002 operates from two basic power supplies: 1 V and 1.5 V or 1.8 V. Either a linear low-dropout (LDO) regulator or a switching regulator can be used for any of those power supplies.

# 1.1 Generating the 1-V Power Supply

The TLK6002 device 1-V power supply specifications are highlighted in Table 1.

|                      | PARAMETER                   |        | SPECIFICATION |        |  |

|----------------------|-----------------------------|--------|---------------|--------|--|

|                      |                             |        | NOM           | MAX    |  |

| Power Supply Voltage | VDDD, AVDD, DVDD, VDDT, VPP | 0.95 V | 1 V           | 1.05 V |  |

| Power Supply Current | VDDD                        |        |               | 75 mA  |  |

|                      | AVDD                        |        |               | 250 mA |  |

|                      | DVDD+VPP                    |        |               | 200 mA |  |

|                      | VDDT                        |        |               | 15 mA  |  |

# Table 1. TLK6002 Device 1-V Supply Specifications

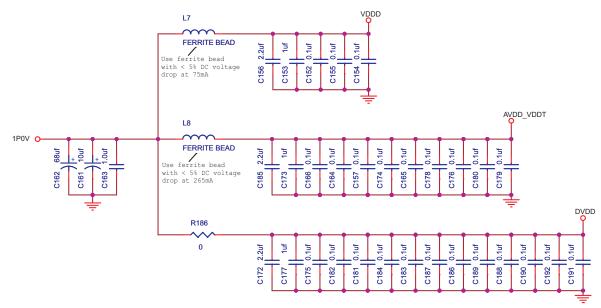

# 1.2 1-V Power Supply Filtering and Decoupling

A recommended power supply filtering and decoupling network is shown in Figure 1. The  $0.1-\mu$ F decoupling capacitors in 0201 (preferred) or 0402 size must be placed as close as possible to the respective power supply pins. Package sizes for the remaining capacitors must be chosen as small as possible. For high-frequency filtering, any ferrite bead can be used as long as it has less than 5% dc voltage drop at the maximum respective power supply current as provided in the Table 1. The AVDD\_VDDT node shown in Figure 1 must be connected to all AVDD and VDDT pins.

# 1.3 Generating the 1.5-V/1.8-V Power Supply

The TLK6002 device 1.5-V/1.8-V power supply specifications are highlighted in Table 2.

|                      | Downwork or       |     | Specification  |              |                |  |

|----------------------|-------------------|-----|----------------|--------------|----------------|--|

| Parameter            |                   | Mir | Min            | Nom          | Мах            |  |

| Power Supply Voltage | VDDQA/B           |     | 1.4 V/1.7 V    | 1.5 V/1.8 V  | 1.6 V/1.9 V    |  |

|                      | VDDRA/B,VDDO1/2/3 |     | 1.425 V/1.71 V | 1.5 V/1.8 V  | 1.575 V/1.89 V |  |

|                      | VREFTA/B          |     | -1%            | 0.75 V/0.9 V | +1%            |  |

| Power Supply Current | VDDQA/B           |     |                |              | 800 mA         |  |

|                      | VDDRA/B           |     |                |              | 40 mA          |  |

|                      | VDDO1/2/3         |     |                |              | 10 mA          |  |

|                      | VREFTA/B          |     |                |              | 0.5 mA         |  |

#### Table 2. TLK6002 Device 1.5-V/1.8-V Supply Specifications

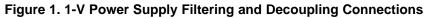

# 1.4 1.5-V/1.8-V Power Supply Filtering and Decoupling

A recommended power supply filtering and decoupling network is shown in Figure 2. The 0.1- $\mu$ F decoupling capacitors in 0201 (preferred) or 0402 size must be placed as close as possible to the respective power supply pins. Package sizes for the remaining capacitors must be chosen as small as possible. For high-frequency filtering, any ferrite bead can be used as long as it has less than 5% dc voltage drop at the maximum respective power supply current as provided in the Table 2. The VDDQ\_VDDO node shown in Figure 2 must be connected to all VDDQA, VDDQB, VDDO1, VDDO2, and VDDO3 pins. The VREF node must be connected to VREFTA and VREFTB pins. The VREF supply is derived from the VDDQ\_VDDO supply using a resistive voltage divider.

3

TLK6002 Power Supply

#### TLK6002 High-Speed Data Path

www.ti.com

Figure 2. 1.5-V/1.8-V Power Supply Filtering and Decoupling Connections

# 1.5 Power Supply Ramp Order

No specific 1-V and 1.5-V/1.8-V power supply ramp order needs to be observed as long as the device provisioning includes the setting of register 28, bit 14 to enable normal CLK\_OUT\_P/N operation. However, it is generally recommended to ramp up DVDD before VDDQA/B.

# 1.6 AGND and DGND

AGND and DGND pins must be tied together on the application board.

# 2 TLK6002 High-Speed Data Path

# 2.1 Layout Recommendations for High-Speed Signals

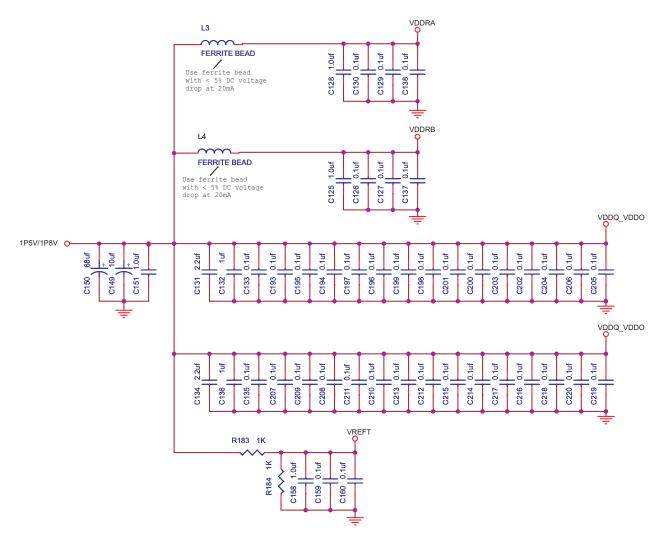

The high-speed data path CML input pins RXAP/RXAN and RXBP/RXBN, and the CML output pins TXAP/TXAN and TXBP/TXBN have to be connected with loosely coupled,  $100-\Omega$  differential transmission lines. Differential intra-pair skew needs to be minimized as much as possible to within ±1 mil. An example of FR-4 printed-circuit board (PCB) realization of such differential transmission lines in microstrip format is shown in Figure 3.

Figure 3. Differential Microstrip PCB Trace Geometry Example

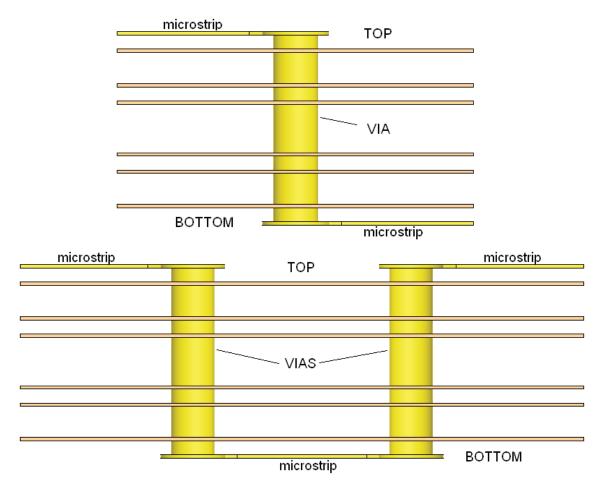

To avoid impedance discontinuities, the high-speed serial signals must be routed on a PCB on either the top or bottom PCB layers in microstrip format with no vias. If vias are unavoidable, an absolute minimum number of vias need to be used. The vias must be made to stretch through the entire PCB thickness (as shown in Figure 4) to connect microstrip traces on the top and bottom layers of the PCB so as to leave no via stubs that can severely impact the performance. If stripline traces are absolutely necessary, then the routing layers must only be one layer below the top layer and one layer above the bottom layer so as to minimize via stub length.

All unused internal layer via pads on high-speed signal vias must be removed to further improve impedance matching. RXAP/RXAN and RXBP/RXBN signals are more sensitive to impedance discontinuities introduced by vias than TXAP/TXAN and TXBP/TXBN signals. For that reason, if only some of those signals need to be routed with vias, then the latter must be routed with vias and the former with no vias.

Figure 4. High-Speed PCB Traces With Vias Having no Via Stubs and no Via Pads on Internal Layers

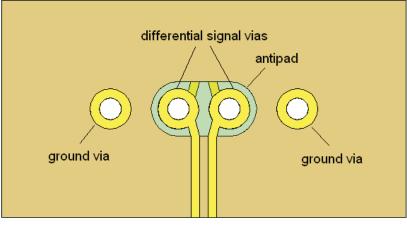

To further improve on impedance matching, differential vias with neighboring ground vias can be used as shown in Figure 5. The optimum dimensions of such a differential via structure depend on various parameters such as the trace geometry, dielectric material, as well as the PCB layer stack-up. A 3D electromagnetic field solver can be used to find the optimum via dimensions.

Figure 5. Differential PCB via Structure, Top View

PCB traces connected to the RXAP/RXAN and RXBP/RXBN pins must have at least 4 dB of differential insertion loss at 3 GHz. For the FR-4 material and 5-mil trace width, the PCB microstrip trace that meets that condition is at least 6 inches long.

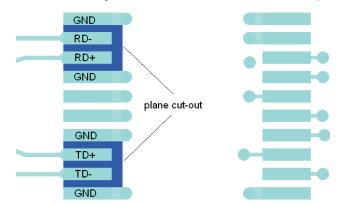

Surface-mount connector pads such as those used with the SFP/SFP+ module connectors are wider and hence have characteristic impedance that is lower than the regular high-speed PCB traces. If the pads are more than 2 times wider than the PCB traces, the pads' impedance needs to be increased to minimize impedance discontinuities. The easy way of increasing the pads' impedance is to cut out the reference plane immediately under those pads as shown in Figure 6 so as to have the pads refer to a reference plane on lower layers while maintaining  $100-\Omega$  differential characteristic impedance.

Figure 6. Reference Plane Cutout Under SFP/SFP+ Module Connector Pads

# 2.2 AC-Coupling

A 0.1-µF series ac-coupling capacitor must be connected to each of the high-speed data path pins RXAP, RXAN, RXBP, RXBN, TXAP, TXAN, TXBP, and TXBN. If the TLK6002 high-speed data path pins are connected to SFP/SFP+ optical modules, then no external ac-coupling capacitors must be used because the modules already have the required capacitors. Adding additional series capacitors may severely impact the performance.

To avoid impedance discontinuities, it is strongly recommended where possible to make the transmission line trace width closely match the ac-coupling capacitor pad size. Smaller capacitor packages such as 0201 make it easy to meet that condition.

# 3 TLK6002 Low-Speed Data Path

# 3.1 Layout Recommendations for Low-Speed Signals

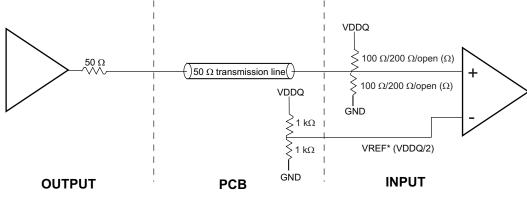

The low-speed data path HSTL input pins TDA\_[19:0] and TDB\_[19:0] and the HSTL output pins RDA\_[19:0] and RDB\_[19:0] have to be routed on a PCB as  $50-\Omega$ , single-ended transmission lines. The HSTL inputs and outputs can operate at 1.5 V or 1.8 V.

All TDA and TDB signals need to be length-matched with the respective TXCLK signals to within  $\pm 1$  mil. All RDA and RDB signals need to be length-matched with the respective RXCLK signals to within  $\pm 1$  mil.

The HSTL inputs and outputs have internal terminations that are dynamically calibrated to compensate for process, voltage, and temperature using four external reference resistors: RESRA, RESTA, RESRB, and RESTB. Each of those resistors needs to be 50  $\Omega$  with 0.5% tolerance. The internal terminations are as shown in Figure 7. While the 50- $\Omega$  series output termination is fixed, the parallel input terminations are selectable: 50  $\Omega$  or 100  $\Omega$  to (VDDQA/B)/2. The termination also can be disabled for lower power consumption but care has to be taken to maintain signal integrity. Because internal terminations are provided, external terminations on TDA, TDB, RDA, and RDB signals are not needed.

Figure 7. HSTL Output and Input Schematic

# 4 TLK6002 Clocks: REFCLK, CLK\_OUT, TXCLK, and RXCLK

# 4.1 General Information

The TLK6002 device requires a low-jitter reference clock to work. The reference clock can be provided on the REFCLK\_0\_P/N or REFCLK\_1\_P/N pins. Both reference clock input pins have internal 100- $\Omega$  differential terminations, so they do not need any external terminations. Both reference clock inputs must be ac-coupled with preferably 0.1- $\mu$ F capacitors. The two channels (A and B) can have same or different reference clocks. Refer to the TLK6002 data sheet for more information on reference clock selection.

The TLK6002 serial receiver recovers clock and data from the incoming serial data. The recovered byte clock is made available on the RXCLK\_A/B pins and can optionally be made available on the CLK\_OUT\_P/N pins. The CLK\_OUT\_P/N CML output pins must be ac-coupled with 0.1- $\mu$ F, ac-coupling capacitors.

# 4.2 External Clock Connections

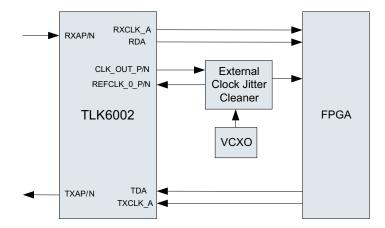

An external clock jitter cleaner, such as Texas Instruments CDCE72010 or CDCM7005, may be used when needed to provide a low-jitter reference clock. An example external clock jitter cleaner connection for channel A is shown in Figure 8.

Figure 8. External Clock Jitter Cleaner Connection Example for Channel A

Note that TXCLK\_A/B must be synchronous with REFCLK\_0/1\_P/N. The TXCLK\_A/B HSTL input pins (as well as all other HSTL input pins) already have selectable internal 50- $\Omega$  or 100- $\Omega$  to (VDDQA/B)/2 terminations; so, no external terminations are needed. The termination can also be disabled for lower power consumption but care has to be taken to maintain signal integrity.

RXCLK\_A/B HSTL output pins have internal 50- $\Omega$  series terminations, so external series terminations are not needed on those pins.

# 5 TLK6002 Control Pins and Interfaces

The TLK6002 device features a number of control pins and interfaces, some of which are described in the following paragraphs.

# 5.1 MDIO Interface

The TLK6002 supports the Management Data Input/Output (MDIO) Interface as defined in Clause 22 of the IEEE 802.3 Ethernet specification. The MDIO allows register-based management and control of the serial links. Normal operation of the TLK6002 is possible without use of this interface. However, some features are accessible only through the MDIO.

The MDIO Management Interface consists of a bidirectional data path (MDIO) and a clock reference (MDC). The port address is determined by the PRTAD[4:0] control pins (see Table 2-10 of the TLK6002 data sheet).

The MDIO pin requires a pullup to VDDO3. No pullup is needed on the MDC pin.

# 5.2 JTAG Interface

The JTAG interface is mostly used for device test. The JTAG interface operates through the TDI, TDO, TMS, TCK, and TRST\_N pins. If not used, all the pins can be left unconnected except TDI and TCK which have to be grounded.

# 5.3 SPI Interface

The SPI interface is not really used to control the TLK6002 device. It is provided only for compatibility with other devices in the same family as the TLK6002. The SPI interface operates through the SCL, SDO, SDI, and CS\_N pins. If not used, all the pins can be left unconnected except SDO, which has to be grounded.

## 5.4 Provisioning for System Debug

To allow easy system debug, PRBS\_EN, RATE\_B2, LOSA, RATE\_A2, and CODEA\_EN pins must each have a placeholder for a pullup resistor to VDDO (1.5 V/1.8 V) and a 0- $\Omega$  series resistor to physically isolate the pin from an external controller when needed. Additionally, GPI0 and TESTEN pins must have placeholders for pullup resistors to VDDO.

### 5.5 Unused Pins

As a general guideline, any unused HSTL or LVCMOS input pin needs to be grounded and any unused HSTL or LVCMOS output pin can be left unconnected. Unused CML differential output pins can be left unconnected. Unused CML differential input pins must be tied to ground through a shared  $100-\Omega$  resistor.

### 6 Summary

This document provides an overview of recommended board design considerations for successful integration of the TLK6002 device on system boards. See the TLK6002 data sheet for more information on device features and control.

## 7 References

TLK6002, Dual Channel 0.47Gbps to 6.25Gbps Multi-Rate Transceiver data sheet (SLLSE34)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                         | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                    | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and<br>Telecom | www.ti.com/communications         |

| DSP                         | dsp.ti.com             | Computers and<br>Peripherals  | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics          | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                        | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                    | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                       | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                      | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense     | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging             | www.ti.com/video                  |

|                             |                        | Wireless                      | www.ti.com/wireless-apps          |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated