# D-CAP+<sup>™</sup> Control for Multiphase, Step-Down Voltage Regulators for Powering Microprocessors

### Brian Cheng

### ABSTRACT

This application report introduces the basics of 3 generations of D-CAP+<sup>™</sup> multiphase step-down controllers. For the multiphase voltage regulators (VRs) powering microprocessors, fast load-transient performance is one of the most important specifications to ensure the performance of the microprocessors. This application report explains the benefits of using D-CAP+ control to achieve fast load-transient performance, while keeping good dynamic current sharing. The mathematical small-signal model of the 2nd-generation D-CAP+ control is also presented in this application report with considerations of adaptive voltage positioning (AVP). Two design examples are given to validate the model based on the designs with TPS53661 and TPS53667.

### Contents

|   |               | <b>Contonito</b>                                                 |    |  |

|---|---------------|------------------------------------------------------------------|----|--|

| 1 | Introdu       | iction                                                           | 1  |  |

|   | 1.1           | History of TI D-CAP+™ Step-Down Multiphase Controllers           | 2  |  |

| 2 | Basics        | of D-CAP+ <sup>™</sup> Control for Multiphase Converters         | 2  |  |

|   | 2.1           | Block Diagram                                                    | 2  |  |

|   | 2.2           | Phase Interleaving and Ramp Compensation                         | 4  |  |

|   | 2.3           | Adaptive Voltage Positioning                                     | 6  |  |

|   | 2.4           | Fast Load Transient Response with Variable Switching Frequencies | 7  |  |

|   | 2.5           | Dynamic Current Sharing                                          | 8  |  |

| 3 | Compe         | ensation Design for the 2nd-Generation D-CAP+ Control            | 9  |  |

|   | 3.1           | Mathematical Small-Signal Model Derivations                      | 9  |  |

|   | 3.2           | Design Examples With the TPS53661 and TPS53667 Devices           | 11 |  |

| 4 | Summ          | ary                                                              | 12 |  |

| 5 | References 12 |                                                                  |    |  |

|   |               |                                                                  |    |  |

## Trademarks

D-CAP+, D-CAP+ are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

# 1 Introduction

With growing demands on the mobile devices, the related infrastructures, such as servers, storage, or telecommunication equipment, are required to be upgraded with higher computing power, higher efficiency, and higher power densities. The microprocessors inside the equipment determine the computing power, and the voltage regulators (VRs) for powering these microprocessors are the key to improve its dynamic peformance, reliability, and efficiency with less costs and higher power densities. In order to fulfill the high-power requirements, multiphase VRs are required. Figure 1 shows the multiphase VRs used for servers.

Figure 1. Multiphase Voltage Regulators for Servers

# 1.1 History of TI D-CAP+<sup>™</sup> Step-Down Multiphase Controllers

TI offers three generations of D-CAP+ <sup>™</sup> step-down multiphase controllers for powering Intel processors and ASICs. Table 1 lists the comparisons of three generations.

| Functionality                        | 1st Generation                                           | 2nd Generation                                                                 | 3rd Generation                                                                            |

|--------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Output Channels                      | Single output                                            | Single output                                                                  | Dual outputs                                                                              |

| Maximum Phase Numbers Per<br>Channel | Up to 3 phases                                           | Up to 6 phases                                                                 | Up to 6 phases                                                                            |

| Current Sensing Methods              | Inductor DCR sensing                                     | Inductor DCR sensing or smart<br>power stage current sensing                   | Smart power stage current sensing                                                         |

| Mode Configurations                  | Pinstraps                                                | Pinstraps or Non-Volatile Memory<br>(NVM)                                      | Non-Volatile Memory (NVM)                                                                 |

| Temperature Sensing                  | NTC                                                      | NTC or smart power stage                                                       | smart power stage                                                                         |

| Loop Compensations                   | External components                                      | External components                                                            | Internal circuits                                                                         |

| Communication Interfaces             | Intel SVID™                                              | Intel SVID <sup>™</sup> and PMBus                                              | Intel SVID <sup>™</sup> and PMBus                                                         |

| Loadline Settings                    | External resistor without on-<br>the-fly programmability | External resistor with on-the-fly<br>programmability                           | Internal circuit with on-the-fly programmability                                          |

| Dynamic Phase<br>Adding/Shedding     | Not supported                                            | Support 1-2-4-6 phases                                                         | Support 1-2-3-4-5-6 phases                                                                |

| TI Product Family                    | TPS51623, TPS51631,<br>TPS53625, TPS53626                | TPS53640, TPS53640A,<br>TPS53631, TPS53641,<br>TPS53661, TPS53647,<br>TPS53667 | TPS53679, TPS53678,<br>TPS53659, TPS53659A,<br>TPS53658, TPS53622,<br>TPS53622A, TPS53681 |

# Table 1. Comparisons of 3 Generations of TI D-CAP+ Multiphase Controllers.

# 2 Basics of D-CAP+<sup>™</sup> Control for Multiphase Converters

# 2.1 Block Diagram

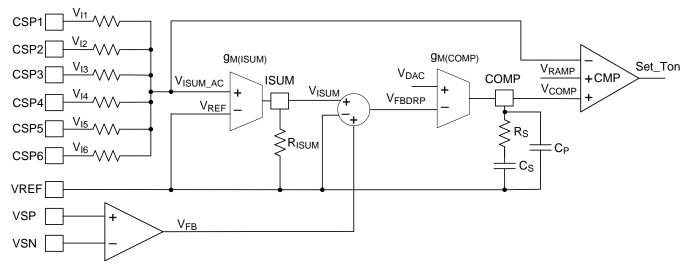

Figure 2 shows the 2nd-generation D-CAP+<sup>TM</sup> control block diagram being used in TPS53661 and TPS53667. The individual phase currents are sensed from TI smart power stages as  $V_{IX}$  and are averaged as  $V_{ISUM AC}$  as follows, which will be sent to the PWM modulator.

### Basics of D-CAP+<sup>™</sup> Control for Multiphase Converters

$$V_{ISUM\_AC} = \sum_{x=1}^{N} \frac{i_{Lx \times} R_{CS}}{6} + V_{REF}$$

where

- N is the total phase number

- i<sub>Lx</sub> is the per-phase inductor current

- $R_{cs}$  is the equivalent current sensing resistance from TI smart power stage, which is 5 m $\Omega$  (typ) •

- V<sub>REF</sub> is the internal reference voltage, which is 1.7V (typ)

In the meanwhile, the averaged phase currents can also be used to generate a droop voltage, VISUM, as shown in Equation 2.

$$V_{ISUM} = (V_{ISUM\_AC} - V_{REF}) \times g_{M(ISUM)} \times R_{ISUM} + V_{REF}$$

where

- RISUM is the external resistor put between the ISUM pin and the VREF pin

- g<sub>M(SUM)</sub> is the internal gain of the transconductance amplifier, which is 0.5mS (typ)

The compensation voltage, V<sub>COMP</sub>, is generated to regulate the feedback voltage with droop, V<sub>FBDRP</sub>, at the DAC voltage, V<sub>DAC</sub>.

$$V_{COMP} = (V_{DAC} - V_{FBDRP}) \times g_{M(COMP)} \times Z_{COMP} + V_{REF}$$

where

- Z<sub>COMP</sub> is the equivalent impedance to be put from the COMP pin to the VREF pin as the compensator

- g<sub>M(COMP)</sub> is the gain of the transconductance amplifier for the compensator, which is 1 mS (typ) (3) V

$$V_{\text{FBDRP}} = (V_{\text{ISUM}} - V_{\text{REF}}) + V_{\text{FB}}$$

(4)

(1)

(2)

Basics of D-CAP+<sup>™</sup> Control for Multiphase Converters

# 2.2 Phase Interleaving and Ramp Compensation

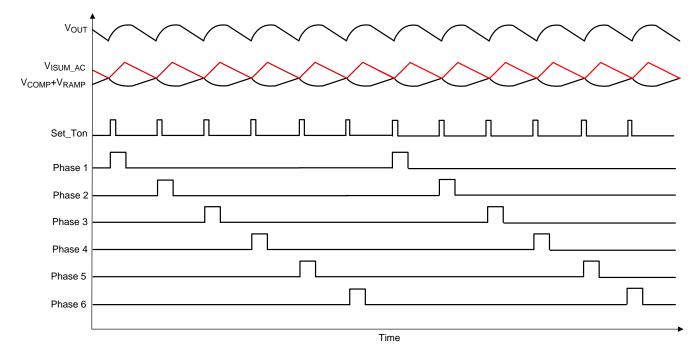

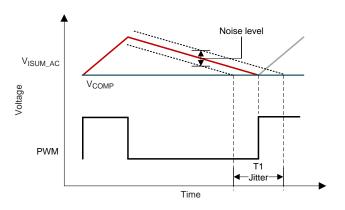

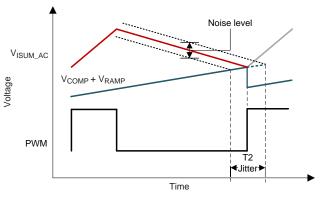

As shown in Figure 2, in addition to the compensation voltage,  $V_{COMP}$ , and the averaged current,  $V_{ISUM_AC}$ , there is also a ramp voltage,  $V_{RAMP}$ , to the PWM comparator. Figure 3 shows the operational waveforms of the D-CAP+ control at the steady-state conditions. Once the valley of the averaged current reaches the summation of the compensation voltage and the ramp voltage, a Set\_Ton signal is triggered to generate the PWM signal, and distributed to different phases based on phase management, to achieve phase interleaving for reducing input and output voltage and current ripples.

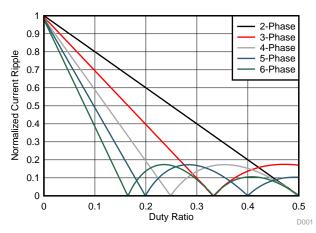

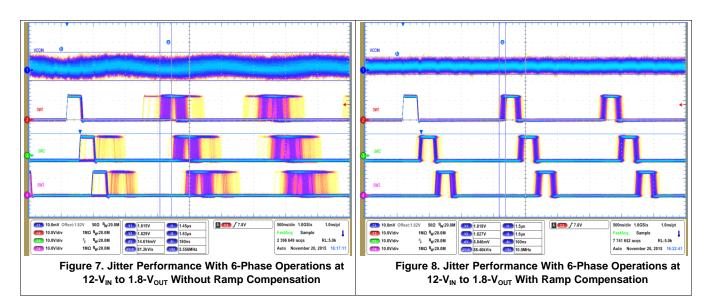

However, the averaged current ripple amplitude would be attenuated due to the ripple cancellation effect with multiphase operations depending on different duty ratios and different phase numbers, as shown in Figure 4. Therefore, a ramp voltage is generated as shown in Figure 5 and Figure 6 to improve the signal-to-noise ratio during operations to improve the jitter performance. Figure 7 and Figure 8 show the comparison of the jitter performance with and without ramp compensation for a 6-phase operation from 12-V input voltage to 1.8-V output voltage. Figure 7 and Figure 8 clearly show that the ramp compensation could effectively improve the jitter performance, especially when operating in multiphase operations. It should also be noted that the more ramp voltage is injected to the PWM comparator, the slower loop response would be expected, so the ramp voltage needs to be adjusted based on the actual operating conditions.

Figure 3. Operational Waveforms of D-CAP+<sup>™</sup> Control

Figure 4. Ripple Cancellation Effects With Different Operating Duty Ratios and Phase Numbers

Figure 5. Operation Without Ramp Compensation

Figure 6. Operation With Ramp Compensation

6

#### 1.85 VOUT 1.80 Output Voltage (V) 1.75 $R_{LL}$ 1.70 (Load Line Undershoot Margins 1.65 Tolerance Band $V_{\text{OUT}} \text{ (Min)}$ 1.60 V<sub>OUT</sub> (Тур) V<sub>OUT</sub> (Max) 1.55 IOUT 100 150 0 50 200 Slew Rate ≥ 800 A/µs Output Current (A)

Figure 10. Waveforms of the Loadline and Droop Voltage

#### 2.3 Adaptive Voltage Positioning

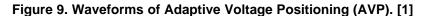

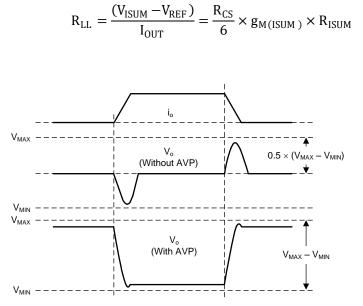

Due to the stringent load transient requirements for VRs powering the microprocessors, the concept of adaptive voltage positioning (AVP) has been proposed to reduce the output capacitance[1]. Figure 9 shows how to reduce the peak-to-peak voltage deviations by half during load transients with enabling AVP. To achieve the AVP design, the loadline is required to lower the output voltage with increasing load currents, as shown in Figure 10, and can be defined as shown in Equation 5.

$$V_{\text{DAC}} = V_{\text{OUT}} + I_{\text{OUT}} \times R_{\text{LL}} = V_{\text{FBDRP}}$$

where

R<sub>LL</sub> is the defined loadline. •

Derive the defined loadline for the 2nd-generation D-CAP+ control using Equation 1 through Equation 5, and adjust by changing the external R<sub>ISUM</sub> resistor as shown in Equation 6.

Copyright © 2019, Texas Instruments Incorporated

www.ti.com

(5)

(6)

Basics of D-CAP+™ Control for Multiphase Converters

# 2.4 Fast Load Transient Response with Variable Switching Frequencies

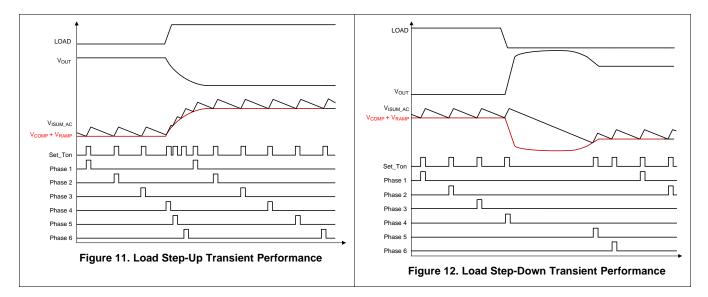

In the steady-state operations, D-CAP+ control can have a *pseudo* fixed-frequency operation for each phase by distributing PWM pulses. During load transients, D-CAP+ control can distribute PWM pulses faster to improve the load transient performance naturally. Figure 11 and Figure 12 show the operational waveforms during load transients. At load step-up transients, the Set\_Ton signals can be generated faster to provide more energy to the load, to reduce the undershoot voltage. On the other hand, at load step-down transients, the switching clock can be held off to discharge the load faster to reduce the overshoot voltage.

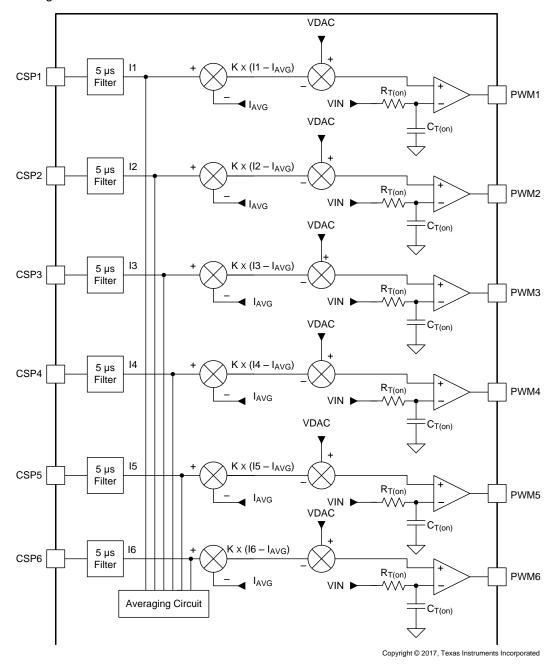

## 2.5 Dynamic Current Sharing

Current sharing performance is very important for the multiphase voltage regulator to balance thermal distributions among phases. Figure 13 shows the block diagram of dynamic current sharing implemented with the D-CAP+ control architecture. Only light filtering is added for each phase current, so the on-time for individual phases can be adjusted quickly to achieve superior dynamic current sharing performance even during load transients.

Figure 13. Current Sharing Block Diagram

### Compensation Design for the 2nd-Generation D-CAP+ Control

m

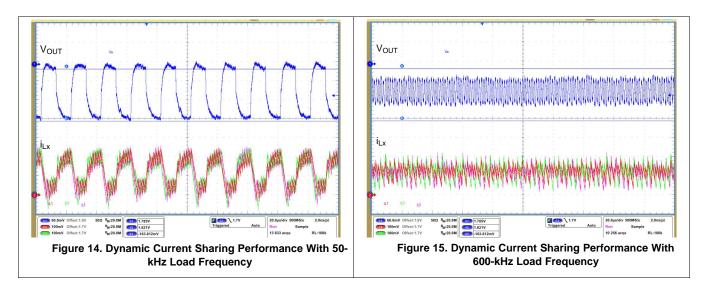

Figure 14 and Figure 15 show the current sharing waveforms with different load frequencies. As seen in Figure 14 and Figure 15, the phase currents can be balanced well under both low and high rep-rate load transients. In addition, due to the nature of the variable switching frequency characteristics mentioned previously, there is no beat-frequency oscillation issue when the load frequency is close to the switching frequency, as shown in Figure 15.

# 3 Compensation Design for the 2nd-Generation D-CAP+ Control

# 3.1 Mathematical Small-Signal Model Derivations

To design the compensators, the loop gain transfer function is required. As shown in Figure 2, the D-CAP+ control architecture consists of two loops[2]. The inner loop is the fast current loop with ramp compensation, and the control-to-inductor current transfer function can be derived as follows in *Equation 7*.

$$G_{c2iL}(s) = \frac{i_{SUM\_AC}(s)}{v_{COMP}(s)} \cong \frac{N}{R_{CS}} \times \frac{1}{\left(1 + \frac{s}{Q_1 \times \omega_1} + \frac{s^2}{(\omega_1)^2}\right)} \times \frac{1 + \frac{I_{SW}}{2 \times N} \times s}{1 + \left(\frac{s_e}{s_f} + \frac{1}{2}\right) \times \frac{T_{SW}}{N} \times s}$$

where

- Q1 = 2 /  $\pi$  and  $\omega$ 1 = N $\pi$  / T<sub>on</sub>

- $T_{ON}$  is the on-time

- T<sub>sw</sub> is the switching period

- s<sub>a</sub> is the slope of the ramp voltage

- s<sub>f</sub> is the down slope of the phase inductor current

(7)

9

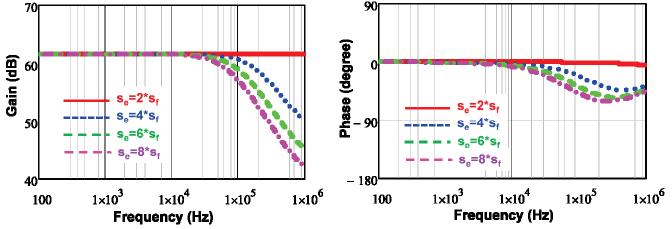

Figure 16 shows the frequency response of the derived control-to-inductor current transfer function with different ramp slopes. As shown in Figure 16, increasing the ramp slopes causes phase drops at high-frequency ranges, compared to an ideal current mode control system. Therefore, the guideline for ramp voltage selection is to have minimum ramp slopes with acceptable jitter performance, to ensure the loop performance.

Figure 16. Frequency Response of Control-to-Inductor Current Transfer Function of the Inner Loop

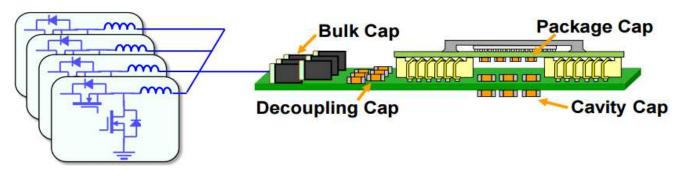

The second loop contains both the current loop for droop design and the voltage loop. The loop gain transfer function can be derived as shown in Equation 8

$$G_{LOOP}(s) = H_{COMP}(s) \times G_{c2iL2}(s) \times Z_{cap}$$

where

- Z<sub>cap</sub> is the equivalent impedance of the output capacitors, which consists of bulk capacitors, cavity capacitors, and the socket impedance for VRs, as shown in Figure 17.

- $H_{COMP}(s)$  is the transfer function of the compensator as follows.

$$H_{\text{COMP}(s)} = g_{\text{M}(\text{COMP})} \times Z_{\text{COMP}(s)}$$

(9)

(8)

$$G_{c2iL2}(s) = \frac{G_{c2iL}(s)}{1 + G_{c2iL}(s) \times R_{LL} \times H_{COMP}(s)}$$

(10)

Figure 17. Output Capacitors in the Power Delivery Path for VRs

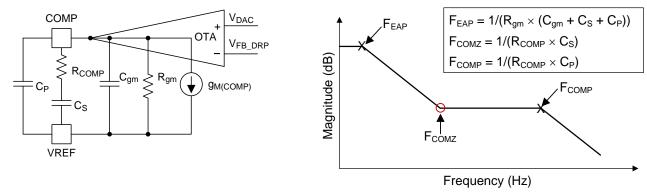

Figure 18 shows an example of a type II compensation network being put as  $Z_{COMP}$ , and its frequency response. The low-frequency pole is dominated by internal parasitics of the transconductance amplifier, such as  $C_{gm}$  and  $R_{gm}$ , and the zero is determined by the series resistor,  $R_{COMP}$ , and the series capacitor,  $C_{s}$ . The high-frequency pole for noise attenuation is dominated by  $R_{COMP}$  and the parallel capacitor,  $C_{P}$ .

Compensation Design for the 2nd-Generation D-CAP+ Control

# 3.2 Design Examples With the TPS53661 and TPS53667 Devices

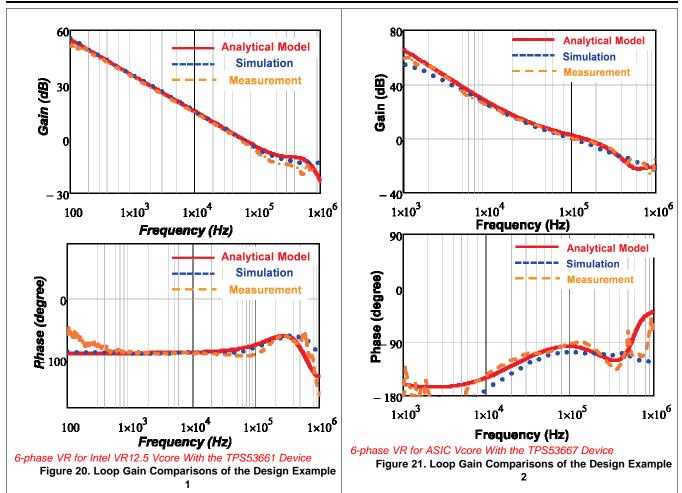

To verify the loop gain model, two design examples are provided in this application note. The first design example uses the TPS53661 device to design a 6-phase VR to power the Intel VR12.5 Vcore rail. The second design example uses the TPS53667 device to design a 6-phase VR to power the ASIC Vcore rail. Table 2 lists the design parameters of both examples. Based on the loop gain model from Equation 8, Equation 9, and Equation 10 the frequency response of the loop gain transfer function can be calculated. Figure 20 and Figure 21 show the comparisons of the frequency responses with the presented analytical model, simulation data, and measurement data. As shown in Figure 20 and Figure 21, the analytical model presented in this application note can predict the loop gain performance for the design.

| Parameters          | Design Example 1:<br>VR for Intel VR12.5 Vcore With the TPS53661 | Design Example 2:<br>VR for ASIC Vcore With the TPS53667     |

|---------------------|------------------------------------------------------------------|--------------------------------------------------------------|

| Input voltage       | 12 V                                                             | 12 V                                                         |

| Output voltage      | 1.8 V                                                            | 1.0 V                                                        |

| Phase numbers       | 6                                                                | 6                                                            |

| Inductor            | 150 nH                                                           | 150 nH                                                       |

| Output capacitors   | 4 × 470 μF / 3 mΩ<br>60 × 22 μF                                  | 4 × 470 μF / 4.5 mΩ<br>20 × 100 μF                           |

| Loadline            | 1.0 mΩ                                                           | 0 mΩ                                                         |

| Switching frequency | 650 kHz                                                          | 500 kHz                                                      |

| Ramp voltages       | 260 mV                                                           | 150 mV                                                       |

| Compensation        |                                                                  | $R_{COMP} = 8.06 kΩ$<br>$C_{S} = 1000 pF$<br>$C_{P} = 12 pF$ |

### **Table 2. Design Example Parameters**

www.ti.com

## 4 Summary

This application note summarized the features of the D-CAP+ control architecture used in multiphase VRs. The analysis of the control loop and its analytical model were also presented to help users design the compensator for different applications. Two design examples were presented to verify the effectiveness of the presented model.

## 5 References

- 1. K. Yao, Y. Ren, J. Sun, K. Lee, M. Xu, J. Zhou, and F. C. Lee, *Adaptive Voltage Position Design For Voltage Regulators*, in Proc. IEEE APEC'04 Conf., 2004, pp. 272 278.

- 2. K. Y. Cheng and Y. Su, Adaptive Voltage Positioning Design of Multiphase Constant On-time l<sup>2</sup> Control For Voltage Regulators With Ramp Compensations, in Proc. IEEE APEC'16 Conf., 2016.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated