Application Report SLVA938A–November 2017–Revised February 2018

# How to Design a Thermally-Efficient Integrated BLDC Motor Drive PCB

Cole Macias, David Vaseliou

#### ABSTRACT

This application report provides an in-depth discussion of thermal design for three-phase integrated BLDC motor drive PCBs in context of the DRV10987. Theoretical and experimental calculations for junction, ambient, and case temperature are discussed.

#### Contents

| 1 | Introduction                               |                                                                  |    |

|---|--------------------------------------------|------------------------------------------------------------------|----|

|   | 1.1                                        | Understanding the Thermal Model                                  | 2  |

| 2 | Understanding Sources of Power Dissipation |                                                                  |    |

|   | 2.1                                        | R <sub>DS(on)</sub>                                              | 3  |

|   | 2.2                                        | Switching Loss                                                   |    |

|   | 2.3                                        | Operating Supply Current Dissipation                             | 3  |

|   | 2.4                                        | Other Power Dissipation                                          | 4  |

| 3 | Understanding Thermal Resistance           |                                                                  |    |

|   | 3.1                                        | Simplified Model                                                 |    |

|   | 3.2                                        | Factors of Junction-to-Case Thermal Resistance ( $\theta_{CA}$ ) |    |

| 4 | Exam                                       | ple Calculations and Data                                        | 5  |

|   | 4.1                                        | Power Dissipated Example Calculation                             | 6  |

|   | 4.2                                        | Example: Board 1                                                 | 7  |

|   | 4.3                                        | Example: Board 2                                                 | 8  |

|   | 4.4                                        | Test Results Summary                                             | 8  |

| 5 | Guide                                      | elines for Optimizing Thermal Performance                        | 9  |

| 6 | Refer                                      | ences                                                            | 11 |

#### List of Figures

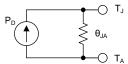

| 1 | Thermal Model to Electrical Model Schematic                    | 2  |

|---|----------------------------------------------------------------|----|

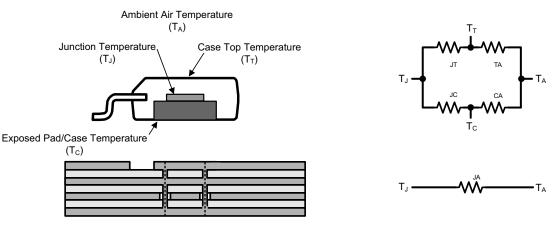

| 2 | Simplified Thermal Resistance Model for a Typical PCB          | 4  |

| 3 | Expanded Thermal Resistance Model for a Typical PCB            | 5  |

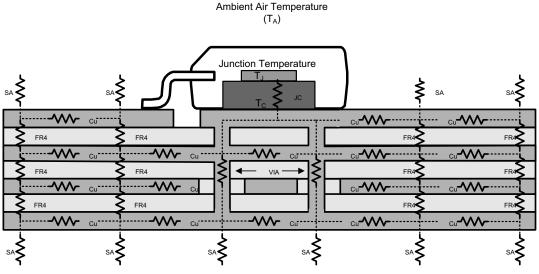

| 4 | Board 1 Thermal Image for Top of Case Temperature              | 7  |

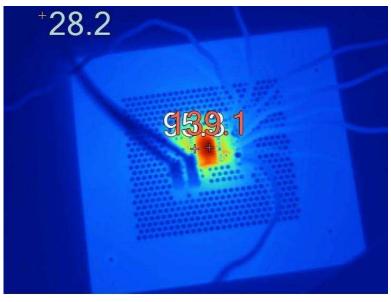

| 5 | Board 2 Thermal Image for Top of Case Temperature              | 8  |

| 6 | Thermal Simulation Data Comparing Board Size and Copper Weight | 10 |

| 7 | Hot Spot Created When a Break is Created in the Thermal Path   | 11 |

|   |                                                                |    |

#### List of Tables

| 1 | Board 1 Thermal Performance | 8 |

|---|-----------------------------|---|

| 2 | Board 2 Thermal Performance | 9 |

# Trademarks

All trademarks are the property of their respective owners.

1

#### 1 Introduction

For BLDC motor drive applications, temperature is often a critical design specification that cannot be violated. Specifically, cooling applications such as pedestal fans, ceiling fans, HVAC automotive seat blowers, washer and dryer fans, server fans, and refrigerator fans should try to dissipate heat as efficiently as possible. This allows for the lowest possible ambient ( $T_A$ ) and case ( $T_C$ ) temperature, in addition to, the lowest possible silicon die or junction temperature ( $T_J$ ) inside the device package. As previously mentioned, these temperatures are important because the ambient, case, and junction temperatures link to critical design specifications.

For the ambient and case temperature, the design specifications are often determined by the application. For example, dryer units deal with very hot ambient temperatures and a dryer fan motor drive circuit produces extra heat that contributes to the overall ambient temperature. As a result, a system used in a home-appliance dryer might design a dryer system that should not violate an ambient temperature of 65°C. In addition, some applications might have heat sensitive material (that is, waterproofing sealant) in close proximity to the motor drive circuits that are disrupted if the case temperature exceeds a certain temperature.

For junction temperature, many devices will not operate correctly if the minimum or maximum junction temperature specifications are violated. For example, the DRV10987 has a maximum junction temperature of 150°C in the absolute maximum ratings table of *DRV10987 12- to 24-V*, *Three-Phase, Sensorless BLDC Motor Driver*. While the DRV10987 has overtemperature protection that shuts down the device, this does not excuse good design practices which could prevent the overtemperature condition from occurring. In addition, motor drive applications are driven by design specifications such as output current. Since the current is directly correlated to the power dissipated, increasing the junction temperature, better thermal design allows for higher current with the same temperature.

### 1.1 Understanding the Thermal Model

Heat dissipation on a printed circuit board (PCB) can be broken down into a simple model that closely resembles the electrical circuit model. Specifically, the electrical circuit model is broken down to voltage (V), current (I), and resistance (R) through a simple relationship shown in Equation 1:

$V = I \times R$

The thermal model takes temperature (T), power dissipation (P), and thermal resistance ( $\theta$ ) and relates them to voltage, current, and resistance, respectively. This is shown in Equation 2.

$T = P \times \theta$

Figure 1. Thermal Model to Electrical Model Schematic

In Figure 1, the thermal model is represented in a schematic format to illustrate the typical conventions established by electrical circuit modeling. Since the ambient and junction temperature are represented as voltages, their difference is simply the sum of all dissipated power times the thermal resistance between the silicon die and the ambient air. This is represented in Equation 3.

$$T_{J} = P_{D} \times \theta_{JA} + T_{A}$$

(3)

(1)

(2)

### 2 Understanding Sources of Power Dissipation

Since there are multiple sources of power dissipation in a BLDC motor driver, their sum results in the total power dissipated in the circuit. This is used to calculate the junction temperature. While a short description is provided for each source of power dissipation, more information is found in *Calculating Motor Driver Power Dissipation*.

Equation 4 summarizes all sources of power dissipation.

$P_D \!=\! P_{RDS} + P_{SW} + P_{IVM} + P_{LDO}$

# 2.1 R<sub>DS(on)</sub>

The largest source of dissipated power inside a three-phase BLDC motor driver is the current flowing through the power MOSFETs. When the FETs are turned on, the high- and low-side FETs act as resistors ( $R_{DS(on)}$ ) that allow the current to flow from the supply to the terminal windings of the motor. The act of current flowing through the windings is what causes a magnetic field to develop and attract the permanent magnets on the rotor to cause motion. The power dissipated is represented by Equation 5.

$$P_{RDS} = 1.5 \times R_{DS(on)} \times (I_{OUT(RMS)})^2$$

Where:

- $R_{DS(on)}$  = sum of  $R_{DS(on)}$  for both the high- and low-side FETs

- I<sub>OUT(RMS)</sub> = RMS output current being applied to the motor windings (not to be confused with the supply current)

Since  $R_{DS(on)}$  increases as temperature increases, note that the lower the junction temperature and power dissipation from the FETs reduces the power dissipated.

In the case of the DRV10987, the typical  $R_{DS(on)}$  at  $T_A = 25^{\circ}$ C is 425 m $\Omega$  and the maximum continuous current is 2  $A_{(RMS)}$ . Since the DRV10987 is a three-phase BLDC motor driver with 180° sinusoidal control, all of the power MOSFETs and phase terminal windings have current flowing through them during operation. The sum of the phase shifted sinusoidal current waveforms equate to a constant power dissipation.

### 2.2 Switching Loss

For a three-phase BLDC driver, switching loss refers to the power dissipated when a transistor switches from high to low and low to high. Since three-phase BLDCs are controlled with PWM signals on the gates of the power MOSFETs, some power is dissipated every time the switching occurs. This is represented in Equation 6.

$$\mathsf{P}_{\mathsf{SW}} = \frac{\mathsf{V}_{\mathsf{M}}^2 \times \mathsf{I}_{\mathsf{OUT}(\mathsf{RMS})} \times \mathsf{f}_{\mathsf{SW}}}{\mathsf{SR}}$$

Where:

- $V_M$  = supply voltage that is supplied to motor, otherwise known as motor voltage

- I<sub>OUT(RMS)</sub> = RMS output current being applied to the motor windings (not to be confused with the supply current)

- f<sub>SW</sub> = switching frequency of the PWM signal

- SR = slew rate of the switching signal.

The DRV10987 has a maximum output current of 2  $A_{(RMS)}$  and can operate with a supply voltage from 6.2 V to 28 V. The PWM switching frequency is configured for 25 kHz or 50 kHz and the slew rate can be configured for 120, 80, 50, or 35 V/µs.

# 2.3 Operating Supply Current Dissipation

The driver consumes some current during operation. Note that the absence of a speed command can place the devices into sleep or standby to minimize current. However, the power dissipated calculations only rely on operation conditions. This is shown in Equation 7:

$$P_{IVM} = I_{VCC} \times V_M$$

Where:

- V<sub>M</sub> = supply voltage that is supplied to motor, otherwise known as motor voltage

- I<sub>VCC</sub> = active current during operation

The DRV10987 uses the specification called active current to quantify the amount of supply current consumed during operation. Note that the DRV10987 includes a step-down hysteretic voltage regulator that can operate with an external inductor or resistor. Depending on the component and mode used in the design, the active current is defined differently. Consult *DRV10987 12- to 24-V, Three-Phase, Sensorless BLDC Motor Driver* in the step-down regulator section for more information.

(7)

3

(5)

The typical value of the active current in the resistor mode is 13 mA, the maximum value is 16 mA.

# 2.4 Other Power Dissipation

Many motor drivers, including the DRV10987, have an LDO regulator that provides some current. The LDO offered on the DRV10987 outputs 3.3 V and more information is found in *DRV10987 12- to 24-V*, *Three-Phase, Sensorless BLDC Motor Driver*. This is represented in Equation 8:

$P_{LDO} = I_{LDO_OUT}(V_M - V_{OUT})$

(8)

Where:

- I<sub>LDO\_OUT</sub> = output current from the LDO with load

- $V_{M}$  = supply voltage that is supplied to motor, otherwise known as motor voltage

- V<sub>OUT</sub> = output voltage of the LDO

If the LDO is not outputting any current, ignore this power dissipation.

# 3 Understanding Thermal Resistance

For many semiconductor devices, the junction-to-thermal resistance is often given as a specification in the data sheet. For example, the DRV10987 shows  $\theta_{JA}$  is 36.1 °C/W. While this specification is based on data and JEDEC standards, the junction-to-thermal resistance does not account for real world factors and good thermal design like board thickness, use of a die attach pad (DAP) or power pad, copper thickness, vias, and breaks in the thermal path. These factors can reduce the thermal resistance making it easier for heat to uniformly dissipate and reduce the junction temperature.

# 3.1 Simplified Model

Figure 2. Simplified Thermal Resistance Model for a Typical PCB

As Figure 2 illustrates, the thermal model shows that the junction-to-ambient thermal resistance is but one component. However, the thermal resistance can be broken up into multiple parallel paths that make up all of the thermal resistance. In this case, a simplified version of the model is used.

Figure 2 shows that there are two paths for heat to travel from the junctions of the silicon: up towards the top of the case and down towards the power pad through the bottom of the PCB. This equivalent thermal resistance is found in Equation 9:

$$\theta_{\mathsf{J}\mathsf{A}} = (\theta_{\mathsf{J}\mathsf{T}} + \theta_{\mathsf{T}\mathsf{A}}) || (\theta_{\mathsf{J}\mathsf{C}} + \theta_{\mathsf{C}\mathsf{A}})$$

Where:

- $\theta_{JT}$  = junction-to-case (top) thermal resistance

- $\theta_{TA}$  = case (top) to ambient thermal resistance

- $\theta_{JC}$  = junction-to-case (power pad or equivalent path of least resistance) thermal resistance

- $\theta_{CA}$  = case (power pad or equivalent path of least resistance) to ambient thermal resistance (through PCB)

Equation 9 describes an important relationship for identifying the thermal resistance of the system.  $\theta_{JT}$ ,  $\theta_{TA}$ , and  $\theta_{JC}$  are all fixed values that cannot be influenced by the designer. However,  $\theta_{CA}$  can be greatly reduced applying good thermal design. Since the paths to the top and bottom of the case are in parallel, if the  $\theta_{CA}$  is reduced to a small enough value, ignore the path to the top of the case.

## 3.2 Factors of Junction-to-Case Thermal Resistance ( $\theta_{cA}$ )

As Figure 3 shows, there are many paths for heat to travel: through the copper plane laterally, vertically through thermal vias, through the vertical FR-4 laminate of the PCB, and radiating off the surface of the board to the ambient air. These paths are broken into parallel paths where the thermal resistance varies. As previously mentioned, it is important to make every path low resistance. As a result, higher resistance paths such as paths using the FR-4, contribute less to the overall  $\theta_{CA}$ .

Figure 3. Expanded Thermal Resistance Model for a Typical PCB

While these thermal resistances are modeled like resistors in an electrical circuit model, the modeled resistor network is complicated and may not perfectly model the board. Generally, vias and copper planes have a lower thermal resistance than the FR-4 laminate of the PCB. Equations and typical values for these factors are found in *AN-2020 Thermal Design By Insight*, *Not Hindsight*. However, the effects of these equations are summarized into general guidelines and design rules in Section 5 with supporting data in Section 4.

# 4 Example Calculations and Data

Before showing the typical calculations and data collection used in thermal analysis, the methods for finding the junction temperature must be discussed.

$$T_J = P_D \times \theta_{JA} + T_A$$

(10)

(11)

5

As previously mentioned, Equation 10 shows the very inaccurate and rough measurement that is typically used to calculate the junction temperature. This method does not take into account the effects of good thermal PCB design.

$T_J = P_D \times \Psi_{JT} + T_C$

SLVA938A–November 2017–Revised February 2018 How to Design a Thermally-Efficient Submit Documentation Feedback Copyright © 2017–2018, Texas Instruments Incorporated

**NOTE:**  $\theta_{JT}$ ,  $\theta_{TA}$ , and  $\theta_{JC}$  are all values that are widely known or found in the data sheet where  $\theta_{CA}$  is calculated.

**NOTE:** A useful  $\theta_{CA}$  and  $\theta_{JA}$  can be obtained through thermal modeling PCB simulation software. However, this modeling is usually provided as a service and associated as an extra cost during production.

#### Where:

- $\Psi_{JT}$  = junction to top of case characterization parameter

- T<sub>c</sub> = temperature at the top of the case

Equation 11 illustrates how junction temperature is calculated when measuring the temperature at the top of the case. Using the measured temperature at the top of the case and power dissipation, the characterization parameter  $\Psi_{JT}$  is taken from the data sheet to calculate the junction temperature.

While  $\theta_{JT}$  is often confused for  $\Psi_{JT}$  when doing the calculation, the use of junction to top of case thermal resisitance,  $\theta_{JT}$ , only works in context of Equation 9 and the modeling of the parallel paths discussed in Section 3.1 and Section 3.2.

The characterization parameter  $\Psi_{JT}$  is based on widely-adopted standards (JEDEC51-2). Furthermore,  $\Psi_{JT}$  estimates junction temperature based on experimental data instead of theoretical modeling. As a result, use  $\Psi_{JT}$  when the actual case temperature is measured. More information is found in *Semiconductor and IC Package Thermal Metrics*.

Note that the JEDEC standards were developed to help standardize sizes and layout for testing thermal metrics in most data sheets. Look for the verbiage indicating JEDEC standards when evaluating thermal metrics between different devices.

## 4.1 Power Dissipated Example Calculation

Assumptions for calculations are based on measured or typical and maximum electrical characteristic values:

- Two boards with two different devices were tested using the same HSOP package size to minimize thermal resistance error.

- Board 1 was not optimized for thermal performance where board 2 was optimized.

- Board 1 had a one-oz copper pour while board 2 had a two-oz copper pour.

- $V_{CC} = 19.6 \text{ V} \text{ and } T_{A\_Measured} = 24^{\circ}\text{C}.$

- For simplicity,  $I_{OUT(RMS)} = 2.9 A_{(RMS)}$  for both boards despite  $I_{OUT(RMS)-Board1} = 2.85 A_{(RMS)}$  and  $I_{OUT(RMS)-Board2} = 2.95 A_{(RMS)}$ . This introduces some error in favor of board 2.

- $R_{DS(on)}$  value assumes  $T_A = 25^{\circ}C$  where  $T_{A\_Measured} = 24^{\circ}C$ . This will introduce some error for both boards.

- Slew rate (SR) was set to 35 V/µs and the PWM frequency was set to 25 kHz.

- Both boards were in inductor mode. The maximum specification (15 mA) was used for margin.

- The LDO had no load in both experiments.

- The same motor was used with both boards in same environment to minimize error.

2

Calculating P<sub>RDS</sub>, more information is available in Section 2.1. Note 250 m $\Omega$  is the typical value for R<sub>DS(on)</sub> at T<sub>A</sub> = 25°C, as mentioned in the assumptions:

$$P_{RDS} = 1.5 \times R_{DS(ON)} \times (I_{OUT(RMS)})$$

$P_{RDS} = 1.5(250 \times 10^{-3}) \times (2.9)^{2}$

$P_{RDS} = 3.154$  W

Calculating P<sub>SW</sub>, more information is available in Section 2.2:

$$P_{SW} = \frac{V_{M}^{2} \times I_{OUT(RMS)} \times f_{SW}}{SR}$$

$$P_{SW} = \frac{(19.6)^{2} \times (2.9) \times (25 \times 10^{3})}{(35 \times 10^{6})}$$

$$P_{SW} = 0.796 \text{ W}$$

Calculating P\_{IVM}, more information is available in Section 2.3:  $P_{IVM} = I_{VCC} \times V_M$  (12)

(13)

| $P_{IVM} = (15 \times 10^{-3}) \times (19.6)$<br>$P_{IVM} = 0.294$ W             | (14) |

|----------------------------------------------------------------------------------|------|

| Calculating P <sub>LDO_OUT</sub> , more information is available in Section 2.4: |      |

| $P_{LDO} = I_{LDO_OUT}(V_M - V_{OUT})$                                           |      |

| $P_{LDO} = (0)((19.6) - (3.3))$                                                  |      |

| $P_{LDO} = 0 W$                                                                  | (15) |

| Calculating P <sub>D</sub> :                                                     |      |

| $P_{D} = P_{RDS} + P_{SW} + P_{IVM} + P_{LDO}$                                   |      |

| $P_D = (3.154) + (0.796) + (0.294) + (0)$                                        |      |

| $P_D = 4.244$ W                                                                  | (16) |

This value is used to calculate  $T_J$ .

# 4.2 Example: Board 1

To estimate the junction temperature (T<sub>J</sub>) of the device, we use both Equation 10 and Equation 11. As previously mentioned, Equation 10 is inaccurate as an estimation. In the previous section we calculated the power dissipated on board 1 as 4.244 W. From the data sheet,  $\theta_{JA}$  is 36.1°C/W and the  $\Psi_{JT}$  is 0.4°C/W. We use the measured value (157.5°C) of the top-of-case temperature when the device is dissipating 4.244 W for T<sub>c</sub>. Figure 4 shows the measured top-of-case temperature for board 1.

$$T_{J} = (P_{D} \times \theta_{JA}) + T_{A} = (4.244 \times 36.1) + 24$$

$$T_{J} = 177.2^{\circ}C$$

(17)

Where:

- T<sub>A</sub> = ambient temperature

- T<sub>J</sub> = junction temperature

- P<sub>D</sub>= power dissipated

- $\theta_{JA}$  = junction-to-ambient thermal resistance

- $T_J = (P_D \times \Psi_{JT}) + T_C = (4.244 \times 0.4) + 157.5$

Figure 4. Board 1 Thermal Image for Top of Case Temperature

(18)

#### 4.3 Example: Board 2

As with board 1, solving for T<sub>J</sub> with the same power dissipation at the same ambient temperature, the junction temperature equals 291.07°C. This is because Equation 10 does not take into account PCB layout thermal techniques.

As for Equation 11, the only change is the measured T c which is caused by thermal optimization techniques. Figure 5 shows the Top of Case temperature for Board 2.

$T_J = (P_D \times \Psi_{JT}) + T_C = (4.244 \times 0.4) + 139.1$

$T_{J} = 140.8^{\circ}C$

(19)

Figure 5. Board 2 Thermal Image for Top of Case Temperature

#### 4.4 Test Results Summary

8

Table 1 and Table 2 show the measured thermal performance of board 1 and board 2, respectively.

| Speed (RPM) | I RMS (A) | Voltage | Top of Case Temperature (°C) | Power (W) |

|-------------|-----------|---------|------------------------------|-----------|

| 6090        | 1.88      | 19.65   | 71.8                         | 36.942    |

| 6420        | 2.05      | 19.6    | 79.1                         | 40.18     |

| 6750        | 2.24      | 19.6    | 84.7                         | 43.904    |

| 7140        | 2.4       | 19.64   | 91.8                         | 47.136    |

| 7410        | 2.54      | 19.57   | 103.4                        | 49.7078   |

| 7800        | 2.68      | 19.6    | 118.0                        | 52.528    |

| 8190        | 2.78      | 19.6    | 132.4                        | 54.488    |

| 8460        | 2.85      | 19.6    | 157.5                        | 55.86     |

Table 1. Board 1 Thermal Performance

| Speed (RPM) | I RMS (A) | Voltage | Top of Case Temperature (°C) | Power (W) |

|-------------|-----------|---------|------------------------------|-----------|

| 6150        | 1.52      | 19.57   | 53.8                         | 29.746    |

| 6540        | 1.66      | 19.64   | 57.3                         | 32.602    |

| 6930        | 1.824     | 19.63   | 61.9                         | 35.8051   |

| 7230        | 1.975     | 19.55   | 67.1                         | 38.611    |

| 7650        | 2.12      | 19.56   | 74.7                         | 41.467    |

| 8010        | 2.24      | 19.57   | 81.4                         | 43.837    |

| 8220        | 2.38      | 19.57   | 91.3                         | 46.577    |

| 8490        | 2.54      | 19.55   | 102.6                        | 49.657    |

| 8820        | 2.65      | 19.5    | 115.9                        | 51.675    |

| 9150        | 2.78      | 19.43   | 123.4                        | 54.0154   |

| 9330        | 2.95      | 19.41   | 139.1                        | 57.318    |

| 9570        | 3.075     | 19.41   | 144.1                        | 59.686    |

#### Table 2. Board 2 Thermal Performance

As the calculated and measured results show, using good thermal optimization layout techniques provides significant improvements in thermal performance allowing for better efficiency and higher power consumption while driving a motor. The calculations also show how using Equation 10 can be inaccurate for estimating a junction temperature far greater than the thermal shutdown temperature. Using Equation 11 is a better estimate for the junction temperature resulting in a realistic junction temperature.

# 5 Guidelines for Optimizing Thermal Performance

Use the following recommendations as guidelines for designing the PCB for thermal testing or functional evaluation:

- Use a large and multi-layer PCB:

- Use Equation 20 to find the minimum recommended board size if  $\theta_{\text{JC}}$  is unknown:

Board Area

$$(cm^2) \ge 15.29 \quad \frac{cm^2}{W} \times P_D$$

Board Area  $(in^2) \ge 2.37 \quad \frac{in^2}{W} \times P_D$  (20)

– Use Equation 21 to find minimum recommended board size if  $\theta_{JC}$  is known:

Board Area  $(cm^2) \ge 500 \frac{\frac{\circ c \times cm2}{W}}{\theta_{JA} - \theta_{JC}}$

Board Area

$$(in^2) \ge \frac{77.5 \frac{W}{W}}{\theta_{JA} - \theta_{JC}}$$

- TI recommends using at least one-oz copper.

- Two-oz copper is recommended for designs that dissipate more than 3 W.

- Four-oz copper is recommended for designs that dissipate more than 6 W.

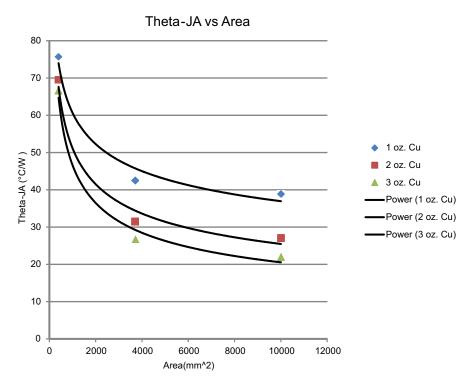

- Figure 6 shows the affects of board size and copper weight on thermal performance.

9

(21)

#### Figure 6. Thermal Simulation Data Comparing Board Size and Copper Weight

- Use thermal vias connecting the DAP landing pattern on the top layer, inter GND, and bottom GND layer in both DAP landing pattern and ground plane.

- Use Equation 22 to find the thermal resistance of vias.

$$\theta_{VIA} \frac{\frac{1}{\lambda_{Cu}} \times \text{Length}}{\pi \times [(\text{radius})^2 - (\text{radius} - \text{plating thickness})^2]}$$

(22)

- Design the thermal vias near the periphery of the exposed DAP if the maximum number of vias is not applicable.

- Use 0.33-mm diameter vias if possible, especially for packages with small exposed pad, which may reduce  $\theta_{IA}$  approximately 15% to 25%.

- Generate as large a GND plane as allowable on the top and bottom layers, especially near the package.

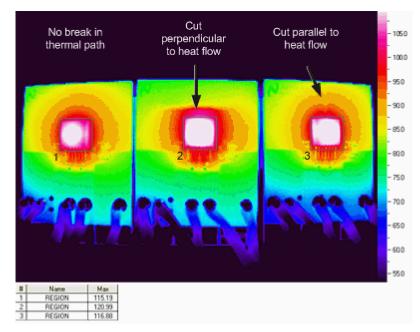

- Generate with as few breaks as possible to create a heat spreader on the PCB.

- Connect the top GND pattern with the DAP landing pattern underneath the package.

- Gather the same functional pins together in die design, such as for GND,  $P_{VIN}$ ,  $P_{OUT}$  in the power device. This allows maximizing the Cu area near the package by eliminating the needs for isolating each lead pattern on the PCB.

- Make the traces as long as possible, achieving better thermal conductivity near the package.

- Do not run traces parallel to the board edge, this blocks thermal path edges of the board ٠

Figure 7. Hot Spot Created When a Break is Created in the Thermal Path

#### 6 References

- 1. DRV10987 Product Folder: http://www.ti.com/product/DRV10987

- 2. Texas Instruments, Calculating Motor Driver Power Dissipation Application Report

- 3. Texas Instruments, AN-2020 Thermal Design By Insight, Not Hindsight Application Report

- 4. Texas Instruments, Semiconductor and IC Package Thermal Metrics Application Report

### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (November 2017) to A Revision

| • | Changed Equation 5.                                                                              | 3 |

|---|--------------------------------------------------------------------------------------------------|---|

| • | Added thermal modeling PCB simulation software note.                                             | 5 |

| • | Added last bullet in the Power Dissipated Example Calculation section.                           | 6 |

|   | Changed Equation 12.                                                                             |   |

| • | Changed Equation 13.                                                                             | 6 |

|   | Changed 7.398 W to 4.244 W in the Example: Board 1 section and made appropriate equation changes |   |

| • | Changed Equation 18.                                                                             | 7 |

| • | Changed Equation 19.                                                                             | 8 |

|   |                                                                                                  |   |

Page

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated