## Getting Started in C and Assembly Code With the TMS320LF240x DSP

David M. Alter

DSP Applications - Semiconductor Group

#### **ABSTRACT**

This application report presents basic code for initializing and operating the TMS320LF240x<sup>†</sup> DSP devices. Two functionally equivalent example programs are presented: one written in assembly language and the other in C language. Detailed discussions of each program are provided that explain numerous compiler and assembler directives, code requirements, and hardware-related requirements. The programs are ready to run on either the TMS320LF2407 Evaluation Module (EVM) or the eZdsp™ LF2407 development kit. However, they are also intended for use as a code template for any TMS320LF240x<sup>†</sup> (LF240x) or TMS320LF240xA<sup>†</sup> (LF240xA) DSP target system. The sample code described in this application report can be downloaded from <a href="http://www.ti.com/lit/zip/SPRA755">http://www.ti.com/lit/zip/SPRA755</a>.

#### Contents

| 1    | Introduc                   | ction                                                                           | 2  |  |  |  |  |  |  |  |  |

|------|----------------------------|---------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 2    | 2.1 LF2                    | re Setup<br>2407 EVM Setup                                                      | 2  |  |  |  |  |  |  |  |  |

|      | 2.2 eZd                    | dspE LF2407 Setup                                                               | 3  |  |  |  |  |  |  |  |  |

| 3    | Using th                   | sing the Code Composer GEL File                                                 |    |  |  |  |  |  |  |  |  |

| 4    | Overvie                    | w of the Example Programs                                                       | 4  |  |  |  |  |  |  |  |  |

| 5    |                            | oly Language Example Program                                                    |    |  |  |  |  |  |  |  |  |

| 6    | C Language Example Program |                                                                                 |    |  |  |  |  |  |  |  |  |

| 7    | Conclusion                 |                                                                                 |    |  |  |  |  |  |  |  |  |

| 8    | Referen                    | ces                                                                             | 20 |  |  |  |  |  |  |  |  |

| Арр  | endix A                    | Assembly Language Example Program Listing                                       | 21 |  |  |  |  |  |  |  |  |

| Арр  | endix B                    | C Language Example Program Listing                                              | 30 |  |  |  |  |  |  |  |  |

| Арр  | endix C                    | Addendum to Getting Started in C and Assembly Code With the 23 TMS320LF240x DSP | 30 |  |  |  |  |  |  |  |  |

|      |                            | List of Figures                                                                 |    |  |  |  |  |  |  |  |  |

| Figu | ıre 1                      | Assembly Language Example Program Code Flow                                     | 7  |  |  |  |  |  |  |  |  |

| Figu | ıre 2                      | C Language Example Program Code Flow                                            | 14 |  |  |  |  |  |  |  |  |

$eZdsp\ is\ a\ trademark\ of\ Spectrum\ Digital\ Incorporated.$

TMS320C24x is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

<sup>&</sup>lt;sup>†</sup> Go to http://www.ti.com for a complete list of TMS320C24x<sup>™</sup> devices.

#### 1 Introduction

A hurdle often faced by code developers working with an unfamiliar DSP is knowing how to get started. A good example program that illustrates proper DSP initialization, interrupt handling, and peripheral operation can be invaluable. This application report presents basic code for initializing and operating the TMS320LF240x devices. Although the code herein is designed to run on either the TMS320LF2407 Evaluation Module (EVM) or the eZdsp™ LF2407 development kit, it is also applicable, and intended for use, as a code template for any TMS320LF240x (LF240x) or TMS320LF240xA (LF240xA) DSP target system.

This application report presents two functionally equivalent example programs: one written in assembly language, and the other written in C programming language. A reader who possesses an understanding of one of these two languages can compare the two programs to understand the coding in the other language. The philosophy behind the code examples is to keep them as simple and clear as possible. Therefore, only a few of the numerous peripherals on the LF2407 DSP are exercised. The assumption is that once the basic coding techniques for configuring a peripheral register are illustrated, the reader can easily duplicate the code to configure any other peripheral.

In addition to the example programs, two complete header files are provided that define the addresses of all user-programmable registers on the LF2407 DSP: one for assembly code and the other for C code. Finally, a Code Composer™ v4.1x gel file is provided (along with usage instructions) that conveniently places all LF2407 peripheral registers into a Code Composer menu for easy inclusion into a debugger watch window.

## 2 Hardware Setup

The example programs in this application note are designed to run out-of-the-box on either the LF2407 EVM or eZdsp™ LF2407. If you do not have one of these boards, all of the benefits of the example programs are still available to you. You simply may not be able to run the programs without making modifications to them for your particular target board.

### 2.1 LF2407 EVM Setup

The example programs are ready to run on the LF2407 EVM board without any modification. It is assumed that the reader already has the EVM board, an emulator (e.g., XDS510PP-plus from Spectrum Digital Inc. or XDS510) and a debugger (e.g., Code Composer v4.10 or v4.12) installed on a PC and ready to go. It is beyond the scope of this application report to provide direction on tools installation. Please see the installation instructions that came with the tools for assistance with this.

Numerous jumpers exist on the EVM board. The following are jumper setting requirements for proper operation of the example programs:

JP5: This jumper controls the voltage level of the VCCP pin on the DSP. Normally, leave it in the 1–2 position. If you want to program the FLASH with the example program, set to the 2– 3 position during FLASH programming. It is good practice to return it to the 1–2 position after FLASH programming.

Code Composer is a trademark of Texas Instruments.

- JP6: This jumper controls the voltage level of the MP/MC pin on the DSP. Normally, set to the 1–2 position to use the external RAM in place of the internal FLASH. Set to the 2–3 position if you want to program the FLASH with the example program, and leave in the 2–3 position to run the program out of the FLASH after it is programmed.

- JP13: Set to the 1–2 position. This uses the clock oscillator on the EVM board.

- JP16: Set to the 1–2 position. This disables bootloading.

All other jumper settings are don't cares for the example programs, since those jumpers affect peripherals that are not used here (e.g., CAN, SPI, ADC, or SCI). Additional information on these jumpers can be found in reference [7].

The LF2407 EVM is assumed to contain a 7.3728 MHz on-board oscillator. The example programs configure the DSP phase-locked loop (PLL) for multiply-by-four mode, which gives a CPU clock of 29.49 MHz (i.e., 30 MHz). The values stated in this report for the PWM carrier frequency, GPIO toggle period, and LED bank update rate have been computed assuming a 30 MHz CPU clock. If a different oscillator value is used, these values will be different. In addition, one must be careful not to exceed the rated clock speed of the DSP in use (30 MHz for current LF240x devices or 40 MHz for current LF240xA devices). Some early LF2407 EVM boards used 15 MHz oscillators that exceed the 30 MHz DSP rating if multiplied by four with the PLL. All you need to do in this situation is edit the example programs so that the PLL is configured for multiply-by-two mode instead. This setting is selected by bits 11-9 in the SCSR1 register. These bits are currently written as 000b. Change these to 001b to get the multiply-by-two PLL (see discussions for program lines 114 and 572 in sections 5 and 6, respectively, of this document). Also, some of the newest EVMs may have been fitted with a 40 MHz LF2407A DSP and use a 10 MHz oscillator. No program change is necessary here, although again timing values for the PWM, GPIO toggle, etc., will differ from those stated in this report (i.e., they will be 33% faster). For more information on the PLL and the SCSR1 register, see reference [2], pages 2–3 to 2–5.

### 2.2 eZdsp™ LF2407 Setup

The example programs are ready to run on the eZdsp™ LF2407 board (henceforth referred to as eZdsp™) without any modification. It is assumed that the reader already has the eZdsp™ and its debugger software installed and ready to go. It is beyond the scope of this application report to provide direction on tools installation. Please see the installation guide that came with the tools for assistance with this.

Several jumpers exist on the eZdsp™ board. The following are jumper setting requirements for proper operation of the example programs:

- JP3: This jumper controls the voltage level of the VCCP pin on the DSP. Normally, leave it in the 1–2 position. If you want to program the FLASH with the example program, set to the 2– 3 position during FLASH programming. It is good practice to return it to the 1–2 position after FLASH programming.

- JP4: This jumper controls the voltage level of the MP/MC pin on the DSP. Normally, set to the 1–2 position to use the external RAM in place of the internal FLASH. Set to the 2–3 position if you want to program the FLASH with the example program, and leave in the 2–3 position to run the program out of the FLASH after it is programmed.

All other jumper settings are don't cares for the example programs, since those jumpers affect the ADC peripheral and the ADC is not used by the example programs. Additional information on these jumpers can be found in reference [8].

The eZdsp™ is assumed to contain a 14.7 MHz on-board oscillator. The on-board FPGA then implements a divide-by-two, such that a 7.35 MHz clock signal is ultimately fed into the LF2407 DSP. The example programs configure the DSP phase-locked loop (PLL) for multiply-by-four mode, which gives a CPU clock of 29.4 MHz (i.e., 30 MHz). The values stated in this report for the PWM carrier frequency, GPIO toggle period, and LED bank update rate have been computed assuming a 30 MHz CPU clock. If a different oscillator value is used, these values will be different. In addition, you must be careful not to exceed the rated clock speed of the DSP in use (30 MHz for current LF240x devices, or 40 MHz for current LF240xA devices). For example, if you are using a 30 MHz oscillator instead of the standard 14.7 MHz one, using the multiply-by-four PLL mode would exceed the 30 MHz frequency rating of the LF2407 DSP. All you need to do in this situation is edit the example programs so that the PLL is configured for multiply-by-two mode instead. This setting is selected by bits 11-9 in the SCSR1 register, and these bits are currently written as 000b. Change these to 001b to get the multiply-by-two PLL (see discussions for program lines 114 and 572 in sections 5 and 6, respectively, of this document). For more information on the PLL and the SCSR1 register, see reference [2], pages 2-3 to 2-5.

## 3 Using the Code Composer GEL File

The file *If2407.gel* is provided with this application report download. This is a script file containing startup instructions for TMS320C2xx Code Composer v4.1x. Specifically, it has been tested with v4.10 and v4.12 of this debugger. When installed with Code Composer, it causes all LF2407 DSP peripheral registers to be listed on the GEL menu inside Code Composer. When a particular register is selected on this menu (e.g., by clicking on it with your PC mouse), that register is added to the WATCH WINDOW inside Code Composer. This functionality is a useful aid during code debug, and avoids having to fumble through the user's guide to look up register addresses. Note that the peripheral set of the LF2407 DSP is a superset of all other current 240x and 240xA devices. Therefore, this gel file is usable with any 240x or 240xA target.

To use the gel file with Code Composer, place the file in the C:\tic2xx\cc\gel directory on your PC (assuming you used the default installation paths when you installed Code Composer). Then, right-click on the shortcut (or Windows 95/98 Start menu item) that you use to invoke Code Composer. Select Properties, and then click on the Short Cut menu. The Target: box on this menu should show the following (again assuming default installation paths):

C:\tic2xx\cc\bin\cc app.exe C:\tic2xx\cc\gel\init.gel

To use the If2407.gel file, simply change the Target: box to read:

C:\tic2xx\cc\bin\cc app.exe C:\tic2xx\cc\gel\lf2407.gel

## 4 Overview of the Example Programs

There are two functionally identical programs provided. The first is written in TMS320C2xx DSP assembly language, while the second is written in C programming language. Each example program has been tested on both the LF2407 EVM and the eZdsp™ LF2407. Code generation was performed using the TMS320C2x/C2xx/C5x Code Generation Tools PC v7.00, with C2xx Code Composer Software Package PC v4.12 as the debugger. The C example program was tested with compiler optimization disabled, and also with level 3 (–o3) optimization.

Each example program performs the following tasks on the DSP:

- Configures the two System Control and Status registers

- Disables the Watchdog Timer

- Configures the external memory interface

- Configures the shared device pins

- Configures GP Timer 1 and the compare units to provide 20KHz, 25% duty cycle symmetric PWM on the PWM1 pin. This can be observed by connecting an oscilloscope to the PWM1/IOPA6 signal located on the EVM and eZdsp™ signal headers.

- Configures GP Timer 2 to provide a 250ms interrupt

- Configures the core and event manager interrupt registers, and enables global interrupts

- In the GP Timer 2 interrupt service routine, the following is performed:

- Context save/restore using a software stack

- The quad LED bank on the EVM is sequenced (250 ms update rate). This is visible only on the EVM, since the eZdsp™ does not have the quad LED bank. However, no modifications to the program are necessary for operation on the eZdsp™. The LED update instructions produce a benign write to I/O space on the external memory interface of the DSP when using the eZdsp™.

- The IOPC0 pin is toggled, producing a 2 Hz (500ms) square wave. On the EVM, the IOPC0 pin is connected to the red LED labeled DS1 on the board. On the eZdsp™, the IOPC0 pin is connected to the red LED labeled DS2 on the board. Users can visually see the pin toggle by observing the LED. Alternately, an oscilloscope can be connected to the W/R/IOPC0 pin on the EVM and eZdsp™ signal headers.

In addition, the example programs illustrate the following concepts:

- How to work with multiple files

- How to work with multiple code sections

- How to write an interrupt service routine using either C or assembly language

- How to insert inline assembly code into a C language program

- How to access the I/O space using either C or assembly language

- How to access peripheral registers using either C or assembly language

- How to use include files

- Complete core interrupt vector tables for C and assembly language programs

- Example LF2407 DSP linker command files for both C and assembly language programs

Finally, note that besides running from external memory, each example program can be programmed into the internal FLASH memory on the LF2407 DSP and run out of the FLASH on either the LF2407 EVM or the eZdsp™ LF2407, without the need for any file modifications.

## 5 Assembly Language Example Program

The assembly language example program consists of the following files:

- vectors.asm: Interrupt vector table

- example.asm: Main program

- **f2407.h**: Header file containing peripheral register address definitions

- example.cmd: Linker command file

- example.mak: C2xx Code Composer v4.1x project file

- example.out: Program executable

- **example.map**: Memory map file output by the code generation tools

Only the first five listed files are needed to build the program. The final two files are provided for convenience, and are produced by the code generation tools when the program is built. To build the project using Code Composer, load the project file *example.mak* into Code Composer (click on PROJECT—>OPEN), and then select PROJECT—>BUILD or PROJECT—>REBUILD ALL. See the online help available within Code Composer for additional assistance.

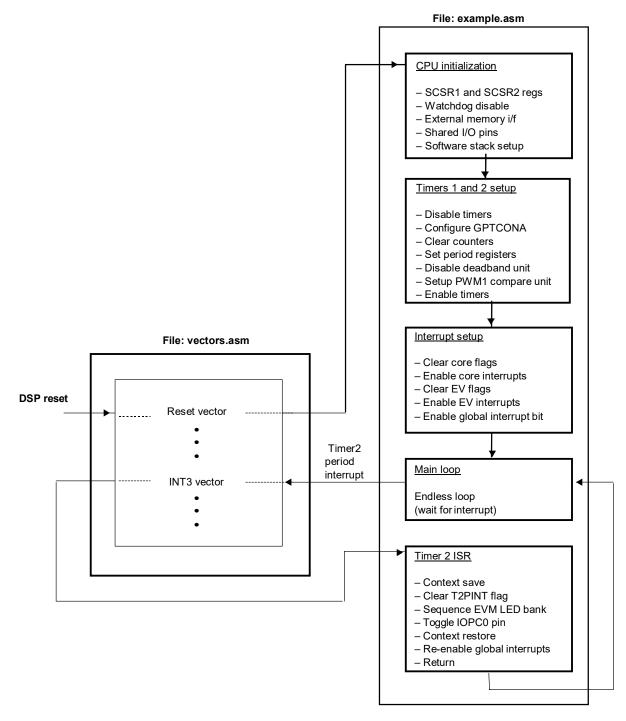

Figure 1 illustrates the code flow for the assembly language example program. Execution begins at the reset vector in the file *vectors.asm* after a hardware reset. This vector branches to the start of the main program in the file *example.asm*. Processor initialization is then performed, after which an endless main loop is entered. The DSP is periodically interrupted out of this endless loop by the timer 2 period interrupt, at which time the interrupt service routine is executed.

Appendix A contains file listings of *vectors.asm*, *example.asm*, and *example.cmd*. Contiguous line numbers have been provided along the left-hand side of the code to facilitate discussion. The assembly instructions used in the code are documented in reference [1], and it is beyond the scope of this application report to provide detailed explanations of the instruction mnemonics and syntax. However, a number of details and useful pieces of information will now be discussed.<sup>1</sup>

**Line 1** (*vectors.asm*): The asterisk in column 1 indicates that the entire line is a comment. The asterisk can only be used in column 1. To place a comment in a line beginning at a different column, use a semi-colon, as shown in line 16.

**Line 13** (*vectors.asm*): The .ref directive is used to reference symbols defined externally to a source file. In this case, the symbols "start" and "timer2\_isr" are both declared in the file *example.asm*, but are referenced here in *vectors.asm*. The .ref directive is the complement of the .def directive (see Line 69 below). The .ref directive is documented in reference [4], page 4–44.

**Line 15** (*vectors.asm*): The .sect directive is used to declare an initialized section. In this case, the interrupt vectors (code) are being placed in the section named "vectors" so that they can be linked to a specific address range. You can find the vectors section listed in the SECTIONS portion of the linker command file *example.cmd*.

Cited page and section numbers in references correspond to the specific revision of the documentation listed in the Reference section of this

application report. These numbers have been given as a matter of convenience, but may no longer be accurate if a new revision of the

documentation is released. The referenced material itself, however, should still be found in the cited document. See the index in the cited

document to find the correct page for the referenced subject.

Figure 1. Assembly Language Example Program Code Flow

Lines 16 - 47 (vectors.asm): Each interrupt vector is two 16-bit words long and contains a single branch instruction that indicates the address of the interrupt service routine (ISR) associated with it. Line 16 is the reset vector. It branches to the label start located at the beginning of the main program in example.asm. Line 19 is the core interrupt 3 vector. This core interrupt is shared between several peripheral interrupts, among them the timer 2 period interrupt. In this example program, the timer 2 period interrupt is the only interrupt enabled on core interrupt 3. Therefore, the interrupt 3 vector can branch directly to the timer 2 interrupt service routine, located at the label timer2 isr in example.asm. If more than one peripheral interrupt is enabled on a given core interrupt line, the software needs to differentiate among the peripheral interrupts so that the correct ISR is executed. The procedure for doing this is discussed in reference [2], pages 2–20 to 2–21. The core interrupt vector addresses are documented in reference [1], pages 5–15 to 5–16. The sharing of the core interrupts is documented in reference [5], pages 20 to 23. Note that all remaining interrupt vectors branch to themselves. This is useful during code development to trap erroneous interrupts. In a real application, one would probably want to branch all unused interrupts to an error-handling routine that performs whatever recovery steps are desired.

**Line 69** (example.asm): The .def directive is used to make symbols declared in a source file visible to code in other files. In this case, the labels "start" and "timer2\_isr" are both declared here in the file example.asm, but are referenced in vectors.asm. The .def directive is the complement of the .ref directive (see Line 13 above). The .def directive is documented in reference [4], page 4–44.

**Line 74 (example.asm):** The .include directive is used to import a file directly into your source code at assembly time. In this case, the address definition file *f2407.h* is being included. The file *f2407.h* contains address definitions for all of the peripheral registers in the LF2407 DSP. The .include directive is documented in reference [4], page 4–29.

**Line 76 (example.asm):** The .set directive is used to define a constant in assembly code. The assembler replaces all occurrences of the constant within the source file with the specified value. The .set directive is documented in reference [4], page 4–67.

**Lines 76 – 82 (example.asm):** The .set directive is being used here to define the addresses in external I/O space of the D/A converter, DIP switch bank, and quad LED bank found on the LF2407 EVM (the eZdsp™ LF2407 does not contain any of these features). Note that only the quad LED bank is exercised by the example program (has no effect on eZdsp™ LF2407). Additional information on these EVM features can be found in reference [7].

**Lines 98 – 99 (example.asm):** The .bss directive is used to allocate space for uninitialized variables in the .bss section. In this case, 1 word (16-bits) is being allocated for the variable temp1, and 1 word is being allocated for the variable LED\_index. You can find the .bss section listed in the SECTIONS portion of the linker command file *example.cmd*. The .bss directive is documented in reference [4], page 4–25.

Note that uninitialized variables can also be allocated using the .usect directive, which allows their placement into named sections other than .bss. The .bss directive is nothing but a special case of the .usect directive, and is used mostly for convenience. For example, the following two lines of code are equivalent:

```

.bss temp1, 1 ;reserve 1 word in .bss section

temp1 .usect ".bss", 1 ;reserve 1 word in .bss section

```

The .usect directive is documented in reference [4], page 4–67. An example of .usect, used in this example program, may be found at Line 252.

**Line 106** (*example.asm*): The .text directive is used to signify that the code (or initialized data) which follows is to be placed into the .text section. You can find the .text section listed in the SECTIONS portion of the linker command file, *example.cmd*. The .text directive is documented in reference [4], page 4–75.

Note that code and/or initialized data sections other than .text can be declared using the .sect directive. The .text directive is nothing but a special case of the .sect directive, and is used mostly for convenience. For example, the following two lines of code are equivalent:

```

.text ; code that follows goes in .text section

.sect ".text" ; code that follows goes in .text section

```

The .sect directive is documented in reference [4], page 4–66.

**Line 107** (example.asm): The label "start" is being used to mark the beginning of the main program. The reset vector in vectors.asm (see Line 16 above) branches here. Note that all labels must begin in column 1 in an assembly source file. The colon following the label is optional.

**Line 112** (example.asm): The LDP instruction is used to set the data page for instructions using the direct-addressing mode that follow it. The assembler constant DP\_PF1 is defined in the include file *f*2407.*h*.

**Line 114** (example.asm): The SPLK instruction is used to load a number into a data space address. In this case, the address corresponds to the SCSR1 register. Since the constant SCSR1 has been defined in the include file *f2407.h* (see Line 74 above), you can simply reference the address by the name of the constant (SCSR1).

The value written to the SCSR1 register contains bit fields to program the PLL for x4 mode. In addition, there are six clock control bits that enable the clocks for the on-chip peripheral modules. Note that a peripheral module does not function if the clock to it is not enabled. In the example here, all clocks have been enabled. In a real application, you might want to disable clocks to any peripherals not being used to reduce power consumption. Finally, the ILLADR bit (illegal address detection bit) is being cleared by writing a 1 to it. Although ILLADR defaults to 0 after a reset, it is good practice to clear it anyway, in case (for example) software were to branch to the reset vector as a means of restarting a program. The SCSR1 register is documented in reference [2], pages 2–3 to 2–5.

**Lines 131 – 143 (example.asm):** The SCSR2 register is being initialized. Boolean operations are being used to set and clear the various bits. This procedure is used instead of a direct register load so it does not disturb the state of the MP/MC bit. This bit reflects the state of the MP/MC pin at reset, and determines whether the FLASH memory is active in program space, or if external memory is mapped to those addresses. Since this example program is designed to run from either FLASH or external memory, the state of the MP/MC pin at power up is unknown. Therefore, the state of the MP/MC pin must be preserved.

Bit 5 of SCSR2 is the WD OVERRIDE bit. This is a clear-only bit. If this bit is cleared (by writing a 1 to it), the watchdog timer cannot be disabled. The example code does not clear this bit, and the watchdog timer is later disabled at Line 150.

The SCSR2 register is documented in reference [2], pages 2–5 to 2–7.

**Lines 148 – 157 (example.asm):** The WDCR register is being configured to disable the watchdog timer. The WDCR register is documented in reference [2], pages 11–9 to 11–10.

**Lines 162 – 173 (example.asm):** The WSGR register is being configured to set the wait states for the external memory interface. On both the LF2407 EVM and eZdsp™ LF2407, zero wait states are needed in both program and data space. For the I/O space, one wait state is needed on the EVM for the D/A converter, whereas this is a don't care on the eZdsp™ LF2407, since there are no devices in the external I/O space. The WSGR register is located in I/O space, so the OUT instruction must be used to write to it. The WSGR register is documented in reference [2], pages 3–18 to 3–19.

**Lines 178 – 238 (example.asm):** The shared pins on the LF2407 are being configured. All shared pins default to the General Purpose Input Output (GPIO) input function after a device reset. The example program is configuring the PWM1/IOPA6 pin for PWM1 function. All other pins are left as GPIO. Note that bits 15–9 of the MCRB register affect operation of the JTAG emulation pins. These bits should always be written as 1. The MCRx registers are documented in reference [2], Chapter 5.

**Lines 243 – 246 (example.asm):** The W/R/IOPC0 pin is being configured as a GPIO output. The W/R/IOPC0 pin was previously configured for GPIO function in Line 200 using the MCRB register. The PCDATDIR register now determines GPIO input or output function. The W/R/IOPC0 pin is toggled by the example program, as discussed in section 4. The PCDATDIR register is documented in reference [2], Chapter 5.

**Lines 251 – 254 (example.asm):** A software stack is being set up. In this example program, the software stack is used only for context saves and restores during interrupt service routines. However, other uses for a software stack include parameter passing to called functions and storage of local function variables. Here, the AR1 register is being used as the stack pointer, which is the same register convention employed by the C compiler.

The .usect directive is used to allocate space for the software stack in the uninitialized section called stack. You can find the stack section allocated in the SECTIONS portion of the linker command file *example.cmd*. The .usect directive is documented in reference [4], page 4–67.

**Lines 260 – 261 (example.asm):** GP Timers 1 and 2 are both disabled before being configured. This is proper programming procedure: always disable a peripheral before configuring it.

**Lines 263 – 336 (example.asm):** The various event manager registers necessary to configure the desired 20KHz PWM output using timer 1 and compare 1, and also the desired 250ms periodic interrupt using timer 2 are being initialized. The event manager is documented in reference [2], Chapter 6.

Lines 348 – 351 (example.asm): The core interrupt flag register (IFR) and core interrupt mask register (IMR) are initialized to enable the desired core interrupts. It is good practice to clear the IMR register first, since the IMR is not initialized by a DSP reset, and therefore contains an unknown value after power-up. After doing this, the IFR register is cleared to clear any pending core interrupts, and then the desired interrupts are enabled in the IMR. Note that before enabling any peripheral interrupt, the core interrupt on which it is grouped should first be enabled. The IFR and IMR registers are documented in reference [1], pages 5–17 to 5–20.

**Lines 356 – 370 (example.asm):** The desired event manager interrupts are being enabled. Note that before enabling any peripheral interrupt, the core interrupt on which it is grouped should first be enabled in the IMR register. Also note that the only event manager interrupt used in this program is the timer 2 period interrupt, which is enabled by setting bit 1 in the EVAIMRB register. The event manager interrupt registers are documented in reference [2], Chapter 6.

**Line 375 (example.asm):** The global interrupt mask bit is cleared. Clearing this bit enables all maskable core interrupts that have been enabled via the IMR register. The INTM bit is located in Status Register 0 (ST0), and is documented in reference [1], pages 4–15 to 4–17.

**Lines 380 – 382 (example.asm):** The main loop in the program is nothing but an endless loop containing a single NOP instruction. The DSP loops here until an enabled interrupt occurs, in this case, the timer 2 period interrupt.

**Lines 396 – 401 (example.asm):** A context save to the software stack is being performed. In this example, only ST0, ST1, and the ACC are being saved since these are the only registers used by the ISR. The context save illustrated here can easily be expanded to include other registers as needed.

Note that Line 397 advances the stack pointer (AR1) by one location, which skips a memory word. This is a necessary operation since there can potentially be situations in a program where the stack pointer is not pointing to the next free memory location, but instead is pointing to the last used location on the stack. An example of where this situation can arise is during a context restore, starting at Line 425. If interrupts were being nested here and an interrupt occurred during the context restore, that ISR must skip one memory location with the stack pointer, so as not to overwrite an occupied stack location (note that in this example, the program interrupts have not been nested). Another example is when accessing local variables or passed function parameters which reside on the stack (note that this does not occur in the example program here). To do this, a copy of the stack pointer is generally made using a different ARx register, and the copy then used for addressing. The code to make the stack pointer copy would appear as follows, using AR5 here as the copy register:

```

MAR *, AR1 ;ARP = stack pointer

SAR AR1, * ;Save the stack pointer (AR1) onto the stack.

LAR AR5, * ;AR5 now contains a copy of the stack pointer.

; Stack pointer again points to next free location.

```

Upon completion of the above code segment, AR5 can be used to address into the stack and access any local variables or passed function parameters. Notice that between the SAR and LAR instructions, the stack pointer (AR1) is actually pointing to an occupied stack location. If an interrupt were to occur between those two instructions, that ISR would overwrite an occupied stack location unless it had skipped one stack location before putting anything onto the stack.

**Lines 404 – 405 (example.asm):** Peripheral interrupt flags must be manually cleared in the ISR, unlike core interrupt flags in the IFR register which are cleared automatically by the DSP when the interrupt is serviced. In this case, the T2PINT flag is cleared by writing a 1 to its bit in the EVAIFRB register. The EVAIFRB register is documented in reference [2], Chapter 6.

**Lines 408 – 415 (example.asm):** The quad LED bank on the LF2407 EVM is updated. The variable LED\_index is first used to update the LED bank, after which it is advanced by 1 by using a left-shift followed by a store back to memory. Since the LED bank exists in the I/O memory space, the OUT instruction is used. After the LED\_index has been advanced 4 times (i.e., since there are 4 LEDs), it is reset back to 1.

**Lines 418 – 421 (example.asm):** The W/R/IOPC0 pin is toggled by an XOR (exclusive OR) of the proper bit (bit 0) in the PCDATDIR register, with a binary 1.

**Lines 424 – 429 (example.asm):** The context restore is performed from the software stack. Note that the restoration order of ST0 and ST1 is important. When using indirect addressing (as was used here), ST0 should be restored first, followed by ST1. If direct addressing is used for the context save/restore, ST1 should be restored first. These sequences for context restore ensure that the ARP and DP bit fields are restored properly in the ST0 and ST1 registers.

**Line 430 (example.asm):** Global interrupts must be manually re-enabled before returning from an ISR by clearing the INTM bit.

**Line 431 (example.asm):** The RET instruction returns from the ISR.

**Lines 442 – 455 (example.cmd):** The MEMORY section of the linker command file should define all available memory on the DSP target system. The basic memory map for the LF2407 DSP is documented in reference [5], pages 16 and 32 to 33. You should tailor external memory definitions to meet those of your particular target board. In this example, a memory map has been defined that works for both the LF2407 EVM and the eZdsp™ LF2407.

The memory definitions are defined separately for program space (linker page 0) and data space (linker page 1). In the program space, the memory region named "VECS" has been specially defined so that the reset and interrupt vectors can be linked to the correct locations, as required by hardware. The interrupt vector addresses are documented in reference [1], pages 5–15 to 5–16. Note that the VECS memory is physically part of either the internal FLASH or external memory, depending on the state of the MP/MC pin at reset. The memory region named "FLASH" is defined over a 32Kx16 memory address range that will correspond to two possible physical memories. It will either be the internal FLASH memory (if the MP/MC pin was low during DSP reset), or it will map to external memory (if MP/MC pin was high during reset). See section 2 of this document for information on jumper settings that control the MP/MC pin on the LF2407 EVM and eZdsp™ LF2407 boards. Finally, the memory region named "EXTPROG" defines the external program memory that is available on the LF2407 EVM and eZdsp™ LF2407, the external SRAM available at the EXTPROG addresses can also be mapped to the FLASH region addresses. See reference [8] for details.

In the data space, the internal dual-access memory blocks B0, B1, and B2 are defined, as is the 2Kx16 internal single-access RAM block SARAM. The memory region named "EXTDATA" defines the external data memory that is available on the LF2407 EVM and eZdsp™ LF2407.

**Lines 457 – 463 (example.cmd):** The SECTIONS section of the linker command file tells the linker where to locate each section used in the code. Here, only four sections have been used (.text, .bss, vectors, and stack). Notice that the vectors section has been linked to the VECS memory region, which places the interrupt vectors at the correct DSP-specific addresses. The SECTIONS section of the linker command file is documented in reference [4], section 8.7.

Note (example.cmd): Numerous linker options exist, all of which can be invoked either on the command line that starts the linker, or by placing the options at the beginning of the linker command file before the MEMORY section. Chapter 8 in reference [4] shows examples that place various options at the beginning of the linker command file (e.g., Example 8–2, page 8–17). However, placing these options in the linker command file is neither necessary nor recommended when using the Code Composer debugger, since Code Composer offers configuration menus that allow you to select desired options for your code project. Code Composer then uses the selected options on the linker command line when it invokes the linker during project building. This is why example.cmd only contains the MEMORY and SECTIONS sections, and nothing else. To select linker (and compiler and assembler) options from within Code Composer, click on the PROJECT menu, and then select OPTIONS.

## 6 C Language Example Program

The C language example program consists of the following files:

cvectors.asm: Interrupt vector table

example\_c.c: Main program

• f2407\_c.h: Header file containing peripheral register address definitions

example\_c.cmd: Linker command file

example\_c.mak: C2xx Code Composer v4.1x project file

• example\_c.out: Program executable

• example.map: Memory map file output by the code generation tools

Only the first five listed files are needed to build the program. The final two files are provided for convenience, and are produced by the code generation tools when the program is built. To build the project using Code Composer, load the project file <code>example\_c.mak</code> into Code Composer (click on PROJECT—>OPEN), and then select PROJECT—>BUILD or PROJECT—>REBUILD ALL. See the online help available within Code Composer for additional assistance.

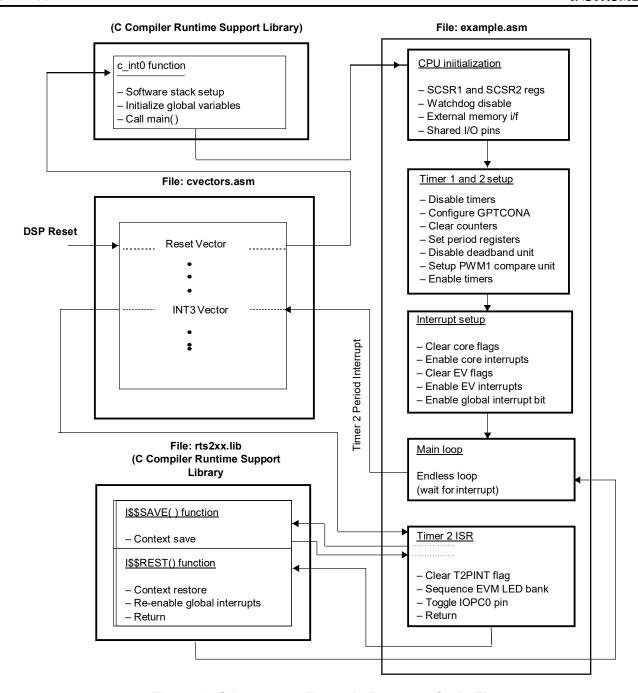

Figure 2 illustrates the code flow for the C language example program. Execution begins at the reset vector in the file *cvectors.asm* after a hardware reset. This vector branches to the c\_int0() function in the C language runtime support library *rts2xx.lib*. This library comes with the code generation tools, and must be linked with all C language programs (done by adding it to your Code Composer project). This has already been done in *example\_c.mak*. The c\_int0() function sets up the C stack, initializes values for all initialized global and static variables, and finally calls main(). The c\_int0() function is documented in reference [3], section 6.8.

Once at main(), the processor is initialized, after which an endless main loop is entered. The DSP is periodically interrupted out of this endless loop by the timer 2 period interrupt, at which time the interrupt service routine is executed. ISR context save and restore, global interrupt re-enable, and program return are handled automatically by functions in the runtime support library.

Appendix B contains file listings of *cvectors.asm*, *example\_c.c*, and *example\_c.cmd*. Contiguous line numbers have been provided along the left-hand side of the code to facilitate discussion. The file *example\_c.c* is functionally equivalent to the assembly language program *example.asm*, previously discussed in this document. Readers can compare these two files in order to gain insight into C language implementations of assembly language code segments, and vice versa. A number of details and useful pieces of information will now be discussed.<sup>2</sup>

<sup>2.</sup> Cited page and section numbers in references correspond to the specific revision of the documentation listed in the Reference section of this application report. These numbers have been given as a matter of convenience, but may no longer be accurate if a new revision of the documentation is released. The referenced material itself, however, should still be found in the cited document. See the index in the cited document to find the correct page for the referenced subject.

Figure 2. C Language Example Program Code Flow

**NOTE:** Much of the discussion that follows presents identical points to those made previously in section 5 for the assembly language example program. Information is repeated here to allow independent reading of the discussions of the C and assembly language example programs.

**General** (cvectors.asm): The interrupt vector table must be written in assembly language. While you could use inline assembly to embed the vector table into a C language file, it is better programming practice to use a separate file, as was done in this example. Multiple source files need simply be added to the Code Composer project. They will then be linked together automatically by the code generation tools during a project build.

Line 464 (cvectors.asm): The asterisk in column 1 indicates that the entire line is a comment. The asterisk can only be used in column 1. To place a comment in a line beginning at a different column, use a semi-colon, as shown in line 478.

Line 475 (cvectors.asm): The .ref directive is used to reference symbols defined externally to a source file. In this case, the symbol c int0 is declared in the runtime support library rts2xx.lib, and the label timer2 isr is declared in the file example c.c. However, both are referenced here in cvectors.asm. Note the use of the leading underscore on both labels. All symbols which are defined in C but referenced with assembly code must have a leading underscore appended to the symbol name in the assembly code reference. The .ref directive is documented in reference [4], page 4-44.

**Line 477 (cvectors.asm):** The .sect directive is used to declare an initialized section. In this case, the interrupt vectors (code) are being placed in the section named vectors so that they can be linked to a specific address range. You will find the vectors section listed in the SECTIONS portion of the linker command file example c.cmd.

Lines 478 – 509 (cvectors.asm): Each interrupt vector is two 16-bit words long, and contains a single branch instruction that indicates the address of the interrupt service routine (ISR) associated with it. Line 478 is the reset vector, and branches to the label c int0 which is the entry point to a routine located in the rts2xx.lib library. Line 481 is the core interrupt 3 vector. This core interrupt is shared between several peripheral interrupts, among them the timer 2 period interrupt. In this example program, the timer 2 period interrupt is the only interrupt enabled on core interrupt 3. Therefore, the interrupt 3 vector can branch directly to the timer 2 interrupt service routine, located at the label timer2 isr in example c.c. If more than one peripheral interrupt were enabled on a given core interrupt line, software would need to differentiate among the peripheral interrupts so that the correct ISR could be executed. The procedure for doing this is discussed in reference [2], pages 2-20 to 2-21. The core interrupt vector addresses are documented in reference [1], pages 5–15 to 5–16. The sharing of the core interrupts is documented in reference [5], pages 20 to 23. Note that all remaining interrupt vectors branch to themselves. This is useful during code development to trap erroneous interrupts. In a real application, one would probably want to branch all unused interrupts to an error handling routine that performs whatever recovery steps are desired.

**Line 531 (example\_c.c):** The file f2407\_c.h is being included into the C source file. This file contains address definitions for all of the peripheral registers in the LF2407 DSP. For example,

/\* WD timer control register \*/ #define WDCR (volatile unsignedint \*)0x7029

defines the data space address for the watchdog timer control register WDCR. The above uses the ANSI C language preprocessor directive #define to associate the text WDCR with an immediate pointer to an unsigned integer at the address 0x7029. This allows one to access the defined register in their C program using a simple pointer construct. For example, to write the value 0x00E8 to the WDCR register, you simply write the following in your C program:

15

```

*WDCR = 0x00E8; /* write 0x00E8 to the WDCR register */

```

The volatile keyword in the address definition tells the compiler that a variable is not under its sole control (e.g., something other than code generated by the compiler, such as hardware, could change its value). It is important to use this keyword with register definitions, especially if the compiler optimizer is enabled. The volatile keyword is documented in reference [3], page 3–10.

Lines 533 – 552 (example\_c.c): Address definitions for the I/O space are being made. The I/O space for LF2407 devices consists of a 64Kx16 address block, beginning at address 0x0000. On the LF2407 EVM, the D/A converter, DIP switch bank, and quad-LED bank are located external to the DSP in the I/O space (on the eZdsp™ LF2407, no external devices exist in the I/O space). Note that only the quad LED bank is exercised by the example program (has no effect on eZdsp™ LF2407). The compiler assumes that a variable is located in the data space unless that variable is specifically defined as being in the I/O space.

The compiler provides the "ioport" keyword to declare an I/O space address. The ioport keyword declares an address in the I/O space as being of a particular type, e.g. unsigned int. The address itself is declared using the construct portxxxx, where xxxx is the 64K word address of the port. For example:

| ioport unsig | ned int | port000C; | /* | I/O | space  | address  | 0x000C   | is ar | n unsigned  | int */   |

|--------------|---------|-----------|----|-----|--------|----------|----------|-------|-------------|----------|

| #define      | LED     | port000C  | /* | EVM | LED ba | ank is a | t addres | s 0x0 | 000C in I/O | space */ |

| ioport unsig | ned int | port000C; | /* | I/O | space  | address  | 0x000C   | is ar | n unsigned  | int */   |

To make the C code more readable, you can associate a symbol with port000C as follows:

You can now access the declared I/O address using the defined name. For example, to write the value 0x0001 to address 0x000C in I/O space, you would write:

The ioport keyword is documented in reference [3], page 5–13. For details on the I/O space memory map, see reference [3], or the datasheet for your particular TI DSP device.

**Line 568** (*example\_c.c*): This is the function declaration for main(). This function is called by the c int0 function, located in the runtime support library *rts2xx.lib*.

Line 572 (example\_c.c): The SCSR1 register is being initialized. The value written to the SCSR1 register contains bit fields to program the PLL for x4 mode. In addition, there are six clock control bits that enable the clocks for the on-chip peripheral modules. Note that a peripheral module will not function if the clock to it is not enabled. In the example here, all clocks have been enabled. In a real application, you can disable clocks to any peripherals not being used to reduce power consumption. Finally, the ILLADR bit (illegal address detection bit) is cleared by writing a 1 to it. Although ILLADR defaults to 0 after a reset, it is good practice to clear it anyway in case, for example, software were to branch to the reset vector as a means of restarting a program. The SCSR1 register is documented in reference [2], pages 2–3 to 2–5.

Line 589 (example c.c): The SCSR2 register is being initialized. Boolean operations are used to set and clear the various bits. This procedure is used instead of a direct register load, so as not to disturb the state of the MP/MC bit. This bit reflects the state of the MP/MC pin at reset and determines whether the FLASH memory is active in program space, or if external memory is mapped to those addresses. Since this example program is designed to run from either FLASH or external memory, the state of the MP/MC pin at power up is unknown. Therefore, the state of the MP/MC pin must be preserved.

Bit 5 of SCSR2 is the WD OVERRIDE bit. This is a clear-only bit. If this bit is cleared (by writing a 1 to it), the watchdog timer cannot be disabled. The example code does not clear this bit, and the watchdog timer is later disabled at Line 601.

The SCSR2 register is documented in reference [2], pages 2–5 to 2–7.

**Line 601 (example c.c):** The WDCR register is being configured to disable the watchdog timer. The WDCR register is documented in reference [2], pages 11–9 to 11–10.

**Line 612** (example\_c.c): The WSGR register is being configured to set the wait states for the external memory interface. On both the LF2407 EVM and eZdsp™ LF2407, zero wait states are needed in both program and data space. For the I/O space, one wait state is needed on the EVM for the D/A converter, whereas this is a don't care on the eZdsp™ LF2407 since there are no devices in the external I/O space. The WSGR register is located in I/O space, and was declared using the ioport keyword in the file f2407 c.h. This is why an asterisk (i.e., pointer symbol) is not used in the code in front of WSGR. See lines 533 – 552 above for more information on I/O space accesses in C. The WSGR register is documented in reference [2], pages 3-18 to 3-19.

**Lines 622 – 680 (example c.c):** The shared pins on the LF2407 are being configured. All shared pins default to the GPIO (General Purpose Input Output) input function after a device reset. The example program is configuring the PWM1/IOPA6 pin for PWM1 function. All other pins are left as GPIO. Note that bits 15–9 of the MCRB register affect operation of the JTAG emulation pins. These bits must always be written as a 1. The MCRx registers are documented in reference [2], Chapter 5.

Line 683 (example c.c): The W/R/IOPC0 pin is being configured as a GPIO output. The W/R/IOPC0 pin was previously configured for GPIO function in Line 642 using the MCRB register. The PCDATDIR register now determines GPIO input or output function. The W/R/IOPC0 pin is toggled by the example program, as discussed in section 4. The PCDATDIR register is documented in reference [2]. Chapter 5.

**Lines 687 – 688 (example c.c):** GP Timers 1 and 2 are both disabled before being configured. This is proper programming procedure: always disable a peripheral before configuring it.

**Lines 690 – 766 (example c.c):** The various event manager registers necessary to configure the desired 20KHz PWM output using timer 1 and compare 1, and also the desired 250ms periodic interrupt using timer 2 are being initialized. The event manager is documented in reference [2], Chapter 6.

17

Lines 772 – 774 (example\_c.c): The core interrupt flag register (IFR) and core interrupt mask register (IMR) are initialized to enable the desired core interrupts. It is good practice to clear the IMR register first, since the IMR is not initialized by a DSP reset, and therefore contains an unknown value after power up. After doing this, the IFR register is cleared to clear any pending core interrupts, and then the desired interrupts are enabled in the IMR. Note that before enabling any peripheral interrupt, the core interrupt on which it is grouped should first be enabled. The IFR and IMR registers are documented in reference [1], pages 5–17 to 5–20.

**Lines 777 – 789 (example\_c.c):** The desired event manager interrupts are being enabled. Note that before enabling any peripheral interrupt, the core interrupt on which it is grouped should first be enabled in the IMR register. Also note that the only event manager interrupt in use in this program is the timer 2 period interrupt, which is enabled by setting bit 1 in the EVAIMRB register. The event manager interrupt registers are documented in reference [2], Chapter 6.

**Line 792** (example\_c.c): Inline assembly is being used to clear the global interrupt mask bit. The INTM bit is not directly accessible from C code, hence the use of inline assembly and the CLRC assembly instruction. Clearing this bit enables all maskable core interrupts that have been enabled via the IMR register. The INTM bit is located in Status Register 0 (ST0), and is documented in reference [1], pages 4–15 to 4–17.

Inline assembly is invoked by using the asm keyword, and placing in quotations the desired assembly language statement:

With inline assembly, whatever is written between the quotation marks is inserted directly into the compiler-generated assembly code. The functional position of the statement relative to the C code is preserved in the assembly code (i.e., the compiler optimizer will not move instructions around an inline assembly statement). Note that the character immediately following the first quotation mark is placed at column 1 in the assembly file. The space between the quotation mark and the CLRC instruction is therefore important in this example, since only labels and comments can begin in column 1 of an assembly file. The asm keyword is documented in reference [3], page 6–22.

**Line 795 (example\_c.c:** The main loop in the program is nothing but an empty endless while() loop. The DSP will loop here until an enabled interrupt occurs, in this case the timer 2 period interrupt.

**Line 797 (example\_c.c):** The closing brace marks the end of main().

**Line 800** (example\_c.c): This is the function declaration for the interrupt service routine timer2\_isr(). Interrupt service routines can neither return a value, nor receive passed values, hence the use of the void data types in the function declaration. The "interrupt" keyword is used to tell the compiler that this function is an ISR. When this keyword is used, the compiler will insert code into the ISR that calls the context save function I\$\$SAVE upon function entry, and also insert code that branches to the context restore function I\$\$REST at the end of the ISR. These two functions are located in the runtime support library rts2xx.lib. After restoring the context, the I\$\$REST function re-enables global interrupts (i.e., clears the INTM bit) and then returns to the original interrupted routine. The interrupt keyword is documented in reference [3], page 6–26.

**Line 803** (example\_c.c.): Peripheral interrupt flags must be manually cleared in the ISR, unlike core interrupt flags in the IFR register which are cleared automatically by the DSP when the interrupt is serviced. In this case, the T2PINT flag is cleared by writing a 1 to its bit in the EVAIFRB register. The EVAIFRB register is documented in reference [2], Chapter 6.

**Lines 806 – 808** (example\_c.c): The quad LED bank on the LF2407 EVM is updated. The variable LED\_index is first used to update the LED bank, after which it is advanced by 1 by left-shifting it once. The LED bank exists in the I/O memory space, and the label "LED" was previously defined to access the proper address in I/O space in Lines 551–552. After the LED\_index has been advanced 4 times (i.e., since there are 4 LEDs), it is reset back to 1.

**Line 811** (example\_c.c): The W/R/IOPC0 pin is toggled by an XOR (exclusive OR) of the proper bit (bit 0) in the PCDATADIR register with a binary 1.

**Line 813 (example c.c):** The closing brace marks the end of the ISR.

**Lines 825 – 838 (example\_c.cmd):** The MEMORY section of the linker command file defines all available memory on the DSP target system. The basic memory map for the LF2407 DSP is documented in reference [5], page 16 and also pages 32 to 33. You should tailor external memory definitions to meet those of your particular target board. In this example, a memory map has been defined that works for both the LF2407 EVM and the eZdsp™ LF2407.

The memory definitions are defined separately for program space (linker page 0) and data space (linker page 1). In the program space, the memory region named VECS has been specially defined so that the reset and interrupt vectors can be linked to the correct locations, as required by hardware. The interrupt vector addresses are documented in reference [1], pages 5–15 to 5–16. Note that the VECS memory is physically part of either the internal FLASH or external memory, depending on the state of the MP/MC pin at reset. The memory region named FLASH is defined over a 32Kx16 memory address range that will correspond to two possible physical memories. It will either be the internal FLASH memory if the MP/MC pin was low during DSP reset, or it will map to external memory if MP/MC pin was high during reset. See section 2 of this document for information on jumper settings that control the MP/MC pin on the LF2407 EVM and the eZdsp™ LF2407 boards. Finally, the memory region named "EXTPROG" defines the external program memory that is available on the LF2407 EVM and eZdsp™ LF2407. Note that on the eZdsp™ LF2407, the external SRAM available at the EXTPROG addresses may also be mapped to the FLASH region addresses. See reference [8] for details.

In the data space, the internal dual-access memory blocks B0, B1, and B2 are defined, as is the 2Kx16 internal single-access RAM block SARAM. The memory region named "EXTDATA" defines the external data memory that is available on the LF2407 EVM and eZdsp™ LF2407.

**Lines 840 – 853 (example\_c.cmd):** The SECTIONS section of the linker command file tells the linker where to locate each section used in the code. The C compiler uses seven specific sections (Lines 843 – 849), although it does not necessarily always allocate each section (e.g., .switch section will only be allocated if you have used switch statements in your C code). The function of each of these sections is documented in reference [3], pages 6–3 to 6–4. In addition to these sections, one user defined section called vectors (defined in the file *cvectors.asm*) is also used by this program, and therefore must be specified in the linker command file. The vectors section has been linked to the VECS memory region, which places the interrupt vectors at the correct DSP specific addresses. The SECTIONS section of the linker command file is documented in reference [4], section 8.7.

Note (example\_c.cmd): Numerous linker options exist, all of which can be invoked either on the command line that starts the linker, or by placing the options at the beginning of the linker command file before the MEMORY section. Chapter 8 in reference [4] shows examples that place various options at the beginning of the linker command file (e.g., Example 8–2, page 8–17). However, placing these options in the linker command file is neither necessary nor recommended when using the Code Composer debugger, since Code Composer offers configuration menus that allow you to select desired options for your code project. Code Composer then uses the selected options on the linker command line when it invokes the linker during project building. This is why example\_c.cmd only contains the MEMORY and SECTIONS sections, and nothing else. To select linker (and compiler and assembler) options from within Code Composer, click on the PROJECT menu, and then select OPTIONS.

#### 7 Conclusion

Two functionally identical example programs, one written in assembly language, and the other in the C programming language, have been presented and discussed. These programs illustrate basic code for initializing and operating the TMS320LF240x DSP. The programs are ready to run on either the TMS320LF2407 Evaluation Module (EVM) or the eZdsp™ LF2407 development kit, but are also intended for use as code templates for any LF240x or LF240xA DSP target system.

#### 8 References

- 1. TMS320F/C24x DSP Controllers CPU and Instruction Set Reference Guide (SPRU160C).

- 2. TMS320LF/LC240x DSP Controllers System and Peripherals Reference Guide (SPRU357A).

- 3. TMS320C2x/C2xx/C5x Optimizing C Compiler User's Guide (SPRU024E).

- 4. Fixed-Point DSP Assembly Language Tools User's Guide (SPRU018D).

- 5. TMS320LF2407, TMS320LF2406, TMS320LF2402 DSP Controllers datasheet (SPRS094F).

- 6. TMS320LF2407 DSP Controller Silicon Errata (SPRZ158F).

- 7. TMS320LF2407 Evaluation Module Technical Reference (from Spectrum Digital, Inc.)

- 8. eZdsp™ Technical Reference (from Spectrum Digital, Inc.)

## Appendix A Assembly Language Example Program Listing

Line numbers listed along the left-hand side of the file listings are numerically contiguous across all files in Appendixes A and B.

```

******************

* Filename: vectors.asm

3

* Author: David M. Alter, Texas Instruments Inc.

4

5

* Last Modified: 03/14/01

6

7

8

* Description: Interrupt vector table for ^\prime240x DSP core

9

* for use with assembly language programs.

10

*****************

11

12

13

.ref start, timer2 isr

14

.sect

"vectors"

15

rset: B

16

start

int1

;00h reset

;02h INT1

17

int1: B

int2

;04h INT2

int2: B

18

int2

timer2_isr

int4

int5

int6

int7

int8

int9

int10

int11

in+12

19

int3: B

;06h INT3

20

int4: B

;08h INT4

21

int5: B

; OAh INT5

22

int6: B

; OCh INT6

; OEh reserved

23

int7: B

int8: B

;10h INT8 (software)

24

;12h INT9 (software)

25

int9: B

int10: B

;14h INT10 (software)

26

27

int11: B

;16h INT11 (software)

int12: B

28

int12

;18h INT12 (software)

int13: B

;1Ah INT13 (software)

29

int13

30

int14: B

int14

;1Ch INT14 (software)

31

int15: B

int15

;1Eh INT15 (software)

32

int16: B

int16

;20h INT16 (software)

int17: B

33

int17

;22h TRAP

int18: B

34

int18

;24h NMI

;26h reserved

35

36

;28h INT20 (software)

37

;2Ah INT21 (software)

;2Ch INT22 (software)

38

;2Eh INT23 (software)

39

;30h INT24 (software)

40

41

;32h INT25 (software)

42

;34h INT26 (software)

;36h INT27 (software)

43

;38h INT28 (software)

45

;3Ah INT29 (software)

;3Ch INT30 (software)

46

47

;3Eh INT31 (software)

```

```

*****************

48

* Filename: example.asm

49

50

* Author: David M. Alter, Texas Instruments Inc.

51

52

53

* Last Modified: 03/14/01

54

55

* Description: This program illustrates basic initialization and

56

* operation of the LF2407 DSP. The following peripherals are

57

* exercised:

58

* 1) Timer 2 is configured to generate a 250ms period interrupt.

^{\star} 2) The LED bank on the LF2407 EVM is sequenced in the Timer2 ISR. ^{\star}

59

^{\star} 3) The IOPC0 pin is toggled in the Timer2 ISR.

60

* 4) Timer 1 is configured to drive 20KHz 25% duty cycle symmetric

61

62

PWM on the PWM1 pin.

63

*******************

64

65

66

67

;Global symbol declarations

68

.def start, timer2 isr

70

71

72

;Address definitions

73

74

.include f2407.h

75

;EVM DAC register 0 (I/O space)

0000h

76

DAC0

.set

0001h

;EVM DAC register 0 (1/0 space)

;EVM DAC register 1 (I/0 space)

;EVM DAC register 2 (I/0 space)

;EVM DAC register 3 (I/0 space)

;EVM DAC update register (I/0 space)

;EVM DIP switch (I/0 space)

;EVM LED bank (I/0 space)

77

DAC1

78

DAC2

.set 0002h

.set 0003h

.set 0004h

.set 0008h

.set 000Ch

79

DAC3

DACUD

80

DIPSWCH

81

82

83

84

85

;Constant definitions

86

;250ms timer2 period with a 1/128 ;timer prescaler and 30MHz CPUCLK

87

timer2_per

.set 58594

88

89

90

pwm half per .set 750

;period/2, 20KHz symmetric PWM with

91

;a 30MHz CPUCLK

92

93

.set 563

pwm duty

;25% PWM duty cycle

94

95

96

;Uninitialized global variable definitions

97

.bss temp1,1 ;general purpose variable

.bss LED_index,1 ;LED index

98

99

100

101

```

```

102

103

MAIN ROUTINE

104

105

106

.text

107 start:

108

109 ;-----

110 ; Configure the System Control and Status Registers

LDP #DP_PF1 ;set data page

112

113

SPLK #000000011111101b, SCSR1

114

115

FEDCBA9876543210

116

* bit 15

* bit 14

* bit 13-12

* bit 11-9

* bit 11-9

* bit 8

* bit 7

* bit 7

* bit 1 - orable SCI module clock

117

118

119

120

121

122

1:

1:

1:

1:

1:

0:

123 * bit 6

1 = enable SCI module clock

1 = enable SPI module clock

124

* bit 5

1 = enable CAN module clock

1 = enable EVB module clock

1 = enable EVA module clock

reserved

* bit 4

125

* bit 3

126

* bit 2

127

128

* bit 1

* bit 0

1:

129

clear the ILLADR bit

130

LACC SCSR2 ; ACC = SCSR2 register

OR #000000000001011b ; OR in bits to be set

AND #00000000001111b ; AND out bits to be cleared

131

132

133

134

FEDCBA9876543210

135

136

0: do NOT clear the WD OVERRIDE bit

0: XMIF_HI-Z, 0=normal mode, 1=Hi-Z'd

1: disable the boot ROM, enable the FLASH

137

138

* bit 4

139

* bit 3

* bit 2

140

no change MP/MC* bit reflects the state of the MP/MC* pin

141

* bit 1-0

11: 11 = SARAM mapped to prog and data (default)

142

SCSR2

143

SACL

;store to SCSR2 register

144

145

146

; Disable the watchdog timer

147

148

;

LDP #DP_PF1

; set data page

149

;

SPLK #000000011101000b, WDCR

150

151

152

FEDCBA9876543210

153 * bits 15-8 0's reserved

* bit 7 1: clear WD flag

* bit 6 1: disable the dog

* bit 5-3 101: must be written as 101

* bit 2-0 000: WDCLK divider = 1

154

155

156

157

158

```

```

159

160

;Setup external memory interface for LF2407 EVM

161

LDP #temp1

162

; set data page

163

SPLK #000000001000000b, temp1

164

165

166

* bit 15-11 0's: reserved

* bit 10-9 00: bus visibility off

* bit 8-6 001: 1 wait-state for I/O space

* bit 5-3 000: 0 wait-state for program space

* bit 2-0 000: 0 wait state for program space

167

168

169

170

171

172

173

OUT temp1, WSGR

174

175

;Setup shared I/O pins

176

177

LDP #DP PF2

178

;set data page

179

SPLK #000000001000000b, MCRA; group A pins

180

181

* bit 15

* bit 15

* bit 14

* bit 14

* bit 13

* bit 12

* bit 11

* bit 11

* bit 11

* bit 11

* bit 12

* bit 11

* bit 10

* bit 10

* bit 9

* bit 8

* bit 7

* bit 6

* bit 5

* bit 6

* bit 1

* bit 2

* bit 3

* bit 4

* bit 3

* bit 4

* bit 5

* bit 4

* bit 5

* bit 6

* bit 7

* bit 7

* bit 8

* bit 9

* bit 9

* bit 9

* bit 9

* bit 10

* bit 10

* bit 10

* bit 10

* bit 2

* bit 10

* bit 1

182

FEDCBA9876543210

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

SPLK #111111100000000b, MCRB ; group B pins

201

202

FEDCBA9876543210

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

```

```

220

SPLK #00000000000000b, MCRC ; group C pins

221

222

FEDCBA9876543210

0: reserved

223

* bit 15

* bit 14

0=IOPF6,

224

0:

1=IOPF6

0=IOPF5,

0:

* bit 13

1=TCLKINB

225

0: 0=IOFF3,

0: 0=IOFF4,

0: 0=IOFF3,

0: 0=IOFF2,

226

* bit 12

1=TDIRB

1=T4PWM/T4CMP

227

* bit 11

* bit 10

228

1=T3PWM/T3CMP

* bit 9

229

0:

0=IOPF1,

1=CAP6

0=IOPF0,

0=IOPE7,

230 * bit 8

0:

1=CAP5/QEP4

231

* bit 7

0:

1=CAP4/QEP3

0:

0:

0:

* bit 6

0=IOPE6,

232

1=PWM12

0=IOPE5,

0=IOPE4,

0=IOPE3,

0=IOPE2,

* bit 5

233

1=PWM11

* bit 4

234

1=PWM10

* bit 3

235

1=PWM9

0:

236

* bit 2

1=PWM8

* bit 1

237

0:

0=IOPE1,

1=PWM7

238

* bit 0

0:

0=IOPE0,

1=CLKOUT

239

240

241

;Configure IOPCO pin as an output

242

LDP

#DP_PF2

243

; set data page

LACC

244

#0100h

; ACC = 0100h

;OR in PCDATDIR register

245

OR

PCDATDIR

PCDATDIR

;store result to PCDATDIR

246

SACL

247

248

249

;Setup the software stack

250

stk_len .set 100 ;stack length

251

.usect "stack", stk len ; reserve space for stack

252

st.k

253

LAR AR1, #stk

254

;AR1 is the stack pointer

255

256

257

;Setup timers 1 and 2, and the PWM configuration

258

LDP #DP EVA

259

; set data page

;disable timer 1

SPLK #0000h, T1CON

260

261

SPLK #0000h, T2CON

; disable timer 2

262

SPLK #00000000000000b, GPTCONA

263

264

FEDCBA9876543210

265

* bit 15 0: reserved

* bit 14 0: T2STAT, read-only

* bit 13 0: T1STAT, read-only

* bit 12-11 00: reserved

* bit 10-9 00: T2TOADC, 00 = no timer2 event starts ADC

* bit 8-7 00: T1TOADC, 00 = no timer1 event starts ADC

* bit 6 0: TCOMPOE, 0 = Hi-z all timer compare outputs

* bit 5-4 00: reserved

* bit 3-2 00: T2PIN, 00 = forced low

* bit 1-0 00: T1PIN, 00 = forced low

266

267

268

269

270

271

272

273

274

275

276

```

```

277

;Timer 1: Configure to clock the PWM on PWM1 pin.

;Symmetric PWM, 20KHz carrier frequency, 25% duty cycle

279

#0000h, T1CNT

SPLK

;clear timer counter

280

SPLK

#pwm half per, T1PR

;set timer period

281

SPLK

#0000h, DBTCONA

; deadband units off

282

SPLK

;set PWM duty cycle

#pwm duty, CMPR1

283

284

SPLK

#000000000000010b, ACTRA

285

286

FEDCBA9876543210

287

* bit 15

0:

space vector dir is CCW (don't care)

288

* bit 14-12

000:

basic space vector is 000 (dont' care)

289

* bit 11-10

00:

PWM6/IOPB3 pin forced low

* bit 9-8

PWM5/IOPB2 pin forced low

290

00:

* bit 7-6

00:

PWM4/IOPB1 pin forced low

291

292

* bit 5-4

00:

PWM3/IOPB0 pin forced low

293

* bit 3-2

00:

PWM2/IOPA7 pin forced low

10:

* bit 1-0

294

PWM1/IOPA6 pin active high

295

296

SPLK #10000010000000b, COMCONA

297

298

FEDCBA9876543210

299

* bit 15

1:

1 = enable compare operation

* bit 14-13

300

00:

00 = reload CMPRx regs on timer 1 underflow

301

* bit 12

0:

0 = space vector disabled

* bit 11-10

00:

302

00 = reload ACTR on timer 1 underflow

* bit 9

303

1:

1 = enable PWM pins

304

* bit 8-0

0's:

reserved

305

306

SPLK #0000100001000000b, T1CON

307

308

FEDCBA9876543210

309

* bit 15-14

00:

stop immediately on emulator suspend

310

* bit 13

0:

reserved

311

* bit 12-11

01:

01 = continous-up/down count mode

312

* bit 10-8

000:

000 = x/1 \text{ prescaler}

313

* bit 7

0:

reserved in T1CON

314

* bit 6

1:

TENABLE, 1 = enable timer

* bit 5-4

00 = CPUCLK is clock source

315

00:

* bit 3-2

00:

316

00 = reload compare reg on underflow

317

* bit 1

0:

0 = disable timer compare

* bit 0

318

0:

reserved in T1CON

319

320

;Timer 2: configure to generate a 250ms periodic interrupt

321

#0000h, T2CNT

; clear timer counter

SPLK

322

SPLK

#timer2 per, T2PR

; set timer period

323

324

#1101011101000000b, T2CON

SPLK

325

326

FEDCBA9876543210

* bit 15-14

327

11:

stop immediately on emulator suspend

* bit 13

328

0:

reserved

* bit 12-11

10:

329

10 = continous-up count mode

330

* bit 10-8

111:

111 = x/128 \text{ prescaler}

* bit 7

0:

331

T2SWT1, 0 = use own TENABLE bit

332

* bit 6

TENABLE, 1 = enable timer

1:

333

* bit 5-4

00:

00 = CPUCLK is clock source

334

* bit 3-2

00:

00 = reload compare reg on underflow

335

* bit 1

0:

0 = disable timer compare

336

* bit 0

0:

SELT1PR, 0 = use own period register

337

```

```

339 ;Other setup

340 ;-----

;LED index initialization

LDP #LED index

; set data page

SPLK #1h, LED_index ;initialize the LED index

343

344

346 ;Setup the core interrupts

LDP

#0h

348

LDP #0h

SPLK #0h,IMR

;set data page

349

; clear the IMR register

SPLK #111111b,IFR

SPLK #000100b,IMR

;clear any pending core interrupts

;enable desired core interrupts

SPLK

350

3.51

352

354 ; Setup the event managerinterrupts

LDP #DP_EVA ;set data page

SPLK #0FFFFh, EVAIFRA ;clear all EVA group A interrupts

SPLK #0FFFFh, EVAIFRB ;clear all EVA group B interrupts

SPLK #0FFFFh, EVAIFRC ;clear all EVA group C interrupts

SPLK #00000h, EVAIMRA ;enabled desired EVA group A interrupts

SPLK #00000h, EVAIMRB ;enabled desired EVA group B interrupts

SPLK #00000h, EVAIMRC ;enabled desired EVA group C interrupts

356

357

358

359

360

361

362

363

LDP

#DP EVB

364

;set data page

SPLK #0FFFFh, EVBIFRA ; clear all EVB group A interrupts

SPLK #0FFFFh, EVBIFRB ; clear all EVB group B interrupts

SPLK #0FFFFh, EVBIFRC ; clear all EVB group C interrupts

SPLK #00000h, EVBIMRA ; enabled desired EVB group A interrupts

SPLK #00000h, EVBIMRB ; enabled desired EVB group B interrupts

SPLK #00000h, EVBIMRC ; enabled desired EVB group C interrupts

365

366

367

368

369

370

371

372

373 ; Enable global interrupts

CLRC INTM

; enable global interrupts

376

378 :Mainloop

380 loop:

381

NOP

B loop

382

;branch to loop

383

384

******************

385

* INTERRUPT SERVICE ROUTINES

386

387

388

390 ;GP Timer 2 period interrupt (core interrupt INT3)

392

393 timer2_isr:

394

395 ; Context save to the software stack

MAR *,AR1

;ARP=stack pointer

```

```

397

*+

MAR

; skip one stack location (required)

398

SST

#1, *+

;save ST1

#0, *+

399

SST

; save STO

*+

400

SACH

; save ACCH

401

*+

SACL

; save ACCL

402

403

;Clear the T2PINT interrupt flag

#DP EVA

404

LDP

; set data page

#00001h, EVAIFRB