# TMS320VC5502 to TMS320C5517 Hardware Migration Guide

#### ABSTRACT

This application report discusses the differences between the Texas Instruments TMS320VC5502 processor and the TMS320C5517 processor.

|   | Introduction                 |   |

|---|------------------------------|---|

| 2 | Basic Feature comparison     | 2 |

|   | Power, Input Clocks, and PLL |   |

|   | Boot Modes                   |   |

| 5 | Pin Multiplexing             | 7 |

| 6 | Compiler Options             | 8 |

| 7 | References                   | 8 |

|   |                              |   |

## List of Figures

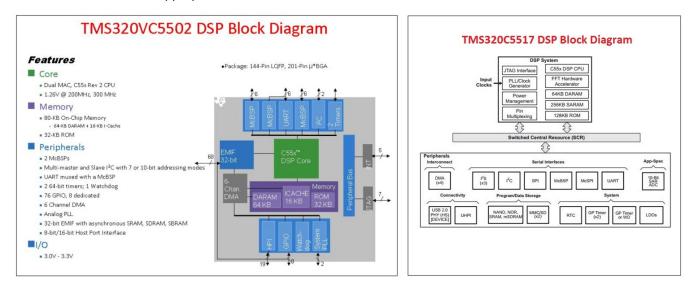

| 1 | TMS320VC5502 and TMS320C5517 DSP Block Diagrams | 2 |

|---|-------------------------------------------------|---|

#### List of Tables

| 1 | Basic Feature Comparison                         | 2 |

|---|--------------------------------------------------|---|

| 2 | VC5502 Voltage Rails                             | 3 |

| 3 | C5517 Voltage Rails                              | 4 |

| 4 | VC5502 Input Clocks                              | 4 |

| 5 | C5517 Input Clocks                               | 4 |

| 6 | Comparison of Boot Modes on the VC5502 and C5517 | 5 |

|   |                                                  |   |

#### Trademarks

Code Composer Studio is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

# 1 Introduction

Texas Instruments recommends using the TMS320C5517 Digital Signal Processor (DSP) as an alternative part to replace the TMS320VC5502 DSP. This alternative part that has similar functionality but is not functionally equivalent to the TMS320VC5502 device. While the maximum system clock is changed from 300 MHz to 200 MHz with the TMS320C5517, it offers improvements like substantially more on-chip memory, a hardware-accelerated FFT coprocessor, and an improved C55x core to handle similar workloads. The TMS320C5517 includes many of the same peripherals as the TMS320VC5502 device for backwards compatibility, but also offers newer, faster peripherals for todays needs. Additionally, the newer TMS320C5517 device comes with better support from TI like an improved Chip Support Library with more examples, better Code Composer Studio<sup>™</sup> integration, easier to use EVMs with newer components, and better support on the E2E forum.

#### Basic Feature comparison

All of the documentation referenced in this migration guide can be found in the two product folders [1] [2] shown in Section 7. The descriptions of the behavior and functions of the devices are explained only to the extent to illustrate the differences. This document does not cover the silicon exceptions that may be present on the device. For the list of silicon exceptions and the suggested workarounds, consult the device-specific Silicon Errata [5] [6]. All references in this document to VC5502 refer to the TMS320VC5502 device, unless otherwise specified. All references in this document to C5517 refer to the TMS320C5517 device, unless otherwise specified.

#### 2 Basic Feature comparison

Figure 1 and Table 1 show a comparison of the basic features of the VC5502 and the C5517. The remainder of this document presents a comparison of these features in greater detail, and also provides references to the appropriate documentation for further information.

# Figure 1. TMS320VC5502 and TMS320C5517 DSP Block Diagrams

#### **Table 1. Basic Feature Comparison**

| Device                                      | VC5502                                                                                         | C5517                                                                                                                            |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Processor                                   |                                                                                                | -                                                                                                                                |  |

| Device Family                               | Fixed-Point TMS320C55x Digital Signal<br>Processor                                             | Fixed-Point TMS320C55x Digital Signal<br>Processor                                                                               |  |

| DSP Core                                    | TMS320C55x DSP up to 300MHz                                                                    | TMS320C55x DSP up to 200MHz                                                                                                      |  |

| Silicon Revision                            | 1.0                                                                                            | 2.1                                                                                                                              |  |

| CPU Revision                                | 2.2 (refer to C55x_CPU_revision)                                                               | 3.3 (refer to C55x_CPU_revision)                                                                                                 |  |

| Operating Frequency 200 MHz, 300 MHz        |                                                                                                | 75 MHz, 175 MHz, 200 MHz                                                                                                         |  |

| Operating Voltage Core Voltage: 1.26 V Core |                                                                                                | Core Voltage: 1.05 V, 1.3 V, 1.4 V                                                                                               |  |

| FFT Hardware Accelerator                    | No                                                                                             | Yes – one tightly coupled FFT hardware accelerator that supports 8- to 1024-point (by power of 2) real- and complex-valued FFTs. |  |

| Memory                                      | <u>.</u>                                                                                       | -                                                                                                                                |  |

| Internal Memory                             | 64KB Dual Access RAM (support two reads<br>in one cycle) + 16KB Instruction Cache;<br>32KB ROM | 64KB Dual Access RAM (support two reads<br>in one cycle) + 256KB Single Access RAM<br>(zero-wait state); 128KB ROM               |  |

| DMA Controller                              | 1 (6 channels)    4 DMA controllers each with 4 chanchannels)                                  |                                                                                                                                  |  |

| Device                                                        | VC5502                                                                                                                                  | C5517                                                                                                                                                               |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EMIF Controller                                               | Asynchronous Static RAM (SRAM)<br>Asynchronous EPROM<br>Synchronous DRAM (SDRAM)<br>Synchronous Burst RAM (SBRAM)                       | 8-Bit or 16-Bit NAND Flash<br>1-Bit or 4-Bit ECC 8-Bit and 16-Bit NOR<br>Flash<br>Asynchronous Static RAM (SRAM)<br>SDRAM or Mobile SDRAM (1.8, 2.75, and<br>3.3 V) |  |

| Peripherals                                                   |                                                                                                                                         |                                                                                                                                                                     |  |

| USB                                                           | No                                                                                                                                      | USB 2.0 High- and Full-Speed Device (device mode only)                                                                                                              |  |

| McBSP                                                         | 3 – full-duplex, 128 separately enabled<br>channels, supports CLKSTP (SPI<br>master/slave), multiplexed with UART                       | 1                                                                                                                                                                   |  |

| UART                                                          | 1 - multiplexed with McBSP2                                                                                                             | 1 - programmable baud rates, even, odd, or no PARITY bit generation and detection                                                                                   |  |

| McSPI                                                         | 0                                                                                                                                       | 1 – master and slave, full-duplex,<br>synchronous, serial communication to SPI-<br>compliant external devices (slaves and<br>masters), 128-bytes built-in FIFO      |  |

| SPI                                                           | 0                                                                                                                                       | 1 – master mode only                                                                                                                                                |  |

| 12C                                                           | 1 - fast mode - upto 400 Kbps, supports<br>seven bit or ten bit addressing mode, master<br>and slave                                    | 1 - fast mode - upto 400 Kbps, supports<br>seven bit or ten bit addressing mode, master<br>and slave                                                                |  |

| 12S                                                           | 0                                                                                                                                       | 3 - full-duplex, I2S and DSP modes, word-<br>lengths of 8, 10, 12, 14, 16, 18, 20, 24, or 32<br>bits                                                                |  |

| GPIO                                                          | 8 26                                                                                                                                    |                                                                                                                                                                     |  |

| HPI                                                           | 8-bit or 16-bit HPU                                                                                                                     | 16-bit UHPI                                                                                                                                                         |  |

| ADC                                                           | C No 10-bit 4-Input Successive<br>(SAR) ADC, one 3.6V to                                                                                |                                                                                                                                                                     |  |

| MMC/SD/SDIO No 2 - MMC v3.31, SD Ph<br>v2.0, 4-bit data width |                                                                                                                                         | 2 - MMC v3.31, SD Phys Layer v2.0, SDIO v2.0, 4-bit data width                                                                                                      |  |

| RTC                                                           | No                                                                                                                                      | Yes                                                                                                                                                                 |  |

| GP Timer                                                      | 2 3 32-Bit General-Purpos<br>Timer2 shared with Wat                                                                                     |                                                                                                                                                                     |  |

| Watchdog Timer                                                | 1                                                                                                                                       | 1, shared with GP Timer 2                                                                                                                                           |  |

| JTAG                                                          | Yes                                                                                                                                     | Yes                                                                                                                                                                 |  |

| Package                                                       |                                                                                                                                         |                                                                                                                                                                     |  |

| Package Options                                               | 176-Terminal LQFP (Low-Profile Quad<br>Flatpack) (PGF Suffix)<br>201-Terminal MicroStar BGA (Ball Grid<br>Array) (GZZ and ZZZ Suffixes) | 196-Terminal Pb-Free Plastic BGA (Ball Grid<br>Array) (ZCH Suffix), 0.65-mm Pitch                                                                                   |  |

# Table 1. Basic Feature Comparison (continued)

# 3 Power, Input Clocks, and PLL

# 3.1 Voltage Rails

Table 2 and Table 3 compare the power supplies for C5502 and C5517.

#### Table 2. VC5502 Voltage Rails

| Supply | Description Value                                              |  |

|--------|----------------------------------------------------------------|--|

| CVDD   | Device Supply Voltage 1.26 V                                   |  |

| DVDD   | Device supply voltage, I/O (except DP, DN, PU, SDA, SCL) 3.3 V |  |

| PVDD   | Device supply voltage, PLL 3.3 V                               |  |

Power, Input Clocks, and PLL

# Table 3. C5517 Voltage Rails

| Supply      | Description                                            | Value                                                 |  |

|-------------|--------------------------------------------------------|-------------------------------------------------------|--|

| CVDD        | Digital Core supply voltage                            | 1.05 V (75 MHz)<br>1.3 V (175 MHz)<br>1.4 V (200 MHz) |  |

| DVDDIO      | I/O power supply for non-EMIF and non-RTC I/Os         | 1.8 V, 2.75 V, or 3.3 V                               |  |

| DVDDEMIF    | EMIF I/O power supply                                  | 1.8 V, 2.75 V, or 3.3 V                               |  |

| LDOI        | Analog Pwr Mgmt and LDO Inputs                         | 1.8 V to 3.6 V                                        |  |

| CVDDDRTC    | RTC digital core and RTC oscillator power supply       | 1.05 V, 1.3 V, 1.4 V                                  |  |

| DVDDRTC     | RTC I/O power supply                                   | 1.8 V, 2.75 V, or 3.3 V                               |  |

| VDDA_PLL    | Analog PLL power supply for the system clock generator | 1.3 V                                                 |  |

| USB_VDDPLL  | USB Analog PLL power supply.                           | 3.3 V                                                 |  |

| USB_VDD1P3  | Digital core power supply for USB PHY                  | 1.3 V                                                 |  |

| USB_VDDA1P3 | Analog 1.3V power supply for USB PHY                   | 1.3 V                                                 |  |

| USB_VDDA3P3 | Analog 3.3V power supply for USB PHY 3.3 V             |                                                       |  |

| USB_VDDOSC  | Power supply for USB oscillator                        | 3.3 V                                                 |  |

| VDDA_ANA    | Supply for power management and 10-bit SAR ADC 1.3 V   |                                                       |  |

# 3.2 Power Management

The C5502 does not have power management built in to the device.

The C5517 supports power management and has the following features:

- PLL Power Down

- Peripheral Clock Idling

- Core Voltage Scaling

- RTC-only mode (CORE Voltage off)

- DARAM/SARAM Low Power Modes

- Independent Power Domains

- I/O Voltage Selection

- USB Power Down

- RTC Power Down

# 3.3 Input Clocks

The following tables compare the input clocks for C5502 and C5517.

#### Table 4. VC5502 Input Clocks

| Clock Name Source          |  | Value       |  |

|----------------------------|--|-------------|--|

| X2/CLKIN Master Oscillator |  | 5 to 20 MHz |  |

# Table 5. C5517 Input Clocks

| Clock Name | Source                                                                                                   | Value      |  |

|------------|----------------------------------------------------------------------------------------------------------|------------|--|

| CLKIN      | Input clock 11.2896, 12.0, 12.288, 16.8, or 19.2<br>System clock generator input when CLK_SEL pin = 1    |            |  |

| USB_MXI    | 12-MHz on-chip USB oscillator    12 MHz      System clock generator input when CLK_SEL pin = 0    12 MHz |            |  |

| RTC_XI     | Real-time clock oscillator input. (RTC clock only)                                                       | 32.768 kHz |  |

#### 3.4 PLLs

Both C5502 and C5517 have the following PLLs, driven by an input crystal (X2/CLKIN):

• VC5502

The GPIO4 pin determines the source of the input clock for the PLL. If GPIO4 is low at reset, the internal oscillator and the external crystal will generate an input clock (OSCOUT) for the DSP. If GPIO4 is high, the CLKMD0 bit will be set to '1' and the input clock will be taken directly from the X2/CLKIN pin.

• C5517

The CLK\_SEL pin determines whether the input clock to the PLL comes from the USB oscillator (CLK\_SEL = 0) or the CLKIN pin (CLK\_SEL = 1).

# 4 Boot Modes

Table 6 compares the support for various boot modes on the VC5502 and C5517.

| C5502                                           | C5517 | Boot Type                                         | Description                                                                                                                          |

|-------------------------------------------------|-------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| N Y NOR This mode allows booting from NOR flash |       | This mode allows booting from NOR flash memories. |                                                                                                                                      |

|                                                 |       |                                                   | The C5502 does not support NOR flash boot.                                                                                           |

|                                                 |       |                                                   | For C5517, 16-bit NOR flash boots from all asynchronous CS spaces, system clock generator is in bypass mode.                         |

| N                                               | Y     | NAND                                              | This mode starts downloading code from an NAND memory.                                                                               |

|                                                 |       |                                                   | The C5502 does not support NAND flash boot.                                                                                          |

|                                                 |       |                                                   | For C5517, 16-bit or 8-bit NAND flash data boot, system clock generator is in bypass mode.                                           |

| Y                                               | Ν     | Asynchronous                                      | This mode starts downloading code from an asynchronous memory.                                                                       |

|                                                 |       | Memory                                            | The C5502 supports external asynchronous memory boot (via the EMIF) from 16-bit-wide memory.                                         |

|                                                 |       |                                                   | The C5517 does not support this boot mode.                                                                                           |

| Y                                               | Ν     | Direct Execution-                                 | This mode executes code directly from an asynchronous memory                                                                         |

|                                                 |       | Asynchronous Memory                               | The C5502 supports direct execution (no boot) from external asynchronous memory (via the EMIF) - 32-bit-wide or 16-bit-wide memory.  |

|                                                 |       |                                                   | The C5517 does not support this boot mode.                                                                                           |

| Y                                               | N     | Serial Port Boot                                  | This mode starts booting from the McBSP serial port                                                                                  |

|                                                 |       | (from McBSP)                                      | The C5502 supports serial port boot from the McBSP0 serial port with 16-bit element length.                                          |

|                                                 |       |                                                   | The C5517 does not support this boot mode.                                                                                           |

| Y                                               | Y     | SPI                                               | This mode starts downloading code from an SPI EEPROM or SPI Flash.                                                                   |

|                                                 |       |                                                   | For C5502, Serial (SPI) EPROM Boot (24-bit/16-bit address) via McBSP0.                                                               |

|                                                 |       |                                                   | For C5517, SPI 16-bit or 24-bit address Boot (SPI_CLK < 1 MHz or 10 MHz), system clock generator output = input clock x 3.           |

| Ν                                               | Y     | McSPI                                             | This mode starts downloading code from EEPROM/ Serial Flash through McSPI.                                                           |

|                                                 |       |                                                   | The C5502 does not support McSPI boot.                                                                                               |

|                                                 |       |                                                   | For C5517, McSPI 24-bit address serial flash at 10 MHz or 40 MHz mode.                                                               |

| Y                                               | Y     | I2C                                               | This mode starts downloading code from an I2C EEPROM.                                                                                |

|                                                 |       |                                                   | For C5502, I2C EEPROM (7-bit address).                                                                                               |

|                                                 |       |                                                   | For C5517, I2C 16-bit address Boot, 400 kHz, system clock generator is in bypass mode.                                               |

| Y                                               | Y     | UART                                              | In this mode, the UART sends a BOOTME request to the UART peripheral and waits for a response along with code from a host processor. |

|                                                 |       |                                                   | For C5502, standard UART boot.                                                                                                       |

|                                                 |       |                                                   | For C5517, UART 9600, 57600, 115200 baud boot, system clock generator output = input clock x 3.                                      |

TMS320VC5502 to TMS320C5517 Hardware Migration Guide

#### Table 6. Comparison of Boot Modes on the VC5502 and C5517 (continued)

| C5502 | C5517 | Boot Type | Description                                                                                             |

|-------|-------|-----------|---------------------------------------------------------------------------------------------------------|

| N     | Y     | MMC/SD    | This mode starts booting code from an MMC/SD Controller.                                                |

|       |       |           | The C5502 does not support MMC/SD boot.                                                                 |

|       |       |           | For C5517, SD or SDHC, MMC, or eMMC Controller 0/1 card boot, system clock generator is in bypass mode. |

| Y     | Y     | HPI       | This mode starts booting code from the HPI.                                                             |

|       |       |           | The C5502 supports HPI boot (multiplexed and non-multiplexed)                                           |

|       |       |           | For C5517, UHPI 16-bit multiplexed mode boot, system clock generator output = input clock x 3.          |

| N     | Y     | USB       | This mode starts booting code from the USB device.                                                      |

|       |       |           | The C5502 does not support USB boot.                                                                    |

|       |       |           | For C5517, USB boot, system clock generator output = input clock x 3.                                   |

The C5502 device supports the following boot modes:

- Host-port interface (HPI) boot, both in multiplexed and non-multiplexed modes

- External memory boot (via EMIF) from 16-bit asynchronous memory

- Serial port boot (from McBSP0) with 16-bit element length

- SPI EPROM boot (from McBSP0) supporting EPROMs with 24-bit addresses

- I2C EPROM boot (from I2C) supporting EPROMs larger than 512K bits

- UART boot

- Direct execution (no boot) from 16- or 32-bit external asynchronous memory

The C5517 device supports the following boot modes:

- 16-bit NOR flash data boot, system clock generator is in bypass mode.

- 16-bit or 8-bit NAND flash data boot, system clock generator is in bypass mode.

- UART 9600 baud boot, system clock generator output = input clock x 3

- UART 57600 baud boot, system clock generator output = input clock x 3

- UART 115200 baud boot, system clock generator output = input clock x 3

- SPI 16-bit or 24-bit address Boot (SPI\_CLK < 1 MHz), system clock generator output = input clock x 3

- SPI 16-bit or 24-bit address Boot (SPI\_CLK < 10 MHz), sD or SDHC, MMC, or eMMC Controller 0 card boot, system clock generator is in bypass modeystem clock generator output = input clock x 3

- Polling Mode: Check for valid boot image from peripherals in the following order: NOR, NAND, SPI, I2C, SD/SDHC/MMC/eMMC Controller 0, McSPI, and UART/USB (infinite retry).

- I2C 16-bit address Boot, 400 kHz, system clock generator is in bypass mode.

- SSD or SDHC, MMC, or eMMC Controller 1 card boot, system clock generator is in bypass mode

- Polling Mode: Check for valid boot image from peripherals in the following order: NOR, NAND, SPI, I2C, SD/SDHC/MMC/eMMC Controller 0, SD/SDHC/MMC/eMMC Controller 1, and UART/USB (infinite retry).(2)

- UHPI 16-bit multiplexed mode boot, system clock generator output = input clock x 3

- McSPI 24-bit address serial flash at 10-MHz mode

- McSPI 24-bit address serial flash at 40-MHz mode

- USB boot, system clock generator output = input clock x 3

# 5 Pin Multiplexing

# 5.1 VC5502

The GPIO6 and GPIO7 pins are latched upon the release of reset to configure the pin multiplexing of the VC5502 device. Once set at reset, the pin multiplexing cannot be modified.

The GPIO6 pin is used to select the function of the multiplexed signals in the Parallel Port and the Host Port. The EMIF will be disabled and the HPI will operate in non-multiplexed mode when the GPIO6pin is low during reset. The EMIF will be enabled and the HPI will operate in multiplexed mode when the GPIO6 pin is high during reset.

The GPIO7 pin is used to select the function of the multiplexed signals of Serial Port 2. The UART will be enabled and McBSP2 will be disabled when GPIO7 is low during reset. McBSP2 will be enabled and the UART will be disabled when GPIO7 is high during reset.

# 5.2 C5517

The C5517 pin multiplexing configuration is controlled by software with the EBSR Register.

The EBSR Parallel Port Mode (PPMODE) control bits control the pin multiplexing of the UHPI, SPI, UART, I2S2, I2S3, and GP[31:27, 20:12] pins on the parallel port. Allowable combinations of these peripherals are listed below:

- Mode 0 (16-bit UHPI bus). All 28 signals of the UHPI bus module are routed to the 28 external signals of the parallel port. Note: SDRAM control signals are multiplexed with UHPI bus control signals. In this mode, UHPI bus signals are routed to the control ports, so SDRAM cannot be accessible.

- Mode 1 (SPI, GPIO, UART, I2S2, and SDRAM). 7 signals of the SPI module, 6 GPIO signals, 4 signals of the UART module, 4 signals of the I2S2 module, and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

- Mode 2 (GPIO and SDRAM). 8 GPIO and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

- Mode 3 (SPI, I2S3, and SDRAM). 4 signals of the SPI module, 4 signals of the I2S3 module, and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

- Mode 4 (I2S2, UART, and SDRAM). 4 signals of the I2S2 module, 4 signals of the UART module, and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

- Mode 5 (SPI, UART, and SDRAM). 4 signals of the SPI module, 4 signals of the UART module, and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

- Mode 6 (SPI, I2S2, I2S3, GPIO, and SDRAM). 7 signals of the SPI module, 4 signals of the I2S2 module, 4 signals of the I2S3 module, 6 GPIO, and 7 SDRAM control signals are routed to the 28 external signals of the parallel port.

The two serial port pin mux configurations are controlled by the EBSR Serial Port 1 Mode (SP1MODE) Control Bits and the Serial Port 0 Mode (SP0MODE) Control Bits. Pin multiplexing options for each serial port are listed below.

- Serial Port 1 Mode Control Bits control the pin multiplexing of the MMC/SD1, McSPI, and GPIO signals:

- Mode 0 (MMC1 and SD1). All 6 signals of the MMC1 and SD1 module are routed to the 6 external signals of the serial port 1.

- Mode 1 (McSPI). 6 signals of the McSPI module signals are routed to the 6 external signals of the serial port 1.

- Mode 2 (GP[11:6]). 6 GPIO signals (GP[11:6]) are routed to the 6 external signals of the serial port

1.

- Serial Port 0 Mode Control Bits control the pin multiplexing of the MMC/SD0, I2S0, McBSP, and GPIO signals

- Mode 0 (MMC0 and SD0). All 6 signals of the MMC0 and SD0 module are routed to the 6 external signals of the serial port 0.

- Mode 1 (I2S0 and GP[5:4]). 4 signals of the I2S0 module and 2 GP[5:4] signals are routed to the 6 external signals of the serial port 0.

- Mode 2 (GP[5:0]). 6 GPIO signals (GP[5:0]) are routed to the 6 external signals of the serial port 0.

- Mode 3 (McBSP). 6 signals of the McBSP module are routed to the 6 external signal port 0.

#### 6 Compiler Options

The CC55x Gode Gen Tools require the following compiler target options in order to build object code compatible with the respective CPU revision.

#### 6.1 C5502

- Silicon Revision: 1.0

- CPU Revision: 2.2

- Available Equivalent Compiler Target Options:

- vcore:2.2

- vcpu:2.2

- v5502

- v5502:1.0

#### 6.2 C5517

- Silicon Revision: 2.1

- CPU Revision: 3.3

- Available Equivalent Compiler Target Options:

- vcore:3.3

- vcpu:3.3

- v5515

- v5515:1.0

#### 7 References

- 1. VC5502 Product Page

- 2. C5517 Product Page

- 3. TMS320VC5502 Fixed-Point Digital Signal Processor Data Manual

- 4. TMS320C5517 Fixed-Point Digital Signal Processor

- 5. TMS320VC5502 and TMS320VC5501 Digital Signal Processors Silicon Errata

- 6. TMS320C5517 Fixed-Point Digital Signal Processor Silicon Revision 1.0, 2.0, and 2.1 Silicon Errata

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated