## Migration Between TMS320F2837x and TMS320F2838x

Vivek Singh

#### ABSTRACT

This migration guide describes the hardware and software differences to be aware of when moving between the F2837x and F2838x C2000<sup>™</sup> MCUs. This document highlights the features that are unique between the two devices for all available packages in a device comparison table. Section 2 discusses hardware considerations when migrating between the F2837x and F2838x devices with the 337-ZWT package. The digital general-purpose input/output (GPIO) comparison tables show pin functionality between the two MCUs. This is a good reference for hardware design and signal routing when considering a move between the two devices. Lastly, the F2838x software support is only in EABI format. The EABI migration is discussed in Section 4.

#### Contents

| 1 | Feature Differences Between F2837x and F2838x    | . 2 |

|---|--------------------------------------------------|-----|

| 2 | PCB Hardware Changes                             | 5   |

|   | Feature Differences for System Consideration     |     |

|   | Application Code Migration From F2837x to F2838x |     |

| 5 | References                                       | 33  |

#### List of Figures

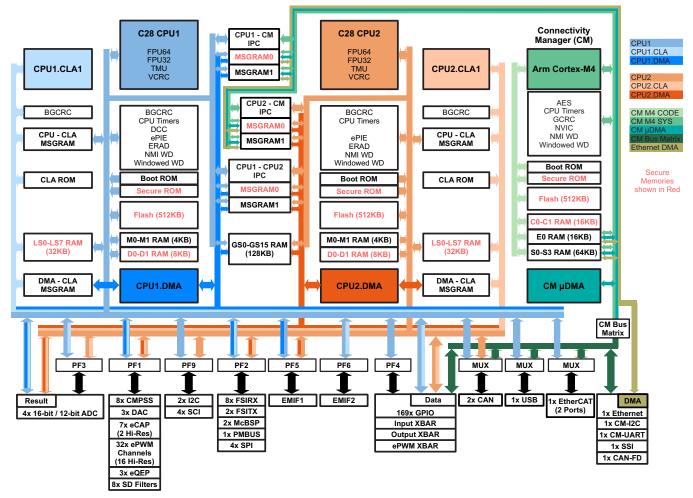

| 1  | F2838x Functional Block Diagram                  | . 2 |

|----|--------------------------------------------------|-----|

|    | List of Tables                                   |     |

| 1  | F28379D and F28388D (Superset) Device Comparison | . 3 |

| 2  | controlCARD Comparison                           | . 6 |

| 3  | PLL Features                                     | . 9 |

| 4  | XCLKOUT Source Select                            | 10  |

| 5  | Pie Channel Legend                               | 11  |

| 6  | PIE Channel Mapping                              | 11  |

| 7  | SYS_ERR Interrupt Input                          | 12  |

| 8  | F2838x CPU1/CPU2 Subsystem Memory                | 13  |

| 9  | DCSM Feature comparison                          | 14  |

| 10 | F2838x ROM contents                              | 15  |

| 11 | Boot-ROM Comparison                              | 15  |

| 12 | ePWM Feature Comparison                          | 16  |

| 13 | eCAP Feature Comparison                          | 17  |

| 14 | SDFM Feature Comparison                          | 18  |

| 15 | Analog Module Instances                          | 19  |

| 16 | Access Control Register                          | 20  |

| 17 | Mux Legend                                       | 22  |

| 18 | GPIO Mux Table Comparison                        | 22  |

| 19 | Section Names                                    | 32  |

| 20 | Flash API Differences                            | 33  |

#### Trademarks

C2000, Code Composer Studio are trademarks of Texas Instruments. Arm, Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All other trademarks are the property of their respective owners.

## 1 Feature Differences Between F2837x and F2838x

F2838x is based on the F2837x MCU architecture with many new features including a connectivity manager (CM) subsystem that provides additional MIPS for communication stacks. It is possible to migrate between F2838x and F2837x with the caveats in this document taken into account.

**NOTE:** This comparison guide focuses on the super-set devices: F28388D and F28379D. Other part numbers in this product family have reduced feature support. For details specific to part numbers, see the device-specific data sheet.

#### 1.1 F2837x and F2838x Feature Comparison

The functional block diagram of F2838x is shown in Figure 1, while the feature comparison of the superset part numbers for the F2837x and F2838x devices are shown in Table 1.

Feature Differences Between F2837x and F2838x

www.ti.com

Table 1. F28379D and F28388D (Superset) Device Comparison

| FEATURE (1)                |                                            | F28388D                                                            | F28379D                                |  |  |

|----------------------------|--------------------------------------------|--------------------------------------------------------------------|----------------------------------------|--|--|

|                            | C28x Subsystem                             |                                                                    |                                        |  |  |

| C28x                       | Number                                     |                                                                    | 2                                      |  |  |

|                            | Frequency (MHz)                            | 2                                                                  | 00                                     |  |  |

|                            | Floating-Point Unit (FPU)                  | 32 bit and 64 bit                                                  | 32 bit                                 |  |  |

|                            | VCRC                                       | Yes                                                                | -                                      |  |  |

|                            | VCU-II                                     | -                                                                  | Yes                                    |  |  |

|                            | ТМU                                        | Yes –                                                              | Туре 0                                 |  |  |

|                            | FINTDIV                                    | Yes                                                                | -                                      |  |  |

| CLA                        | Number                                     | 2 (1 per CPU) – Type 2                                             | 2 (1 per CPU) – Type 1                 |  |  |

|                            | Frequency (MHz)                            | 200                                                                | 200                                    |  |  |

| C28x Flash                 | ,<br>,                                     | 1MB (512KW)<br>[512KB(256KW) per CPU]                              | 1MB (512KW)<br>[512KB (256KW) per CPU] |  |  |

| C28x RAM                   | Dedicated RAM                              | 24KB (12KW) [12k                                                   | KB (6KW) per CPU]                      |  |  |

|                            | Local Shared RAM                           | 64KB (32KW) [32KB<br>(16KW) per CPU]                               | 48KB (24KW)<br>[24KB (12KW) per CPU]   |  |  |

|                            | Global Shared RAM                          | 128KB (64KW) (Sha                                                  | ared between CPUs)                     |  |  |

|                            | Total RAM                                  | 216KB (108KW)                                                      | 200KB (100KW)                          |  |  |

| Background Cyclic Redund   | lancy Check (BGCRC) module                 | 4 (2 per CPU/CLA)                                                  | -                                      |  |  |

| Configurable Logic Block ( | CLB)                                       | 8 tiles                                                            | 4 tiles                                |  |  |

| 32-bit CPU timers          |                                            | 6 (3 pe                                                            | er CPU)                                |  |  |

| 6-Channel DMA              |                                            | 2 (1 per CPU) – Type 0                                             |                                        |  |  |

| Dual-zone Code Security N  | Nodule (DCSM) for on-chip flash and RAM    | Y                                                                  | es                                     |  |  |

| Embedded Real-time Analy   | vsis and Diagnostic (ERAD)                 | Yes                                                                | -                                      |  |  |

| Dual Clock Comparator (D   | CC)                                        | Yes                                                                | -                                      |  |  |

| EMIF                       | EMIF1 (16-bit or 32-bit)                   |                                                                    | 1                                      |  |  |

|                            | EMIF2 (16-bit)                             |                                                                    | 1                                      |  |  |

| External interrupts        |                                            |                                                                    | 5                                      |  |  |

| GPIO                       | I/O pins (shared among CPU1, CPU2, and CM) | 1                                                                  | 69                                     |  |  |

|                            | Input XBAR                                 | Yes                                                                |                                        |  |  |

|                            | Output XBAR                                | Y                                                                  | es                                     |  |  |

| Message RAM                | C28x CPU1, C28x CPU2, and Cortex-M4        | 24KB (4KB each direction<br>between each of the three<br>pairs)    | 4KB [2KB per CPU]                      |  |  |

|                            | C28x CPUs and CLAs                         |                                                                    | ion between each CPU and pair)         |  |  |

|                            | DMAs and CLAs                              | 1KB (256 bytes each<br>direction between each<br>DMA and CLA pair) | -                                      |  |  |

| Nonmaskable Interrupt Wa   | tchdog (NMIWD) timers                      | 2 (1 pe                                                            | er CPU)                                |  |  |

| Watchdog (WD) timers       |                                            | 2 (1 pe                                                            | er CPU)                                |  |  |

|                            | Connectivity Manager (CM) S                | Subsystem                                                          |                                        |  |  |

| Arm® Cortex®-M4            |                                            | 125 MHz                                                            | -                                      |  |  |

| M4 Flash                   |                                            | 512KB                                                              | -                                      |  |  |

| M4 RAM                     |                                            | 96KB                                                               | -                                      |  |  |

| Advanced Encryption Stand  | dard (AES) Accelerator                     | 1                                                                  | -                                      |  |  |

| CPU timers                 |                                            | 3                                                                  | -                                      |  |  |

| Generic Cyclic Redundanc   | y Check (GCRC) module                      | 1                                                                  | -                                      |  |  |

| Memory Protection Unit (M  | PU) for Cortex-M4, µDMA, and Ethernet DMA  | 3                                                                  | -                                      |  |  |

| CM Nonmaskable Interrupt   | (CMNMI) Module                             | 1                                                                  | -                                      |  |  |

## Table 1. F28379D and F28388D (Superset) Device Comparison (continued)

| FEATURE (1)                       |                                           | F28388D                                                 | F28379D                                         |  |

|-----------------------------------|-------------------------------------------|---------------------------------------------------------|-------------------------------------------------|--|

| Trace Port Interface Unit (TPIU)  |                                           | 1                                                       | -                                               |  |

| μDMA                              |                                           | 1                                                       | -                                               |  |

| Watchdog (WD) timer               |                                           | 1                                                       | -                                               |  |

|                                   | C28x Analog Peripher                      | als                                                     |                                                 |  |

| Analog-to-Digital Converter (ADC  | C) (configurable to 12-bit or 16-bit)     |                                                         | 4                                               |  |

| ADC 16-bit mode                   | MSPS                                      | 1                                                       | .1                                              |  |

|                                   | Conversion Time (ns)                      | 9                                                       | 15                                              |  |

|                                   | Input channels (single-ended mode)        | 24                                                      | -                                               |  |

|                                   | Input channels (differential mode)        |                                                         | 12                                              |  |

| ADC 12-bit mode                   | MSPS                                      | 3                                                       | 9.5                                             |  |

|                                   | Conversion Time (ns)                      | 2                                                       | 80                                              |  |

|                                   | Input channels (single-ended)             |                                                         | 24                                              |  |

| Temperature sensor                |                                           |                                                         | 1                                               |  |

| •                                 | ) (each CMPSS has two comparators and two |                                                         | 8                                               |  |

| Buffered Digital-to-Analog Conve  | rter (DAC)                                |                                                         | 3                                               |  |

| C28x Control Peripherals          |                                           |                                                         |                                                 |  |

| eCAP/HRCAP                        | Total inputs                              | 7 – Type 1                                              | 6 – Туре 0                                      |  |

|                                   | Channels with high-resolution capability  | 2                                                       | -                                               |  |

| ePWM/HRPWM                        | Total channels                            | 32 – Type 4                                             |                                                 |  |

|                                   | Channels with high-resolution capability  |                                                         | 16                                              |  |

| ePWM XBAR                         |                                           | Yes                                                     |                                                 |  |

| eQEP modules                      |                                           | 3 – Type 2                                              |                                                 |  |

| SDFM channels                     |                                           | 8 – Type 2                                              |                                                 |  |

|                                   | C28x Communications Per                   |                                                         |                                                 |  |

| Fast Serial Interface (FSI) RX    |                                           | 8 – Type 1                                              |                                                 |  |

| Fast Serial Interface (FSI) TX    |                                           | 2 – Type 1                                              | _                                               |  |

| Inter-Integrated Circuit (I2C)    |                                           |                                                         | Type 0                                          |  |

| Multichannel Buffered Serial Port | t (McBSP)                                 | 2 – Type 1                                              |                                                 |  |

| Power Management Bus (PMBus       |                                           | 1 – Type 0                                              | -                                               |  |

| Serial Communications Interface   | -                                         | 4 – Type 0                                              |                                                 |  |

| Serial Peripheral Interface (SPI) |                                           | 4 – Type 2 3 – Type 2                                   |                                                 |  |

| Controller Area Network (CAN) 2   | .0B                                       | 2 – Type 0 (can be assigned to CPU1, CPU2,              | 2 – Type 0 (can be<br>assigned to CPU1 or CPU2) |  |

| Universal Serial Bus (USB)        |                                           | or CM)<br>1 – Type 0 (can be<br>assigned to CPU1 or CM) | 1 – Type 0 (only on CPU1)                       |  |

| uPP                               |                                           | -                                                       | 1                                               |  |

|                                   | Connectivity Manager (CM) Communic        | cations Peripherals                                     | 1                                               |  |

| CAN with Flexible Data-Rate (CA   |                                           | 1                                                       | -                                               |  |

| Ethernet for Control Automation   | ,                                         | 1 (can be assigned to<br>CPU1 or CM)                    |                                                 |  |

| Ethernet Media Access Controlle   | r (EMAC)                                  | 1                                                       | -                                               |  |

| CM Inter-Integrated Circuit (CM-I | 2C)                                       | 1                                                       | -                                               |  |

| Synchronous Serial Interface (SS  | ,                                         | 1                                                       | -                                               |  |

| CM Universal Asynchronous Rec     | ,                                         | 1                                                       | -                                               |  |

| Package Options                   |                                           | 1                                                       | <u> </u>                                        |  |

| Package Options                   | 337-Ball ZWT                              | Y                                                       | es                                              |  |

|                                   | 176-Pin PTP                               | future                                                  | Yes                                             |  |

| FEATURE (1) |             | F28388D | F28379D |

|-------------|-------------|---------|---------|

|             | 100-Pin PZP | No      | Yes     |

#### Table 1. F28379D and F28388D (Superset) Device Comparison (continued)

(1) A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. For more information, see the C2000 Real-Time Control Peripherals Reference Guide.

## 2 PCB Hardware Changes

This section describes considerations to take when switching boards between the F2837x and F2838x devices.

## 2.1 VDD Pin

The F2838x requires a 56  $\Omega$  resistor between VDD and VSS. If a F2837x PCB design needs to be reused for F2838x without PCB modification, it is acceptable to replace a single VDD decoupling capacitor with a 56  $\Omega$  resistor.

## 2.2 VREGENZ Pin

Internal VREG is not supported on the F2838x device. Pin that has VREGENZ functions on F2837x is not internally connected on F2838x. It may be left open or connected to any voltage within the maximum operating conditions.

## 2.3 Analog Pin Assignment

Analog pin mapping on F2838x is the same as that on F2837x. For analog pin connections, see the guidelines provided in the *TMS320F2838x Microcontrollers With Connectivity Manager Data Manual*.

## 2.4 GPIO Pin Assignment

The number of GPIO pins are identical on F2837x and F2838x devices. All functions available on each pin on F2837x are also available on F2838x for the modules that are common between two devices. Additional mux options have been provided for new modules as well as for some common modules.

For more information, see Section 3.6.1.

## 2.5 controlCARD

The F2838x device controlCARD has some changes due to additional modules like EtherCAT and EtherNET.

Table 2 provides details on some key differences between F2837x and the F2838x controlCARD.

| Feature                          | Short Description                                                                                             | F2838x                                                            | F2837x                            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|

| Input Clock Input clock via XTAL |                                                                                                               | Rev-A - 20MHz default<br>Rev-B - 25MHz default                    | 20MHz                             |

| HD connector                     | 60 pin high density connector support<br>EMIF                                                                 | No. Removed to enable ECAT and<br>ENET support                    | Yes                               |

| EtherCAT                         | -                                                                                                             | Yes                                                               | NA                                |

| Ethernet                         | -                                                                                                             | Yes                                                               | NA                                |

| EMIF support<br>through HSEC     | Edge connector's EMIF support                                                                                 | Yes (only 8 bit Data and no WAIT)                                 | Yes                               |

| USB                              | USB - Ye                                                                                                      |                                                                   | Yes, selection jumper<br>required |

| VDD and VDDIO                    | Monitoring locations for VDDIO and VDD                                                                        | Test point and brought to HSEC for<br>external monitoring         | Test Points                       |

| ERRORSTS Pin                     | ERRORSTS Pin Monitoring locations for ERRORSTS Pin Pin Test point and brought to HSEC for external monitoring |                                                                   | Test Point                        |

| FSI header                       |                                                                                                               | Yes<br>Rev-A - 1 data line support<br>Rev-B - 2 data line support | NA                                |

Table 2. controlCARD Comparison

## 3 Feature Differences for System Consideration

This section outlines the differences and similarities that exist when migrating between the F2838x and F2837x devices.

## 3.1 New Features in F2838x Device

This section outlines features that are new on the F2838x device.

#### 3.1.1 Fast Integer Division (FINTDIV)

The C28x processor Fast Integer Division (FINTDIV) unit provides an open and scalable approach to facilitate different data type sizes (16/16, 32/16, 32/32, 64/32, 64/64), signed and unsigned or mixed data type versions (ui32/ui32, i32/ui32, i32/i32). For additional performance, the operations return both the integer and remainder portion of the calculation simultaneously. The division operations are interruptible so as to enable minimum latency for higher priority tasks, a critical requirement for high performance real-time control applications. Unique to this fast integer division unit is support for Truncated, Modulo and Euclidean division formats without any cycle penalty. Each of these formats represents the integer and remainder result in different forms. Below is a brief summary of the various division formats:

- Truncated format is the traditional division performed in C language (/ = integer, % = remainder), however, the integer value is non-linear around zero.

- Modulo division is commonly found when performing division on an Excel worksheet.

- Euclidean format is another format similar to Modulo, the difference is the sign on the remainder value.

Both the Euclidean and Modulo formats are more appropriate for precise control applications because the integer value is linear around the zero point and avoid potential calculation hysteresis. The C28x compiler supports all three division formats for all data types.

## 3.1.2 VCRC Unit

The VCRC unit extends the capabilities of the C28x CPU by adding additional instructions to support Cyclic Redundancy Check (CRC) or a polynomial code checksum. The VCRC unit on F2838x is a subset of the VCU-II unit on F2837x.

## 3.1.3 EtherCAT Slave Controller (ESC)

The EtherCAT Slave Controller (ESC) is a new module on the F2838x device. Ethernet for Control Automation Technology (EtherCAT) is an Ethernet-based field bus system that was invented by Beckhoff Automation. EtherCAT is standardized in IEC 61158. All of the slave nodes that are connected to the bus interpret, process, and modify data as data is addressed to them, without having to buffer the frame inside the node. It supports up to 2 MII ports to connect to external PHYs. For more information, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

## 3.1.4 Background CRC (BGCRC)

The Background CRC (BGCRC) is a new module for the F2838x device that can compute the CRC-32 value of a configurable block of memory. It accomplishes this by fetching the specified block of memory during idle cycles (when the CPU, CLA, or DMA is not accessing the memory block). It is an upgrade on the CLAPROMCRC found in the F28004x device to test more memories than just the CLA ROM. For more information on the BGCRC, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

## 3.1.5 Diagnostic Features (PBIST/HWBIST)

The F2837x documents refer to PBIST as the controller that executes configurable memory tests routines as part of the boot up sequence. In F2838x documents and in future C2000 device documents, this module is referred to as memory power on self-test (MPOST). MPOST is enabled as part of the boot up sequence in both the F2837x and F2838x devices. HWBIST is a self-test controller for the CPU for fault coverage in safety applications. HWBIST can be invoked from user application code on both F2838x and F2837x device.

## 3.1.6 Power Management Bus Module (PMBus)

The Power Management Bus Module (PMBus) is a new module for the F2838x devices, which provides an interface between the microcontroller and is device compliant with the SMI Forum PMBus Specification Part I version 1.0 and Part II version 1.1. PMBus is based on SMBus that uses a similar physical layer to I2C. It is assumed that you are familiar with the PMBus, SMBus, and I2C bus specifications. For more information on the PMBus, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

## 3.1.7 Fast Serial Interface (FSI)

Fast Serial Interface (FSI) is a new module for the F2838x devices that is a serial communication peripheral capable of reliable high-speed communication across isolation devices. Galvanic isolation devices are used in situations where two different electronic circuits, that do not have common power and ground connections, must exchange information. Though isolation devices facilitate these signal communications, they can also introduce a large delay on the signal lines and add skew between the signals. The FSI is designed specifically to ensure reliable high-speed communication for system scenarios that involve communication across isolation barriers without adding components. The FSI consists of independent transmitter (FSITX) and receiver (FSIRX) cores. The FSITX and FSIRX cores are configured and operated independently. For more information on the FSI, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

## 3.1.8 Embedded Real-time Analysis and Diagnostic (ERAD)

The Embedded Real-time Analysis and Diagnostic (ERAD) is a new module for F2838x devices that enhance the debug and system-analysis capabilities of the device. The ERAD module consists of the Enhanced Bus Comparator units and the System Event Counter units. The Enhanced Bus Comparator units are used to generate hardware breakpoints, hardware watch points, and other output events. The System Event Counter units are used to analyze and profile the system.

The key features provided by the ERAD module are listed below:

- Provides eight additional hardware break points, hence total 10 hardware breakpoints are available during debug.

- Monitor data read address buses, data write address buses, data write data bus, and generate RTOSINT

- Generate an event output which can be used by other modules. This is done through monitoring any of the program address buses, Virtual Program Counter (VPC), or the Program Counter of the CPU.

- System Event Counter (SEC) units can count duration between specified memory reads and writes.

- System Event Counter (SEC) units can count system events (such as interrupts) as well as duration between such events.

- System Event Counter (SEC) units can measure maximum amount of time spent in between a pair of events, measured over multiple iterations.

- It has cyclic redundancy check (CRC) units that monitor CPU buses and compute CRC when the selftest code is executed.

- The ERAD module is accessible by the debugger and by the application software. This significantly

increases the debug capabilities of many real-time systems.

For more details on the ERAD, see the TMS320F2838x Microcontrollers Technical Reference Manual.

#### 3.1.9 Dual-Clock Comparator (DCC)

The Dual-Clock Comparator (DCC) is a new module for the F2838x devices that is used for evaluating and monitoring the clock input based on a second clock, which can be a more accurate and reliable version. This instrumentation is used to detect faults in clock source or clock structures, thereby enhancing the system's safety metrics.

The main features of each of the DCC modules are:

- Allows the application to ensure that a fixed ratio is maintained between frequencies of two clock signals

- Supports the definition of a programmable tolerance window in terms of the number of reference clock cycles

- Supports continuous monitoring without requiring application intervention

- Supports a single-sequence mode for spot measurements

- Allows the selection of a clock source for each of the counters, resulting in several specific use cases

For more details on the DCC, see the TMS320F2838x Microcontrollers Technical Reference Manual.

#### 3.1.10 Connectivity Manager (CM)

Similar to F2837x, F2838x supports dual-core C28x architecture. However, it also has a new connectivity manager subsystem. The connectivity manager (CM) subsystem is based on the industry standard 32-bit Arm Cortex-M4 CPU and features a wide variety of communication peripherals as listed below:

- Shared with CPU1 EtherCAT, USB, DCAN

- Accessible by CM only EtherNET, MCAN (CAN-FD), UART, SSI, I2C

Targeting performance and flexibility, the connectivity manager is based on 125 MHz Cortex-M4 architecture and provides a variety of integrated memories including its own Flash Bank. The primary goals of the Connectivity Manager (CM) are to:

- Allow easy porting of standard communication software stacks from the Arm eco system

- Provide additional communication MIPS

For details on the Connectivity Manager (CM), see the TMS320F2838x Microcontrollers Technical Reference Manual.

## 3.2 Features Differences/Enhancements in F2838x

#### 3.2.1 System

#### 3.2.1.1 Reset

Reset topology on F2838x is the same as on F2837x. Just like F2837x, CPU1 controls the reset for CPU2 and CM as well. CPU1 system reset (CPU1.SYSRSn) resets CPU2 and CM subsystem as well. SOFTPRESx registers, that have reset control bits for all the peripherals accessible from CPU1 (and CPU2 if shared with CPU2), are accessible from CPU1 only. CM has CMSOFTPRESETx registers to control the reset for all the peripherals accessible from CM.

Below is the list of new enhancements on F2838x:

- A new software configuration register SIMRESET has been added in CPU\_SYS\_REGS. This register has two bit field to issue software reset:

- XRSn Writing to this bit will pull the XRSn pin low for 512 INTOSC1 clock cycles.

- CPU1RSn Writing a 1 to this field generates a reset to CPU1.

- A new Reset Cause Clear (RESCCLR) register has been added to clear the status in the Reset Cause (RESC) register.

For more details on Reset, see the TMS320F2838x Microcontrollers Technical Reference Manual.

#### 3.2.1.2 Clocking

#### 3.2.1.2.1 PLL

The PLL blocks of F2837x and F2838x devices are different. Table 3 lists the PLL features for both of these devices for comparison. For more information, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

| Feature                      | F2838x        | F2837x        |

|------------------------------|---------------|---------------|

| VCO Range                    | 220 - 600 MHz | 120 - 400 MHz |

| PLL Raw Clock Range          | 6 - 400 MHz   | 120 - 400 MHz |

| X1 Input Range (PLL enabled) | 10 - 25 MHz   | 2 - 20 MHz    |

| REFCLK Divider               | Yes [132]     | No            |

| PLL Slip Detect              | No (use DCC)  | Yes           |

| Fractional PLLMULT           | No            | Yes           |

#### **Table 3. PLL Features**

Due to the differences in register names and bit fields between the two devices of the PLL module, TI recommends to use the PLL setup function, SysCtrl\_setClock() in C2000Ware to ensure proper PLL setting.

#### 3.2.1.2.2 X1CNT

Similar to F2837x, F2838x also has the X1CNT counter that counts the X1 clock pulse. This counter can be used to check that the X1 clock is running before switching the clock source to the X1 clock. But, on F2837x, this counter did not have a clear mechanism to clear the counter to 0 after it reaches to maximum value of 0x3FF. On F2838x, a configuration bit has been added to the X1CNT (X1CNT.CLR) register to clear the counter to 0.

#### 3.2.1.2.3 XCLKOUT

Similar to F2837x, F2838x supports the XCLKOUT feature. On F2838x, the following additional source has been added to XCLKOUT. Because of this, the LKSRCCTL3.XCLKOUTSEL register bit field has been extended to 4 bit instead of 3.

| XCLKOUTSEL | F2838x                       | F2837x                       |

|------------|------------------------------|------------------------------|

| 000        | PLLSYSCLK (default on reset) | PLLSYSCLK (default on reset) |

| 001        | SYSPLLCLK                    | PLLRAWCLK                    |

| 010        | CPU1.SYSCLK                  | CPU1.SYSCLK                  |

| 011        | CPU2.SYSCLK                  | CPU2.SYSCLK                  |

| 100        | AUXPLLCLK                    | AUXPLLRAWCLK                 |

| 101        | INTOSC1                      | INTOSC1                      |

| 110        | INTOSC2                      | INTOSC2                      |

| 111        | XTAL OSC (o/p clock)         | Reserved                     |

| 1000       | CMCLK                        | NA                           |

| 1100       | PLLRAWCLK                    | NA                           |

| 1101       | AUXPLLRAWCLK                 | NA                           |

| others     | Reserved                     | NA                           |

#### Table 4. XCLKOUT Source Select

Also on the F2838x devices, XCLKOUT has been connected to one of the inputs of the OUTPUTXBAR switch to provide more flexibility to user.

#### 3.2.1.3 Pie Channel Mapping and Interrupt

Pie channel mapping between F2837x and F2838x is different due to the peripheral module changes between these devices.

Table 6 summarizes the common and unique pie channels on these two devices.

## Table 5. Pie Channel Legend

| Color | Description                                         |  |  |  |  |  |

|-------|-----------------------------------------------------|--|--|--|--|--|

|       | channel common for both devices                     |  |  |  |  |  |

|       | Pie channel applicable only for F2837x              |  |  |  |  |  |

|       | F2837x INT has been replaced with new INT on F2838x |  |  |  |  |  |

|       | Pie channel applicable only for F2838x              |  |  |  |  |  |

|         | INTx.1       | INTx.2        | INTx.3       | INTx.4        | INTx.5        | INTx.6        | INTx.7              | INTx.8               | INTx.9                         | INTx.10                        | INTx.11                                            | INTx.12                                               | INTx.13              | INTx.14                      | INTx.15              | INTx.16              |

|---------|--------------|---------------|--------------|---------------|---------------|---------------|---------------------|----------------------|--------------------------------|--------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------|------------------------------|----------------------|----------------------|

| INT1.y  | ADCA1        | ADCB1         | ADCC1        | XINT1         | XINT2         | ADCD1         | TIMER0              | WAKE/<br>WDINT       | I2CA                           | SYS_<br>ERR                    | ECAT<br>SYNC0<br>(CPU1 only)                       | ECAT<br>INTn<br>(CPU1 only)                           | CIPC0                | CIPC1                        | CIPC2                | CIPC3                |

| INT2.y  | EPWM1_<br>TZ | EPWM2_<br>TZ  | EPWM3_<br>TZ | EPWM4_<br>TZ  | EPWM5_<br>TZ  | EPWM6_<br>TZ  | EPWM7_<br>TZ        | EPWM8_<br>TZ         | EPWM9_<br>TZ                   | EPWM10_<br>TZ                  | EPWM11_<br>TZ                                      | EPWM12_<br>TZ                                         | EPWM13_<br>TZ        | EPWM14_<br>TZ                | EPWM15_<br>TZ        | EPWM16_<br>TZ        |

| INT3.y  | EPWM1        | EPWM2         | EPWM3        | EPWM4         | EPWM5         | EPWM6         | EPWM7               | EPWM8                | EPWM9                          | EPWM10                         | EPWM11                                             | EPWM12                                                | EPWM13               | EPWM14                       | EPWM15               | EPWM16               |

| INT4.y  | ECAP1        | ECAP2         | ECAP3        | ECAP4         | ECAP5         | ECAP6         | ECAP7               | _ (1)                | FSITXA_<br>INT1                | FSITXA_<br>INT2                | FSITXB_<br>INT1                                    | FSITXB_<br>INT2                                       | FSIRXA_<br>INT1      | FSIRXA_<br>INT2              | FSIRXB_<br>INT1      | FSIRXB_<br>INT2      |

| INT5.y  | EQEP1        | EQEP2         | EQEP3        | -             | CLB1          | CLB2          | CLB3                | CLB4                 | SDFM1                          | SDFM2                          | ECAT<br>RSTINTn<br>(CPU1 only)                     | ECAT<br>SYNC1<br>(CPU1 only)                          | SDFM1<br>DR1         | SDFM1<br>DR2                 | SDFM1<br>DR3         | SDFM1<br>DR4         |

| INT6.y  | SPIA_RX      | SPIA_TX       | SPIB_RX      | SPIB_TX       | MCBSPA_<br>RX | MCBSPA_<br>TX | MCBSPB_<br>RX       | MCBSPB_<br>TX        | SPIC_RX                        | SPIC_TX                        | SPID_RX                                            | SPID_TX                                               | SDFM2<br>DR1         | SDFM2<br>DR2                 | SDFM2<br>DR3         | SDFM2<br>DR4         |

| INT7.y  | DMA_CH1      | DMA_CH2       | DMA_CH3      | DMA_CH4       | DMA_CH5       | DMA_CH6       | -                   | -                    | FSIRXC_<br>INT1                | FSIRXC_<br>INT2                | FSIRXD_<br>INT1                                    | FSIRXD_<br>INT2                                       | FSIRXE_<br>INT1      | FSIRXE_<br>INT2              | FSIRXF_<br>INT1      | FSIRXF_<br>INT2      |

| INT8.y  | I2CA         | I2CA_<br>FIFO | I2CB         | I2CB_<br>FIFO | SCIC_RX       | SCIC_TX       | SCID_RX             | SCID_TX              | FSIRXG_<br>INT1                | FSIRXG_<br>INT2                | FSIRXH_<br>INT1                                    | FSIRXH_<br>INT2                                       | CLB5                 | CLB6                         | CLB7                 | CLB8                 |

| INT9.y  | SCIA_RX      | SCIA_TX       | SCIB_RX      | SCIB_TX       | CANA_0        | CANA_1        | CANB_0              | CANB_1               | MCANSS_<br>INT0<br>(CPU1 only) | MCANSS_<br>INT1<br>(CPU1 only) | MCANSS_<br>ECC_<br>CORR_<br>PUL_INT<br>(CPU1 only) | MCANSS_<br>WAKE_<br>AND_TS_<br>PLS_INT<br>(CPU1 only) | PMBUSA               | CM_<br>STATUS<br>(CPU1 only) | USBA<br>(CPU1 only)  | -                    |

| INT10.y | ADCA_<br>EVT | ADCA2         | ADCA3        | ADCA4         | ADCB_<br>EVT  | ADCB2         | ADCB3               | ADCB4                | ADCC_EVT                       | ADCC2                          | ADCC3                                              | ADCC4                                                 | ADCD_EVT             | ADCD2                        | ADCD3                | ADCD4                |

| INT11.y | CLA1_1       | CLA1_2        | CLA1_3       | CLA1_4        | CLA1_5        | CLA1_6        | CLA1_7              | CLA1_8               | CMTOCPUx<br>IPCINTR0           | CMTOCPUx<br>IPCINTR1           | CMTOCPUx<br>IPCINTR2                               | CMTOCPUx<br>IPCINTR3                                  | CMTOCPUx<br>IPCINTR4 | CMTOCPUx<br>IPCINTR5         | CMTOCPUx<br>IPCINTR6 | CMTOCPUx<br>IPCINTR7 |

| INT12.y | XINT3        | XINT4         | XINT5        | MPOST         | FMC.<br>DONE  | VCU           | FPU<br>OVER<br>FLOW | FPU<br>UNDER<br>FLOW | EMIF_<br>ERROR                 | ECAP6<br>INT2                  | ECAP7<br>INT2                                      | RAM_ACCE<br>SS_VIOLAT<br>ION                          | CPUxCRC_<br>INT      | CLA1CRC_<br>INT              | CLA<br>OVER<br>FLOW  | CLA<br>UNDER<br>FLOW |

Table 6. PIE Channel Mapping

(1) Cells marked "-" are Reserved. CPUx is CPU1 for CPU1 PIE and CPU2 for CPU2 PIE.

#### 3.2.1.3.1 SYS\_ERR Interrupt

On the F2838x devices, most of the system level error interrupts are combined into one interrupt called SYS\_ERR interrupt.

Table 7 shows a list of all the interrupts that are combined into SYS\_ERR interrupt.

| Input                 | Description                                | F2838x            | F2837x                         |

|-----------------------|--------------------------------------------|-------------------|--------------------------------|

| DCC2                  | Interrupt from DCC2 module                 |                   | NA                             |

| DCC1                  | Interrupt from DCC1 module                 |                   | NA                             |

| DCC0                  | Interrupt from DCC0 module                 |                   | NA                             |

| RAM_ACC_VIOL          | RAM memory access violation interrupt      | SYS_ERR Interrupt | Mapped on PIE Channel INT12.12 |

| FLASH_CORRECTABLE_ERR | Flash Correctable Error interrupt          |                   | Mapped on PIE Channel INT12.11 |

| RAM_CORRECTABLE_ERR   | RAM Correctable Error interrupt            |                   | Mapped on PIE Channel INT12.10 |

| EMIF_ERR              | Error interrupt from EMIF1 or EMIF2 module |                   | Mapped on PIE Channel INT12.9  |

| Table 7. | SYS_ | ERR | Interrupt | Input |

|----------|------|-----|-----------|-------|

|----------|------|-----|-----------|-------|

All of the input to the SYS\_ERR interrupt are latched in the SYS\_ERR\_INT\_FLG register if the respective bit in the SYS\_ERR\_MASK register is cleared. You need to configure the SYS\_ERR registers in addition to the configuration done on F2837x in order to trigger the SYS\_ERR interrupt from any of these inputs.

#### 3.2.1.4 ERRORSTS Pin

The Following enhancement have been made on the F2838x devices for the ERRORSTS pin logic:

- Polarity of the Error pin has been made configurable (configure ERRORCTL.ERRORPOLSEL). Default polarity is active low, which is opposite of F2837x (active high).

- To enable testing of the Error pin, capability to force and clear the Error pin from software has been provided.

- Additional sources of error have been added to ERRORSTS:

- CPU1 Watchdog reset.

- Error on a PIE vector fetch.

- NMI on CM

#### 3.2.2 Watchdog and NMI Watchdog

Following changes have been made to watchdog and NMI watchdog logic on F2838x device -

- Watchdog module on F2837x device has fixed divider of /512 where as F2838x device has programmable divider (WDCR.WDPRECLKDIV) to divide the input clock from /2 to /4096.

- On both device NMI watchdog get trigger by multiple NMI source and status of all the NMI sources get updated in NMIFLG register. On F2837x device all the status bits in NMIFLG registers get reset by XRSn whereas on F2838x these status bits get reset by SYSRSn.

- Below is the list of new NMI source on F2838x device:

- CRC\_FAIL CRC fail status from BGCRC module

- ECATNMIn NMI from EtherCAT (ESC) module

- CMNMIWDRSn NMI when CM NMIWD trigger reset to CM subsystem

- ERADNMI NMI from ERAD module

#### 3.2.3 Memory

#### 3.2.3.1 Internal SRAM/ROM

Total amount of internal RAMs and ROM has been increased on F2838x compared to F2837x. Also some enhancements have been made in the RAM/ROM controller on F2838x.

Below are some of the enhancements on the F2838x devices:

- All ROM on the F2838x devices are Parity protected and also have test logic to test Parity hardware.

- All LSxRAM on the F2838x devices are ECC protected.

- On the F2837x CPU debugger, access was not allowed to the CLA program RAM. On the F2838x CPU debug, access is allowed to the CLA program RAM.

- On the F2838x CLA-DMA, MSG RAMs have been added to enable CLA to use DMA for data transfer.

- Size of IPC MSG RAMs between all the CPU have been increased (2 block of 2KB).

#### 3.2.3.2 Flash

Flash memory logic on F2838x remains the same as on F2837x. Similar to F2837x, every CPU subsystem has 512KB of flash (total 1.5MB flash). The F2837x device family has parts with 1MB flash on CPU1. This option is not available on any parts in the F2838x device family. CPU1 has max 512KB of flash on all the parts.

Table 8 shows the different memory blocks available on the CPU1/CPU2 subsystem of the F2838x devices. The features highlighted in green are new or enhanced from F2837x.

| Memory Block          | Size (On each<br>CPU) | CPUx Access | CPUx.DMA<br>Access | CPUx.CLA<br>Access | ECC/Parity | Secure          |

|-----------------------|-----------------------|-------------|--------------------|--------------------|------------|-----------------|

| CPU BOOT ROM          | 96KB                  | Y           | N                  | N                  | PARITY     | NO              |

| CPU SECURE<br>ROM     | 64KB                  | Y           | Ν                  | Ν                  | PARITY     | YES             |

| CLA DATA ROM          | 8KB                   | Y           | N                  | Y                  | PARITY     | NO              |

| Flash                 | 512KB                 | Y           | N                  | Ν                  | ECC        | YES             |

| USER OTP              | 2KB                   | Y           | N                  | N                  | ECC        | YES (only CPU1) |

| MxRAM                 | 2x2KB                 | Y           | N                  | Ν                  | ECC        | NO              |

| DxRAM                 | 2x4KB                 | Y           | N                  | Ν                  | ECC        | YES             |

| LSxRAM                | 8x4KB                 | Y           | N                  | Y                  | ECC        | YES             |

| GSxRAM (total)        | 16x8KB                | Y           | Y                  | Ν                  | PARITY     | NO              |

| CPU-TO-CPU<br>MSGRAM0 | 2x2KB                 | Y           | Y                  | N                  | PARITY     | YES             |

| CPU-TO-CPU<br>MSGRAM1 | 2x2KB                 | Y           | Y                  | Ν                  | PARITY     | NO              |

| CPU-CLA<br>MSGRAM     | 2x256B                | Y           | Ν                  | Y                  | PARITY     | NO              |

| CLA-DMA<br>MSGRAM     | 2x256B                | Y           | Y                  | Y                  | PARITY     | NO              |

#### Table 8. F2838x CPU1/CPU2 Subsystem Memory

#### 3.2.4 Dual Code Security Module (DCSM)

Dual Code Security Module (DCSM) has been enhanced on the F2838x devices to provide some additional feature. One major difference on the F2838x devices is that instead of each CPU subsystem having their own dual-zones (Zone1 and Zone2), there are only two zones and secure resources of all the CPU subsystems are allocated to these two zones. Only the security settings programmed in CPU1 USER OTP and CPU2 and CM USER OTP are available to program your application code or data.

Table 9 shows the new and enhanced security features on the F2838x devices.

| Table 9. | DCSM | Feature | comparison |

|----------|------|---------|------------|

|----------|------|---------|------------|

| Feature                              | Short Description                                             | F2838x                                                                                                              | F2837x                                                           |

|--------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Dual Zone                            | Two independent security zone for 3rd<br>party development    | Only two zones on device and<br>secure resources of all CPU<br>subsystems are allocated to these<br>two zones only. | CPU1 and CPU2 each have separate two zones                       |

| Security Settings                    | Security Settings are programmed in USER OTP                  | All security settings are<br>programmed in CPU1 USER OTP<br>only.                                                   | CPU1 and CPU2 have<br>security settings in their own<br>USER OTP |

| Default Password                     | All 4 x 32 bit password values are<br>0xFFFF_FFF              | ALL_1 password is invalid<br>password and makes device<br>unlock. TI programs few bits of<br>CSMPSWD1 to 0.         | ALL_1 password makes zone un-secure                              |

| Number of valid<br>Zone_Select_Block | Zone_Select_Block address is based on<br>link pointer         | 15                                                                                                                  | 30                                                               |

| JTAGLOCK                             | Feature to disable the JTAG access on device                  | YES. Password based<br>JTAGLOCK which user can<br>unlock if needed.                                                 | NO                                                               |

| SECURE BOOT                          | This BOOTMODE authenticate the user code before executing it. | YES                                                                                                                 | NO                                                               |

| Secure MSG RAM                       | One MSG RAM block can be allocated to<br>Zone1 or Zone2       | YES                                                                                                                 | NO                                                               |

| CLA Security                         |                                                               | CLA is like CPU and CLA registers are secure when executing secure code.                                            | CLA can be made secure by allocating it to Zone1 or Zone2        |

In addition, the address mapping for different security configurations in CPU1 USER OTP on F2838x has changed. You have to make the appropriate changes to code while importing it from F2837x.

#### 3.2.5 ROM Code and Peripheral Booting

Both F2837x and F2838x have a boot-ROM that initializes the device upon a reset and then boots to the application based on the boot-mode settings. Many enhancements and new features have been added to the F2838x boot-ROM. However, the default options have been retained between the two devices so that migration between the devices has minimal impact from a device-boot perspective.

Table 10 provides the list of items available in different section of ROM of the F2838x devices.

| Table | 10. | F2838x | ROM | contents |

|-------|-----|--------|-----|----------|

|-------|-----|--------|-----|----------|

| ROM         | CPU1                                                                                                             | CPU2                                                                                              | СМ                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| UNSECURE    | <ul> <li>Bootloaders</li> <li>IQmath</li> <li>FPU32/FPU64 Math and FFT<br/>Tables</li> <li>AES Tables</li> </ul> | <ul> <li>IQmath</li> <li>FPU32/FPU64 Math and FFT Tables</li> <li>AES Tables</li> </ul>           |                                                                                                 |

| SECURE      | <ul><li>Secure Copy Code</li><li>Secure CRC</li><li>Secure boot to flash</li></ul>                               | <ul> <li>Secure Copy Code</li> <li>Secure CRC</li> <li>Secure boot to flash</li> <li>•</li> </ul> | <ul> <li>Secure Copy Code</li> <li>Secure CRC</li> <li>Secure boot to flash</li> <li></li></ul> |

| CLA DATAROM | Math and FFT Tables                                                                                              | Math and FFT Tables                                                                               | NA                                                                                              |

Table 11 provides a quick comparison of the BOOTMODE option on F2837x vs F2838x.

#### Table 11. Boot-ROM Comparison

| BOOT Feature                               | F2838x                                                                                          | F2837x                                                                                      |

|--------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Default BOOT Pins                          | GPIO72 and GPIO84                                                                               | GPIO72 and GPIO84                                                                           |

| Number of BOOTMODE pins                    | Can be customized to use 0 to 3 boot mode select<br>GPIOs (default 2 BOOTMODE pins)             | Requires 2 boot mode select GPIOs                                                           |

| Zero BOOTMODE Pin option                   | YES                                                                                             | NO                                                                                          |

| Custom BOOTMODE                            | Up to 8 custom boot mode options can be set in OTP                                              | 1 custom boot mode option can be set in OTP                                                 |

| Flash entry point                          | 4 flash entry addresses                                                                         | 1 flash entry address                                                                       |

| Reset                                      | CPU2 and CM reset are not released to boot until<br>done so by CPU1 application via IPC         | CPU2 is released out of reset to boot<br>during CPU1 boot                                   |

| BOOT Support on CPU2 (and CM)              | Only CPU1 contains bootloaders in ROM                                                           | YES, CPU1 and CPU2 both contain bootloader in ROM                                           |

| BOOTMODE setting via USER<br>OTP           | YES, Z1 and Z2 used for boot OTP config, where Z2<br>has priority (Z2 is checked before Z1)     | YES, Z1 and Z2 used for boot OTP<br>config, where Z1 has priority (Z1 checked<br>before Z2) |

| Wait BOOT                                  | <ul><li>Wait BOOT is replaced with CAN BOOT</li><li>SCI BOOT can be used as Wait BOOT</li></ul> | YES, dedicated Wait BOOT mode option.                                                       |

| Full IPC library in boot-ROM               | NO                                                                                              | YES                                                                                         |

| RAM Initialization (Clear all RAMs to 0x0) | RAM initialization occurs on POR                                                                | RAM initialization occurs on POR and XRS                                                    |

| MPOST Support                              | YES                                                                                             | NO                                                                                          |

| SECURE BOOT                                | YES, all three subsystem (CPU1/CPU2 and CM)<br>supports SECURE BOOT                             | NO                                                                                          |

For more details about ROM Code and Peripheral Booting, see the TMS320F2838x Microcontrollers Technical Reference Manual.

#### 3.2.6 External Memory Interface (EMIF)

External Memory Interface (EMIF) module on F2838x and F2837x are identical. The only change on F2838x is the addition of optional re-mapping (dual mapping) of the SDRAM (CS0) space for EMIF1 in the lower 22 bits address range of memory. Default mapping of the SDRAM space of EMIF1 is the same as on F2837x, which is at address 0x8000 0000. This address is beyond the 22-bit address space. Therefore, execution as well as direct addressing is not allowed. You can re-map this to address 0x0020 0000 by writing TYPE bit-field in MEMTYPE register to "01". Also on F2838x, the EMIF\_ERR (or EMIF\_ERROR) interrupt is combined with other system interrupts on SYS\_ERR.

#### 3.2.7 Communication Modules

The communication module changes between F2837x and F2838x only affect the number of peripherals or accessability from the CM subsystem, which was specifically added on F2838x for communication. Module functionality is maintained for both devices. Table 1 shows the number of instance of each communication module on F2838x and F2837x that should be considered when migrating applications between F2837x and F2838x.

#### 3.2.8 Control Modules

There are changes in the control modules between F2837x and F2838x. Most of the control modules on F2838x are of new "Type" compared to F2837x. Also, the number of instance (or channels) have been increased on the F2838x devices. Table 1 shows the module instance differences and module Type differences that should be considered when migrating applications between F2837x and F2838x.

#### 3.2.8.1 Enhanced Pulse Width Modulator (ePWM) and ePWM Sync Scheme

The ePWM Module Type on the F2838x and F2837x devices is the same, which means that the feature set of the ePWM module is the same on both the devices, but the number ePWM channels has been increased and a new synch scheme has been implemented on the F2838x devices.

Table 12 provide the list of changes associated with the ePWM module between the F2837x and F2838x devices.

| Feature                                                              | F2838x                                                  | F2837x                                               |

|----------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|

| EPWM Type                                                            | Туре 4                                                  | Туре 4                                               |

| Number of EPWM Channels                                              | 32                                                      | 24                                                   |

| Number of EPWM channel<br>with High-resolution capability<br>(HRPWM) | 16                                                      | 16                                                   |

| MAX PWM INPUT CLK Frq                                                | 200 MHz                                                 | 100 MHz                                              |

| HRPWM Clocking                                                       | HRPWM is clocked with their respective EPWM input clock | All the HRPWM is always clocked by EPWM1 input clock |

| SYNC Scheme                                                          | Generic Any-To-Any Scheme                               | Daisy Chain                                          |

| Configuration register for<br>SYNC Select                            | EPWMSYNCINSEL                                           | SYNCSELECT                                           |

#### Table 12. ePWM Feature Comparison

In the new SYNC scheme, any ePWM SYNCOUT or ECAP can be selected as SYNC input for any ePWM module. There are no restrictions like those on F2837x. The new SYNC scheme breaks the code compatibility with F2837x, therefore, you need to modify the respective code while migrating between the F2837x and F2838x devices.

For more details on the ePWM module and new SYNC scheme, see the TMS320F2838x Microcontrollers Technical Reference Manual.

#### 3.2.8.2 Enhanced Capture (eCAP)

The eCAP module on F2838x is "Type 2", which has some additional features compared to those on the F2837x devices ("Type 0"). F2838x also have HRCAP features available on some of eCAP input. Sync scheme for eCAP also has been changed on F2838x (same as ePWM Sync)

Table 13 provide the list of changes associated with eCAP module between F2837x and F2838x.

| Feature                                                     | F2838x                                                                                                                                                      | F2837x                                           |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Туре                                                        | Туре 2                                                                                                                                                      | Туре 0                                           |

| Number of eCAP Inputs                                       | 7                                                                                                                                                           | 6                                                |

| Inputs channels with high-<br>resolution capability (HRCAP) | Yes (2, eCAP6 and eCAP7)                                                                                                                                    | No                                               |

| Event filter reset bit                                      | Yes (ECCTL2.CTRFILTRESET)                                                                                                                                   | No                                               |

| Modulo counter (4 bit sequencer) status bits                | Yes (ECCTL2.MODCNTRSTS)                                                                                                                                     | No                                               |

| DMA Event generation                                        | Yes (ECCTL2.DMAEVTSEL)                                                                                                                                      | No                                               |

| EALLOW protection for<br>registers                          | Yes                                                                                                                                                         | No                                               |

| Input select for eCAP                                       | Input for each eCAP module can be selected out<br>of 128 input source including 16 outputs of INPUT<br>XBAR. Input selection is done by<br>ECCCTLx.INPUTSEL | Fixed input from INPUT XBAR for each eCAP module |

| SYNC Scheme                                                 | Generic Any-To-Any Scheme                                                                                                                                   | Daisy Chain                                      |

| Configuration register for<br>SYNC Select                   | ECAPSYNCINSELECT                                                                                                                                            | SYNCSELECT                                       |

#### Table 13. eCAP Feature Comparison

Even though there are some enhancements to the existing feature of the eCAP module, like different input selection logic and EALLOW protection for configuration register, care has to be taken to avoid breaking the compatibility with F2837x code.

The Following implementation has been done to avoid this:

- Default value of ECCTLx.INPUTSELECT is 0x7F (127) and that selects the same input source as on F2837x.

- ECAPTYPE.TYPE configuration bit is added to enable EALLOW protection for eCAP registers. By default, EALLOW protection is not enabled. You can set ECAPTYPE.TYPE = 1 to enable EALLOW protection.

The new SYNC scheme breaks the code compatibility with F2837x. Therefore, you need to modify the respective code while migrating between the F2837x and F2838x devices. For more details on the eCAP module and new SYNC scheme, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

## 3.2.8.3 Enhanced Quadrature Encoder Pulse (eQEP)

The eCAP module on F2838x is "Type 2. This has some additional features compared to F2837x, which is "Type 0".

Below is the list of new feature and enhancement in eQEP module F2838x:

- A new function block Quadrature Mode Adapter (QMA) has been added, which modifies the QEPA and QEPB signals (does not resemble the traditional quadrature phase shifted signals) such that the modified signals resemble "directional count mode" signals, hence, the directional count mode of eQEP can be used. By default, QMA logic is bypassed and the EQEPA and EQEPB inputs from the pins go directly into the eQEP module. You can enable the QMA feature by setting the QMACTRL[MODE] register bit to 1.

- Hook-up the enable latching position count on ADCSOCA and ADCSOCB signal.

- Addition of the QEPSRCSEL register to configure the source selection for QEPA/QEPB/QEPI and QEPS to support SinCos transducers.

By default on reset, all of the new features of the eQEP module on the F2838x devices are disabled to make F2837x code compatible. For more details on the eQEP module, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

#### 3.2.8.4 Sigma Delta Filter Module (SDFM)

The SDFM module on F2838x has some enhancements, but Mode1/Mode2 and Mode3 are no longer supported.

Table 14 provides the list of changes associated with SDFM module between F2837x and F2838x.

| Feature                             | F2838x                                                                                                                                                  | F2837x                                                                                                       |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| SDFM pin configuration              | ASYNC Option Only                                                                                                                                       | ASYNC Option<br>QUAL Option (3-sample qual)                                                                  |

| SDFM Input qualification option     | Yes, SDCLK and SDDATA can be synchronized                                                                                                               | No                                                                                                           |

| Mode Supported                      | Mode 0                                                                                                                                                  | Mode 0<br>Mode1<br>Mode 2 (Not recommended for new design)<br>Mode 3                                         |

| Single clock source for all filters | SDCLK1 (SD-C1) can be used to clock all 4<br>filters in SDFM by configuring<br>SDCTLPARMx.SDCLKSEL register bit.                                        | Not supported                                                                                                |

| SDSYNC event source                 | Any ePWM can be selected to drive SDSYNC<br>event by configuring SDSYNCx.SDSYNCSEL<br>register bit.                                                     | Only ePWM11 and ePWM12 can drive<br>SDSYNC event                                                             |

| Comparator Filter                   | Comparator Filter outout is memory mapped.                                                                                                              | Comparator Filter output is not memory<br>mapped                                                             |

| Data Filter                         | SDFM saturation issue is fixed                                                                                                                          | SDFM saturation issue (Errata item)                                                                          |

| FIFO Support                        | Supports 16 x 32 bit FIFO                                                                                                                               | Not supported                                                                                                |

| Interrupt                           | Each SDFM has 5 interrupt lines -<br>• Each SDFM DATA Ready event has it's<br>own interrupt line<br>• SDFM Error events have separate interrupt<br>line | Each SDFM has 1 interrupt line<br>Both Data Ready event and SDFM error events<br>share single interrupt line |

#### Table 14. SDFM Feature Comparison

As listed in Table 14, there are many changes in the SDFM module on the F2838x devices. It is recommended to review the code from the F237x devices and make appropriate changes before using it on the F2838x devices. For more details on the SDFM module, see the *TMS320F2838x Microcontrollers Technical Reference Manual*.

#### 3.2.9 Analog Modules

This section outlines the analog differences between the F2838x and F2837x devices. Most of the Analog modules on F2838x are exactly same as on F2837x. There are some minor enhancements in digital logic of some of the modules that are listed in Table 15.

| Module | Feature                                        | F2838x                                                                                                                                                                                                   | F2837x                                                                      |

|--------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|