# TMS320VC5507/5509 DSP Universal Serial Bus (USB) Module Reference Guide

Literature Number: SPRU596A June 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

# Preface

# **Read This First**

#### About This Manual

This manual describes the features and operation of the Universal Serial Bus (USB) module that is available on the TMS320VC5507, TMS320VC5509, and TMS320VC5509A digital signal processors (DSPs) in the TMS320C55 $x^{TM}$  (C55 $x^{TM}$ ) DSP generation.

#### Notational Conventions

This document uses the following conventions:

□ In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers often are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form: 0100b

- ☐ If a signal or pin is active low, it has an overbar. For example, the RESET signal is active low.

- Register bits are sometimes referenced with the following notations:

| Notation      | Description                  | Example                                                         |

|---------------|------------------------------|-----------------------------------------------------------------|

| Register(n–m) | Bits n through m of Register | R(15–0) represents the 16 least significant bits of register R. |

| E[n:m]        | Range of bits En through Em  | E[7:0] represents E7, E6, E5,<br>E4, E3, E2, E1, and E0.        |

The following terms are used to name portions of data:

| Term   | Description            | Example                                |

|--------|------------------------|----------------------------------------|

| LSB    | Least significant bit  | In AC0(15–0), bit 0 is the LSB.        |

| MSB    | Most significant bit   | In AC0(15–0), bit15 is the MSB.        |

| LSByte | Least significant byte | In AC0(15–0), bits 7–0 are the LSByte. |

| MSByte | Most significant byte  | In AC0(15–0), bits15–8 are the MSByte. |

#### **Related Documentation From Texas Instruments**

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **TMS320VC5507 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS244) describes the features of the TMS320VC5507 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS163) describes the features of the TMS320VC5509 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509A Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS205) describes the features of the TMS320VC5509A fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320C55x Technical Overview** (literature number SPRU393) introduces the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- **TMS320C55x DSP Peripherals Overview Reference Guide** (literature number SPRU317) introduces the peripherals, interfaces, and related hardware that are available on TMS320C55x DSPs.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- **TMS320C55x DSP Mnemonic Instruction Set Reference Guide** (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- **TMS320C55x DSP Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

### Trademarks

TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

This page is intentionally left blank.

Universal Serial Bus (USB) Module

# Contents

| 1 | USB    | Concep   | ts Overview                                                                      | 15 |

|---|--------|----------|----------------------------------------------------------------------------------|----|

|   | 1.1    | Termin   | ology                                                                            | 15 |

|   | 1.2    | Data To  | oggle Mechanism                                                                  | 17 |

| 2 | Introd | duction  | to the USB Module                                                                | 18 |

|   | 2.1    | Block D  | Diagram of the USB Module                                                        | 18 |

|   | 2.2    | Conne    | ction of the USB Module to the Bus                                               | 22 |

|   | 2.3    | Transfe  | er of Data Between the USB Host and the DSP Memory                               | 23 |

|   | 2.4    | Clock (  | Generation for the USB Module                                                    | 23 |

|   |        | 2.4.1    | USB Clock Generator on TMS320VC5509 Devices Versus<br>TMS320VC5507/5509A Devices | 24 |

|   |        | 2.4.2    | DPLL Operation                                                                   | 26 |

|   |        | 2.4.3    | APLL Operation (TMS320VC5507/5509A Devices Only)                                 | 30 |

|   |        | 2.4.4    | Idle Mode Considerations                                                         | 33 |

| 3 | USB    | Buffer N | lanager (UBM)                                                                    | 34 |

| 4 | USB    | DMA Co   | ntroller                                                                         | 37 |

|   | 4.1    | Advant   | age of Using the USB DMA Controller                                              | 37 |

|   | 4.2    | Things   | To Consider Before Using the USB DMA Controller                                  | 37 |

|   | 4.3    | Interac  | tion Between the CPU and the USB DMA Controller                                  | 38 |

|   | 4.4    | Automa   | atic Alternating Accesses of the X and Y Buffers                                 | 42 |

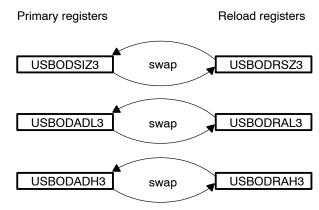

|   | 4.5    | DMA R    | eload Operation (Automatic Register Swapping)                                    | 42 |

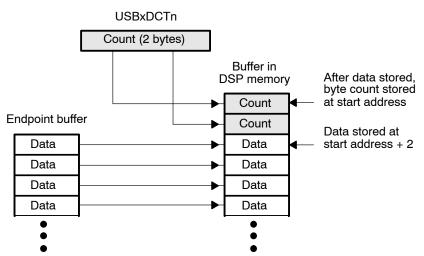

|   | 4.6    | Transfe  | er Count Saved to DSP Memory for an OUT Transfer                                 | 43 |

|   | 4.7    | Configu  | uring the USB DMA Controller                                                     | 44 |

|   |        | 4.7.1    | Set the Transfer Size                                                            | 44 |

|   |        | 4.7.2    | Set the DSP Memory Address                                                       | 45 |

|   |        | 4.7.3    | Enable/Disable a DMA Reload Operation                                            |    |

|   |        | 4.7.4    | Enable/Disable DMA Interrupt Requests                                            |    |

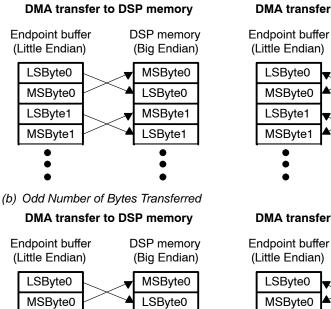

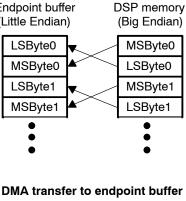

|   |        | 4.7.5    | Select the Endianness (Byte Orientation) of Data                                 | 46 |

|   |        | 4.7.6    | Enable/Disable Concatenation                                                     |    |

|   |        | 4.7.7    | Select Whether a Short Packet is Required to End a USB Transfer                  | 48 |

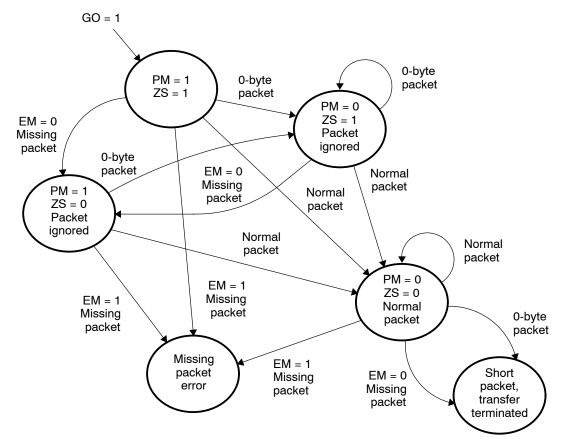

|   |        | 4.7.8    | Select Whether a Missing Packet is an Error During Isochronous<br>Transfers      | 48 |

### Contents

|   | 4.8                                | 4.8.1<br>4.8.2<br>4.8.3<br>4.8.4<br>4.8.5                                       | ring DMA Transfers<br>Checking the Transfer Count<br>Determining Whether a DMA Transfer is in Progress or is Done<br>Determining Whether a DMA Reload Operation is in Progress or is Done<br>Checking for an Overflow or Underflow Condition<br>Watching for a Missing Packet During an Isochronous Transfer<br>MA State Tables and State Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 48<br>. 49<br>. 49<br>. 50<br>. 50                                 |

|---|------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

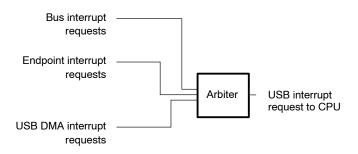

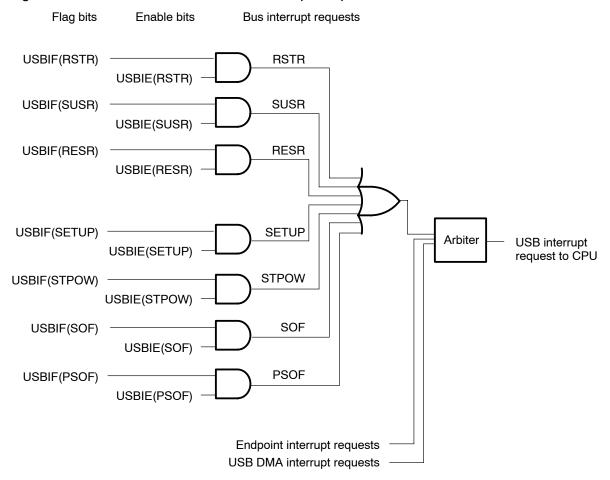

| 5 | <b>Interr</b><br>5.1<br>5.2<br>5.3 | Bus Inte<br>Endpoi                                                              | vity in the USB Module<br>errupt Requests<br>nt Interrupt Requests<br>MA Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 66<br>. 68                                                         |

| 6 | Powe<br>6.1<br>6.2<br>6.3<br>6.4   | Putting<br>USB M<br>USB M                                                       | ation, and Reset Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 72<br>. 72<br>. 72                                                 |

| 7 | USB 1<br>7.1<br>7.2                | High-Le<br>DMA R<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6          | Registersevel Summary of USB Module RegistersegistersUSB DMA Control Register (USBxDCTLn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Address Registers (USBxDADHn and USBxDADLn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Size Register (USBxDSIZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Size Register (USBxDCTn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Count Register (USBxDCTn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Reload-Address Registers (USBxDRAHn and USBxDRALn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ USB DMA Reload-Size Register (USBxDRSZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ DSB DMA Reload-Size Register (USBxDRSZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ DSB DMA Reload-Size Register (USBxDRSZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ DSB DMA Reload-Size Register (USBxDRSZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ DSB DMA Reload-Size Register (USBxDRSZn) $(x = I \text{ or } 0; n = 1, 2, 3, 4, 5, 6, \text{ or } 7)$ DSB DMA Reload-Size Register for INn (USBICNFn) | . 74<br>. 78<br>. 79<br>. 83<br>. 84<br>. 85<br>. 85<br>. 87<br>. 87 |

|   |                                    | <ul><li>7.3.2</li><li>7.3.3</li><li>7.3.4</li><li>7.3.5</li><li>7.3.6</li></ul> | $\begin{array}{l} (n=1,2,3,4,5,6, \mbox{ or } 7) \\ \hline \\ \mbox{Endpoint Configuration Register for OUTn (USBOCNFn)} \\ (n=1,2,3,4,5,6, \mbox{ or } 7) \\ \hline \\ \mbox{Endpoint Buffer Base Address Registers for INn or OUTn} \\ (USBxBAXn, USBxBAYn) (x = I \mbox{ or } 0; \mbox{ n = 1}, 2, 3, 4, 5, 6, \mbox{ or } 7) \\ \hline \\ \mbox{Endpoint Buffer Count Registers for INn or OUTn (USBxCTXn, USBxCTYn)} \\ (x = I \mbox{ or } 0; \mbox{ n = 1}, 2, 3, 4, 5, 6, \mbox{ or } 7) \\ \hline \\ \mbox{Endpoint X-/Y-Buffer Size Register for INn or OUTn (USBxSIZn)} \\ (x = I \mbox{ or } 0; \mbox{ n = 1}, 2, 3, 4, 5, 6, \mbox{ or } 7) \\ \hline \\ \mbox{Endpoint Buffer Size and Count Extension Registers} \\ (USBISIZHn, USBOCTXHn, \mbox{ and USBOCTYHn}) (n = 1, 2, 3, 4, 5, 6, \mbox{ or } 7) \\ \hline \\  \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                          | . 92<br>. 94<br>. 96<br>100                                          |

Universal Serial Bus (USB) Module

| 7.4      | Definiti | on Registers for Endpoints IN0 and OUT0                                    | 103 |

|----------|----------|----------------------------------------------------------------------------|-----|

|          | 7.4.1    | Endpoint Configuration Register for IN0 or OUT0 (USBxCNF0)<br>(x = I or O) | 103 |

|          | 7.4.2    | Endpoint Buffer Count Register for IN0 or OUT0 (USBxCT0)<br>(x = I or O)   |     |

| 7.5      | Interru  | t Registers                                                                |     |

|          | 7.5.1    | Interrupt Source Register (USBINTSRC)                                      |     |

|          | 7.5.2    | Endpoint Interrupt Flag Register (USBxÉPIF)<br>(x = I or O)                |     |

|          | 7.5.3    | Endpoint Interrupt Enable Register (USBxEPIE)<br>(x = I or O)              |     |

|          | 7.5.4    | DMA GO Interrupt Flag Register (USBxDGIF)<br>(x = I or O)                  |     |

|          | 7.5.5    | DMA RLD Interrupt Flag Register (USBxDRIF)<br>(x = I or O)                 |     |

|          | 7.5.6    | DMA Interrupt Enable Register (USBxDIE)<br>(X = I or O)                    |     |

| 7.6      | Genera   | al Control and Status Registers                                            | 115 |

|          | 7.6.1    | Global Control Register (USBGCTL)                                          |     |

|          | 7.6.2    | Frame Number Registers (USBFNUML and USBFNUMH)                             |     |

|          | 7.6.3    | PSOF Interrupt Timer Counter (USBPSOFTMR)                                  | 117 |

|          | 7.6.4    | USB Control Register (USBCTL)                                              |     |

|          | 7.6.5    | USB Interrupt Flag Register (USBIF)                                        | 120 |

|          | 7.6.6    | USB Interrupt Enable Register (USBIE)                                      |     |

|          | 7.6.7    | USB Device Address Register (USBADDR)                                      |     |

|          | 7.6.8    | USB Idle Control Register (USBIDLECTL)                                     |     |

| Revision | History  |                                                                            | 125 |

# Figures

| 1  | Conceptual Block Diagram of the USB Module 19                                       |

|----|-------------------------------------------------------------------------------------|

| 2  | Connection of the USB Module to the Bus (Full-Speed Connection)                     |

| 3  | Path for Data Transferred Between the Host and the DSP Memory                       |

| 4  | Clock Generation for the USB Module                                                 |

| 5  | USB PLL Selection Register (USBPLLSEL)                                              |

| 6  | USB Digital PLL Control Register (USBDPLL)                                          |

| 7  | USB Analog PLL Control Register (USBAPLL)                                           |

| 8  | Role of a NAK Bit in USB Activity at an OUT Endpoint                                |

| 9  | Role of a NAK Bit in USB Activity at an IN Endpoint                                 |

| 10 | Activity for DMA Transfers                                                          |

| 11 | Storage of Transfer Count for an OUT Transfer                                       |

| 12 | The Effect of END = 1 on USB DMA Transfers                                          |

| 13 | State Diagram: Missing Packet Response for Isochronous IN DMA Transfer              |

| 14 | State Diagram: Missing Packet Response for Isochronous OUT DMA Transfer             |

| 15 | Possible Sources of a USB Interrupt Request                                         |

| 16 | Enable Paths for the Bus Interrupt Requests                                         |

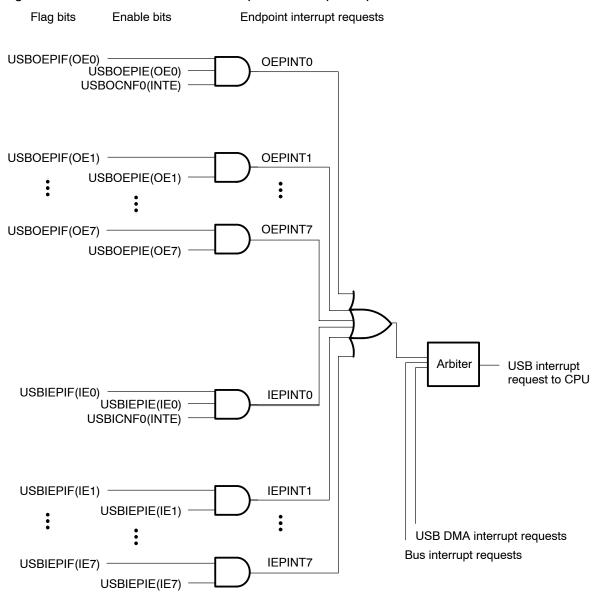

| 17 | Enable Paths for the Endpoint Interrupt Requests                                    |

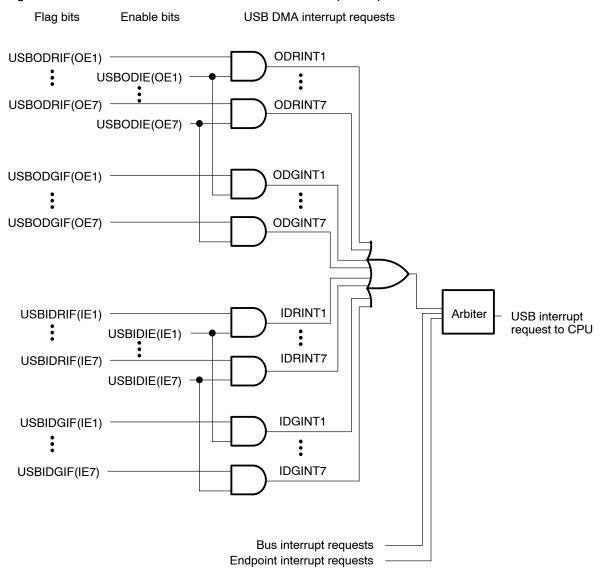

| 18 | Enable Paths for the USB DMA Interrupt Requests                                     |

| 19 | USB DMA Control Register (USBxDCTLn)                                                |

| 20 | USB DMA Address Registers (USBxDADLn and USBxDADHn)                                 |

| 21 | USB DMA Size Register (USBxDSIZn)                                                   |

| 22 | USB DMA Count Register (USBxDCTn)                                                   |

| 23 | USB DMA Reload-Address Registers (USBxDRALn and USBxDRAHn)                          |

| 24 | USB DMA Reload-Size Register (USBxDRSZn)                                            |

| 25 | Endpoint Definition Registers for INn and OUTn in the Isochronous Mode              |

| 26 | Endpoint Definition Registers for INn and OUTn in the Non-Isochronous Mode          |

| 27 | Endpoint Configuration Register for INn (USBICNFn)                                  |

| 28 | Endpoint Configuration Register for OUTn (USBOCNFn)                                 |

| 29 | Endpoint Buffer Base Address Registers for INn or OUTn<br>(USBxBAXn and USBxBAYn)   |

| 30 | Endpoint Buffer Count Registers for INn or OUTn<br>(USBxCTXn and USBxCTYn)          |

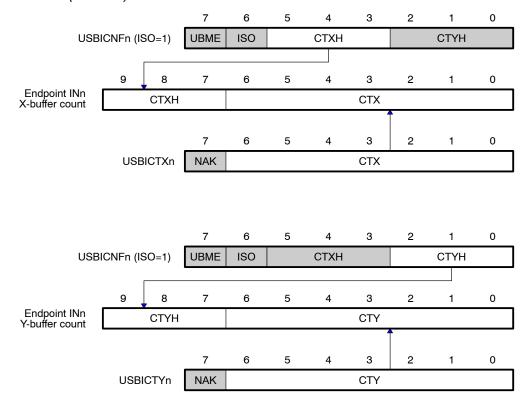

| 31 | Endpoint Extended Buffer Count Values for INn in the Isochronous<br>Mode (ISO = 1)  |

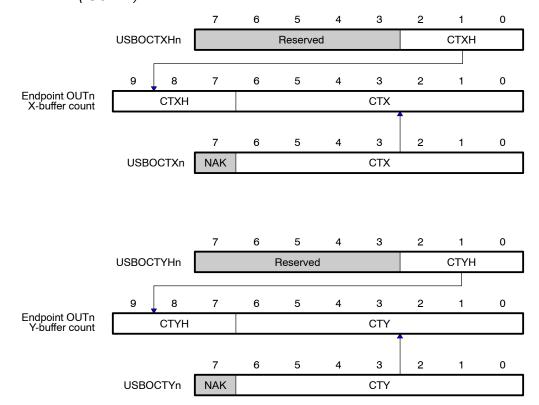

| 32 | Endpoint Extended Buffer Count Values for OUTn in the Isochronous<br>Mode (ISO = 1) |

| 33 | Endpoint X-/Y-Buffer Size Register for INn or OUTn (USBxSIZn)                       |

|    |                                                                                     |

10 Universal Serial Bus (USB) Module

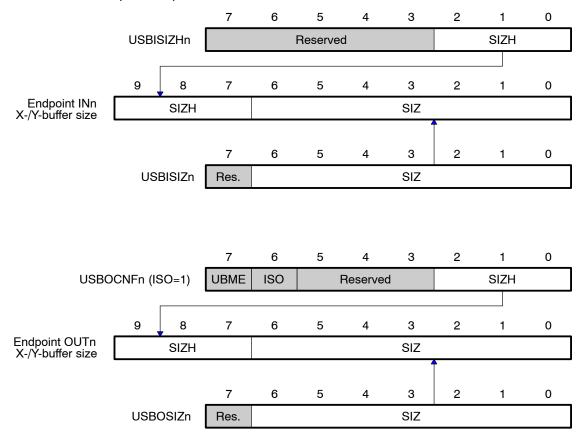

| 34 | Endpoint Extended Buffer Size Values for INn and OUTn in the Isochronous<br>Mode (ISO = 1)  | 101 |

|----|---------------------------------------------------------------------------------------------|-----|

| 35 | Endpoint Buffer Size and Count Extension Registers<br>(USBISIZHn, USBOCTXHn, and USBOCTYHn) | 102 |

| 36 | Endpoint Configuration Register for IN0 or OUT0 (USBxCNF0)                                  | 103 |

| 37 | Endpoint Buffer Count Register for IN0 (USBICT0)                                            | 105 |

| 38 | Endpoint Buffer Count Register for OUT0 (USBOCT0)                                           | 105 |

| 39 | Interrupt Source Register (USBINTSRC)                                                       | 107 |

| 40 | OUT Endpoint Interrupt Flag Register (USBOEPIF)                                             | 109 |

| 41 | IN Endpoint Interrupt Flag Register (USBIEPIF)                                              | 109 |

| 42 | OUT Endpoint Interrupt Enable Register (USBOEPIE)                                           | 110 |

| 43 | IN Endpoint Interrupt Enable Register (USBIEPIE)                                            | 111 |

| 44 | OUT Endpoint DMA GO Interrupt Flag Register (USBODGIF)                                      | 112 |

| 45 | IN Endpoint DMA GO Interrupt Flag Register (USBIDGIF)                                       | 112 |

| 46 | OUT Endpoint DMA RLD Interrupt Flag Register (USBODRIF)                                     | 113 |

| 47 | IN Endpoint DMA RLD Interrupt Flag Register (USBIDRIF)                                      | 113 |

| 48 | OUT Endpoint DMA Interrupt Enable Register (USBODIE)                                        | 114 |

| 49 | IN Endpoint DMA Interrupt Enable Register (USBIDIE)                                         | 115 |

| 50 | Global Control Register (USBGCTL)                                                           | 116 |

| 51 | Frame Number Registers (USBFNUML and USBFNUMH)                                              |     |

| 52 | PSOF Interrupt Timer Counter (USBPSOFTMR)                                                   | 118 |

| 53 | USB Control Register (USBCTL)                                                               | 118 |

| 54 | USB Interrupt Flag Register (USBIF)                                                         | 120 |

| 55 | USB Interrupt Enable Register (USBIE)                                                       | 121 |

| 56 | USB Device Address Register (USBADDR)                                                       | 123 |

| 57 | USB Idle Control Register (USBIDLECTL)                                                      | 123 |

11

# **Tables**

| 1  | Bits of the USB PLL Selection Register (USBPLLSEL)                                                   |

|----|------------------------------------------------------------------------------------------------------|

| 2  | Bits of the USB Digital PLL Control Register (USBDPLL)                                               |

| 3  | DPLL Options for the USB Module Clock Frequency                                                      |

| 4  | Bits of the USB Analog PLL Control Register (USBAPLL)                                                |

| 5  | APLL Options for the USB Module Clock Frequency                                                      |

| 6  | DMA Transfers                                                                                        |

| 7  | Primary USB DMA Size and Address Registers and the Corresponding<br>Reload Registers                 |

| 8  | State Table: Non-Isochronous IN DMA Transfer                                                         |

| 9  | State Table: Non-Isochronous OUT DMA Transfer                                                        |

| 10 | State Table: Isochronous IN DMA Transfer                                                             |

| 11 | State Table: Isochronous OUT DMA Transfer60                                                          |

| 12 | Descriptions of the Bus Interrupt Requests                                                           |

| 13 | High-Level Summary of the USB Module Registers                                                       |

| 14 | USB DMA Registers for Endpoint INn or OUTn (n = 1, 2, 3, 4, 5, 6, or 7)                              |

| 15 | Bits of a USB DMA Control Register (USBxDCTLn)                                                       |

| 16 | Bits of USB DMA Address Registers (USBxDADLn and USBxDADHn)                                          |

| 17 | Bits of a USB DMA Size Register (USBxDSIZn) 85                                                       |

| 18 | Bits of a USB DMA Count Register (USBxDCTn) 85                                                       |

| 19 | Bits of USB DMA Reload-Address Registers (USBxDRALn and USBxDRAHn)                                   |

| 20 | Bits of a USB DMA Reload-Size Register (USBxDRSZn)                                                   |

| 21 | Definition Registers For Endpoint INn or OUTn (n = 1, 2, 3, 4, 5, 6, or 7)                           |

| 22 | Bits of the Endpoint Configuration Register for INn (USBICNFn)                                       |

| 23 | Bits of the Endpoint Configuration Register for OUTn (USBOCNFn)                                      |

| 24 | Bits of the Endpoint Buffer Base Address Registers for INn or OUTn (USBxBAXn and USBxBAYn)           |

| 25 | Bits of the Endpoint Buffer Count Begisters for INn or OUTn                                          |

|    | (USBxCTXn and USBxCTYn)                                                                              |

| 26 | Bits of the Endpoint n X-/Y-Buffer Size Register for INn or OUTn (USBxSIZn) 100                      |

| 27 | Bits of the Endpoint Buffer Size and Count Extension Registers (USBISIZHn, USBOCTXHn, and USBOCTYHn) |

| 28 | Bits of the Endpoint Configuration Register for IN0 or OUT0 (USBxCNF0) 104                           |

| 29 | Bits of the Endpoint Buffer Count Register for IN0 or OUT0 (USBxCT0) 106                             |

| 30 | Bits of the Interrupt Source Register (USBINTSRC)                                                    |

| 31 | Interrupt Sources Matched to INTSRC Values                                                           |

| 32 | Bits of an Endpoint Interrupt Flag Register (USBxEPIF)                                               |

| 33 | Bits of an Endpoint Interrupt Enable Register (USBxEPIE)                                             |

12 Universal Serial Bus (USB) Module

| 34 | Bits of an Endpoint DMA GO Interrupt Flag Register (USBxDGIF)  | 112 |

|----|----------------------------------------------------------------|-----|

| 35 | Bits of an Endpoint DMA RLD Interrupt Flag Register (USBxDRIF) | 114 |

| 36 | Bits of an Endpoint DMA Interrupt Enable Register (USBxDIE)    | 115 |

| 37 | Bits of the Global Control Register (USBGCTL)                  | 116 |

| 38 | Bits of the Frame Number Registers (USBFNUML and USBFNUMH)     | 117 |

| 39 | Bits of the PSOF Interrupt Timer Counter (USBPSOFTMR)          | 118 |

| 40 | Bits of the USB Control Register (USBCTL)                      | 118 |

| 41 | Bits of the USB Interrupt Flag Register (USBIF)                | 120 |

| 42 | Bits of the USB Interrupt Enable Register (USBIE)              | 122 |

| 43 | Bits of the USB Device Address Register (USBADDR)              | 123 |

| 44 | Bits of the USB Idle Control Register (USBIDLECTL)             | 124 |

# Examples

| 1 | DMA Reload Operation for Endpoint OUT3     | 43 |

|---|--------------------------------------------|----|

|   | Loading the Endpoint Buffer Base Addresses |    |

With the USB module, you can use the DSP to create a full speed USB slave device that is compliant with Universal Serial Bus Specification Version 2.0. This chapter explains the architecture of the module and how to program the module.

# 1 USB Concepts Overview

This section explains USB concepts and terminology used in this chapter.

## 1.1 Terminology

In a USB system, the host is the master. The host initiates all data transfers between itself and attached USB devices. Therefore, the direction of a data transfer is described relative to the host:

| OUT transfer | A transfer of data from the host to a device: |

|--------------|-----------------------------------------------|

|              | $Host \rightarrow Device$                     |

| IN transfer  | A transfer of data from a device to the host: |

|              | $Host \gets Device$                           |

Each IN or OUT transfer can be one of the following types. The types of transfers on a USB are:

| Control transfer | The data transfer used by the host to send commands<br>to a USB device, including commands to enumerate<br>the device when it is first attached. Control transfers<br>include error checking.                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bulk transfer    | The data transfer used by the host to send or receive<br>a large amount of non-time-critical data. The data<br>transfer can be used when transfer time is not critical.<br>The host only allocates bus time for bulk transfers<br>when the time is not need by transfers of the other<br>types. Bulk transfers include error checking. A device<br>such as a printer is a good application for this type of<br>transfer. |

| Interrupt transfer      | The data transfer used when a USB device must send<br>or receive moderate amounts of data periodically with<br>minimum latency. Interrupt transfers include error<br>checking. Typical devices that use the interrupt<br>transfer are keyboards and joysticks.                                        |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lsochronous<br>transfer | The data transfer used by USB devices to send or<br>receive data in real time at a constant rate. The<br>isochronous transfers can handle more data than<br>interrupt transfers, but no error checking is performed.<br>A typical candidate for isochronous transfers is a<br>digital speaker system. |

#### Note:

From an implementation standpoint, bulk and interrupt transfers are treated the same way in the C55x USB module. The only difference is that the interrupt transfer is initiated periodically by the host, whereas a bulk transfer is initiated by the host whenever the bus is not used for other transfers.

For data transfer between a USB host and a USB device, the data passes through an endpoint in the device:

| Endpoint     | A designated storage location within a USB device.<br>Each endpoint in a device is uniquely identified by its<br>number and its direction (IN or OUT). |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT endpoint | An endpoint that holds data received from the USB host. To use data from the host, the USB device must read the data from an OUT endpoint.             |

|              | Each device must have an endpoint OUT0 to be used for control transfers.                                                                               |

| IN endpoint  | An endpoint that holds data to be sent to the USB host.<br>To send data to the host, the USB device must write<br>to an IN endpoint.                   |

|              | Each device must have an endpoint IN0 to be used for control transfers.                                                                                |

The overall characteristics of the USB device and the type of each endpoint must be reported to the host when the device is attached to the bus for the first time. This process is called **enumeration**.

The USB bandwidth can be shared by multiple USB devices. Data is transferred on the bus at regular (1-ms) intervals. Each of these intervals is called a **frame**, and the host divides up the frame for all the devices on the bus. As each new USB device is recognized and successfully enumerated by the host, it gains a portion of the frame. The size of the portion depends on factors such as the type of transfer (for example, isochronous versus bulk) and the amount of bandwidth that is not being used by other devices that are already on the bus.

# 1.2 Data Toggle Mechanism

For non-isochronous transfers, USB devices use a data toggle mechanism to detect transmission errors and to keep the transmitter and the receiver of USB data synchronized throughout a transfer. The data toggle mechanism requires two data packet types (DATA0 and DATA1) and two toggle bits (one in the transmitter and one in the receiver). Each packet transmitted is a DATA0 packet or a DATA1 packet, depending on the value of the transmitter's toggle bit (0 = DATA0; 1 = DATA1). If the receiver is synchronized, its toggle bit matches that of the transmitter, and the receiver expects the data type that was transmitted. Once the packet is successfully received, the receiver complements its toggle bit and sends an acknowledgement to the transmitter. When the acknowledgement arrives at the transmitter, the transmitter complements its toggle bit.

The first packet of a USB transfer is a DATA0 packet. Subsequent packets alternate in type (DATA1, DATA0, DATA1, and so on).

# 2 Introduction to the USB Module

The USB module described in this section is a USB 2.0-compliant, full-speed (12 Mbps) slave module.

The C55x USB module has 16 endpoints:

- Two control endpoints (for control transfers only): OUT0 and IN0.

- □ Fourteen general-purpose endpoints (for other types of transfers): OUT1–OUT7 and IN1–IN7. Each of these endpoints can support:

- Bulk, interrupt, and isochronous transfers.

- An optional double-buffer scheme for fast data throughput.

- A dedicated DMA channel. A DMA controller inside the USB module can pass data between the general-purpose endpoints and the DSP memory while the CPU performs other tasks. (The USB DMA controller cannot access the control endpoints.)

### 2.1 Block Diagram of the USB Module

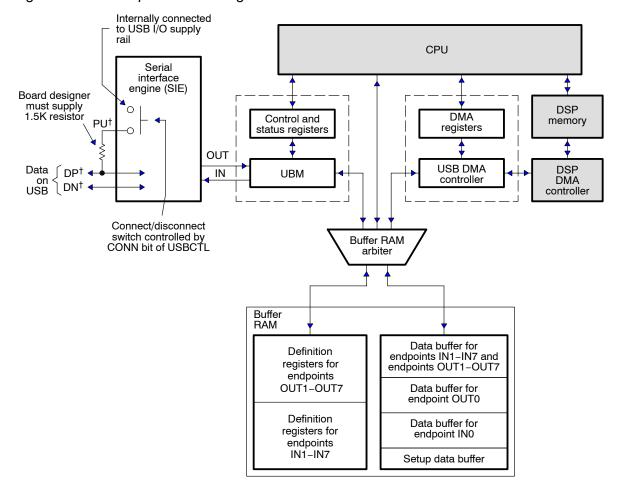

Figure 1 contains a conceptual block diagram of the USB module. The shaded blocks in the figure are outside the USB module. The list following the figure describes each of the main components of the module.

# Figure 1. Conceptual Block Diagram of the USB Module

<sup>†</sup> A more detailed figure of the pin connections is provided in section 2.2 (page 22).

19

Interface pins. The following table introduces the three pins shown in Figure 1. More detailed pin connections are shown in Figure 2 (page 22).

| Pin | Description                                                                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP  | Connect this pin to the USB connector terminal that carries the positive differential data.                                                                                                                |

| DN  | Connect this pin to the USB connector terminal that carries the negative differential data.                                                                                                                |

| PU  | Use this pin to connect a $1.5-\Omega$ pullup resistor to the DP line. A software-controlled switch connects the pullup resistor to the USB I/O supply rail internally.                                    |

|     | When the CPU sets the connect bit of USBCTL (CONN = 1), the switch closes and completes the pullup circuit, causing the USB host to detect the USB module on the bus and to start the enumeration process. |

|     | To disconnect the device from the USB system, clear the CONN bit. The switch will open and disconnect the pullup resistor.                                                                                 |

Serial interface engine (SIE). The SIE is the USB protocol handler. It parses the USB bit stream for data packets that are meant for the USB device. For an OUT transfer, the SIE converts the serial data to parallel data and passes them to the USB buffer manager. For an IN transfer, the SIE converts parallel data from the UBM to serial data, and transmits them over the USB.

The SIE also performs error-checking. For an OUT transfer, the SIE does the error checking and transfers only the good data to the UBM. For an IN transfer, the SIE generates the necessary error-checking information before sending the data on the bus.

USB buffer manager (UBM) and the control and status registers. The UBM controls data flow between the SIE and the buffer RAM. Most of the control registers are used to control the behavior of the UBM, and most of the status registers are modified by the UBM to notify the CPU when any event occurs.

- Buffer RAM. The buffer RAM contains registers that are mapped in the DSP I/O space. The buffer RAM consist of:

- Relocatable buffer space for each of the general-purpose endpoints (3.5K bytes). A general-purpose endpoint can have one data buffer (X buffer) or two data buffers (X buffer and Y buffer).

- A fixed-length (64-byte) data buffer for endpoint OUT0

- A fixed-length (64-byte) data buffer for endpoint IN0

- A fixed-length (8-byte) data buffer for a setup packet

- Definition registers. Each of the general-purpose endpoints has eight definition registers that determine the endpoint characteristics.

- USB DMA controller and the DMA registers. The USB DMA controller can transfer data between the DSP memory and the X and Y buffers of the general-purpose endpoints. Each of these endpoints has a dedicated DMA channel and a dedicated set of DMA registers for controlling and monitoring activity in that channel. The CPU can read from or write to each of these registers.

The USB DMA controller accesses memory via the auxiliary port of the DSP DMA controller. This auxiliary port is shared by the USB DMA controller and the host port interface (HPI). The USB DMA controller is given the higher priority.

Buffer RAM arbiter. The 8-bit-wide buffer RAM can be accessed by the UBM, by the USB DMA controller, and by the DSP CPU. The buffer RAM arbiter provides a fair access scheme by which these three requesters share the buffer RAM.

The USB DMA controller only accesses the X and Y buffers of the general-purpose endpoints. The controller uses 24-bit byte addresses to access DSP memory.

The CPU can access the buffer RAM, including the definition registers, via I/O space. The CPU writes 16-bit values to I/O space. However, when the CPU writes to the RAM, the high eight bits are ignored, and when the CPU reads from the RAM, the high eight bits are don't cares.

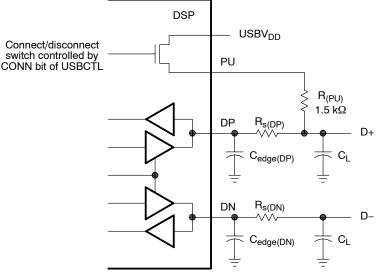

## 2.2 Connection of the USB Module to the Bus

Figure 2 shows the bus connections for the USB module.  $R_{s(DP)}$  and  $R_{s(DN)}$  are series resistors required to match the output impedance of the drivers for the differential data pins (DP and DN). Consult the device-specific data manual for the required values of  $R_{s(DP)}$  and  $R_{s(DN)}$ , as well as  $C_{edge(DP)}$ ,  $C_{edge(DN)}$ , and  $C_L$ . The 1.5 k $\Omega$  pullup resistor,  $R_{(PU)}$ , is a USB specification requirement for a full-speed device.

Setting the connect (CONN) bit of USBCTL connects the pullup (PU) pin to the power supply pin, USBV<sub>DD</sub>. As a result, the USB host detects the USB module on the bus and starts the enumeration process. Clearing the CONN bit disconnects the two pins, resulting in a device-removal condition on the bus.

Figure 2. Connection of the USB Module to the Bus (Full-Speed Connection)

$^{\dagger}$  Consult the device-specific data manual for the required values of R\_{s(DP)}, R\_{s(DN)}, C\_{edge(DP)}, C\_{edge(DP)}, and C\_L.

SPRU596A

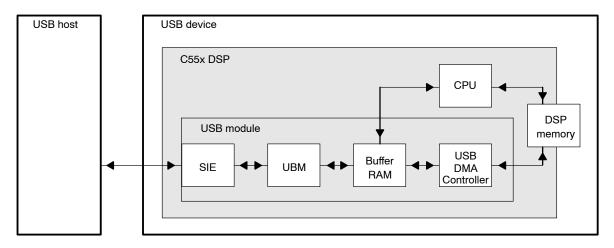

# 2.3 Transfer of Data Between the USB Host and the DSP Memory

Figure 3 shows, at a high-level, how data travels between the USB host and the DSP memory when a C55x DSP handles the USB activity for a USB device. During IN transfers, the SIE (serial interface engine) converts the parallel data from the UBM into a serial data stream for the host. During OUT transfers, the SIE converts the serial data from the host into parallel format for the UBM. The UBM either moves data from the SIE to the buffer RAM or from the buffer RAM to the SIE. Before the UBM transfers data to the SIE, the CPU or the USB DMA controller must put the data into the buffer RAM. When the CPU or the USB DMA controller is ready to move data to the DSP memory, it must wait for the UBM to move the data from the SIE to the buffer RAM.

## Figure 3. Path for Data Transferred Between the Host and the DSP Memory

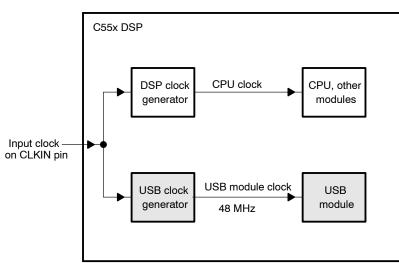

## 2.4 Clock Generation for the USB Module

As shown in Figure 4, the USB module has a dedicated clock generator that is independent of the DSP clock generator. Both generators receive their input from the CLKIN pin. The DSP clock generator supplies the CPU clock that is used by the CPU and most of the other modules inside the DSP. The USB clock generator supplies the clock needed to operate the USB module.

#### Note:

The USB module requires a 48-MHz clock. The clock on the CLKIN pin may vary, but the USB clock generator must be programmed to produce a 48-MHz clock.

Figure 4. Clock Generation for the USB Module

### 2.4.1 USB Clock Generator on TMS320VC5509 Devices Versus TMS320VC5507/5509A Devices

The USB clock generator on TMS320VC5509 devices includes only a digital phase-locked loop circuit (DPLL). On TMS320VC5507/5509A devices, the USB clock generator includes both a DPLL and an analog phase-locked loop circuit (APLL). The choice of DPLL or APLL is made with the USB PLL selection register (USBPLLSEL), which is shown in Figure 5 and described in Table 1. This register is at address 1E80h in the I/O space of a TMS320VC5507/5509A device.

Write to the PLLSEL bit to indicate which PLL circuit is to drive the USB module. Then poll the status bits, DPLLSTAT and APLLSTAT. When a stable clock signal is available from the selected PLL, the corresponding status bit is set and the other status bit is cleared.

At device power-up, the DPLL is selected by default. If software selects the APLL but the APLLSTAT bit remains 0, the APLL is not providing a stable clock signal and should be restarted. Until the APLL is ready, the DPLL is used.

| 15 |          |          |   |          |          | 8      |

|----|----------|----------|---|----------|----------|--------|

|    |          | Reserved |   |          |          |        |

|    |          | R-0      |   |          |          |        |

| 7  |          |          | 3 | 2        | 1        | 0      |

|    | Reserved |          |   | DPLLSTAT | APLLSTAT | PLLSEL |

|    | R–0      |          |   | R-1      | R–0      | R/W-0  |

# Figure 5. USB PLL Selection Register (USBPLLSEL)

**Legend:** R = Read; W = Write; -n = Value after reset

# Table 1. Bits of the USB PLL Selection Register (USBPLLSEL)

| Bit  | Field    | Value | Description                                          |

|------|----------|-------|------------------------------------------------------|

| 15–3 | Reserved |       | These read-only bits return 0s when read.            |

| 2    | DPLLSTAT |       | DPLL status bit                                      |

|      |          | 0     | The DPLL is not the clock source for USB module.     |

|      |          | 1     | The DPLL is the clock source for the USB module.     |

| 1    | APLLSTAT |       | APLL status bit                                      |

|      |          | 0     | The APLL is not the clock source for the USB module. |

|      |          | 1     | The APLL is the clock source for the USB module.     |

| 0    | PLLSEL   |       | PLL selection bits                                   |

|      |          | 0     | The DPLL is selected as the USB module clock source. |

|      |          | 1     | The APLL is selected as the USB module clock source. |

|      |          |       |                                                      |

25

### 2.4.2 DPLL Operation

TMS320VC5509 devices have a DPLL only. On TMS320VC5507/5509A devices, the DPLL is selected if PLLSEL = 0 in USBPLLSEL. The DPLL functions like the DSP clock generator. To find details about the DSP clock generator, see the *TMS320C55x DSP Peripherals Overview Reference Guide* (literature number SPRU317).

The DPLL has two modes: the lock mode and the bypass mode. In the lock mode, the input clock is multiplied and/or divided, and in the bypass mode, the input clock is divided only. At device power-up, the bypass mode is selected.

The lock mode or bypass mode can be selected with the PLLENABLE bit of the USB digital PLL control register (USBDPLL). This register, shown in Figure 6 and described in Table 2, contains all the bits for controlling the DPLL. USBDPLL has the same fields as the DSP clock mode register (CLKMD). USBDPLL is at address 1E00h in the I/O space of the DSP.

| 15       | 14     | 13    | 12                    | 11      |         |         |      |

|----------|--------|-------|-----------------------|---------|---------|---------|------|

| Reserved | IAI    | IOB   | Reserved <sup>‡</sup> | PLLMULT |         |         |      |

| R–0      | R/W-0  | R/W-1 | R/W-0                 | R/W-0   |         |         |      |

| 7        | 6      | 5     | 4                     | 3       | 2       | 1       | 0    |

| PLLMULT  | PLLDIV |       | PLLENABLE             | BY      | PASSDIV | BREAKLN | LOCK |

| R/W-0    | R/W-00 |       | R/W-0                 | F       | R/W–01  | R-1     | R–0  |

Figure 6. USB Digital PLL Control Register (USBDPLL)

**Legend:** R = Read; W = Write; -n = Value after reset <sup>‡</sup> Always write 0 to this reserved bit.

Table 2. Bits of the USB Digital PLL Control Register (USBDPLL)

| Bit | Field    | Value | Description                                                                                                                                                                     |

|-----|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Reserved |       | This read-only reserved bit returns 0 when read.                                                                                                                                |

| 14  | IAI      |       | Initialize after idle bit. IAI determines how the DPLL reacquires the phase lock after the DPLL exits its idle mode (when the CLKGEN idle domain is reactivated).               |

|     |          | 0     | The DPLL does not restart the phase-locking sequence. Instead the DPLL reacquires the lock using the same lock settings that were in use just before the idle mode was entered. |

|     |          | 1     | The DPLL restarts the phase-locking sequence. This option is recommended if the input clock has or may have changed while the clock generator was idle.                         |

| Bit  | Field     | Value   | Description                                                                                                                                                                                                                                                              |

|------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | IOB       |         | Initialize on break bit. IOB determines whether the DPLL initializes the phase-locking sequence whenever the phase lock is broken.                                                                                                                                       |

|      |           |         | If the DPLL indicates a break in the phase lock:                                                                                                                                                                                                                         |

|      |           | 0       | The DPLL is not interrupted. The DPLL stays in the lock mode, and continues to output the current clock signal.                                                                                                                                                          |

|      |           | 1       | The DPLL switches to its bypass mode and restarts the phase-locking sequence.                                                                                                                                                                                            |

| 12   | Reserved  | 0       | Always write 0 to this reserved bit.                                                                                                                                                                                                                                     |

| 11–7 | PLLMULT   | 2 to 31 | PLL multiply value. When PLLENABLE = 1 and the DPLL is locked, the input clock is multiplied by the unsigned integer in PLLMULT and is divided according to the value in the PLLDIV bits. The options are summarized in Table 3.                                         |

| 6–5  | PLLDIV    |         | PLL divide value. When PLLENABLE = 1 and the DPLL is locked,<br>the input clock is multiplied by the unsigned integer in PLLMULT and<br>is divided according to the value in the PLLDIV bits. The options are<br>summarized in Table 3.                                  |

|      |           | 00b     | No division/divide by 1<br>The input frequency is not divided.                                                                                                                                                                                                           |

|      |           | 01b     | Divide by 2<br>The input frequency is divided by 2.                                                                                                                                                                                                                      |

|      |           | 10b     | Divide by 3<br>The input frequency is divided by 3.                                                                                                                                                                                                                      |

|      |           | 11b     | Divide by 4<br>The input frequency is divided by 4.                                                                                                                                                                                                                      |

| 4    | PLLENABLE |         | PLL enable bit. Write to PLLENABLE to enable or disable phase locking. When PLLENABLE is set, the DPLL initiates the phase-locking sequence. When the DPLL acquires the phase lock, the frequency of the DPLL output clock is determined by the PLLMULT and PLLDIV bits. |

|      |           | 0       | Disable phase locking (enter the bypass mode).                                                                                                                                                                                                                           |

|      |           | 1       | Enable phase locking and, when the correct output clock signal is generated, enter the lock mode.                                                                                                                                                                        |

# Table 2. Bits of the USB Digital PLL Control Register (USBDPLL) (Continued)

| Bit | Field     | Value         | Description                                                                                                                                                        |  |

|-----|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3–2 | BYPASSDIV |               | Bypass-mode divide value. In the bypass mode, BYPASSDIV determines the frequency of the output clock signal. The options are summarized in Table 3.                |  |

|     |           | 00b or<br>01b | No division/divide by 1<br>The frequency of the output clock signal is the same as the<br>frequency of the input clock signal.                                     |  |

|     |           | 10b           | Divide by 2<br>The frequency of the output clock signal is 1/2 the frequency of the<br>input clock signal.                                                         |  |

|     |           | 11b           | Divide by 4<br>The frequency of the output clock signal is 1/4 the frequency of the<br>input clock signal.                                                         |  |

| 1   | BREAKLN   |               | Break-lock indicator. BREAKLN indicates whether the DPLL has<br>broken the phase lock. In addition, if you write to CLKMD,<br>BREAKLN is forced to 1.              |  |

|     |           | 0             | The DPLL has broken the phase lock.                                                                                                                                |  |

|     |           | 1             | The phase lock is restored, or a write to CLKMD has occurred.                                                                                                      |  |

| 0   | LOCK      |               | Lock-mode indicator. LOCK indicates whether the DPLL is in its lock mode.                                                                                          |  |

|     |           | 0             | The DPLL is in the bypass mode. The output clock signal has the frequency determined by the BYPASSDIV bits, or the DPLL is in the process of getting a phase lock. |  |

|     |           | 1             | The DPLL is in the lock mode. The DPLL has a phase lock, and the output clock has the frequency determined by the PLLMULT bits and the PLLDIV bits.                |  |

| Table 2. | Bits of the USB Digital PLL | Control Register (USBDPLL) (Continued) |

|----------|-----------------------------|----------------------------------------|

|          |                             |                                        |

| PLLENABLE | BYPASSDIV <sup>†</sup> | PLLDIV <sup>†</sup> | PLLMULT <sup>†</sup> | DPLL Option                   | USB Module<br>Clock Frequency <sup>‡</sup> |

|-----------|------------------------|---------------------|----------------------|-------------------------------|--------------------------------------------|

| 0         | 0 or 1                 | х                   | Х                    | Bypass mode;<br>divide by 1   | Input clock frequency $\times$ 1/1         |

| 0         | 2                      | х                   | Х                    | Bypass mode;<br>divide by 2   | Input clock frequency $\times$ 1/2         |

| 0         | 3                      | Х                   | Х                    | Bypass mode;<br>divide by 4   | Input clock frequency $\times$ 1/4         |

| 1         | Х                      | 0                   | K = 2 to 31          | Lock mode;<br>multiply by K   | Input clock frequency $\times$ K/1         |

| 1         | Х                      | 1                   | K = 2 to 31          | Lock mode;<br>multiply by K/2 | Input clock frequency $\times$ K/2         |

| 1         | Х                      | 2                   | K = 2 to 31          | Lock mode;<br>multiply by K/3 | Input clock frequency $\times$ K/3         |

| 1         | Х                      | 3                   | K = 2 to 31          | Lock mode;<br>multiply by K/4 | Input clock frequency $\times$ K/4         |

DPLL Options for the USB Module Clock Frequency Table 3.

$^\dagger$  X = don't care  $^\ddagger$  The USB clock frequency must be 48 MHz for proper operation of the USB module.

29

### 2.4.3 APLL Operation (TMS320VC5507/5509A Devices Only)

On TMS320VC5507/5509A devices, the APLL is selected if PLLSEL = 1 in USBPLLSEL. The APLL has two modes: the lock mode and the bypass mode. In the lock mode, the input clock is multiplied and/or divided, and in the bypass mode, the input clock is divided only. At device power-up, the bypass mode is selected.

To configure the APLL, use the USB analog PLL control register, USBAPLL (see Figure 7 and Table 4). This register is at address 1F00h in the I/O space of a TMS320VC5507/5509A device. The following paragraphs describe the functionality provided by the bits in USBAPLL.

The MODE bit selects either the lock mode or the bypass mode. In the lock mode, the APLL requires the use of an internal voltage-controlled oscillator (VCO). The VCO is turned on by either the MODE bit or the ON bit, and the VCO is turned off if both of these bits are 0.

The MULT field of USBAPLL selects a multiplication factor K. In the bypass mode, K determines how the input clock (CLKIN) is divided to produce the USB module clock. In the lock mode, K is used in conjunction with the DIV bit to determine the relative frequency of the USB module clock. Table 15 summarizes all the options. Remember that the USB module requires a frequency of 48 MHz.

The COUNT field is a down-counter used to track the APLL lock time. The APLL requires approximately 350  $\mu$ s to lock, and COUNT provides a means to track the lock time in terms of the input clock (CLKIN). As soon as the lock mode is turned on (that is, as soon as the MODE bit changes from 0 to 1), the phase-locking sequence begins and COUNT decremented by 1 every 16 CLKIN cycles. When COUNT reaches 0, the STAT bit is set. To make sure the countdown time matches the lock time, use the following equation when loading COUNT:

$$COUNT = \left(\frac{Lock \ time}{16 \ \times \ CLKIN \ period}\right) - 1$$

| 15    | 12 11 | 10    |       |      |

|-------|-------|-------|-------|------|

| MULT  | DIV   |       | COUNT |      |

| R/W-0 | R/W-0 |       | R/W-0 |      |

|       | 3     | 2     | 1     | 0    |

| COUNT |       | ON    | MODE  | STAT |

| R/W-0 |       | R/W-0 | R/W-0 | R-0  |

#### Figure 7. USB Analog PLL Control Register (USBAPLL)

**Legend:** R = Read; W = Write; -n = Value after reset <sup>†</sup> This reserved bit must be kept 0 for proper operation of the USB clock generator.

| Table 4. | Bits of the USB Analog | PLL Control Re | agister (USBAPLL) |

|----------|------------------------|----------------|-------------------|

|          |                        |                |                   |

| Bit   | Field | Value | Description                                                                                                             |

|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------|

| 15–12 | MULT  |       | PLL multiply value. MULT + 1 is the multiply factor K. Table 5 shows how this factor affects the operation of the APLL. |

|       |       | 0000b | K= 1                                                                                                                    |

|       |       | 0001b | K = 2                                                                                                                   |

|       |       | 0010b | K = 3                                                                                                                   |

|       |       | 0011b | K = 4                                                                                                                   |

|       |       | 0100b | K = 5                                                                                                                   |

|       |       | 0101b | K = 6                                                                                                                   |

|       |       | 0110b | K = 7                                                                                                                   |

|       |       | 0111b | K = 8                                                                                                                   |

|       |       | 1000b | K = 9                                                                                                                   |

|       |       | 1001b | K = 10                                                                                                                  |

|       |       | 1010b | K= 11                                                                                                                   |

|       |       | 1011b | K = 12                                                                                                                  |

|       |       | 1100b | K = 13                                                                                                                  |

|       |       | 1101b | K= 14                                                                                                                   |

|       |       | 1110b | K = 15                                                                                                                  |

|       |       | 1111b | K = 16                                                                                                                  |

31

| Bit  | Field | Value                            | Description                                                                                                                                                                                    |

|------|-------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | DIV   | 0 or 1                           | PLL divide value. Table 5 shows how this value affects the operation of the APLL in the lock mode. This value is a don't care in the bypass mode.                                              |

| 10–3 | COUNT | 0 to 255                         | PLL lock counter bits. COUNT offers the ability to track the APLL lock time, which is approximately $350 \ \mu$ s. Before switching to the lock mode, load COUNT using the following equation: |

|      |       |                                  | COUNT = [Lock time / (16 x CLKIN period)] -1                                                                                                                                                   |

|      |       |                                  | As soon as the lock mode is selected (that is, when the MODE bit<br>changes from 0 to 1), COUNT is decremented by 1 every<br>16 CLKIN cycles. When COUNT reaches 0, the STAT bit is set.       |

| 2    | ON    |                                  | PLL VCO on bit. This bit can be used to enable the internal voltage-control oscillator (VCO).                                                                                                  |

|      |       | 0                                | If the MODE bit is also 0, writing 0 to ON turns the VCO off.                                                                                                                                  |

|      |       | 1                                | Writing 1 to ON turns the VCO on if it is not already running due to the MODE bit.                                                                                                             |

| 1    | MODE  |                                  | Mode selection bit                                                                                                                                                                             |

|      |       | 0                                | Bypass mode. Writing 0 to MODE selects the bypass mode.                                                                                                                                        |

|      |       | 1                                | Lock mode. Writing 1 to MODE selects the lock mode and also turns the VCO on if it is not already running due to the ON bit.                                                                   |

| 0    | STAT  |                                  | PLL lock status bit. If COUNT has been loaded properly, STAT = 1 indicates that enough time has passed for the APLL to achieve a phase lock.                                                   |

|      |       | 0                                | COUNT has not been decremented to 0.                                                                                                                                                           |

|      | 1     | COUNT has been decremented to 0. |                                                                                                                                                                                                |

Table 4. Bits of the USB Analog PLL Control Register (USBAPLL) (Continued)

| MODE | DIV    | Κ <sup>†</sup> | APLL Option                    | USB Module Clock Frequency <sup>‡</sup> |

|------|--------|----------------|--------------------------------|-----------------------------------------|

| 0    | 0 or 1 | 1 to 15        | Bypass mode; divide by 2       | Input clock frequency $\times$ 1/2      |

| 0    | 0 or 1 | 16             | Bypass mode; divide by 4       | Input clock frequency $\times$ 1/4      |

| 1    | 0      | 1 to 15        | Lock mode; multiply by K       | Input clock frequency $\times$ K/1      |

| 1    | 0      | 16             | Lock mode; multiply by 1       | Input clock frequency $\times$ 1/1      |

| 1    | 1      | odd            | Lock mode; multiply by K/2     | Input clock frequency $\times$ K/2      |

| 1    | 1      | even           | Lock mode; multiply by (K–1)/4 | Input clock frequency $\times$ (K–1)/4  |

Table 5. APLL Options for the USB Module Clock Frequency

<sup>†</sup> K = MULT + 1

<sup>‡</sup> The USB clock frequency must be 48 MHz for proper operation of the USB module.

### 2.4.4 Idle Mode Considerations

Idling the USB module does not idle the USB clock generator. Doing this simply prevents the USB module clock signal from driving the USB module.

Both the DSP clock generator and the USB clock generator are part of the CLKGEN idle domain. If the IDLE instruction deactivates the CLKGEN domain, both clock generators stop running.

33

#### **USB Buffer Manager (UBM)** 3

When data is to be moved to or from the buffer RAM, the UBM accesses one of the following endpoint buffers in the buffer RAM:

| Buffers For Transfers<br>To DSP Memory | Buffers For Transfers<br>From DSP Memory |  |  |  |

|----------------------------------------|------------------------------------------|--|--|--|

|                                        | Control endpoint buffers                 |  |  |  |

| OUT0 buffer                            | IN0 buffer                               |  |  |  |

| General-purpose endpoint buffers       |                                          |  |  |  |

| OUT1 buffer (X or Y)                   | IN1 buffer (X or Y)                      |  |  |  |

| OUT2 buffer (X or Y)                   | IN2 buffer (X or Y)                      |  |  |  |

| OUT3 buffer (X or Y)                   | IN3 buffer (X or Y)                      |  |  |  |

| OUT4 buffer (X or Y)                   | IN4 buffer (X or Y)                      |  |  |  |

| OUT5 buffer (X or Y)                   | IN5 buffer (X or Y)                      |  |  |  |

| OUT6 buffer (X or Y)                   | IN6 buffer (X or Y)                      |  |  |  |

| OUT7 buffer (X or Y)                   | IN7 buffer (X or Y)                      |  |  |  |

Each general-purpose endpoint can be configured to have a single buffer (X) or a double buffer (two buffers, X and Y). This is controlled by the double buffer mode (DBUF) bit in USBxCNFn. If there are two buffers, the UBM keeps track of which buffer to use. If the endpoint is in the non-isochronous mode, the UBM uses the X buffer for a DATA0 packet and the Y buffer for a DATA1 packet.

Each of the endpoint buffers is associated with a programmable count register of the following format:

| 7   | 6 0        | ) |

|-----|------------|---|

| NAK | CT (bytes) |   |

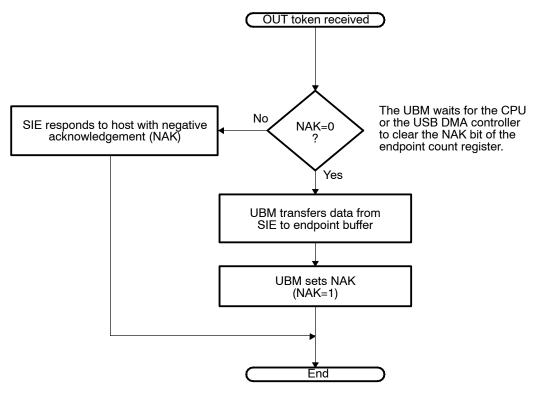

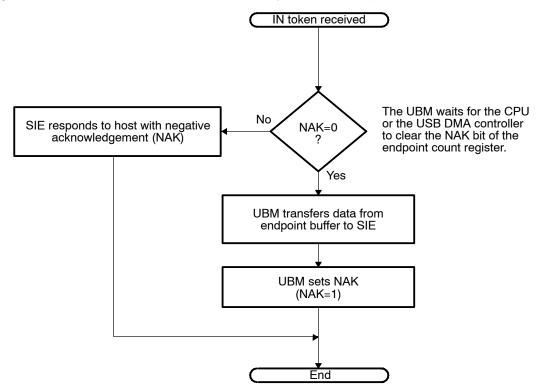

The NAK bit corresponds to the negative acknowledgement (NAK) of the USB protocol. If the NAK bit is set (NAK = 1), the SIE sends a NAK in response to a host request to that particular endpoint. The UBM does not access the buffer until NAK is cleared (NAK = 0).

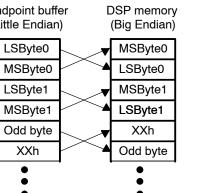

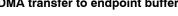

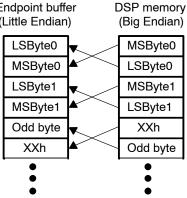

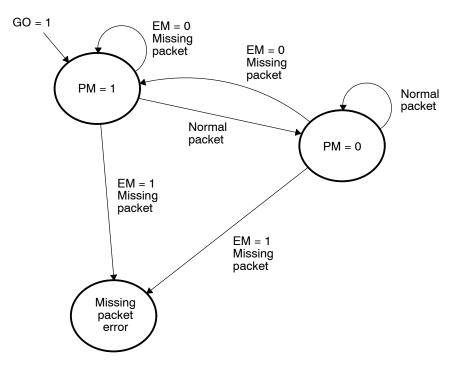

Universal Serial Bus (USB) Module