# TMS320DM644x DMSoC ATA Controller

# **User's Guide**

Literature Number: SPRUE21 December 2005

# Contents

| Pref | face  |                                                                    | 5   |

|------|-------|--------------------------------------------------------------------|-----|

| 1    | Intro | duction                                                            | 7   |

|      | 1.1   | Purpose of the Peripheral                                          | . 7 |

|      | 1.2   | Features                                                           | . 7 |

|      | 1.3   | Functional Block Diagram                                           | . 8 |

|      | 1.4   | Supported Use Cases                                                | . 8 |

|      | 1.5   | Industry Standard(s) Compliance                                    | . 9 |

|      | 1.6   | Terminology Used in This Document                                  | . 9 |

| 2    | Perip | oheral Architecture                                                | 9   |

|      | 2.1   | Clock Control                                                      | 9   |

|      | 2.2   | Signal Descriptions                                                | 10  |

|      | 2.3   | Pin Multiplexing                                                   | 12  |

|      | 2.4   | Protocol Description(s)                                            | 12  |

|      | 2.5   | General Architecture                                               | 12  |

|      | 2.6   | DMA and PIO Data Transaction Overview                              | 17  |

|      | 2.7   | Attached Device Reset Considerations                               | 21  |

|      | 2.8   | Initialization                                                     | 22  |

|      | 2.9   | Interrupt Support                                                  | 25  |

|      | 2.10  | EDMA Event Support                                                 | 28  |

|      | 2.11  | Power Management                                                   | 29  |

|      | 2.12  | Emulation Considerations                                           | 29  |

| 3    | Supp  | ported Use Cases                                                   | 29  |

|      | 3.1   | Interfacing to a Standard ATA/ATAPI Device                         | 29  |

|      | 3.2   | Interfacing to a Standard ATA/ATAPI Device Through a Level-Shifter | 30  |

|      | 3.3   | Interfacing to Compact Flash                                       | 31  |

| 4    | Regi  | sters                                                              | 33  |

|      | 4.1   | Primary IDE Channel DMA Control Register (BMICP)                   | 34  |

|      | 4.2   | Primary IDE Channel DMA Status Register (BMISP)                    | 35  |

|      | 4.3   | Primary IDE Channel DMA Descriptor Table Pointer Register (BMIDTP) | 36  |

|      | 4.4   | Primary IDE Channel Timing Register (IDETIMP)                      | 37  |

|      | 4.5   | IDE Controller Status Register (IDESTAT)                           | 38  |

|      | 4.6   | Ultra-DMA Control Register (UDMACTL)                               | 39  |

|      | 4.7   | Miscellaneous Control Register (MISCCTL)                           | 40  |

|      | 4.8   | Task File Register Strobe Timing Register (REGSTB)                 | 41  |

|      | 4.9   | Task File Register Recovery Timing Register (REGRCVR)              | 42  |

|      | 4.10  | Data Register Access PIO Strobe Timing Register (DATSTB)           | 43  |

|      | 4.11  | Data Register Access PIO Recovery Timing Register (DATRCVR)        | 44  |

|      | 4.12  | Multiword DMA Strobe Timing Register (DMASTB)                      | 45  |

|      | 4.13  | Multiword DMA Recovery Timing Register (DMARCVR)                   | 46  |

|      | 4.14  | Ultra-DMA Strobe Timing Register (UDMASTB)                         | 47  |

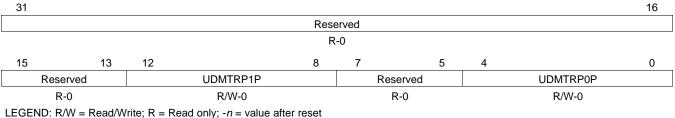

|      | 4.15  | Ultra-DMA Ready-to-Pause Timing Register (UDMATRP)                 | 48  |

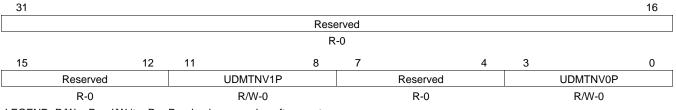

|      | 4.16  | Ultra-DMA Timing Envelope Register (UDMATENV)                      | 49  |

|      | 4.17  | Primary IO Ready Timer Configuration Register (IORDYTMP)           | 50  |

|      |       |                                                                    |     |

# List of Figures

| 1  | ATA Controller Block Diagram                                       | . 8        |

|----|--------------------------------------------------------------------|------------|

| 2  | Physical Region Descriptor (PRD) Table Entry                       | 18         |

| 3  | Primary IDE Channel DMA Control Register (BMICP)                   | 34         |

| 4  | Primary IDE Channel DMA Status Register (BMISP)                    | 35         |

| 5  | Primary IDE Channel DMA Descriptor Table Pointer Register (BMIDTP) | 36         |

| 6  | Primary IDE Channel Timing Register (IDETIMP)                      | 37         |

| 7  | IDE Controller Status Register (IDESTAT)                           | 38         |

| 8  | Ultra-DMA Control Register (UDMACTL)                               | 39         |

| 9  | Miscellaneous Control Register (MISCCTL)                           | 40         |

| 10 | Task File Register Strobe Timing Register (REGSTB)                 | 41         |

| 11 | Task File Register Recovery Timing Register (REGRCVR)              | 42         |

| 12 | Data Register Access PIO Strobe Timing Register (DATSTB)           | 43         |

| 13 | Data Register Access PIO Recovery Timing Register (DATRCVR)        | 44         |

| 14 | Multiword DMA Strobe Timing Register (DMASTB)                      | 45         |

| 15 | Multiword DMA Recovery Timing Register (DMARCVR)                   | 46         |

| 16 | Ultra-DMA Strobe Timing Register (UDMASTB)                         | 47         |

| 17 | Ultra-DMA Ready-to-Pause Timing Register (UDMATRP)                 | 48         |

| 18 | Ultra-DMA Timing Envelope Register (UDMATENV)                      | 49         |

| 19 | Primary IO Ready Timer Configuration Register (IORDYTMP)           | <b>5</b> 0 |

# List of Tables

| 1  | Supported IDE Controller Signals                                                               | 10         |

|----|------------------------------------------------------------------------------------------------|------------|

| 2  | Unsupported IDE Controller Signals                                                             | 12         |

| 3  | Description of Single Physical Region Descriptor (PRD) Table Entry                             | 18         |

| 4  | Identifying the ATA Controller Interrupt Sources                                               | 25         |

| 5  | DMA Driven Interrupt Conditions                                                                | 28         |

| 6  | ATA/ATAPI Device Interface Connections for a Standard ATA/ATAPI Device                         | 29         |

| 7  | ATA/ATAPI Device Interface Connections for a Standard ATA/ATAPI Device Through a Level-Shifter | 31         |

| 8  | ATA/ATAPI Device Interface Connections for a Compact Flash Device                              | 32         |

| 9  | ATA Host Controller Registers                                                                  |            |

| 10 | ATA Controller Registers in the Attached Device                                                | 33         |

| 11 | Primary IDE Channel DMA Control Register (BMICP) Field Descriptions                            | 34         |

| 12 | Primary IDE Channel DMA Status Register (BMISP) Field Descriptions                             | 35         |

| 13 | Primary IDE Channel DMA Descriptor Table Pointer Register (BMIDTP) Field Descriptions          | 36         |

| 14 | Primary IDE Channel Timing Register (IDETIMP) Field Descriptions                               |            |

| 15 | IDE Controller Status Register (IDESTAT) Field Descriptions                                    |            |

| 16 | Ultra-DMA Control Register (UDMACTL) Field Descriptions                                        | 39         |

| 17 | Miscellaneous Control Register (MISCCTL) Field Descriptions                                    |            |

| 18 | Task File Register Strobe Timing Register (REGSTB) Field Descriptions                          |            |

| 19 | Task File Register Recovery Timing Register (REGRCVR) Field Descriptions                       | 42         |

| 20 | Data Register Access PIO Strobe Timing Register (DATSTB) Field Descriptions                    | 43         |

| 21 | Data Register Access PIO Recovery Timing Register (DATRCVR) Field Descriptions                 | 44         |

| 22 | Multiword DMA Strobe Timing Register (DMASTB) Field Descriptions                               | 45         |

| 23 | Multiword DMA Recovery Timing Register (DMARCVR) Field Descriptions                            | 46         |

| 24 | Ultra-DMA Strobe Timing Register (UDMASTB) Field Descriptions                                  | 47         |

| 25 | Ultra-DMA Ready-to-Pause Timing Register (UDMATRP) Field Descriptions                          | 48         |

| 26 | Ultra-DMA Timing Envelope Register (UDMATENV) Field Descriptions                               | 49         |

| 27 | Primary IO Ready Timer Configuration Register (IORDYTMP) Field Descriptions                    | <b>5</b> 0 |

Preface SPRUE21–December 2005

#### About This Manual

The AT attachment/ATA packet interface (ATA/ATAPI), also known as IDE controller, is the traditional choice of the communication medium between a portable computer (PC) and a hard-disk drive. Ever since its adoption by the industry, it has been the choice of interface between a PC and a common storage medium. This standard interface provides a common attachment interface for system manufacturers, system integrators, software suppliers, and suppliers of intelligent storage devices.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM644x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DM644x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <u>www.ti.com/c6000</u>.

- SPRUE14 TMS320DM644x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM644x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem, the video processing subsystem, and a majority of the peripherals and external memories.

- <u>SPRUE15</u> *TMS320DM644x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM644x Digital Media System-on-Chip (DMSoC).

- <u>SPRUE19</u> *TMS320DM644x DMSoC Peripherals Overview Reference Guide.* Provides an overview and briefly describes the peripherals available on the TMS320DM644x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

- SPRU871 TMS320C64x+ DSP Megamodule Reference Guide. Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- <u>SPRAAA6</u> *EDMA v3.0 (EDMA3) Migration Guide for TMS320DM644x DMSoC.* Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) enhanced direct memory access (EDMA2) to the TMS320DM644x Digital Media System-on-Chip (DMSoC) EDMA3. This document summarizes the key differences between the EDMA3 and the EDMA2 and provides guidance for migrating from EDMA2 to EDMA3.

# ATA Controller

#### 1 Introduction

The AT attachment/ATA packet interface (ATA/ATAPI), also known as IDE controller, is the traditional choice of the communication medium between a portable computer (PC) and a hard-disk drive. Ever since its adoption by the industry, it has been the choice of interface between a PC and a common storage medium. This standard interface provides a common attachment interface for system manufacturers, system integrators, software suppliers, and suppliers of intelligent storage devices.

This document describes the ATA controller on the TMS320DM644x Digital Media System-on-Chip (DMSoC). The ATA controller provides a glueless interface to storage media to be used by video and audio applications for video and audio data storage.

#### 1.1 Purpose of the Peripheral

The AT attachment/ATA packet interface (ATA/ATAPI) is an interface that is most commonly used by PCs and portable devices to interface a host processor with data storage or audio devices. The ATA interface debuted in the mid 1980s as an interface between a hard-disk drive and a PC by way of a ribbon cable. Ever since then, other devices, mostly storage, including compact Flash and compact disks have widely adopted the ATA/ATAPI interface, leveraging from its proven capability as the means for connecting to a host processor. These allowed device manufacturers to avoid developing and supporting a proprietary interface that would significantly limit the use of their devices. The ATA/ATAPI interface is popular due to its simplicity, low cost, reliability, compatibility, as well as its wide acceptance and long history of use within the PC industry market.

The DM644x DMSoC supports an onboard ATA/ATAPI host controller module (IDE controller) allowing it to exploit access to a vast majority of available data storage and audio devices. The onboard IDE host controller performs PIO, multiword, and ultra-DMA transactions with ATA and ATAPI compliant devices. Hard-disk drive, compact disk (CD), compact Flash (CF), and DVD are some ATA/ATAPI-compliant devices that the IDE host controller is destined to interface with. This allows applications like streaming media and digital still cameras the means for easy access to commonly used external storage devices.

The content described here assumes the knowledge of ATA/ATAPI-6 and compact Flash v2.0 specifications and should be used in conjunction with this document.

#### 1.2 Features

The IDE host controller logic supports PIO, multiword DMA and ultra-DMA (ultra-ATA) modes. The ATA controller has the following features:

- Single channel capable for connecting up to two ATA/ATAPI devices

- Supports interface to compact Flash (CF) configured in True-IDE mode

- Supports PIO modes 0, 1, 2, 3, and 4

- Supports multiword DMA modes 0, 1, and 2

- Supports ultra-DMA modes 0, 1, 2, 3, 4, and 5

- Full scatter gather DMA capability

- Programmable timing parameters provide support of any multiple ATA timing options mode at any processor clock frequency

#### 1.3 Functional Block Diagram

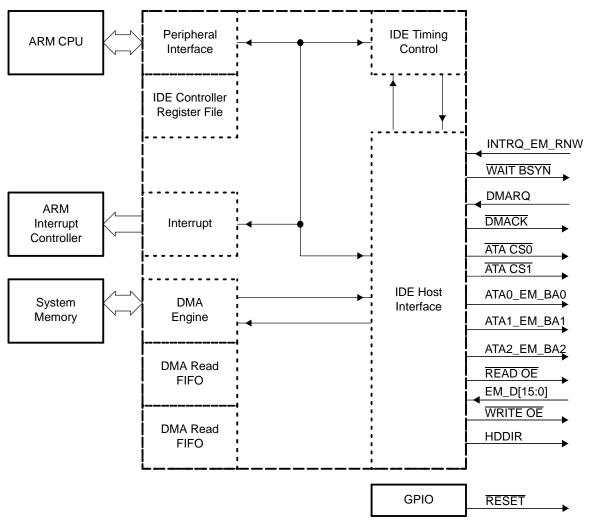

The ATA controller is shown in Figure 1.

#### Figure 1. ATA Controller Block Diagram

#### 1.4 Supported Use Cases

The IDE controller is commonly used to interface to ATA and ATAPI devices. Devices like hard disk drives are ATA devices. Devices like CDs, compact flash, and DVDs are ATAPI devices. Both ATA and ATAPI devices use the same identical interface and differ partly in protocol (specifically the way command is delivered to the attached device). This difference is transparent to the IDE host controller and meaningful to the driver/firmware that is running on the host supporting the attached device. For ATA devices, all commands and commands parameters are register-driven while ATAPI devices make use of both register-driven and packet-driven commands. Consult the ATA/ATAPI-6 specification for more information.

For information on how to interface to a standard ATA/ATAPI device, see Section 3.1.

For information on how to interface to a standard ATA/ATAPI device with a higher I/O voltage requirement using a level-shifter, see Section 3.2.

For information on how to interface to a compact Flash (CF) device, see Section 3.3.

# 1.5 Industry Standard(s) Compliance

The IDE controller supports the ATA/ATAPI-6 and compact flash 2.0 specifications. The specific modes of operations (PIO, multiword, and ultra-DMA) depend on the frequency at which the IDE controller operates. For this reason, not all modes supported by the specification and device may be used if the clocking to the IDE controller is low. The actual mode supported (subset of the ATA/ATAPI standard) by the device is directly tied to the IDE controller clock sourcing. For more information on the clocking provided to the peripheral, see Section 2.1. In addition to possible reduction of mode support due to low frequency clocking, the processor does not pin out all the signals available in the ATA/ATAPI specification. Additional signals (necessary to support wide range of devices) that are not present within the ATA/ATAPI standard specification are also available. See Section 2.2 for more information on the signals supported on this peripheral.

## 1.6 Terminology Used in This Document

The following is a brief explanation of some terms used in this document:

| Term           | Meaning                                                                |

|----------------|------------------------------------------------------------------------|

| ATA/ATAPI      | AT attachment/ATA packet interface                                     |

| ATA controller | ATA/ATAPI controller peripheral                                        |

| CF             | Compact Flash                                                          |

| device         | External ATA/ATAPI device attached to the IDE controller               |

| DMA            | DMA within the ATA controller, not the processor EDMA system           |

| host           | Processor IDE controller (this peripheral), unless otherwise specified |

| IDE controller | Synonymous with ATA controller                                         |

| processor      | DM644x Digital Media Processor                                         |

## 2 Peripheral Architecture

This section discusses the architecture of the ATA controller.

#### 2.1 Clock Control

The IDE controller uses a single programmable clock for its operation. This clock needs to be reconfigured prior to enabling access to the attached ATA/ATAPI device. The maximum clock frequency supplied to the ATA controller is dependent upon the clock frequency of the processor. See the device specific data manual for more information on the processor voltage and speed characteristics.

SYSCLK5 (PLL1 output frequency divided by 6) is the source of the clock to the ATA peripheral. To ensure proper operation, the operating frequency of the ATA controller clock should be chosen in such a way that it is at least twice as fast as the ATA data strobe frequency in order to achieve expected throughput.

# 2.2 Signal Descriptions

# 2.2.1 ATA/ATAP Interface Signals Supported by the ATA Controller

Table 1 describes the signals supported by the IDE controller interface.

| Terminal Name             | Direction From IDE<br>Controller: In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATA_CS0                   | Output                                   | Chip Select Signals 0 and 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ATA_CS1                   |                                          | These are the chip select signals from the host used to select the Command Block or Control Block registers. ATA_CS0 is asserted during Command Block register accesses. ATA_CS1 is asserted during Control Block register accesses. When DMACK is asserted, ATA_CS0 and ATA_CS1 are both asserted and transfers will be 16 bits wide.                                                                                                                                                                                                                                                                                                                                                                    |

| ATA0_EM_BA0               | Output                                   | Device Address Bits[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ATA1_EM_BA1<br>ATA2_EM_A0 |                                          | This is a 3-bit binary coded address asserted by the host to access a register or data port in the attached device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EM_D[15:0]                | Input/Output                             | Host Read/Write Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                           |                                          | This is a 16-bit bi-directional data interface between the host and the device. Data transfers are 16-bits wide except for CF devices that implement 8-bit data transfers. In this case, EM_D[7:0] will be used for 8-bit register transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMARQ                     | Input                                    | Device DMA Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |                                          | The device will assert this signal, used for DMA data transfers between host and device, when the device is ready to transfer data to or from the host in any of the DMA modes. For multiword transfers, the direction of data transfer is controlled by READ_OE and WRITE_OE. This signal is used in a handshake manner with DMACK, that is, the device will wait until the host asserts DMACK before negating DMARQ, and re-asserting DMARQ if there is more data to transfer. For multiword DMA transfers, the DMARQ/DMACK handshake is used to provide flow control during the transfer. For ultra-DMA, the DMARQ/DMACK handshake is used to indicate when the function of interface signals changes. |

|                           |                                          | This signal will be released when the device is not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMACK                     | Output                                   | Host DMA Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           |                                          | This signal is used by the host in response to DMARQ to initiate DMA transfers. For multiword DMA transfers, the DMARQ/DMACK handshake is used to provide flow control during the transfer. For ultra-DMA, the DMARQ/DMACK handshake is used to indicate when the function of interface signals changes.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                           |                                          | When DMACK is asserted, ATA_CS0 and ATA_CS1 is not asserted and transfers are 16 bits wide.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WAIT_BSYN                 | Input                                    | Device I/O ready during PIO transaction<br>DMA ready during ultra-DMA write<br>DMA strobe during ultra-DMA read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                                          | WAIT_BSYN is negated to extend the host transfer cycle of any host register access (PIO 8-bit) or PIO data access when the device is not ready to respond to a transfer request. If the device requires that the host transfer cycle time be extended, the device will assert the WAIT_BSYN signal. Devices that support PIO modes 3 and above are required by the ATA/ATAPI specification to support WAIT_BSYN.                                                                                                                                                                                                                                                                                          |

|                           |                                          | For ultra-DMA data-write transaction, this signal is a flow control signal for data-out bursts. This signal is asserted by the device to indicate to the host that the device is ready to receive Ultra DMA data-out bursts. The device may negate WAIT_BSYN to pause an Ultra DMA data-out burst.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           |                                          | For ultra-DMA data-read transaction, this signal is a data-in strobe signal from the device for data-in burst. Both the rising and falling edges of WAIT_BSYN latch the data from EM_D[15:0] into the host. The device may stop generating WAIT_BSYN edges to pause an ultra DMA data-in burst.                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                                          | This signal is released when the device is not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 1. Supported IDE Controller Signals

| Terminal Name | Direction From IDE<br>Controller: In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ_OE       | Output                                   | PIO Read Transaction Indicator<br>DMA Ready during Ultra-DMA Read<br>DMA Data Strobe during Ultra-DMA Write                                                                                                                                                                                                                                                                                                         |

|               |                                          | READ_OE is the strobe signal used by the host to read device registers or data. Data is transferred on the negation of this signal.                                                                                                                                                                                                                                                                                 |

|               |                                          | When performing ultra-DMA data read transaction, this signal is used by the host for flow control during data-in bursts. This signal is asserted by the host to indicate to the device that the host is ready to receive ultra-DMA data-in bursts. The host may negate $\overline{\text{READ}_O\text{E}}$ to pause an ultra DMA data-in burst.                                                                      |

|               |                                          | When performing ultra-DMA data write transaction, the host uses the READ_OE to strobe the ultra-DMA data-out burst.                                                                                                                                                                                                                                                                                                 |

|               |                                          | Both the rising and falling edges of READ_OE latch the data from EM_D[15:0] into the device. The host may stop generating READ_OE edges to pause an ultra DMA data-out burst.                                                                                                                                                                                                                                       |

| WRITE_OE      | Output                                   | PIO Write Transaction Indicator<br>Stop Ultra-DMA Data Read/Write Bursts                                                                                                                                                                                                                                                                                                                                            |

|               |                                          | WRITE_OE is the strobe signal used by the host to write device registers (PIO 8-bit) or data (PIO 16-bit). Data is transferred on the negation of this signal.                                                                                                                                                                                                                                                      |

|               |                                          | The host will negate WRITE_OE prior to initiation of an ultra DMA burst. The host will negate WRITE_OE before data is transferred in an ultra-DMA burst. Assertion of WRITE_OE by the host during an ultra-DMA burst signals the termination of the ultra DMA burst.                                                                                                                                                |

| INTRQ_EM_RNW  | Input                                    | Attached Device Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                                          | This signal is used by the selected device to interrupt the host system when interrupt pending is set. When the nIEN bit is cleared to zero and the device is selected, INTRC is enabled. When the nIEN bit is set to one or the device is not selected, the INTRQ signal is disabled.                                                                                                                              |

|               |                                          | When asserted, this signal should be negated by the device within 400 ns of the negation of READ_OE that reads the Status register to clear interrupt pending. When asserted, this signal should be negated by the device within 400 ns of the negation of WRITE_OE that writes the Command register to clear interrupt pending.                                                                                    |

|               |                                          | When the device is selected by writing to the Device register while interrupt pending is set, INTRQ_EM_RNW should be asserted within 400 ns of the negation of WRITE_OE that writes the device register. When the device is deselected by writing to the device register while interrupt pending is set, INTRQ_EM_RNW should be released within 400 ns of the negation of WRITE_OE that writes the device register. |

|               |                                          | This signal shares a function with an EMIF signal. For simplicity, in the remainder of this document this signal will be referred to as INTRQ.                                                                                                                                                                                                                                                                      |

| HDDIR         | Output                                   | External Level Shifter Direction Indicator                                                                                                                                                                                                                                                                                                                                                                          |

|               |                                          | This signal is used when a 3.3 V or 5.0 V tolerant ATA/ATAPI devices are used to interface with the IDE controller. This signal indicates the direction of the current data transfer.                                                                                                                                                                                                                               |

|               |                                          | Although this signal provides direction control, it is the responsibility of the user to enable the shifter properly. The processor does not provide an enable control for the level shifter.                                                                                                                                                                                                                       |

# Table 1. Supported IDE Controller Signals (continued)

#### 2.2.2 ATA/ATAPI/Compact Flash Specification Signals Not Supported by This Peripheral

The processor supports all the signals needed to realize the supported modes of operation. Table 2 lists some of the signals that are present within the ATA/ATAPI specification that are not available. In addition, the processor supports additional signals to interface to devices that are 3.3 V and 5.0 V tolerant devices.

| Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                               | This signal is used by the IDE controller to perform a hardware reset on the attached ATA/ATAPI device.<br>A GPIO signal can be used for this purpose due to lack of a dedicated ATA reset signal on the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cable Select (CSEL)                 | The processor host IDE controller requires the use of the proper type cable based on the maximum mode of operation in which the external device is intended to operate. Specifically, if the external device supports UDMA mode greater than mode2, then it is expected that an 80-conductor ribbon cable be used to connect the IDE controller with the ATA device. The use of a 40-conductor ribbon cable with higher UDMA mode of operation would result in reduced throughput due to the introduction of error from signals propagating on adjacent conductors. This signal is not necessary because an 80-conductor cable must be used with the DM644x. |

| Cable ID (CBLID)                    | The Cable ID signal is used by attached devices in order to configure themselves as master or slave without the need for a jumper configuration setting. The host does not need to have a dedicated signal to drive this signal. This task is achieved by tying the appropriate pin (on the header on the processor side) low external to the processor.                                                                                                                                                                                                                                                                                                     |

| True IDE Mode Selector<br>(ATA_SEL) | This signal needs to be driven low prior to power-up in order to configure a Compact Flash in True IDE mode. Since any Compact Flash mounted to work with the processor is only useful in True IDE mode, the state of this signal is tied to ground by the header. Note that CF devices use a 50 pin header that is different from the standard ATA/ATAPI header.                                                                                                                                                                                                                                                                                            |

#### Table 2. Unsupported IDE Controller Signals

#### 2.3 Pin Multiplexing

The DM644x ATA/ATAPI controller peripheral signals share pins on the processor package with other processor functions. For detailed information on the processor pin multiplexing and configuration, see the pin multiplexing information in the device-specific data manual.

#### 2.4 Protocol Description(s)

The IDE controller supports the protocols defined in the ATA/ATAPI-6 and compact Flash 2.0 specifications.

#### 2.5 General Architecture

#### 2.5.1 Programmable Timing Registers

The IDE controller implements several programmable timing registers that allow users to reprogram the key IDE interface signal timings for the four transfer types: 8-bit task file registers accesses, 16-bit PIO data accesses, multiword DMA transfers, and ultra-DMA transfers. This allows the host controller to effectively be reconfigured to support a wide range of input clock frequencies and any target interface for all transfer types.

The default state for the programmable timing registers logic is disabled; that is, the TIMORIDE bit in the miscellaneous control register (MISCCTL) is 0. The programmable timing registers should be enabled by setting the TIMORIDE bit to 1 for proper operation. The IDE controller may not be able to operate correctly if the programmable timing registers are not enabled.

Four sets of programming timing registers exist to support the four types of IDE transfers. In addition, the MISCCTL upper bits allow for a common control over the write data hold time for three of the four transfers: task file writes, PIO writes, and multiword DMA writes. The write data hold time in MISCCTL must satisfy the worst case requirement of these three modes.

- The task file register strobe timing register (REGSTB) and the task file register recovery timing register (REGRCVR) control the timing parameters for 8-bit accesses of the task file registers.

- The data register PIO strobe timing register (DATSTB) and the data register PIO recovery timing register (DATRCVR) control the timing parameters for PIO data accesses.

- The DMA strobe timing register (DMASTB) and the DMA recovery timing register (DMARCVR) control timings for multiword DMA accesses.

- The ultra DMA strobe timing register (UDMASTB), the ultra DMA ready-to-stop timing register (UDMATRP), and the ultra DMA timing envelope register (UDMATENV) control the timing of ultra DMA accesses.

The timing override registers are programmed with a value indicating the number of clock cycles (minus 1 cycle) that the IDE controller will wait to meet a particular timing parameter. You identify the minimum or maximum value for a timing parameter from the IDE specification, determine the IDE clock frequency, and then calculate the number of clock cycles necessary to meet that timing parameter. For example, if the required IDE controller clock frequency is 99 MHz (10.10 ns period), then to meet a minimum IDE interface timing requirement of 25 ns, 3 clock cycles are required (3 cycles  $\times$  10.10 ns = 30.3 ns). This means that the corresponding timing register that controls the parameter would be programmed with a 2 (3 clock cycles minus 1 cycle). If the IDE controller clock frequency is 50 MHz (20 ns) and a minimum timing requirement of 55 ns is to be met, this would require at least 3 clock cycles (3 cycles  $\times$  20 ns = 60 ns); therefore, the timing register should be programmed with a value of 2.

Note that programming the HWNHLD*n*P bits in MISCCTL controls the write data hold times used for task file registers writes, PIO data writes, and multiword DMA data writes. Since a single timing programmable parameter is used for all three types of write transfers, the value programmed here will be the largest among the three transfers: PIO-8 bit, PIO-16-bit, and multiword DMA.

#### 2.5.1.1 Programming 8-bit Task File Timing Registers

The REGSTB, REGRCVR, and MISCCTL are used in reprogramming the timings for 8-bit task file register accesses. The required IDE timing parameters for 8-bit task file register accesses are defined in the ATA/ATAPI-6 specification.

The REGSTB and REGRCVR can be programmed to match the parameters  $t_0$  (cycle time),  $t_2$  (strobe time), and  $t_{2i}$  (recovery time). The HWNHLD bits in MISCCTL are used to program the hold time for the write data ( $t_4$  parameter).

The REGSTB directly controls the number of clock cycles that the READ\_OE and WRITE\_OE strobes will be asserted during 8-bit task file accesses. This corresponds to the strobe width timing parameter, t<sub>2</sub>.

The REGRCVR defines the number of clock cycles for the recovery time between task file accesses. This corresponds to recovery timing parameter,  $t_{2i}$ .

The sum of both parameters ( $t_2 + t_{2i}$ ) must be equal or greater than the cycle time,  $t_0$ . The HWNHLD*n*P bits in MISCCTL allow control over the number of clock cycles for the write data hold time during task file writes.

With knowledge of the IDE controller clock frequency, you can program the appropriate number of clock cycles to match the timing requirements. Note that the timing registers must be programmed with a value one less than the desired number of cycles, so a value of 0 specifies 1 clock cycle, a value of 1 specifies 2 clock cycles, etc.

Example 1 and Example 2 illustrate how the 8-bit task file timing registers can be programmed.

#### Example 1. 8-Bit Task File Timing Registers Programming for Mode 0

Programming task file accesses for mode 0 operation using an IDE controller clock frequency of 66 MHz (15 ns period).

For mode 0 operation,  $t_2$  requires a minimum of 290 ns, this translates to a minimum of 20 clock cycles (20 cycles × 15 ns = 300 ns). There is no requirement for  $t_{2i}$  in mode 0 operation, but  $t_0$  requires a minimum of 600 ns, or 40 clock cycles. This means REGSTB and REGRCVR can be programmed to any combination equaling 40 (or more) clock cycles, with REGSTB specifying at least 20 clock cycles.

Sample programming values are REGSTB = 13h (20 clock cycles) and REGRCVR = 13h (20 clock cycles), or REGSTB = 1Fh (32 clock cycles) and REGRCVR = 7h (8 clock cycles). In addition, the minimum write data hold time specified is 30 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 2 clock cycles. A sample value is HWNHLD*n*P = 2h (3 clock cycles) providing enough hold time and margin.

#### Example 2. 8-Bit Task File Timing Registers Programming for Mode 4

Programming task file accesses for mode 4 operation using an IDE controller clock frequency of 99 MHz (10.10 ns period).

For mode 4 operation,  $t_2$  requires a minimum of 70 ns, this translates to a minimum of 7 clock cycles (7 cycles × 10.10 ns = 70.70 ns).  $t_{2i}$  is defined to be at least 25 ns, this translates to a minimum of 3 clock cycles (3 cycles × 10.10 ns = 30.30 ns). The minimum cycle time  $t_0$  is 120 ns, or 12 clock cycles. This means REGSTB and REGRCVR can be programmed to any combination equaling 12 (or more) clock cycles, with REGSTB specifying at least 7 cycles and REGRCVR specifying at least 3 cycles.

Sample programming values are REGSTB = 7h (8 clock cycles) and REGRCVR = 3h (4 clock cycles), or REGSTB = 8h (9 clock cycles) and REGRCVR = 2h (3 clock cycles). In addition, the minimum write data hold time specified is 10 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 1 clock cycle. A sample value is HWNHLD*n*P = 1h (2 clock cycles) providing enough hold time and margin.

#### 2.5.1.2 Programming Data Register Timing Register Access

The DATSTB and DATRCVR are used in reprogramming the timings for 16-bit PIO data accesses. The required IDE timing parameters for 8-bit task file register accesses are defined in the ATA/ATAPI-6 specification.

The DATSTB and DATRCVR can be programmed to match the parameters  $t_0$  (cycle time),  $t_2$  (strobe time), and  $t_{2i}$  (recovery time). The HWNHLD*n*P bits in MISCCTL are used to program the hold time for the write data ( $t_4$  parameter).

The DATSTB directly controls the number of clock cycles that the READ\_OE and WRITE\_OE strobes will be asserted during the PIO data access. This corresponds to the strobe width timing parameter, t<sub>2</sub>.

The DATRCVR defines the number of clock cycles for the recovery (de-assert) time for the PIO data access. This corresponds to recovery timing parameter,  $t_{2i}$ .

The sum of both parameters  $(t_2 + t_{2i})$  must be equal or greater than the cycle time,  $t_0$ . The HWNHLD*n*P bits in MISCCTL allow control over the number of clock cycles for the write data hold time during PIO data writes.

With knowledge of the IDE controller clock frequency, you can program the appropriate number of clock cycles to match the timing requirements. Note that the timing registers must be programmed with a value one less than the desired number of cycles, so a value of 0 specifies 1 clock cycle, a value of 1 specifies 2 clock cycles, etc.

Example 3 and Example 4 illustrate how the data register access timing registers can be programmed.

#### Example 3. Data Register Timing Registers Programming for Mode 2

Programming PIO data accesses for mode 2 operation using an IDE controller clock frequency of 33 MHz (30 ns period).

For mode 2 operation,  $t_2$  requires a minimum of 100 ns, this translates to a minimum of 4 clock cycles (4 cycles × 30 ns = 120 ns). There is no requirement for  $t_{2i}$  in mode 2 operation, but the minimum requirement for  $t_0$  is 240 ns, or 8 clock cycles. This means DATSTB and DATRCVR can be programmed to any combination equaling 8 (or more) clock cycles, with DATSTB specifying at least 4 clock cycles.

Sample programming values are DATSTB = 3h (4 clock cycles) and DATRCVR = 3h (4 clock cycles), or REGSTB = 5h (6 clock cycles) and DATRCVR = 1h (2 clock cycles). In addition, the minimum write data hold time specified is 15 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 1 clock cycle. A sample value is HWNHLD*n*P = 0h (0 clock cycles) providing enough hold time and margin.

#### Example 4. Data Register Timing Registers Programming for Mode 3

Programming PIO data accesses for mode 3 operation using an IDE controller clock frequency of 99 MHz (10.10 ns period).

For mode 3 operation,  $t_2$  requires a minimum of 80 ns, this translates to a minimum of 8 clock cycles (8 cycles × 10.10 ns = 80.80 ns). The minimum requirement on  $t_{2i}$  is defined to be 70 ns, this translates to a minimum of 7 clock cycles (7 cycles × 10.10 ns = 70.70 ns). The minimum cycle time  $t_0$  is 180 ns, or 18 clock cycles. This means that DATSTB and DATRCVR can be programmed to any combination equaling 18 (or more) clock cycles, with DATSTB specifying at least 8 cycles and DATRCVR specifying at least 7 cycles.

Sample programming values are DATSTB = 9h (10 clock cycles) and DATRCVR = 7h (8 clock cycles), or DATSTB = Ah (11 clock cycles) and DATRCVR = 6h (7 clock cycles). In addition, the minimum write data hold time specified is 10 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 1 clock cycle. A sample value is HWNHLD*n*P = 0h (1 clock cycle) providing enough hold time and margin.

#### 2.5.1.3 Programming Multiword DMA Register Accesses

The DMASTB and DMARCVR are used in reprogramming the timings for multiword DMA transfers. The required IDE timing parameters for multiword DMA transfers are defined in the ATA/ATAPI-6 specification.

The DMASTB and DMARCVR can be programmed to match the parameters  $t_0$  (cycle time),  $t_D$  (strobe time), and  $t_{KW}$  (recovery time for DMA write). The HWNHLD*n*P bits in MISCCTL are used to program the hold time for the write data ( $t_H$  parameter).

The DMASTB directly controls the number of clock cycles that the READ\_OE and WRITE\_OE strobes will be asserted during multiword DMA transfers. This corresponds to the strobe width timing parameter, t<sub>D</sub>.

The DMARCVR defines the number of clock cycles for the recovery time for multiword DMA transfers. This corresponds to recovery timing parameters,  $t_{KR}$  and  $t_{KW}$ .

The sum of both parameters must be equal or greater than the cycle time, t<sub>0</sub>. The HWNHLD*n*P bits in MISCCTL allow control over the number of clock cycles for the write data hold time during multiword DMA data writes.

With knowledge of the system clock frequency, you can program the appropriate number of clock cycles to match the timing requirements. Note that the timing registers must be programmed with a value one less than the desired number of cycles, so a value of 0 specifies 1 clock cycle, a value of 1 specifies 2 clock cycles, etc.

Example 5 and Example 6 illustrate how the timing of the multiword DMA registers can be programmed.

#### Example 5. Multiword DMA Register Access Programming for Mode 0

Programming multiword DMA transfers for mode 0 operation using an IDE controller clock frequency of 66 MHz (15 ns period).

For mode 0 operation,  $t_D$  requires a minimum of 215 ns, this translates to a minimum of 15 clock cycles (15 cycles × 15 ns = 225 ns). The minimum requirement on  $t_{KW}$  is 215 ns (for writes), this translates to a minimum of 15 clock cycles (15 cycles × 15 ns = 225 ns). The minimum requirement for  $t_0$  is 480 ns, or 32 clock cycles. This means DMASTB and DMARCVR can be programmed to any combination equaling 32 (or more) clock cycles, with both DMASTB and DMARCVR specifying at least 15 clock cycles.

Sample programming values are DMASTB = Fh (16 clock cycles) and DMARCVR = Fh (16 clock cycles), or DMASTB = 10h (17 clock cycles) and DMARCVR = Eh (15 clock cycles). In addition, the minimum write data hold time specified is 20 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 2 clock cycles. A sample value is HWNHLD*n*P = 2h (3 clock cycles) providing enough hold time and margin and also covering the PIO and task file mode 0 timings.

#### Example 6. Multiword DMA Register Access Programming for Mode 2

Programming multiword DMA transfers for mode 2 operation using an IDE controller clock frequency of 99 MHz (10.10 ns period).

For mode 2 operation,  $t_D$  requires a minimum of 70 ns, this translates to a minimum of 7 clock cycles (7 cycles × 10.10 ns = 70.70 ns). The minimum requirement on  $t_{KW}$  is 25 ns, this translates to a minimum of 3 clock cycles (3 cycles × 10.10 ns = 30.30 ns). The minimum cycle time  $t_0$  is 120 ns, or 12 clock cycles. This means that DMASTB and DMARCVR can be programmed to any combination equaling 12 (or more) clock cycles, with DMASTB specifying at least 7 cycles and DMARCVR specifying at least 3 cycles.

Sample programming values are DMASTB = 7h (8 clock cycles) and DMARCVR = 3h (4 clock cycles), or DMASTB = 8h (9 clock cycles) and DMARCVR = 2h (3 clock cycles). In addition, the minimum write data hold time specified is 10 ns, so the HWNHLD*n*P bits in MISCCTL should be programmed to a value of at least 1 clock cycle. A sample value is HWNHLD*n*P = 2h (3 clock cycles) providing enough hold time and margin and also covering the PIO and task file mode 2 timings.

#### 2.5.1.4 Programming Ultra-DMA Register Accesses

The UDMASTB, UDMATRP, and UDMATENV are used in reprogramming the timings for ultra-DMA transfers. The required IDE timings parameters for ultra-DMA transfers are defined in the ATA/ATAPI-6 specification.

The UDMASTB, UDMATRP, and UDMATENV can be programmed to match the parameters  $t_{CYC}$  (cycle time),  $t_{2CYCTYP}$  (two cycle time),  $t_{RP}$  (ready-to-pause), and  $t_{ENV}$  (time envelope).

The UDMASTB directly controls the number of clock cycles for the ultra-DMA strobe during ultra-DMA transfers. This corresponds to the strobe width timing parameter,  $t_{CYC}$ , which is  $\frac{1}{2}(t_{2CYCTYP})$ .

The UDMATRP defines the number of clock cycles for the ready-to-pause timing parameter, t<sub>RP</sub>.

The UDMATENV indicates the number of clock cycles for the timing envelope timing parameter, t<sub>ENV</sub>.

With knowledge of the IDE controller clock frequency, you can program the appropriate number of clock cycles to match the timing requirements. Note that the timing registers must be programmed with a value one less than the desired number of clock cycles, so a value of 0 specifies 1 clock cycle, a value of 1 specifies 2 clock cycles, etc.

Example 7 and Example 8 illustrate how the timing of the ultra-DMA registers can be programmed.

#### Example 7. Ultra-DMA Register Access Programming for Mode 5

Programming ultra-DMA transfers for mode 5 operation using an IDE controller clock frequency of 99 MHz (10.10 ns period).

For mode 5 operation,  $t_{2CYC}$  is 40 ns ( $t_{CYC}$  = 20 ns), this translates to a minimum of 2 clock cycles (2 cycles × 10.10 ns = 20.20 ns) per UDMA cycle. The requirement on  $t_{RP}$  is 85 ns, this translates to a minimum of 9 clock cycles (9 cycles × 10 ns = 90.90 ns).  $t_{ENV}$  has a minimum value of 20 ns and a maximum value of 50 ns, so this needs to be 2 to 5 clock cycles (2 × 10 ns = 20.20 ns to 5 × 10 ns = 50.50 ns).

Sample programming values are UDMASTB = 1h (2 clock cycles), UDMATRP = 8h (9 clock cycles), and UDMATENV = 2h (3 clock cycles).

#### Example 8. Ultra-DMA Register Access Programming for Mode 4

Programming ultra-DMA transfers for mode 4 operation using an IDE controller clock frequency of 66 MHz (15 ns period).

For mode 4 operation,  $t_{2CYC}$  is 60 ns ( $t_{CYC}$  = 30 ns), this translates to a minimum of 2 clock cycles (2 cycles × 15 ns = 30 ns) per UDMA cycle. The requirement on  $t_{RP}$  is 100 ns, this translates to a minimum of 7 clock cycles (7 cycles × 15 ns = 105 ns).  $t_{ENV}$  has a minimum value of 20 ns and a maximum value of 55 ns, so this needs to be 2 to 4 clock cycles (2 cycles × 15 ns = 30 ns to 4 cycles × 15 ns = 60 ns).

Sample programming values are UDMASTB = 1h (2 clock cycles), UDMATRP = 6h (7 clock cycles), and UDMATENV = 2h (3 clock cycles).

#### 2.6 DMA and PIO Data Transaction Overview

The IDE controller supports a dedicated DMA controller in order to handle DMA transfers between host memory and attached ATA/ATAPI device. This occurs for both multiword and ultra-DMA transfers during DMA writes to and reads from the device. The DMA controller includes logic to manage the physical region descriptors (PRDs) that describe the DMA transfers, and controls a set of 32-bit wide FIFOs (256-byte read FIFO and 256-byte write FIFO resident within the IDE controller) to temporarily store data for DMA transfers.

When pre-fetching and post-writing is enabled, the dedicated DMA controller also controls PIO sector writes and reads even though this is a PIO transaction. The internal FIFO is reused for these PIO transfers to store the pre-fetch/post-write data. During PIO reads, the sector data is pre-fetched into the FIFO and then read out of the FIFO by firmware. During PIO write, the PIO write sector data is stored in the FIFO and then eventually written out through the IDE interface to the device.

#### 2.6.1 DMA Controller and FIFO Operation

The DMA controller is the primary initiator for DMA transfers for both multiword and ultra-DMA read and write transfers. For any ATA DMA writes to the device, the DMA controller will initiate a read transfer from host memory to fill up its internal FIFO and then transfer the data out of the FIFO to the ATA device. For ATA DMA read transfers from the device to host/system memory, the DMA controller will initiate a read transfer and read data from the ATA device into the internal FIFO and then transfer the data from the FIFO into host memory. The DMA controller makes use of the physical region descriptors to identify buffer locations and sizes of data (in bytes) to be transferred for its data transaction.

The difference between multiword DMA and ultra-DMA transfers is mostly on the signaling part of the transaction. For multiword DMA transactions, the host IDE controller is responsible for strobing data. In addition, a single word is transferred per strobe cycle. For ultra-DMA data transactions, data strobing is

#### Peripheral Architecture

handled by the entity that is sending the data. If the data transaction is a write to a disk, then the host IDE controller is responsible for strobing the data. However, if the data transaction is a read from a disk, then the attached device is responsible for strobing the data. In addition, during ultra-DMA transactions, one word (2 bytes/word) is transferred for every edge of the strobe within a single strobe cycle increasing the throughput.

#### 2.6.1.1 Physical Region Descriptors (PRDs)

The physical region descriptors (PRDs) define the physical memory regions that data is transferred from (when moving data from host memory to the ATA device) or transferred to (when moving data from the ATA device to host memory). The DMA controller contains the logic and control for handling the physical region descriptors. When a DMA transfer is started, the DMA controller will issue a two-word burst to read the first descriptor from memory. It then decodes and stores the byte transfer count and the source or target memory address, and then starts the DMA operation using the descriptor information. Once a PRD has been completely processed by the DMA controller and the entire DMA transfer has completed, the next PRD in the table will be fetched and processed. If all PRD entries have been processed, an interrupt is generated.

The DMA interface is used to control data transfers to and from host memory and the FIFO internal to the IDE controller block. The DMA engine contains the bus master IDE control registers. These registers are the primary IDE channel DMA control register (BMICP), the primary IDE channel DMA status register (BMISP), and the primary IDE channel DMA descriptor pointer register (BMIDTP).

The DMA engine interfaces to the DMA interface to the processor on one end and the IDE controller interface on the other. The IDE controller block strobes data into and out of the FIFO in the DMA engine block, based on the setting of the read/write direction bit (DMADIR bit in BMICP).

The BMIDTP is the pointer to a physical region descriptor table in system memory. This descriptor table contains physical region descriptors, which describe areas of memory that are involved in the data transfer. The descriptor table must be aligned on a 4-byte boundary and the table cannot cross a 64 KB boundary in memory.

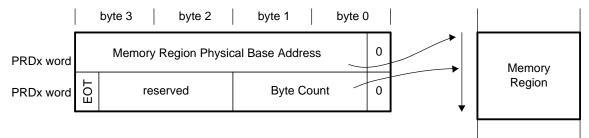

The physical memory region to be transferred is described by a physical region descriptor (PRD). Each PRD entry is 8 bytes in length (Figure 2 and Table 3). The first 4 bytes specify the byte address of a physical memory region; the next two bytes specify the count of the region in bytes (64K byte limit per region). A value of zero in these two bytes indicates 64K. Bit 7 of the last byte indicates the end of the table (EOT) when set to 1.

#### Figure 2. Physical Region Descriptor (PRD) Table Entry

| PRDx Word | Bit   | Description                                                                   |

|-----------|-------|-------------------------------------------------------------------------------|

| 0         | 31-0  | Memory region physical base address for PRDx (Must be 2-bytes aligned, even). |

| 1         | 31    | End of descriptor table marker (last PRD marker).                             |

| 1         | 30-16 | Reserved                                                                      |

| 1         | 15-0  | Byte count (must be even). A value of 0 implies 64 Kbytes size.               |

DMA activity is started when the host software sets the DMA start/stop bit (DMASTART bit in BMICP). The DMA engine state machine starts fetching the first entry in the PRD table. Once the PRD is fetched, the DMA engine state machine starts moving data between system memory and the FIFO. If the end of table (EOT) bit is 0, a new PRD table entry is fetched when the current physical region data transfer is complete. Data transfer continues until the last block of data is moved and the EOT bit is set to 1.

By linking multiple PRDs where each PRD identifies a buffer within the reach of the dedicated ATA DMA, the IDE controller can perform a single transaction where data is read from (or written to) multiple (PRD entries) buffers allowing the realization of the scatter gather capability.

When all data transfers for the DMA command submitted to the device are complete, the ATA/ATAPI device asserts INTRQ (if enabled). The DMA channel waits until the last data words have been moved to/from system memory before setting the interrupt bit (and passing the interrupt to the host interrupt handler) and clearing the bus master IDE active bit (IDEACT bit in BMISP).

#### 2.6.1.2 DMA Driven Disk Write Transfer Operation

To perform an ATA DMA write operation to an attached ATA/ATAPI device, a physical descriptor region is programmed by firmware indicating a system memory address to transfer data from and the number of bytes to transfer. The BMIDTP register is initialized with the start address of the first physical region descriptor. The DMA write command is then issued to the drive, and the DMA transfer starts when firmware programs the DMASTART bit in the primary IDE channel DMA control register (BMICP). When the DMASTART bit is set, the DMA controller issues a two-word (8 bytes) request to read the first physical region descriptor (PRD) entry from memory. This information is stored and processed by the DMA controller to indicate where in memory to start reading data from and also the size of data (in bytes) to transfer to the device. The DMA controller will then read out the data from host/system memory in bursts starting at the specified transfer address. Data read from the system memory is stored in the FIFO. The DMA controller will issue consecutive read bursts until it fills the FIFO. The transfer will start up again when the IDE controller starts emptying out the FIFO and space is available in the FIFO. When the DMA finishes processing the current PRD, based on the state of the EOT field of the current PRD, it will either fetch the next PRD or wait until the FIFO is fully empty to generate an interrupt (and also set the INTRSTAT bit in the primary IDE channel DMA status register, BMISP) and also clear the IDEACT bit in BMISP indicating the end of the transfer. The total data size entered within the PRD tables for a given DMA transaction should be equal to the data size value entered via command. The combination of status bit settings by the DMA controller and the attached device will allow you to identify the user entry condition.

#### 2.6.1.3 DMA Driven Disk Read Transfer Operation

To perform an ATA DMA read operation from an attached ATA/ATAPI device, a physical descriptor region is programmed by firmware indicating a system memory address to transfer the disk data to and the number of bytes to transfer. The BMIDTP register is initialized with the start address of the first physical region descriptor. The DMA read command is then issued to the drive, and the DMA transfer is started when firmware programs the DMASTART bit in the primary IDE channel DMA control register (BMICP). When the DMASTART bit is set, the DMA controller first issues a two-word (8 bytes) request to read the first physical region descriptor (PRD) entry from memory. This information is stored and processed by the DMA controller to indicate where in memory to store the data read from the disk and also the size (in bytes) of data transfer. The IDE controller will facilitate the reception of data from the attached device and store read data within the read FIFO. This occurs for both multiword and ultra-DMA writes. The IDE interface control logic continues reading words from the ATA device and storing them into the FIFO. The DMA controller routes read data to the system/host memory based on the PRD entries. This continues until the size entered in the PRD is exhausted or the FIFO becomes empty. When enough data to fill all the sizes noted within the PRD entries has been stored at the host/system memory, the DMA generates an interrupt (also sets the INTRSTAT bit in the primary IDE channel DMA status register, BMISP) and also clears the IDEACT bit in BMISP indicating the end of the transfer. The total data size entered within the PRD tables for a given DMA transaction should be equal to the data size value entered via command. he combination of status bit settings by the DMA controller and the attached device will allow you to identify the user entry condition.

#### 2.6.1.4 Miscellaneous Cases

#### 2.6.1.4.1 Multiword and Ultra-DMA Abort

After any type of DMA transfer has been initiated (multiword or ultra-DMA read or write), firmware is allowed to prematurely abort the transfer. A DMA transfer is initiated when a PRD has been set up and the DMASTART bit in the primary IDE channel DMA control register (BMICP) has been set to 1. After this time, firmware is allowed to prematurely terminate the transfer if it has not completed yet by writing a 0 to the DMASTART bit. When a DMA abort is detected by the IDE DMA controller, the DMA state machine will immediately abort the current transfer and return to an idle state. The IDE interface state machine will finish its current word transfer and terminate the transfer. The FIFO logic will be reset, so any words currently in the FIFO are lost. Also, any data transferred from memory to disk (during disk writes) or from the disk to memory (during disk reads) should be considered invalid, as it is will not be clear which words were actually transferred.

#### 2.6.1.4.2 Ultra-DMA Pause

Pauses in the data flow occur whenever one side of the transfer is not keeping up with the data flow.