# TMS320VC5505/5504 DSP Inter-IC Sound (I2S) Bus

# **User's Guide**

Literature Number: SPRUFP4

September 2009-Revised January 2010

| Pref | face     |                                                                     | . 6 |

|------|----------|---------------------------------------------------------------------|-----|

| 1    | Inter-IC | Sound (I2S) Bus                                                     | 9   |

| 1    | Introdu  | ction                                                               | 9   |

|      | 1.1      | Purpose of the Peripheral                                           | . 9 |

|      | 1.2      | Features                                                            | . 9 |

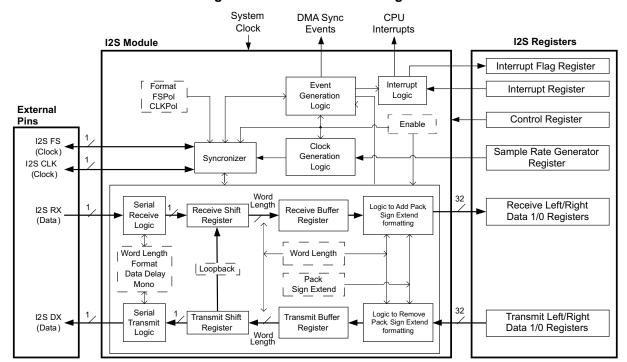

|      | 1.3      | Functional Block Diagram                                            | . 9 |

|      | 1.4      | Industry Standard(s) Compliance                                     | 10  |

| 2    | Archite  | cture                                                               | 11  |

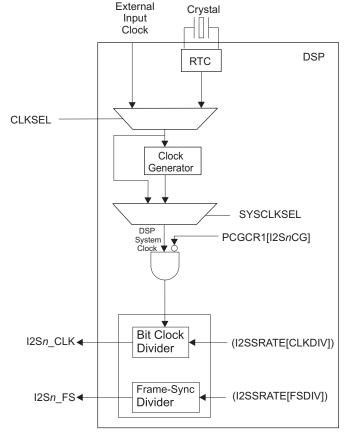

|      | 2.1      | Clock Control                                                       | 11  |

|      | 2.2      | I2S Clock Generator                                                 | 11  |

|      | 2.3      | Signal and Pin Descriptions                                         | 12  |

|      | 2.4      | Frame Clock Timing Requirement in Slave Mode                        | 13  |

|      | 2.5      | Protocol Description                                                | 15  |

|      | 2.6      | I2S Data Transfer and Control Behavior                              | 17  |

|      | 2.7      | I2S Data Transfer Latency                                           | 18  |

|      | 2.8      | Data Packing and Sign Extension Options                             | 18  |

|      | 2.9      | Reset Considerations                                                | 23  |

|      | 2.10     | Interrupt Support                                                   | 23  |

|      | 2.11     | DMA Event Support                                                   | 24  |

|      | 2.12     | Power Management                                                    | 24  |

|      | 2.13     | Emulation Considerations                                            | 24  |

|      | 2.14     | Steps for I2S Configuration and I2S Interrupt Service Routine (ISR) | 24  |

| 3    | Registe  | rs                                                                  | 26  |

|      | 3.1      | I2Sn Serializer Control Register (I2SSCTRL)                         | 28  |

|      | 3.2      | I2Sn Sample Rate Generator Register (I2SSRATE)                      | 30  |

|      | 3.3      | I2Sn Transmit Left Data 0 Register (I2STXLT0)                       | 31  |

|      | 3.4      | I2Sn Transmit Left Data 1 Register (I2STXLT1)                       | 31  |

|      | 3.5      | I2Sn Transmit Right Data 0 Register (I2STXRT0)                      | 32  |

|      | 3.6      | I2Sn Transmit Right Data 1 Register (I2STXRT1)                      |     |

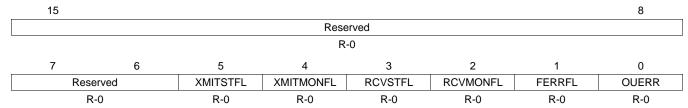

|      | 3.7      | I2Sn Interrupt Flag Register (I2SINTFL)                             | 33  |

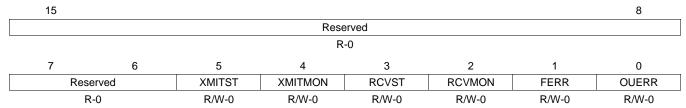

|      | 3.8      | I2Sn Interrupt Mask Register (I2SINTMASK)                           |     |

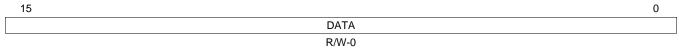

|      | 3.9      | I2Sn Receive Left Data 0 Register (I2SRXLT0)                        |     |

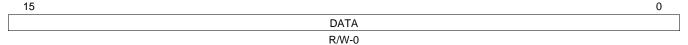

|      | 3.10     | I2Sn Receive Left Data 1 Register (I2SRXLT1)                        |     |

|      | 3.11     | I2Sn Receive Right Data 0 Register (I2SRXRT0)                       | 36  |

|      | 3.12     | I2Sn Receive Right Data 1 Register (I2SRXRT1)                       | 36  |

# **List of Figures**

| Functional Block Diagram                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inter-IC Sound Clock Control Diagram                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Block Diagram of I2S Interface to Audio/Voice Band Codec                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2S Frame Clock Timing Constraint in Slave Mode                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Typical Frame Clock Timing Specification                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Delaying I2S Frame Clock to Overcome Synchronization Problems                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Timing Diagram for Left-Justified Mode with Inverse Frame-Sync Polarity and One-Bit Delay | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

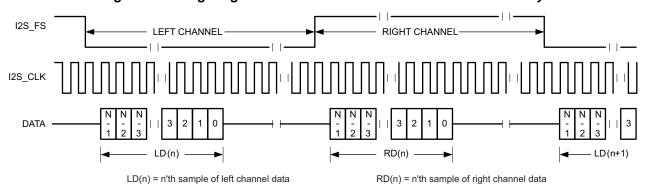

| Timing Diagram for I2S Mode                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Timing Diagram for I2S Mode with Inverse Bit-Clock Polarity                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

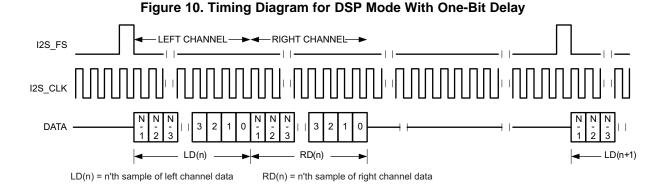

| Timing Diagram for DSP Mode With One-Bit Delay                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

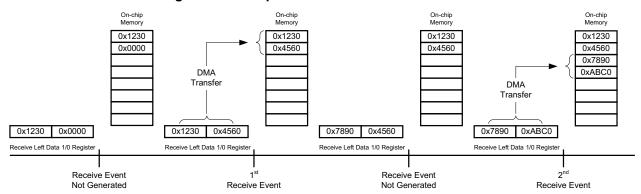

| Example of Unpacked 12-Bit Data Receive                                                   | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Example of Packed 12-Bit Data Receive                                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Serializer Control Register (I2SSCTRL)                                               | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

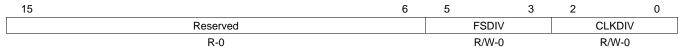

| I2Sn Sample Rate Generator Register (I2SSRATE)                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Transmit Left Data 0 Register (I2STXLT0)                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Transmit Left Data 1 Register (I2STXLT1)                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Transmit Right Data 0 Register (I2STXRT0)                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Transmit Right Data 1 Register (I2STXRT1)                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Interrupt Flag Register (I2SINTFL)                                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Interrupt Mask Register (I2SINTMASK)                                                 | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Receive Left Data 0 Register (I2SRXLT0)                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Receive Left Data 1 Register (I2SRXLT1)                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Receive Right Data 0 Register (I2SRXRT0)                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I2Sn Receive Right Data 1 Register (I2SRXRT1)                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                           | Functional Block Diagram Inter-IC Sound Clock Control Diagram Block Diagram of I2S Interface to Audio/Voice Band Codec I2S Frame Clock Timing Constraint in Slave Mode. Typical Frame Clock Timing Specification Delaying I2S Frame Clock to Overcome Synchronization Problems Timing Diagram for Left-Justified Mode with Inverse Frame-Sync Polarity and One-Bit Delay. Timing Diagram for I2S Mode Timing Diagram for I2S Mode with Inverse Bit-Clock Polarity Timing Diagram for DSP Mode With One-Bit Delay Example of Unpacked 12-Bit Data Receive.  Example of Packed 12-Bit Data Receive. I2Sn Serializer Control Register (I2SSCTRL) I2Sn Sample Rate Generator Register (I2SSRATE) I2Sn Transmit Left Data 0 Register (I2STXLT1) I2Sn Transmit Right Data 1 Register (I2STXRT1) I2Sn Transmit Right Data 1 Register (I2STXRT1) I2Sn Interrupt Flag Register (I2SINTFL) I2Sn Receive Left Data 0 Register (I2SRXLT0) I2Sn Receive Left Data 1 Register (I2SRXLT1) I2Sn Receive Left Data 1 Register (I2SRXLT1) I2Sn Receive Left Data 1 Register (I2SRXLT1) I2Sn Receive Right Data 0 Register (I2SRXLT1) I2Sn Receive Right Data 1 Register (I2SRXRT1) |

#### www.ti.com

# **List of Tables**

| 1  | I2S Signal Descriptions                                           | 13 |

|----|-------------------------------------------------------------------|----|

| 2  | Example of Sign Extension Behavior                                | 20 |

| 3  | PACK and Sign Extend Data Arrangement for 8 - Bit Word Length     | 20 |

| 4  | PACK and Sign Extend Data Arrangement for 10 - Bit Word Length    | 21 |

| 5  | PACK and Sign Extend Data Arrangement for 12 - Bit Word Length    | 21 |

| 6  | PACK and Sign Extend Data Arrangement for 14 - Bit Word Length    | 21 |

| 7  | PACK and Sign Extend Data Arrangement for 16 - Bit Word Length    | 22 |

| 8  | PACK and Sign Extend Data Arrangement for 18 - Bit Word Length    | 22 |

| 9  | PACK and Sign Extend Data Arrangement for 20 - Bit Word Length    | 22 |

| 10 | PACK and Sign Extend Data Arrangement for 24 - Bit Word Length    | 23 |

| 11 | PACK and Sign Extend Data Arrangement for 32 - Bit Word Length    | 23 |

| 12 | DMA Access to I2S                                                 | 24 |

| 13 | I2S0 Register Mapping Summary                                     | 26 |

| 14 | I2S1 Register Mapping Summary                                     | 26 |

| 15 | I2S2 Register Mapping Summary                                     | 26 |

| 16 | I2S3 Register Mapping Summary                                     | 27 |

| 17 | I2Sn Serializer Control Register (I2SSCTRL) Field Descriptions    | 28 |

| 18 | I2Sn Sample Rate Generator Register (I2SSRATE) Field Descriptions | 30 |

| 19 | I2Sn Transmit Left Data 0 Register (I2STXLT0) Field Descriptions  | 31 |

| 20 | I2Sn Transmit Left Data 1 Register (I2STXLT1) Field Descriptions  | 31 |

| 21 | I2Sn Transmit Right Data 0 Register (I2STXRT0) Field Descriptions | 32 |

| 22 | I2Sn Transmit Right Data 1 Register (I2STXRT1) Field Descriptions | 32 |

| 23 | I2Sn Interrupt Flag Register (I2SINTFL) Field Descriptions        | 33 |

| 24 | I2Sn Interrupt Mask Register (I2SINTMASK) Field Descriptions      | 34 |

| 25 | I2Sn Receive Left Data 0 Register (I2SRXLT0) Field Descriptions   | 35 |

| 26 | I2Sn Receive Left Data 1 Register (I2SRXLT1) Field Descriptions   | 35 |

| 27 | I2Sn Receive Right Data 0 Register (I2SRXRT0) Field Descriptions  | 36 |

| 28 | 12Sn Receive Right Data 1 Register (I2SRXRT1) Field Descriptions  | 36 |

# Read This First

#### **About This Manual**

This document describes the features and operation of Inter-IC Sound (I2S) Bus for the TMS320VC5505/5504 Digital Signal Processor (DSP). This structure assumes that a support model where only specific use cases are supported. Although the general architecture is described and the register functions are included, only the functions supported by TI are documented and supported.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320VC5505/5504 Digital Signal Processor (DSP). Copies of these documents are available on the internet at <a href="http://www.ti.com">http://www.ti.com</a>.

- <u>SWPU073</u> TMS320C55x 3.0 CPU Reference Guide. This manual describes the architecture, registers, and operation of the fixed-point TMS320C55x digital signal processor (DSP) CPU.

- <u>SPRU652</u> TMS320C55x DSP CPU Programmer's Reference Supplement. This document describes functional exceptions to the CPU behavior.

- SPRUFO0 TMS320VC5505/5504 Digital Signal Processor (DSP) Universal Serial Bus 2.0 (USB) User's Guide. This document describes the universal serial bus 2.0 (USB) in the TMS320VC5505/5504 Digital Signal Processor (DSP). The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices.

- SPRUFO1 TMS320VC5505/5504 Digital Signal Processor (DSP) Inter-Integrated Circuit (I2C)

Peripheral User's Guide. This document describes the inter-integrated circuit (I2C) peripheral in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The I2C peripheral provides an interface between the device and other devices compliant with Phillips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1 and connected by way of an I2C-bus. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUFO2 TMS320VC5505/5504 Digital Signal Processor (DSP) Timer/Watchdog Timer User's Guide. This document provides an overview of the three 32-bit timers in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The 32-bit timers of the device are software programmable timers that can be configured as general-purpose (GP) timers. Timer 2 can be configured as a GP, a Watchdog (WD), or both simultaneously.

- SPRUFO3 TMS320VC5505/5504 Digital Signal Processor (DSP) Serial Peripheral Interface (SPI) User's Guide. This document describes the serial peripheral interface (SPI) in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 32 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI supports multi-chip operation of up to four SPI slave devices. The SPI can operate as a master device only.

- SPRUFO4 TMS320VC5505/5504 Digital Signal Processor (DSP) General-Purpose Input/Output (GPIO) User's Guide. This document describes the general-purpose input/output (GPIO) on the TMS320VC5505/5504 digital signal processor (DSP). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of an internal register. When configured as an output you can write to an internal register to control the state driven on the output pin.

- SPRUFO5 TMS320VC5505/5504 Digital Signal Processor (DSP) Universal Asynchronous Receiver/Transmitter (UART) User's Guide. This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU.

- SPRUF07 TMS320VC5505/5504 Digital Signal Processor (DSP) Real-Time Clock (RTC) User's Guide. This document describes the operation of the Real-Time Clock (RTC) module in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The RTC also has the capability to wake-up the power management and apply power to the rest of the device through an alarm, periodic interrupt, or external WAKEUP signal.

- SPRUFO8 TMS320VC5505/5504 Digital Signal Processor (DSP) External Memory Interface (EMIF) User's Guide. This document describes the operation of the external memory interface (EMIF) in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The purpose of the EMIF is to provide a means to connect to a variety of external devices.

- SPRUFO9 TMS320VC5505/5504 Digital Signal Processor (DSP) Direct Memory Access (DMA)

Controller User's Guide. This document describes the features and operation of the DMA controller that is available on the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The DMA controller is used to move data among internal memory, external memory, and peripherals without intervention from the CPU and in the background of CPU operation.

- SPRUFP0 TMS320VC5505 Digital Signal Processor (DSP) System User's Guide. This document describes various aspects of the TMS320VC5505/5504 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUGL6 TMS320VC5504 Digital Signal Processor (DSP) System User's Guide. This document describes various aspects of the TMS320VC5505/5504 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUFP1 TMS320VC5505 Digital Signal Processor (DSP) Successive Approximation (SAR)

Analog to Digital Converter (ADC) User's Guide. This document provides an overview of the Successive Approximation (SAR) Analog to Digital Converter (ADC) on the TMS320VC5505/5504 Digital Signal Processor (DSP). The SAR is a 10-bit ADC using a switched capacitor architecture which converts an analog input signal to a digital value.

- SPRUFP3 TMS320VC5505 Digital Signal Processor (DSP) Liquid Crystal Display Controller (LCDC) User's Guide. This document describes the liquid crystal display controller (LCDC) in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. The LCD controller includes a LCD Interface Display Driver (LIDD) controller.

SPRUFP4 — TMS320VC5505/5504 Digital Signal Processor (DSP) Inter-IC Sound (I2S) Bus User's Guide. This document describes the features and operation of Inter-IC Sound (I2S) Bus in the TMS320VC5505/5504 Digital Signal Processor (DSP) device. This peripheral allows serial transfer of full duplex streaming data, usually streaming audio, between DSP and an external I2S peripheral device such as an audio codec.

# Inter-IC Sound (I2S) Bus

#### 1 Introduction

This document describes the features and operation of Inter-IC Sound (I2S) Bus. This peripheral allows serial transfer of full duplex streaming data, usually streaming audio, between DSP and an external I2S peripheral such as an audio codec.

#### 1.1 Purpose of the Peripheral

The I2S bus is used as an interface for full-duplex serial ports such as those found in audio or voice-band analog to digital converters (ADC) to acquire audio signals or digital-to analog converters (DAC) to drive speakers and headphones.

#### 1.2 Features

The I2S bus supports the following features:

- Full-duplex (transmit and receive) communication.

- Double buffered data registers that allow for continuous data stream.

- · Most significant bit (MSB) first data transfers.

- I2S/Left-justified and DSP serial data communication formats with a data delay of 1 or 2 bits.

- Data word-lengths of 8, 10, 12, 14, 16, 18, 20, 24, or 32 bits.

- Ability to sign-extend received data samples for easy use in signal processing algorithms.

- Ability to pack multiple data words into CPU or DMA accessible data registers to reduce interrupts for more efficient operation.

- Programmable polarity for both frame synchronization and bit-serial clocks.

- Digital loopback of data from transmit to receive data register(s) for application code debug.

- Stereo (in I2S/Left-justified or DSP data formats) or mono (in DSP data format) mode.

- Programmable divider for serial data clock (bit-clock) generation when I2S bus is used as a master device.

- Programmable divider for frame sync clock generation when I2S bus is used as the master device.

- Detection of over-run, under-run, and frame-synchronization error conditions.

The DSP includes four independent I2S modules .

#### 1.3 Functional Block Diagram

Figure 1 is a functional block diagram of the I2S bus illustrating the different control, data transfer, clock generation and event management blocks and their interactions. The I2S peripheral has a set of control and data registers which the CPU can access through its I/O space. The DMA can also make 32-bit accesses to receive and transmit data registers for efficient data transfer.

The bus is configured by writing to the I2S*n* Serializer Control Register (I2SSCTRL) bit fields. The bit fields in this register determine the communication protocol over the I2S bus and the arrangement of data in the data registers.

Introduction www.ti.com

Figure 1. Functional Block Diagram

Data on the I2S*n*\_RX pin is shifted serially into the Receive Shift Register and then copied into the Receive Buffer Register. The data is then copied to I2S*n* Receive Left/Right Data *n* Registers. For each channel (left and right), these registers can be accessed as two 16-bit registers by the CPU or as a 32-bit register by the DMA. Similarly, the I2S*n* Transmit Left/Right Data *n* Registers store the data to be transmitted out of the I2S peripheral. The CPU or DMA writes the transmit data to the I2S*n* Transmit Left/Right Data *n* Registers which is then copied to the Transmit Shift Register via the Transmit Buffer Register and shifted serially out to I2S*n*\_DX pin. This structure allows internal data movement and external data communications simultaneously. Data handling and movement is discussed in further detail in later sections.

The control block consists of internal clock generation, frame synchronization signal generation, and their control. The I2Sn Sample Rate Generator Register (I2SSRATE) contains fields to configure the frame-synchronization and bit-clock dividers to drive the I2Sn\_FS and I2Sn\_CLK clocks when the I2S peripheral is configured as a master device. When configured as a slave device, the internal clock generation logic is disabled and frame synchronization is performed on the clocks generated by the external master I2S device (see Section 2.2). The polarities of the bit-clock and the frame-synchronization can be set by the CLKPOL bit and FSPOL bit respectively in the I2SSCTRL register. The I2S supports a data delay of 1 bit or 2 bits as configured by the DATADLY bit in the I2SSCTRL register.

The I2S peripheral can be configured to interrupt the CPU by writing to the I2Sn Interrupt Mask Register (I2SINTMASK). When interrupts are enabled, the event-generation block posts a transmit interrupt when transmit data registers are empty and a receive interrupt when receive data registers are full. The corresponding flag is set in the I2Sn Interrupt Flag Register (I2SINTFL). In addition to data transaction interrupts, error events are also flagged in this register. Error events are not connected to interrupts on the CPU. The I2S also sends synchronization events corresponding to the transmit and receive events to the DMA controller associated with the I2S module. The I2SINTMASK register has no effect on DMA sync signal generation events. (See Section 2.10, Section 2.11, Section 3.7 and Section 3.8)

#### 1.4 Industry Standard(s) Compliance

This Inter-IC Sound (I2S) Bus is compliant to industry I2S Bus Standard.

www.ti.com Architecture

#### 2 Architecture

#### 2.1 Clock Control

As shown in Figure 2, the I2S bus is driven by the system clock. Unused I2S modules can be independently idled (clock-gated) via the peripheral clock gating configuration register 1 (PCGCR 1) for power dissipation savings. Each I2S bus should be brought out of idle before being programmed. For more details, see Section 2.12.

Figure 2. Inter-IC Sound Clock Control Diagram

If the I2S bus is configured as the master device, the DSP clock generator may need to be programmed to achieve an appropriate system clock so that the I2S clock dividers can generate the required clock rates. For more information on the DSP clock generation options, see the *TMS320VC5505/5504 DSP System Guide* (SPRUFP0).

#### 2.2 I2S Clock Generator

The I2Sn Sample Rate Generator Register (I2SSRATE) controls the clock generation logic in the I2S bus. In slave mode (MODE = 0 in I2SSCTRL - see Section 3.1), the required clock signals (I2Sn\_CLK and I2Sn\_FS) are generated by the external master I2S device and the internal I2S clock generator is not used. Configuring the I2SSRATE register has no effect in this mode. However, when configured as a master device (MODE = 1), the I2S module generates these clocks by dividing the system clock by a value calculated from the CLKDIV and FSDIV fields programmed in the I2SSRATE register (see Section 3.2). The clocks can be calculated as shown below:

```

I2Sn_CLK = SystemClock / (2^{CLKDIV+1})

I2Sn_FS = I2Sn_CLK / (2^{FSDIV+3})

```

Architecture www.ti.com

I2Sn CLK is the bit-clock that determines the rate at which data bits are transferred on the serial I2S bus. I2Sn FS is referred to as the frame-sync clock or word clock and is the rate at which a data word is transferred to and/or from the I2S module. This can also be seen as the frequency at which data (audio from a microphone for example) is sampled by an analog-to-digital converter (ADC) or an audio codec.

The clock divide-by value, 2<sup>FSDIV+3</sup>, that derives the frame-sync clock from the bit-clock (as shown above), gives the number of data bits (bit-clocks) in one cycle of the frame-sync clock. Since one cycle of the frame-sync clock should accommodate two data words (one left and one right channel data word) for stereo operation and one data word (one left channel only) for mono operation, the following restrictions apply while choosing an appropriate setting for FSDIV:

```

2<sup>FSDIV+3</sup> ≥ 2 * WDLNGTH (for stereo mode)

```

$2^{\text{FSDIV}+3} \ge \text{WDLNGTH}$  (for mono mode)

For example, to achieve a particular sampling rate of I2Sn\_FS = 48000 Hz with stereo operation of data length of 16 bits, the value of the FSDIV bit in the I2SSRATE register should be first chosen such that:

$$2^{\text{FSDIV+3}} \ge 2*16 = 32.$$

If we choose

FSDIV = 2 (010 binary)

the resultant I2Sn CLK can be calculated as:

$$12Sn_{CLK} = 12Sn_{FS} * (2^{FSDIV+3}) = 48000 * 32 = 1.536 \text{ MHz}.$$

Based on application requirements, if the DSP needs to be run at a minimum system clock or DSP clock of 45 MHz, the CLKDIV bit in the I2SSRATE register can be chosen such that,

SystemClock

$$\geq$$

I2Sn CLK \* 2<sup>CLKDIV+1</sup>  $\geq$  45 MHz

Hence we should choose:

CLKDIV = 4 (100 binary)

Which will give us,

As a result, the DSP clock generator should be configured to generate the required clock of 49.15 MHz. Due to limitations/restrictions of the DSP clock generator, it may not be possible to generate the exact system clock required, in which case I2Sn\_FS will deviate from the expected value. While it is sufficient to choose a setting for FSDIV such that 2FSDIV+3 is equal to the required number of data bits per frame-sync clock (as shown in example above), it may sometimes be necessary to choose a higher setting so that a faster bit-clock can be achieved. For a given system clock, this expedites transfer of data bits of the programmed word length on the I2S bus. As a result, the interrupts/events occur earlier in the frame-sync cycle, providing more time for the CPU/DMA to service the interrupt/event before the next interrupt/event. This is a particularly useful technique when the I2S uses CPU to handle data transfers to/from its data registers.

NOTE: 12S peripheral clock generator should only be configured if the I2S is configured as a master device. When the I2S is configured as the slave, the external master device supplies the required clocks.

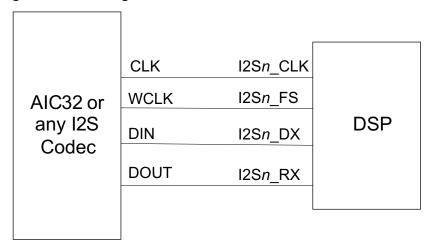

#### 2.3 Signal and Pin Descriptions

The I2S bus is a four-wire interface with two clock pins, bit-serial clock (I2Sn CLK) and frame-synchronization or word clock (I2Sn FS), and two data pins, serial data transmit (I2Sn DX) and serial data receive (I2Sn RX), for data communication as shown in Figure 1. The I2Sn CLK and I2Sn FS pins are bi-directional based on whether the I2S peripheral is configured as a master or slave device.

www.ti.com Architecture

|                  | Table 1. I2S Signal Descriptions |                      |  |  |  |  |  |  |  |

|------------------|----------------------------------|----------------------|--|--|--|--|--|--|--|

| Name             | Signal                           | Description          |  |  |  |  |  |  |  |

| I2Sn_CLK         | INPUT /OUTPUT                    | I2S Clock            |  |  |  |  |  |  |  |

| I2S <i>n</i> _FS | INPUT /OUTPUT                    | I2S Frame Sync Clock |  |  |  |  |  |  |  |

| I2S <i>n_</i> DX | OUTPUT                           | I2S Data Transmit    |  |  |  |  |  |  |  |

| 12S <i>n</i> _RX | INPUT                            | I2S Data Receive     |  |  |  |  |  |  |  |

The diagram below is a typical connection between I2S interface to an audio or voice-band Codec.

Figure 3. Block Diagram of I2S Interface to Audio/Voice Band Codec

#### 2.3.1 Pin Multiplexing

Depending on the I2S bus being used, the DSP should be configured to route those I2S signals to the multiplexed Serial Port 0, Serial Port 1, or Parallel Port pins by writing to the External Bus Selection Register (EBSR). For more information on pin multiplexing, see the *TMS320VC5505/5504 DSP System Guide* (SPRUFP0).

**NOTE:** Configuring the EBSR to route I2S0 or I2S1 signals to Serial Port0 or Serial Port1 respectively also routes those I2S interrupts to the CPU (see Section 2.10).

#### 2.4 Frame Clock Timing Requirement in Slave Mode

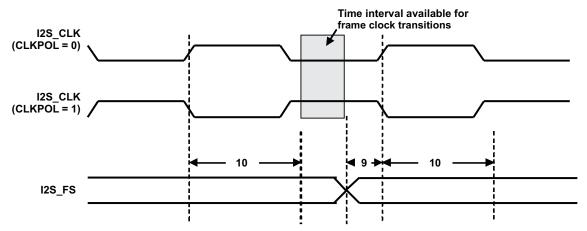

When configured as the slave, frame clock (I2S\_FS) is required to be latched on both edges of the bit clock (I2S\_CLK), which are generated by the external master device. This imposes an additional constraint on the timing of I2S\_FS as illustrated in Figure 4. The generated frame clock should meet the specified setup and hold requirements with respect to the sampling edge of the generated bit clock. For actual timing requirements, see the I2S section of the TMS320C55xx data sheet. These constraints imply that the frame clock transitions should occur in the time window as indicated by the shaded region in the figure.

Architecture www.ti.com

| No. | Parameter                 | Description                                                       |

|-----|---------------------------|-------------------------------------------------------------------|

| 9   | t <sub>su(FSV-CLKH)</sub> | Minimum setup time, I2S_FS valid before I2S_CLK high (CLKPOL = 0) |

|     | t <sub>su(FSV-CLKL)</sub> | Minimum setup time, I2S_FS valid before I2S_CLK low (CLKPOL = 1)  |

| 10  | t <sub>h(CLKH-FSV)</sub>  | Minimum hold time, I2S_CLK high to I2S_FS (CLKPOL = 0)            |

|     | t <sub>h(CLKL-FSV)</sub>  | Minimum hold time, I2S_CLK low to I2S_FS (CLKPOL = 1)             |

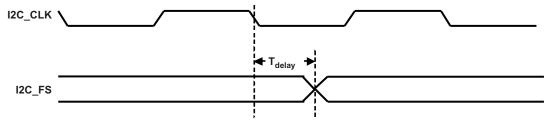

Devices (ADCs, DACS and audio/voice-band codecs) that interface to the I2S module usually only specify a maximum delay for the frame clock transition from the falling edge of the bit clock in master mode as indicated by parameter  $T_{delay}$  in Figure 5.

Figure 5. Typical Frame Clock Timing Specification

Architecture www.ti.com

Synchronization issues may occur if the frame clock transitions close to the falling edge of the bit clock violating the previously described hold requirement resulting in incorrect data transfer. In these circumstances, the frame clock should be delayed with respect to the bit clock by introducing a time delay in its signal path as shown in Figure 6. The RC circuit delays the frame clock by a value given by the relation Trc = RC.

12Sn CLK CLK **WDCLK** 12Sn FS External Slave Master 125 125 **Device** Port I2Sn\_DX DIN on **DSP DOUT** I2Sn RX R

Figure 6. Delaying I2S Frame Clock to Overcome Synchronization Problems

NOTE: Signal should be probed as close to the TMS320C55xx device pins as possible for better results.

#### 2.5 **Protocol Description**

The I2S bus communicates with a corresponding external I2S peripheral in a series of 1's and 0's. This series has a hierarchical organization that can be described in terms of bits, words, and frames.

A bit is the smallest entity in the serial stream. A "1" is represented by logic high on the data pin for the entire duration of a single bit clock. A "0" is represented by a logic low for the entire duration of a single bit clock.

A word is a group of bits that make up the data being transmitted or received. The length of the word is programmed by the user in the WDLNGTH field in the I2Sn Serializer Control Register (I2SSCTRL).

A frame is a group of words (usually one - mono or two - stereo) that make up the data being transmitted or received. The number of bit clocks per frame and the frame rate (sampling frequency) is programmed by the user in the I2Sn Sample Rate Generator Register (I2SSRATE).

I2S supports two serial data communication formats with external I2S devices: I2S/Left-justified format and DSP format. The I2S format is a specialized case of the more general left-justified data format. In DSP mode, the frame is marked between two consecutive pulses of the frame sync signal. On I2S, the frame is marked by a whole clock cycle of the frame sync signal with 50% duty cycle.

#### 2.5.1 **I2S/Left-Justified Format**

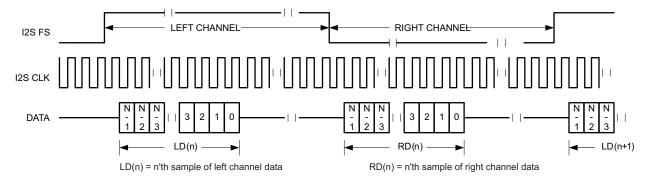

In the left-justified format, the frame-synchronization or word clock has a 50% duty cycle indicating dual channel data fields with left channel data transferred during one half of the cycle and right channel data transferred during the other half. The MSB-first data is transferred serially, left justified in its own field with appropriate bit delays.

Architecture www.ti.com

As shown in Figure 7, the typical I2S format utilizes left-justified format with a data delay of one bit and low frame synchronization pulse for left channel data and high pulse for right channel data. Serial data sent by the transmitter may be synchronized with either the trailing or the leading edge of serial clock I2Sn\_CLK. However, the serial data must be latched by the receiver on the leading edge of I2Sn\_CLK. In this format, the MSB of the left channel is valid on the second leading edge of the bit-clock, I2Sn\_CLK after the trailing edge of the frame-synchronization clock, I2Sn\_FS. Similarly the MSB of the right channel is valid on the second leading edge of I2Sn\_FS.

Figure 7. Timing Diagram for Left-Justified Mode with Inverse Frame-Sync Polarity and One-Bit Delay

Figure 8. Timing Diagram for I2S Mode

Figure 9. Timing Diagram for I2S Mode with Inverse Bit-Clock Polarity

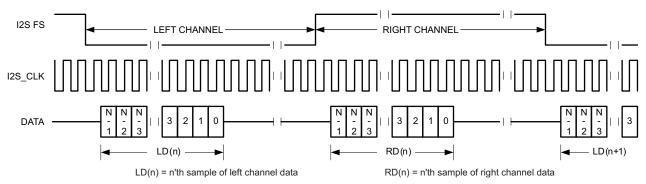

#### 2.5.2 DSP Format

In DSP format, the trailing edge of the frame-synchronization pulse, I2S $n_F$ S, starts the data transfer with the left channel data first and immediately followed by the right channel data. Each data bit is valid on the trailing edge of the bit-clock, I2S $n_C$ CLK. The first data sample can be delayed by 1 bit or 2 bits after the trailing edge of I2S $n_F$ S. With one bit delay, the MSB coincides with the trailing edge of I2S $n_F$ S. With two bit delay, the MSB follows the trailing edge of I2S $n_F$ S after one I2S $n_C$ CLK. Figure 10 illustrates DSP format operation with a one-bit data delay.

Architecture www.ti.com

#### NOTE:

- The I2Sn\_DX and I2Sn\_RX pins are tri-stated during unused bit clocks in a frame.

- In I2S/Left-justified format:

- Mono operation is not supported due to the 50% duty cycle restriction on the frame-synchronization clock.

- The number of I2Sn\_CLKs should be greater than or equal to twice the configured data word-length.

- In DSP format:

- The number of I2Sn\_CLKs should be greater than or equal to twice the configured data word-length for stereo operation.

- The number of I2Sn\_CLKs should be greater than or equal to the configured data word-length for mono operation.

#### 2.6 I2S Data Transfer and Control Behavior

When the I2S module is enabled, MSB-first data transfer starts when the appropriate level is detected on the frame-sync clock. Data in the Transmit Shift Register is shifted out serially to the I2Sn\_DX while data bits are shifted in serially from the I2Sn\_RX pin to the Receive Shift Register on the falling or leading edge of the bit-clock as programmed in the CLKPOL field of the I2SSCTRL. Data for the left channel is transferred first followed by the right channel data.

The module generates the transmit interrupt/event (the transmit and receive interrupts should be enabled in the I2SINTMASK register if CPU transfers are desired; if DMA is used to transfer data these interrupts should be disabled - see Sections 2.8 and 2.9) to indicate that the Transmit Left/Right Data1/0 registers should be filled with valid data for the next set of transfers. The CPU or DMA servicing this interrupt/event writes the next valid data to the above mentioned registers. Failure to do so before the next frame-sync cycle will result in the OUERROR being flagged in the I2SINTFL register (assuming that error detection has been enabled in the I2SINTMASK register). At the next frame-sync cycle, data from the Transmit Left/Right Data1/0 registers into the Transmit Buffer register and then to the Transmit Shift register.

NOTE: Data should be written into the Transmit Left/Right Data1/0 registers only on a transmit interrupt. Data can not be preloaded into these registers before enabling the I2S module or before receiving the first transmit interrupt.

When the required number of data words is received in the Receive Shift register (one for mono or two for stereo), the data is moved into the Receive Buffer register and ultimately into the Receive Left/Right Data1/0 registers. A receive interrupt/event is generated at this point. The CPU or DMA servicing this interrupt reads the register into memory. Failure to do so before the next frame-sync cycle will result in the OUERROR being flagged in the I2SINTFL register (assuming that error detection has been enabled in the I2SINTMASK register).

Architecture www.ti.com

Transmit and receive interrupts/events are continuously generated after every transfer from the transmit data registers to the transmit buffer register and from the receive buffer register to the receive data registers respectively. If packed mode is enabled (PACK = 1 in I2SSCTRL), interrupts/events are generated after all the required number of data words have been transmitted/received (see Section 2.8).

#### 2.7 I2S Data Transfer Latency

Due to the buffered nature of the I2S module, there exists some latency in the transmit and receive paths (from the Transmit Data registers to the I2S\_DX pin and I2S\_RX pin to Receive Data registers) which is dependent on the desired configuration of the module. The latency may not be of consequence when the I2S module in its intended scope of a streaming audio peripheral. However, it is documented here in the interests of completeness. It will also help explain observed loopback data (LOOPBACK=1 in I2SSCTRL) as the latency is also present in loopback mode.

#### 2.7.1 Transmit Path Latency

After the I2S is enabled, the first valid data sample on the I2Sn\_DX pin will appear after:

- Five frame-sync clocks if PACK mode is used (PACK=1 in I2SSCTRL) or,

- Three frame-sync clocks if PACK mode is not used (PACK=0 in I2SSCTRL)

Hence there is a latency of three or five samples (for each channel) before the first data sample that is written to the Transmit Left/Right Data 1/0 registers after the first transmit interrupt/event. During this time, the I2S transmits random data bits which should be discarded or ignored.

#### 2.7.2 Receive Path Latency

After the I2S is enabled, the receive path starts receiving data after:

- 1 or 2 frame-sync clocks for 8-, 18-, 20-, 24-, or 32-bit data depending on other configuration

- 1, 2 or 3 frame-sync clocks for 10-, 12-, 14-, or 16-bit data depending on other configuration

#### 2.7.3 Loopback Path Latency

The internal loopback mode (LOOPBACK=1 in I2SSCTRL) can be used as a debug tool to verify the user's program to service I2S interrupts/events. This is different from an external loopback which would require the I2Sn\_DX pin to be connected to the I2Sn\_RX pin. In the internal loopback mode, data from the Transmit Shift register is directly routed to the Receive Shift register, changing the data latency as given below:

- If pack mode is used (PACK=1 in I2SSCTRL)

- Ignore the first 6 samples received for 8-bit data and FSDIV=000 in I2SSRATE

- Ignore the first 5 samples received for 8-bit data and FSDIV > 000 in I2SSRATE

- Ignore the first 6 samples received for 10-, 12-, 14- or 16-bit data

- If pack mode is not used (PACK=0 in I2SSCTRL), ignore the first 2 samples received.

#### 2.8 Data Packing and Sign Extension Options

The I2S bus supports the use of packed (multiple) and/or sign extended data words in its data registers to reduce software overheads in servicing interrupts for every data sample and for ease of data handling in software algorithms.

**NOTE:** Using the Pack or Sign Extend options does not affect transmission of data samples over the serial I2S bus; it only affects how data words are arranged in the Receive and Transmit Data Registers.

#### 2.8.1 Data Pack Mode

Setting the PACK bit field in the I2SSCTRL register enables data packing in the 32-bit I2S data registers for word-lengths of 8, 10, 12, 14 and 16 bits. This mode can be used in the following scenario:

www.ti.com Architecture

- Using DMA to transfer data samples: to make better use of data buffers.

- Using CPU to transfer data samples: to reduce interrupt overheads.

During the receive operation, the I2S bus puts successive data samples into the I2Sn Receive Left/Right Data n Registers (Data 1 register first, Data 0 register next) before generating the interrupt/event. The transmit data is expected in a similar format in the I2Sn Transmit Left/Right Data n Registers. Four 8-bit data samples or two 10, 12, 14 or 16-bit data samples can be packed in the data registers, as shown in Section 2.8.3.

The advantages of using the PACK mode can be seen as given below:

- Reduces the number of I2S interrupts/events, which results in reducing interrupt overheads and the better use of bus bandwidth.

- Efficient use of internal/on-chip memory if DMA is used for transferring data between I2S and main memory. Since the DMA transfers a double-word (all 32-bits of the I2Sn Transfer Left/Right Data n Registers) during each transaction, using packed I2Sn Receive/Transmit Left/Right Data n Registers results in efficient transfer of data samples. Hence, for a given number of samples, size of data buffers is reduced by a factor of two for 10-, 12-, 14- or 16-bit word length or by a factor of four for 8-bit word length.

Figure 11 and Figure 12 illustrate packed and unpacked data receive behavior for mono transmission of four 12-bit data samples (sign extension is not enabled). When pack mode is not used, the I2S module stores 12-bit data left-justified in MSW (with trailing zeros) and generates DMA event resulting in zeros stored in alternate memory locations. When pack mode is used, the module packs 12-bit data left-justified in MSW first and then LSW (with trailing zeros) and generates DMA event once every two transfers resulting in better utilization of memory.

On-chip On-chip 0x1230 0x1230 0x1230 0x1230 0x0000 0x0000 0x0000 0x0000 0x4560 0x4560 0x4560 DMA 0x0000 0x0000 0x0000 DMA Transfer Transfer 0x7890 DMA 0x7890 DMA Transfer 0x0000 0x0000 Transfer 0xABC0 0x0000 0xABC0 0x0000 0x1230 0x0000 0x4560 0x0000 0x7890 0x0000 Receive Event Receive Left Data 1/0 Regis Receive Left Data 1/0 Reg Receive Left Data 1/0 Registe Receive Left Data 1/0 Regi  $2^{nd}$ Receive Event Receive Event Receive Event Receive Event

Figure 11. Example of Unpacked 12-Bit Data Receive

Figure 12. Example of Packed 12-Bit Data Receive

Architecture www.ti.com

#### 2.8.2 Data Sign Extend Mode

The I2S peripherals can be configured to work with sign extended data samples for ease of use in commonly used S16 or S32 data representations in signal processing algorithms. Data words of lengths 8-, 10-, 12- or 14-bits are sign-extended (right-justified) to 16 bits (8-bit data cannot be sign extended in packed mode as four samples are packed into the 32-bit data registers). Data of word lengths 18-, 20- or 24-bits are sign extended (right-justified) to 32 bits.

The choice of PACK, SIGN\_EXT and WDLNGTH bit options in the I2SSCTRL register affects the arrangement of received data in the I2S*n* Receive Left/Right Data *n* Registers. Similarly, the I2S peripheral expects data to be arranged in a similar fashion in the I2S*n* Transmit Left/Right Data *n* Registers for the correct data value to be shifted out to the I2S*n*\_DX pin.

Table 2 illustrates sign extension behavior with an example.

Table 2. Example of Sign Extension Behavior

|             |                 |                    | jister With<br>_EXT=0 | Data Register With<br>SIGN_EXT=1 |                    |  |

|-------------|-----------------|--------------------|-----------------------|----------------------------------|--------------------|--|

| Word Length | Data on I2S Bus | Data 1<br>Register | Data 0<br>Register    | Data 1<br>Register               | Data 0<br>Register |  |

| 8           | 0xA1            | 0xA100             | 0x0000                | 0xFFA1                           | 0x0000             |  |

| 10          | 0x2B7           | 0xAD80             | 0x0000                | 0xFEB7                           | 0x0000             |  |

| 12          | 0x6AA           | 0x6AA0             | 0x0000                | 0x06AA                           | 0x0000             |  |

| 14          | 0x3999          | 0xE666             | 0x0000                | 0xF999                           | 0x0000             |  |

| 16          | 0x29CC          | 0x29CC             | 0x0000                | 0x29CC                           | 0x0000             |  |

| 18          | 0x19EFA         | 0x67BE             | 0x8000                | 0x0001                           | 0x9EFA             |  |

| 20          | 0x7ADE1         | 0x7ADE             | 0x1000                | 0x0007                           | 0xADE1             |  |

| 24          | 0x98A311        | 0x98A3             | 0x1100                | 0xFF98                           | 0xA311             |  |

| 32          | 0xD16AEE09      | 0xD16A             | 0xEE09                | 0xD16A                           | 0xEE09             |  |

#### 2.8.3 PACK and Sign Extend Data Arrangement for Various Word Lengths

The tables in this section describe sign extended and packed data arrangement for each configurable word length. Data samples are indicated by x[0], x[1], x[2] and x[3] in increasing temporal order (x[3] is the most recent sample).

#### 2.8.3.1 8 - Bit Word Length

Table 3. PACK and Sign Extend Data Arrangement for 8 - Bit Word Length

|              |                   |     | nsmit Left or<br>Register |   |    | I2S Receive/Ti<br>Right Data | ansmit Left or<br>0 Register | • |

|--------------|-------------------|-----|---------------------------|---|----|------------------------------|------------------------------|---|

| PACK = 0     | 15                | 8 7 | 7                         | 0 | 15 |                              |                              | 0 |

| SIGN_EXT = 0 | x(0)              |     | 0                         |   |    | (                            | )                            |   |

| PACK = 0     | 15                | 8 7 | 7                         | 0 | 15 |                              |                              | 0 |

| SIGN_EXT = 1 | Sign Bits (Bit #7 | 7)  | x(0)                      |   |    | (                            | )                            |   |

| PACK = 1     | 15                | 8 7 | 7                         | 0 | 15 | 8                            | 7                            | 0 |

| SIGN_EXT = 0 | x(0)              |     | x(1)                      |   |    | x(2)                         | x(3)                         |   |

| PACK = 1     | 15                | 8 7 | 7                         | 0 | 15 | 8                            | 7                            |   |

| SIGN_EXT = 1 | x(0)              |     | x(1)                      |   |    | x(2)                         | x(3)                         |   |

Architecture www.ti.com

#### 10 - Bit Word Length 2.8.3.2

Table 4. PACK and Sign Extend Data Arrangement for 10 - Bit Word Length

|              |                  | eive/Tran<br>t Data 1 l | smit Left or<br>Register |   |      | I2S Receive/Tr<br>Right Data |   |      |

|--------------|------------------|-------------------------|--------------------------|---|------|------------------------------|---|------|

| PACK = 0     | 15               | 6 5                     |                          | 0 | 15   |                              |   |      |

| SIGN_EXT = 0 | x(0)             |                         | 0                        |   |      | (                            | ) |      |

| PACK = 0     | 15               | 10 9                    |                          | 0 | 15   |                              |   |      |

| SIGN_EXT = 1 | Sign Bits (Bit # | 9)                      | x(0)                     |   |      | (                            | ) |      |

| PACK = 1     | 15               | 6 5                     |                          | 0 | 15   | 6                            | 5 |      |

| SIGN_EXT = 0 | x(0)             |                         | 0                        |   |      | x(1)                         |   | 0    |

| PACK = 1     | 15               | 10 9                    |                          | 0 | 15   | 10                           | 9 |      |

| SIGN_EXT = 1 | Sign Bits (Bit # | 9)                      | x(0)                     |   | Sign | Bits (Bit #9)                |   | x(1) |

#### 2.8.3.3 12 - Bit Word Length

Table 5. PACK and Sign Extend Data Arrangement for 12 - Bit Word Length

|              | li       | 2S Receive/Tr<br>Right Data |    |      |   |    |                     |    | ansmit Left or<br>0 Register |   |

|--------------|----------|-----------------------------|----|------|---|----|---------------------|----|------------------------------|---|

| PACK = 0     | 15       | 4                           | 3  |      | 0 | 15 |                     |    |                              | 0 |

| SIGN_EXT = 0 | >        | ĸ(0)                        |    | 0    |   |    |                     | 0  |                              |   |

| PACK = 0     | 15       | 12                          | 11 |      | 0 | 15 |                     |    |                              | 0 |

| SIGN_EXT = 1 | Sign Bit | s (Bit #11)                 |    | x(0) |   |    |                     | 0  |                              |   |

| PACK = 1     | 15       | 4                           | 3  |      | 0 | 15 |                     | 4  | 3                            | 0 |

| SIGN_EXT = 0 | >        | ĸ(0)                        |    | 0    |   |    | x(1)                |    | 0                            |   |