# TMS320C5504 DSP System

# **User's Guide**

Literature Number: SPRUGH6C November 2010-Revised May 2014

# **Contents**

| Pref | ace      |         |                                                           | 7  |

|------|----------|---------|-----------------------------------------------------------|----|

| 1    | Syste    | em Con  | itrol                                                     | 10 |

|      | 1.1      | Introdu | Iction                                                    | 11 |

|      |          | 1.1.1   | Block Diagram                                             | 12 |

|      |          | 1.1.2   | CPU Core                                                  | 12 |

|      |          | 1.1.3   | Power Management                                          | 12 |

|      |          | 1.1.4   | Peripherals                                               | 13 |

|      | 1.2      | System  | n Memory                                                  | 13 |

|      |          | 1.2.1   | Program/Data Memory Map                                   | 14 |

|      |          | 1.2.2   | I/O Memory Map                                            | 18 |

|      | 1.3      | Device  | Clocking                                                  | 19 |

|      |          | 1.3.1   | Overview                                                  | 19 |

|      |          | 1.3.2   | Clock Domains                                             | 20 |

|      | 1.4      | System  |                                                           | 21 |

|      |          | 1.4.1   | Overview                                                  | 21 |

|      |          | 1.4.2   | Functional Description                                    | 22 |

|      |          | 1.4.3   | •                                                         | 24 |

|      |          | 1.4.4   | Clock Generator Registers                                 | 28 |

|      | 1.5      | Power   | Management                                                | 33 |

|      |          | 1.5.1   | Overview                                                  | 33 |

|      |          | 1.5.2   | Power Domains                                             | 33 |

|      |          | 1.5.3   | Clock Management                                          | 34 |

|      |          | 1.5.4   | Static Power Management                                   | 46 |

|      |          | 1.5.5   |                                                           |    |

|      | 1.6      | Interru | pts                                                       | 55 |

|      |          | 1.6.1   | IFR and IER Registers                                     | 55 |

|      |          | 1.6.2   | Interrupt Timing                                          | 57 |

|      |          | 1.6.3   | Timer Interrupt Aggregation Flag Register (TIAFR) [1C14h] | 58 |

|      |          | 1.6.4   | GPIO Interrupt Enable and Aggregation Flag Registers      |    |

|      |          | 1.6.5   | DMA Interrupt Enable and Aggregation Flag Registers       |    |

|      | 1.7      | System  |                                                           | 59 |

|      |          | 1.7.1   | -                                                         | 59 |

|      |          | 1.7.2   | Device Identification                                     | 59 |

|      |          | 1.7.3   | Device Configuration                                      | 63 |

|      |          | 1.7.4   | DMA Controller Configuration                              | 71 |

|      |          | 1.7.5   | Peripheral Reset                                          | 75 |

|      |          | 1.7.6   | EMIF and USB Byte Access                                  |    |

|      |          | 1.7.7   | EMIF Clock Divider Register (ECDR) [1C26h]                |    |

| Rev  | ision Hi | istorv  |                                                           |    |

|      |          | -       |                                                           |    |

# List of Figures

| 1-1.                                                                                                                                | Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2.                                                                                                                                | DSP Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                                                                                                                                             |

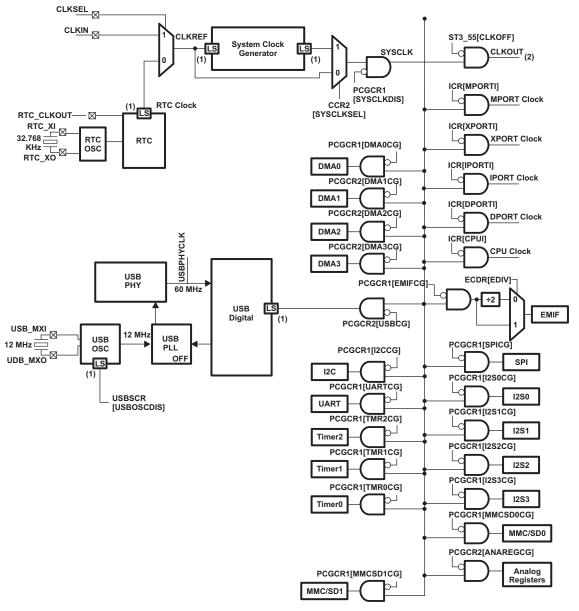

| 1-3.                                                                                                                                | DSP Clocking Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                                                                                                                                             |

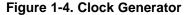

| 1-4.                                                                                                                                | Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                                                                                             |

| 1-5.                                                                                                                                | CLKOUT Control Source Select Register (CCSSR) [1C24h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                                                                                                                                             |

| 1-6.                                                                                                                                | Clock Generator Control Register 1 (CGCR1) [1C20h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                                                                             |

| 1-7.                                                                                                                                | Clock Generator Control Register 2 (CGCR2) [1C21h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                                                                             |

| 1-8.                                                                                                                                | Clock Generator Control Register 3 (CGCR3) [1C22h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                |

| 1-9.                                                                                                                                | Clock Generator Control Register 4 (CGCR4) [1C23h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                                                                                                             |

| 1-10.                                                                                                                               | Clock Configuration Register 1 (CCR1) [1C1Eh]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                                                                                                                             |

| 1-11.                                                                                                                               | Clock Configuration Register 2 (CCR2) [1C1Fh]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                |

| 1-12.                                                                                                                               | Idle Configuration Register (ICR) [0001h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                                                                                                                                             |

| 1-13.                                                                                                                               | Idle Status Register (ISTR) [0002h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                                                                                                                                                                             |

| 1-14.                                                                                                                               | Peripheral Clock Gating Configuration Register 1 (PCGCR1) [1C02h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                |

| 1-15.                                                                                                                               | Peripheral Clock Gating Configuration Register 2 (PCGCR2) [1C03h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                                                                                                                             |

| 1-16.                                                                                                                               | Peripheral Clock Stop Request/Acknowledge Register (CLKSTOP) [1C3Ah]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                                                                                                                                             |

| 1-17.                                                                                                                               | USB System Control Register (USBSCR) [1C32h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                                                                                                                             |

| 1-18.                                                                                                                               | RTC Power Management Register (RTCPMGT) [1930h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

| 1-19.                                                                                                                               | RTC Interrupt Flag Register (RTCINTFL) [1920h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                                                                                                                                                             |

| 1-20.                                                                                                                               | RAM Sleep Mode Control Register1 [0x1C28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                                                                                                                             |

| 1-21.                                                                                                                               | RAM Sleep Mode Control Register2 [0x1C2A]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                                             |

| 1-22.                                                                                                                               | RAM Sleep Mode Control Register3 [0x1C2B]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                                             |

| 1-23.                                                                                                                               | RAM Sleep Mode Control Register4 [0x1C2C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                |

| 1-24.                                                                                                                               | RAM Sleep Mode Control Register5 [0x1C2D]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                                             |

| 1-25.                                                                                                                               | IFR0 and IER0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                |

| 1-26.                                                                                                                               | IFR1 and IER1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                                                                                                                                                                                             |

| 1-27.                                                                                                                               | Die ID Register 0 (DIEIDR0) [1C40h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>60</b>                                                                                                                                                                                      |

| 1-28.                                                                                                                               | Die ID Register 1 (DIEIDR1) [1C41h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                |

| 1-29.                                                                                                                               | Die ID Register 2 (DIEIDR2) [1C42h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                |

| 1-30.                                                                                                                               | Die ID Register 3 (DIEIDR3) [1C43h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                             |

|                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

| 1-31.                                                                                                                               | Die ID Register 4 (DIEIDR4) [1C44h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                             |

| 1-31.<br>1-32.                                                                                                                      | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61<br>61                                                                                                                                                                                       |

|                                                                                                                                     | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61<br>61<br>62                                                                                                                                                                                 |

| 1-32.                                                                                                                               | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61<br>61<br>62                                                                                                                                                                                 |

| 1-32.<br>1-33.<br>1-34.<br>1-35.                                                                                                    | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61<br>61<br>62<br>62<br>63                                                                                                                                                                     |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.                                                                                           | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61<br>62<br>62<br>63<br>65                                                                                                                                                                     |

| 1-32.<br>1-33.<br>1-34.<br>1-35.                                                                                                    | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61<br>62<br>62<br>63<br>65<br>67                                                                                                                                                               |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.                                                                         | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]                                                                                                                                                                                                                                                                                                                                                                                                                     | 61<br>62<br>62<br>63<br>65<br>67<br>68                                                                                                                                                         |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.                                                                | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]                                                                                                                                                                                                                                                                                                                                                                  | 61<br>62<br>62<br>63<br>65<br>67<br>68<br>69                                                                                                                                                   |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.                                                       | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]                                                                                                                                                                                                                                                                                                               | <ul> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> </ul>                                                                         |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.<br>1-41.                                              | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]                                                                                                                                                                                                                                                                                                               | <ul> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> </ul>                                                             |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.                                                       | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]<br>DMA Interrupt Flag Register (DMAIFR) [1C31h]                                                                                                                                                                                                                                                               | <ul> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> <li>73</li> </ul>                                                 |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.<br>1-41.<br>1-42.<br>1-43.                            | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]<br>DMA Interrupt Flag Register (DMAIFR) [1C31h]<br>DMA Interrupt Enable Register (DMAIFR) [1C31h]                                                                                                                                                                                                             | <ul> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> <li>73</li> <li>74</li> </ul>                                     |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.<br>1-41.<br>1-42.<br>1-43.<br>1-44.                   | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]<br>DMA Interrupt Flag Register (DMAIFR) [1C31h]<br>DMA Interrupt Enable Register 1 (DMA <i>n</i> CESR1) [1C1Ah, 1C1Ch, 1C36h, and 1C38h]<br>DMA <i>n</i> Channel Event Source Register 2 (DMA <i>n</i> CESR2) [1C1Bh, 1C1Dh, 1C37h, and 1C39h]                                                                | <ul> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> <li>74</li> <li>74</li> </ul>                                     |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.<br>1-41.<br>1-41.<br>1-42.<br>1-43.<br>1-44.<br>1-45. | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]<br>DMA Interrupt Flag Register (DMAIFR) [1C30h]<br>DMA Interrupt Enable Register (DMAIER) [1C31h]<br>DMA <i>n</i> Channel Event Source Register 1 (DMA <i>n</i> CESR1) [1C18h, 1C1Ch, 1C36h, and 1C38h]<br>DMA <i>n</i> Channel Event Source Register 2 (DMA <i>n</i> CESR2) [1C18h, 1C1Dh, 1C37h, and 1C39h] | <ul> <li>61</li> <li>62</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> <li>74</li> <li>74</li> <li>75</li> </ul>                         |

| 1-32.<br>1-33.<br>1-34.<br>1-35.<br>1-36.<br>1-37.<br>1-38.<br>1-39.<br>1-40.<br>1-41.<br>1-42.<br>1-43.<br>1-44.                   | Die ID Register 4 (DIEIDR4) [1C44h]<br>Die ID Register 5 (DIEIDR5) [1C45h]<br>Die ID Register 6 (DIEIDR6) [1C46h]<br>Die ID Register 7 (DIEIDR7) [1C47h]<br>External Bus Selection Register (EBSR) [1C00h]<br>RTC Power Management Register (RTCPMGT) [1930h]<br>Output Slew Rate Control Register (OSRCR) [1C16h]<br>Pulldown Inhibit Register 1 (PDINHIBR1) [1C17h]<br>Pulldown Inhibit Register 2 (PDINHIBR2) [1C18h]<br>Pulldown Inhibit Register 3 (PDINHIBR3) [1C19h]<br>DMA Interrupt Flag Register (DMAIFR) [1C31h]<br>DMA Interrupt Enable Register 1 (DMA <i>n</i> CESR1) [1C1Ah, 1C1Ch, 1C36h, and 1C38h]<br>DMA <i>n</i> Channel Event Source Register 2 (DMA <i>n</i> CESR2) [1C1Bh, 1C1Dh, 1C37h, and 1C39h]                                                                | <ul> <li>61</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> <li>67</li> <li>68</li> <li>69</li> <li>70</li> <li>73</li> <li>73</li> <li>74</li> <li>74</li> <li>75</li> <li>75</li> </ul> |

| 1-48. | EMIF Clock Divider Register (ECDR) [1C26h] | 78 |

|-------|--------------------------------------------|----|

|-------|--------------------------------------------|----|

# List of Tables

| 1-1.                    | DARAM Blocks                                                                                                             |                 |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1-2.                    | SARAM Blocks                                                                                                             | 16              |

| 1-3.                    | SAROM Blocks                                                                                                             | 17              |

| 1-4.                    | PLL Output Frequency Configuration                                                                                       | 22              |

| 1-5.                    | CLKOUT Control Source Select Register (CCSSR) Field Descriptions                                                         | 23              |

| 1-6.                    | Clock Generator Control Register Bits Used In BYPASS MODE                                                                | 25              |

| 1-7.                    | Output Frequency in Bypass Mode                                                                                          | 25              |

| 1-8.                    | Clock Generator Control Register Bits Used In PLL Mode                                                                   | 26              |

| 1-9.                    | PLL Clock Frequency Ranges                                                                                               | 26              |

| 1-10.                   | Examples of Selecting a PLL MODE Frequency, When CLK_SEL=L                                                               | 27              |

| 1-11.                   | Clock Generator Registers                                                                                                | 28              |

| 1-12.                   | Clock Generator Control Register 1 (CGCR1) Field Descriptions                                                            | 29              |

| 1-13.                   | Clock Generator Control Register 2 (CGCR2) Field Descriptions                                                            | 29              |

| 1-14.                   | Clock Generator Control Register 3 (CGCR3) Field Descriptions                                                            | 30              |

| 1-15.                   | Clock Generator Control Register 4 (CGCR4) Field Descriptions                                                            | 30              |

| 1-16.                   | Clock Configuration Register 1 (CCR1) Field Descriptions                                                                 | 31              |

| 1-17.                   | Clock Configuration Register 2 (CCR2) Field Descriptions                                                                 | 31              |

| 1-18.                   | Power Management Features                                                                                                | 33              |

| 1-19.                   | DSP Power Domains                                                                                                        | 34              |

| 1-20.                   | Idle Configuration Register (ICR) Field Descriptions                                                                     | 36              |

| 1-21.                   | Idle Status Register (ISTR) Field Descriptions                                                                           | 37              |

| 1-22.                   | CPU Clock Domain Idle Requirements                                                                                       | 38              |

| 1-23.                   | Peripheral Clock Gating Configuration Register 1 (PCGCR1) Field Descriptions                                             | 39              |

| 1-24.                   | Peripheral Clock Gating Configuration Register 2 (PCGCR2) Field Descriptions                                             | 41              |

| 1-25.                   | Peripheral Clock Stop Request/Acknowledge Register (CLKSTOP) Field Descriptions                                          | 42              |

| 1-26.                   | USB System Control Register (USBSCR) Field Descriptions                                                                  | 44              |

| 1-27.                   | RTC Power Management Register (RTCPMGT) Field Descriptions                                                               |                 |

| 1-28.                   | RTC Interrupt Flag Register (RTCINTFL) Field Descriptions                                                                | 47              |

| 1-29.                   | On-Chip Memory Standby Modes                                                                                             |                 |

| 1-30.                   | Power Configurations                                                                                                     | 50              |

| 1-31.                   | Interrupt Table                                                                                                          |                 |

| 1-32.                   | IFR0 and IER0 Register Description                                                                                       |                 |

| 1-33.                   | IFR1 and IER1 Register Description                                                                                       | 57              |

| 1-34.                   | Die ID Registers                                                                                                         | 59              |

| 1-35.                   | Die ID Register 0 (DIEIDR0) Field Descriptions                                                                           |                 |

| 1-36.                   | Die ID Register 1 (DIEIDR1) Field Descriptions                                                                           |                 |

| 1-37.                   | Die ID Register 2 (DIEIDR2) Field Descriptions                                                                           |                 |

| 1-38.                   | Die ID Register 3 (DIEIDR3) Field Descriptions                                                                           |                 |

| 1-39.                   | Die ID Register 4 (DIEIDR4) Field Descriptions                                                                           |                 |

| 1-40.                   | Die ID Register 5 (DIEIDR5) Field Descriptions                                                                           |                 |

| 1-41.                   | Die ID Register 6 (DIEIDR6) Field Descriptions                                                                           |                 |

| 1-42.                   | Die ID Register 7 (DIEIDR7) Field Descriptions                                                                           |                 |

| 1-43.                   | EBSR Register Bit Descriptions Field Descriptions                                                                        |                 |

| 1-44.                   | RTCPMGT Register Bit Descriptions Field Descriptions                                                                     |                 |

| 4 4 5                   | Output Slew Rate Control Register (OSRCR) Field Descriptions                                                             | 67              |

| 1-45.                   |                                                                                                                          |                 |

| 1-45.<br>1-46.<br>1-47. | Pulldown Inhibit Register 1 (PDINHIBR1) Field Descriptions<br>Pulldown Inhibit Register 2 (PDINHIBR2) Field Descriptions | <mark>68</mark> |

| 1-48. | Pulldown Inhibit Register 3 (PDINHIBR3) Field Descriptions            | 70 |

|-------|-----------------------------------------------------------------------|----|

| 1-49. | Channel Synchronization Events for DMA Controllers                    | 72 |

| 1-50. | System Registers Related to the DMA Controllers                       | 72 |

| 1-51. | DMA Interrupt Flag Register (DMAIFR) Field Descriptions               | 73 |

| 1-52. | DMA Interrupt Enable Register (DMAIER) Field Descriptions             | 73 |

| 1-53. | DMAn Channel Event Source Register 1 (DMAnCESR1) Field Descriptions   | 74 |

| 1-54. | DMAn Channel Event Source Register 2 (DMAnCESR2) Field Descriptions   | 74 |

| 1-55. | Peripheral Software Reset Counter Register (PSRCR) Field Descriptions | 75 |

| 1-56. | Peripheral Reset Control Register (PRCR) Field Descriptions           | 76 |

| 1-57. | Effect of BYTEMODE Bits on EMIF Accesses                              | 77 |

| 1-58. | Effect of USBSCR BYTEMODE Bits on USB Access                          | 77 |

| 1-59. | EMIF System Control Register (ESCR) Field Descriptions                | 77 |

| 1-60. | EMIF Clock Divider Register (ECDR) Field Descriptions                 | 78 |

#### **About This Manual**

This document describes various aspects of the TMS320C5504 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

# **Related Documentation From Texas Instruments**

The following documents describe the TMS320C5515/14/05/04 Digital Signal Processor (DSP) Digital Signal Processor (DSP). Copies of these documents are available on the internet at <a href="http://www.ti.com">http://www.ti.com</a>.

<u>SWPU073</u> — TMS320C55x 3.0 CPU Reference Guide. This manual describes the architecture, registers, and operation of the fixed-point TMS320C55x digital signal processor (DSP) CPU.

- <u>SPRU652</u> TMS320C55x DSP CPU Programmer's Reference Supplement. This document describes functional exceptions to the CPU behavior.

- SPRUFO1A TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Inter-Integrated Circuit (I2C) Peripheral User's Guide. This document describes the inter-integrated circuit (I2C) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The I2C peripheral provides an interface between the device and other devices compliant with Phillips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1 and connected by way of an I2Cbus. This document assumes the reader is familiar with the I2C-bus specification.

- <u>SPRUF02</u> TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Timer/Watchdog Timer User's Guide. This document provides an overview of the three 32-bit timers in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The 32-bit timers of the device are software programmable timers that can be configured as general-purpose (GP) timers. Timer 2 can be configured as a GP, a Watchdog (WD), or both simultaneously.

- SPRUF03 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Serial Peripheral Interface (SPI) User's Guide. This document describes the serial peripheral interface (SPI) in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The SPI is a highspeed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 32 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI supports multi-chip operation of up to four SPI slave devices. The SPI can operate as a master device only.

SPRUF04 — TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) General-Purpose Input/Output (GPIO) User's Guide. This document describes the general-purpose input/output (GPIO) on the TMS320C5515/14/05/04/VC05/VC04 digital signal processor (DSP) devices. The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of an internal register. When configured as an output you can write to an internal register to control the state driven on the output pin.

<u>SPRUF05</u> — TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Universal Asynchronous Receiver/Transmitter (UART) User's Guide. This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU.

SPRUFT2— TMS320C5515/14/05/04 DSP Direct Memory Access (DMA) Controller User's Guide This document describes the features and operation of the DMA controller that is available on the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The DMA controller is used to move data among internal memory, external memory, and peripherals without intervention from the CPU and in the background of CPU operation.

SPRUGU6— TMS320C5515/14/05/04 DSP External Memory Interface (EMIF) User's Guide. This document describes the operation of the external memory interface (EMIF) in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The purpose of the EMIF is to provide a means to connect to a variety of external devices.

<u>SPRUF06</u>— TMS320C5515/14/05/04/VC05/VC04 DSP Multimedia Card (MMC)/Secure Digital (SD) Card Controller This document describes the Multimedia Card (MMC)/Secure Digital (SD) Card Controller on the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The multimedia card (MMC)/secure digital (SD) card is used in a number of applications to provide removable data storage. The MMC/SD card controller provides an interface to external MMC and SD cards.

<u>SPRUFX2</u>— TMS320C5515/14/05/04 Digital Signal Processor (DSP) Real-Time Clock (RTC) User's Guide. This document describes the operation of the Real-Time Clock (RTC) module in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The RTC also has the capability to wake-up the power management and apply power to the rest of the device through an alarm, periodic interrupt, or external WAKEUP signal.

SPRUFX4— TMS320C5515/14/05/04 Digital Signal Processor (DSP) Inter-IC Sound (I2S) Bus User's Guide. This document describes the features and operation of Inter-IC Sound (I2S) Bus in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. This peripheral allows serial transfer of full duplex streaming data, usually streaming audio, between DSP and an external I2S peripheral device such as an audio codec.

SPRUFX6— TMS320C5514 DSP System User's Guide. This document describes various aspects of the TMS320C5514 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUFX5— TMS320C5515 DSP System User's Guide. This document describes various aspects of the TMS320C5515 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- <u>SPRUGH6</u>— TMS320C5504 DSP System User's Guide. This document describes various aspects of the TMS320C5504 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- <u>SPRUGH5</u>— TMS320C5505 DSP System User's Guide. This document describes various aspects of the TMS320C5505 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

<u>SPRUGH9</u>— TMS320C5515 DSP Universal Serial Bus 2.0 (USB) Controller User's Guide This document describes the universal serial bus 2.0 (USB) in the TMS320C5515 Digital Signal Processor (DSP) devices. The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices.

# System Control

#### Topic

#### Page

| 1.1 | Introduction                     | 11 |

|-----|----------------------------------|----|

| 1.2 | System Memory                    | 13 |

| 1.3 | Device Clocking                  | 19 |

| 1.4 | System Clock Generator           | 21 |

| 1.5 | Power Management                 | 33 |

| 1.6 | Interrupts                       | 55 |

| 1.7 | System Configuration and Control | 59 |

# 1.1 Introduction

The TMS320C5504 digital-signal processor (DSP) contains a high-performance, low-power DSP to efficiently handle tasks required by portable audio, wireless audio devices, industrial controls, software defined radio, fingerprint biometrics, and medical applications. The DSP consists of the following primary components:

- A C55x CPU and associated memory

- Four DMA controllers and external memory interface

- Power management module

- A set of I/O peripherals that includes I2S, I2C, SPI, UART, Timers, EMIF, USB 2.0

For more information on these components, see the following documents:

- TMS320C55x 3.0 CPU Reference Guide (SWPU073).

- TMS320C55x v3.x CPU Algebraic Instruction Set Reference Guide (<u>SWPU068E</u>)

- TMS320C55x v3.x CPU Mnemonic Instruction Set Reference Guide (<u>SWPU067E</u>)

- TMS320C55x DSP Peripherals Overview Reference Guide (SPRU317)

Introduction

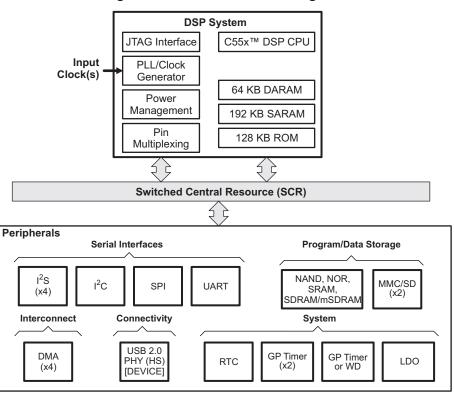

#### 1.1.1 Block Diagram

The DSP block diagram is shown in Figure 1-1.

#### Figure 1-1. Functional Block Diagram

#### 1.1.2 CPU Core

The C55x CPU is responsible for performing the digital signal processing tasks required by the application. In addition, the CPU acts as the overall system controller, responsible for handling many system functions such as system-level initialization, configuration, user interface, user command execution, connectivity functions, and overall system control.

Tightly coupled to the CPU are the following components:

- DSP internal memories

- Dual-access RAM (DARAM)

- Single-access RAM (SARAM)

- Read-only memory (ROM)

- Ports and buses

The CPU also manages/controls all peripherals on the device. Refer to the device-specific data manual for the full list of peripherals.

Figure 1-1 shows the functional block diagram of the DSP and how it connects to the rest of the device. The DSP architecture uses the switched central resource (SCR) to transfer data within the system.

#### 1.1.3 Power Management

Integrated into the DSP are the following power management features:

- One low dropout LDO for analog portions of the device, DSP PLL (V<sub>DDA\_PLL</sub>), and power management circuits (V<sub>DDA\_ANA</sub>): ANA\_LDO

- One LDO for DSP core (CV<sub>DD</sub>): DSP\_LDO

- One LDO for USB core and PHY (USB\_V<sub>DDA1P3</sub>): USB\_LDO

- Idle controller with several clock domains:

- CPU domain

- Clock generator domain

- Peripheral domain

- USB domain

- Real-time clock (RTC) domain

- Independent voltage and power domains

- LDOI (LDOs and Bandgap Power Supply)

- Analog POR, and PLL (V<sub>DDA ANA</sub> and V<sub>DDA PLL</sub>)

- Real-time clock core (CV<sub>DDRTC</sub>) Note: CV<sub>DDRTC</sub> must always be powered by an external power source. None of the on-chip LDOs can power CV<sub>DDRTC</sub>.

- Digital core (CV<sub>DD</sub>)

- USB core (USB\_ V<sub>DD1P3</sub> and USB\_V<sub>DDA1P3</sub>)

- USB PHY and USB PLL (USB\_V<sub>DDOSC</sub>, USB\_V<sub>DDA3P3</sub>, and USB\_V<sub>DDPLL</sub>)

- EMIF I/O (DV<sub>DDEMIF</sub>)

- RTC I/O (DV<sub>DDRTC</sub>)

- Rest of the I/O (DV<sub>DDIO</sub>)

# 1.1.4 Peripherals

The DSP includes the following peripherals:

- Four direct memory access (DMA) controllers, each with four independent channels.

- One external memory interface (EMIF) with 21-bit address and 16-bit data. The EMIF has support for mobile SDRAM and non-mobile SDRAM single-level cell (SCL) NAND with 1-bit ECC, and multi-level cell (MLC) NAND with 4-bit ECC.

- **NOTE:** The DSP can support non-mobile SDRAM under certain circumstances. The DSP always uses mobile SDRAM initialization but it is able to support SDRAM memories that ignore the BAO and BA1 pins for the 'load mode register' command. During the mobile SDRAM initialization, the device issues the 'load mode register' initialization command to two different addresses that differ in only the BAO and BA1 address bits. These registers are the Extended Mode register and the Mode register. The Extended mode register exists only in mSDRAM and not in non-mSDRAM. If a non-mobile SDRAM memory ignores bits BAO and BA1, the second loaded register value overwrites the first, leaving the desired value in the Mode register and the non-mobile SDRAM will work with this DSP.

- Two serial busses each configurable to support one Multimedia Card (MMC) / Secure Digital (SD/SDIO) controller, one inter-IC sound bus (I2S) interface with GPIO, or a full GPIO interface.