# Safety Manual for C2000<sup>™</sup> MCUs in IEC60730 Safety Applications

# **User's Guide**

Literature Number: SPRUHI3A April 2013–Revised August 2013

# Contents

| 1    | Introd | uction                                                                  | 4         |

|------|--------|-------------------------------------------------------------------------|-----------|

|      | 1.1    | About This Document                                                     | 4         |

|      | 1.2    | C2000 and its Application Sectors                                       | 5         |

| 2    | C2000  | Architecture and Product Overview                                       | 5         |

|      | 2.1    | C2000 MCU Architecture Classifications                                  | 6         |

|      | 2.2    | Targeted Applications and Product Safety Constraints                    | 8         |

| 3    | C2000  | MCU Development Process for Management of Systematic Faults             | 9         |

|      | 3.1    | TI Standard Automotive MCU and C2000 MCU Development Process            | . 9       |

|      | 3.2    | C2000 MCU Development Process                                           | 10        |

| 4    | Produ  | ct Architecture for Management of Random Faults                         | 11        |

|      | 4.1    | Philosophy and Architecture Partition for Safety Analysis               | 11        |

|      | 4.2    | Management of Family Variants                                           | 11        |

|      | 4.3    | Piccolo MCU Family                                                      | 12        |

|      | 4.4    | Delfino MCU Family                                                      | 20        |

|      | 4.5    | C2000 MCUs Operating States                                             | 23        |

|      | 4.6    | Management of Exception and Errors                                      | 24        |

| 5    | C2000  | MCU Architecture Safety Mechanisms and Assumptions of Use               | <b>24</b> |

|      | 5.1    | Standard Safety Diagnostic Functions With C2000 MCUs and Subsystems     | 24        |

|      | 5.2    | Functional Descriptions of Safety Modules in C2000 MCUs                 | 26        |

| 6    | Next S | Steps in Your Safety Development                                        | 27        |

| Appe | ndix A | Summary of Recommended Safety Feature Usage                             | <b>29</b> |

| Appe | ndix B | IEC60730-Class B/UL1998 Class 1 MCU Safety Compliance Features          | 31        |

| Appe | ndix C | C2000 MCU IEC60730 Software Safety Development Process                  | 32        |

|      | C.1    | Software Design                                                         | 32        |

|      | C.2    | Coding Standard and Naming Conventions                                  | 32        |

|      | C.3    | MISRA C Exceptions for C2000 MCU C28x Architecture                      | 34        |

| Appe | ndix D | C2000 Compiler and Tools Development Process and Tracking               | 35        |

| Appe | ndix E | STL Test Suite Release Process                                          | 36        |

| Appe | ndix F | Typical Application Firmware With IEC60730 Safety Supervisory Functions | 38        |

| Appe | ndix G | Glossary                                                                | 39        |

| Appe | ndix H | Revision History                                                        | <b>40</b> |

| -    |        |                                                                         |           |

2

# List of Figures

| 1  | C2000 MCU for IEC60730 Applications - An Overview of System Architecture                                        | 6  |

|----|-----------------------------------------------------------------------------------------------------------------|----|

| 2  | TI Standard MCU Automotive QM Development Process                                                               | 10 |

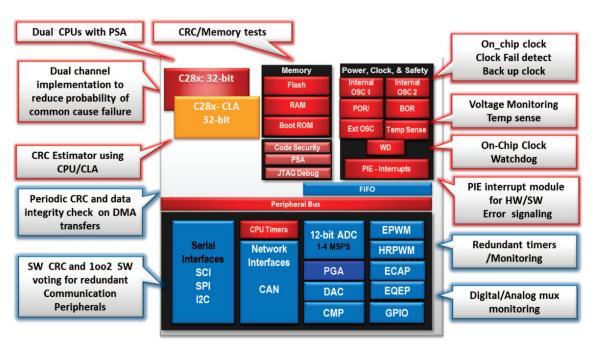

| 3  | C2000 MCU Piccolo F2806x With Safety Features in Software                                                       | 13 |

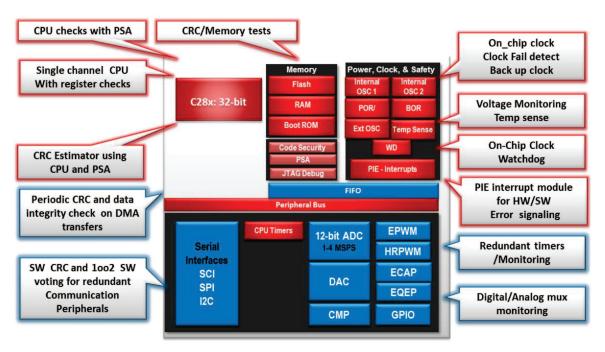

| 4  | C2000 MCU Piccolo F2803x With Safety Features in Software                                                       | 15 |

| 5  | C2000 MCU Piccolo F2805x With Safety Features in Software                                                       | 17 |

| 6  | C2000 MCU Piccolo F2802x With Safety Features in Software                                                       | 19 |

| 7  | C2000 MCU Delfino F2833x With Safety Features in Software                                                       | 21 |

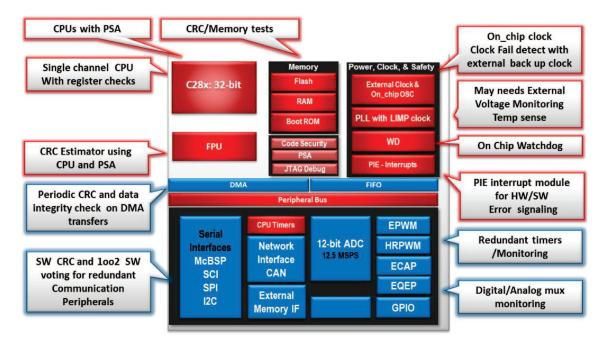

| 8  | C2000 MCU Delfino F2823x With Safety Features in Software                                                       | 22 |

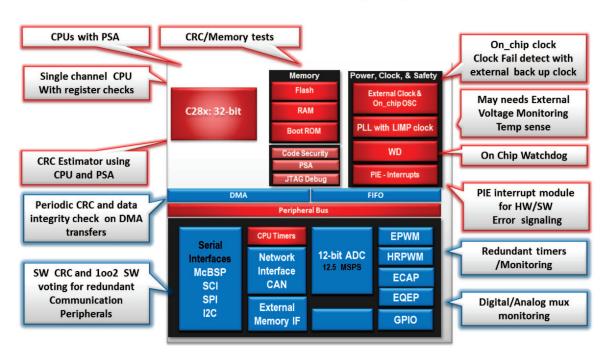

| 9  | Piccolo and Delfino MCUs Operating States                                                                       | 23 |

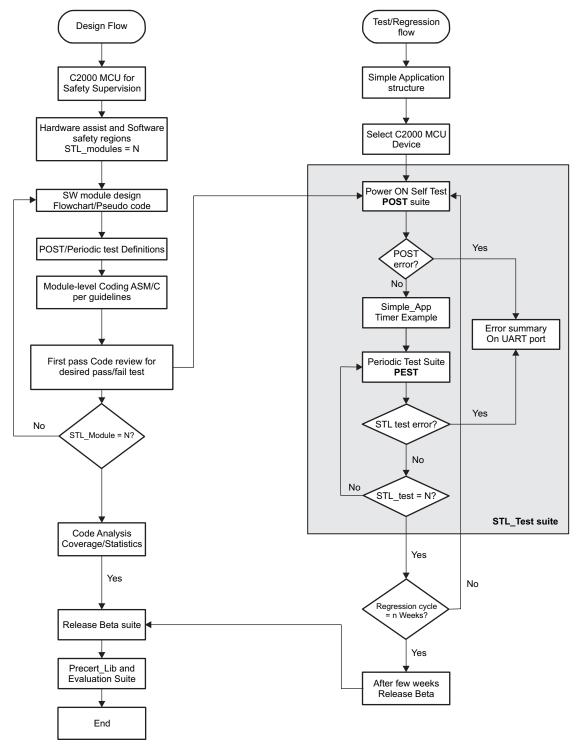

| 10 | C2000 STL Library Development Process                                                                           | 32 |

| 11 | C2000 IEC60730 STL Library – Design, Test and Regression Flow - DTR                                             | 36 |

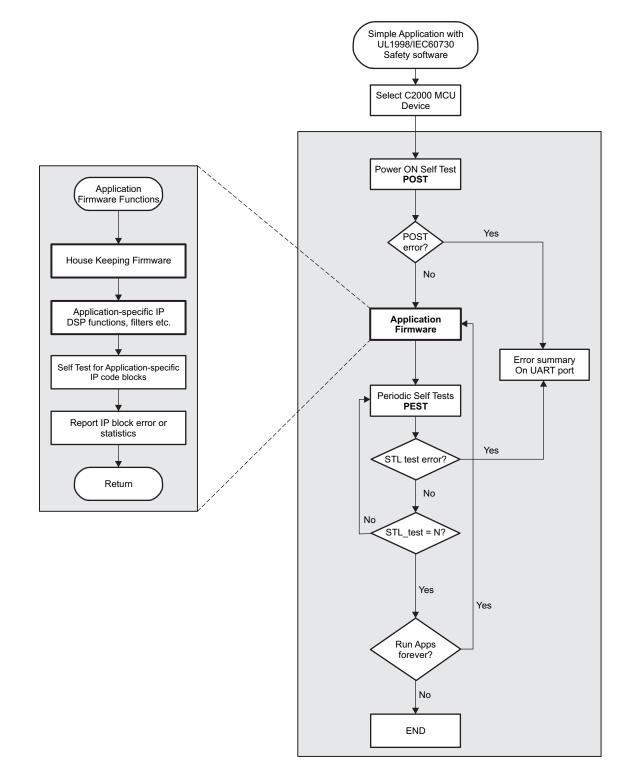

| 12 | Typical Application Firmware Components With C2000 IEC60730 STL (Self Test Libraries) – POST and PEST Functions | 38 |

# List of Tables

| 1  | C2000 MCU Documentation                                                   | 7  |

|----|---------------------------------------------------------------------------|----|

| 2  | C2000 MCU Features List                                                   | 11 |

| 3  | Functional Descriptions of Safety Modules in C2000 MCUs                   | 25 |

| 4  | C2000 MCU IEC60730/UL1998/IEC60335 product functional safety deliverables | 27 |

| 5  | Legend                                                                    | 29 |

| 6  | Summary of Safety Features and Recommendations                            | 29 |

| 7  | Coverage for MCU Hardware Failure Modes and Software Safety Function      | 31 |

| 8  | TI Wiki Links for Software Tools                                          | 35 |

| 9  | Table Terms and Definitions                                               | 39 |

| 10 | SPRUHI3A Revisions                                                        | 40 |

|    |                                                                           |    |

3

# Safety Manual for C2000<sup>™</sup> MCUs in IEC60730 Safety Applications

# 1 Introduction

You, as a system and equipment manufacturer or designer, are responsible to ensure that your systems (and any Texas Instruments hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested TI products, and other materials) is provided for reference only. You understand and agree that your use of TI components in safety critical applications is entirely at your risk, and that you (as buyer) agree to defend, indemnify, and hold harmless TI from any and all damages, claims, suits, or expense resulting from such use.

This document is a safety manual for the Texas Instruments C2000 32-bit real time C2000<sup>™</sup> microcontrollers product family. This document introduces TI's C2000 family of controllers and its subsystem-based architecture that matches most real-time control systems. Its inherent safety features could enable existing and emerging systems that require IEC60730 and IEC60335 or UL1998 safety compliance.

# 1.1 About This Document

This safety manual provides information needed by system developers to assist in the creation of a IEC60730 class of safety system using a C2000 microcontroller (MCU). This document contains:

- An overview of C2000 MCU Piccolo™ and Delfino™ MCU product architecture

- An overview of the development process utilized to reduce systematic failures

- An overview of the safety architecture for management of **random** failures

- The details of architecture partitions, implemented safety mechanisms, and recommended usage

- · Software design and development process

It is expected that the user of this document should have a general familiarity with the C2000 product family. More information can be found at <a href="http://www.ti.com/C2000">http://www.ti.com/C2000</a>. This document is intended to be used in conjunction with the device-specific data sheets, technical reference manuals, and other documentation for the products under development. This partition of technical content is intended to simplify development, reduce duplication of content, and avoid confusion as compared to the definition of safety manual referenced in any of the IEC safety standards.

IEC60730, IEC60335 and UL1998 specification addresses safety in appliances and equipment's that uses microelectronic hardware and its related software. All these standards reference similar safety functions addressing appliances or industrial equipment. Throughout this document IEC60730 will be the common name used for this safety standard, unless called separately. This document will cover Class B and Class1 level of safety mentioned in these specifications. For this release of this document, all references are applicable IEC60730-1: 2010 Class B and UL1998:2008 Class 1 standards.

C2000, Piccolo, Delfino, Code Composer Studio are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

IEC60730 Safety manual is part of the C2000 MCU device-specific collateral material and help implement functional safety features enabling the hardware and software libraries. The IEC60730 Library release includes the following collaterals:

- IEC60730 software user's manual

- Software libraries

- Hardware kit for software evaluation, as applicable

Each of the C2000 MCU supporting safety applications may support limited FMEA analysis summary. These are available as NDA documents only. Please contact your TI field and support for product-specific FMEA.

# 1.2 C2000 and its Application Sectors

C2000 MCUs brings together highly efficient control CPU, control peripherals and rich analog peripherals to build a deterministic control applications. All C2000 MCUs use real-time 32-bit C28x CPU with or without floating-point unit (FPU). Higher end C2000 MCUs support highly differentiated math capabilities using Viterbi Complex Unit (VCU) modules. Piccolo (TMSS320F2806x/5x/3x/2x) and Delfino (TMS320F28023x/33x) MCU feature sets have been proven to deliver high performance in many of the following applications spaces and still grow with their built-in safety features to meet several safety compliance standards:

- Low and high appliances, white goods, and industrial drives

- Power conversion (invertors)

- Energy conversion (solar) controllers

- Power line communication (PLC) controllers

Piccolo and Delfino families of real-time microcontrollers are part of the C2000 MCUs. These devices are available in different flavors of peripheral selection. Product-specific nomenclature and its derivatives are explained in the Piccolo and Delfino data sheets. Special derivatives, if any, are referenced explicitly with its part numbers.

# 2 C2000 Architecture and Product Overview

C2000 MCUs are built around real-time 32-bit C28x CPUs with system-on-chip (SoC) microcontroller (MCU) features with independent communication and real-time control and analog subsystems. Piccolo (TMSS320F2806x/5x/3x/2x) and Delfino (TMS320F28023x/33x) are part of this family that can enable IEC60730 Class B safety in industrial control, appliances, and other applications. The C2000 MCUs architecture provides users many control topologies utilizing its diverse peripherals within one physical IC package.

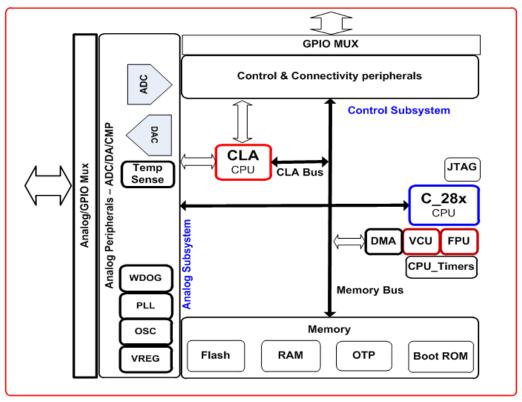

Figure 1 provides a very high-level overview of the C2000 MCUs featured in Piccolo and Delfino family of MCU devices.

Copyright © 2013, Texas Instruments Incorporated

# **C2000 MCUs - Piccolo and Delfino architecture**

# 2.1 C2000 MCU Architecture Classifications

The following configurations of CPU and subsystems are available across many of Piccolo and Delfino MCU devices. In this document subsystem refers to a collection of Control or Analog peripherals, critical for real time control applications. The above architecture breaks down to four types based on CPU processing power and subsystems.

- Type A: C28x CPU + FPU + VCU + CLA with Control and Analog Subsystem Piccolo6x family

- **Type B: C28x CPU + CLA** with Control and Analog Subsystem Piccolo3x/5x family

- Type C: C28x CPU + FPU with Control and Analog Subsystem Delfino F2833x family

- Type D: C28x CPU with Control and Analog Subsystem Piccolo2x and Delfino F2823x families

6

Texas

**NSTRUMENTS**

# • Type A: C28x CPU with FPU, VCU, CLA and CONTROL Subsystem:

32-bit microcontroller CPU with floating-point capabilities and control law accelerator (CLA) and dedicated I/O optimized for execution of real-time control algorithms, available on the Piccolo**6x** (F2806x) family of devices. This system contains multiple control peripherals (pulse width modulator (PWM), capture, encoders, serial interfaces). The CLA offers floating-point CPU with event optimized peripheral and I/O optimized for Analog subsystem. The CLA can also include safety functions in its capacity as a supervisory microcontroller. The Piccolo6x (2806x) family has an additional math unit VCU (Viterbi and Complex math unit) specifically to do advanced signal processing capabilities for control and power line communication applications

# • Type B: C28x CPU with FPU, CLA and CONTROL Subsystem:

32-bit microcontroller with fixed point and IQ math CPU capabilities, with CLA and I/O optimized for execution of real-time control algorithms, available on the Piccolo**3x** and Piccolo**5x** (F2803x/F2805x) family of devices. This system contains multiple control peripherals (PWM, capture, encoders, serial interfaces) for advanced control and sophisticated signal processing applications. The CLA offers a floating-point CPU with event optimized peripheral and I/O optimized for Analog subsystem. The CLA can also include safety functions in its capacity as a supervisory microcontroller.

# • Type C: C28x CPU with FPU and CONTROL Subsystem:

32-bit microcontroller CPU with floating-point capabilities and dedicated I/O optimized for execution of real-time control algorithms, available on the Delfino (F2833x) family of devices. This system contains multiple control peripherals (PWM, capture, encoders, serial interfaces) for advanced control and sophisticated signal processing applications.

#### • Type D: C28x CPU and CONTROL Subsystem:

32-bit microcontroller with fixed point and IQ math CPU capabilities, with dedicated I/O optimized for execution of real-time control algorithms, available on the Piccolo**2x** (F2802x) and Delfino (F2823x) family of devices. This system contains multiple control peripherals (PWM, capture, encoders, serial interfaces) for advanced control and sophisticated signal processing applications.

#### ANALOG Subsystem:

The Piccolo MCUs contain a rich set of integrated analog components, such as high performance 12bit analog-to-digital converter (ADC), analog comparators, zero-pin oscillators and voltage regulators.

The Delfino MCUs have reduced analog integration, but with high performance 12-bit 12.5 MSPS ADCs and clocking peripherals. Some of its hardware limitation has to be complemented with on-board feature depending on the end application.

The Delfino and Piccolo devices are built in the 180 nm process technology. This is a highly mature silicon technology process with high volume production across TI MCUs for more than a decade. This offers high level of integration, performance and reliability.

The C2000 MCU IEC60730 Safety Manual is to be complemented with its device level documentation, as listed in Table 1, to provide the necessary details on functional implementation and application use:

| C2000 MCU Product Family Technical Documentation                              | Abstract                                                                                                                               |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TMS320x28xx, 28xxx DSP Peripheral Reference Guide (SPRU566)                   | Summary and cross reference guide that describes the peripheral reference guides of the 28x digital signal processors (DSPs and MCUs). |  |  |

| TMS320F2806x Piccolo Microcontrollers Data Manual (SPRS698)                   |                                                                                                                                        |  |  |

| TMS320F2805x Piccolo Microcontrollers Data Manual (SPRS797)                   |                                                                                                                                        |  |  |

| TMS320F2803x Piccolo Microcontrollers Data Manual (SPRS584)                   | Technical data manual that describes the package, pin outs, and brief functional overview of all modules and electrical timings.       |  |  |

| TMS320F2802x, TMS320F2802xx Piccolo Microcontrollers Data<br>Manual (SPRS523) |                                                                                                                                        |  |  |

| TMS320F2802x0 Piccolo Microcontrollers Data Manual (SPRS810)                  |                                                                                                                                        |  |  |

| TMS320F2802x Piccolo MCU Silicon Errata (SPRZ292)                             |                                                                                                                                        |  |  |

| TMS320F2803x Piccolo MCU Silicon Errata (SPRZ295)                             | Describes silicon exceptions for system workaround and production readiness of silicon.                                                |  |  |

| TMS320F2806x Piccolo MCU Silicon Errata (SPRZ342)                             |                                                                                                                                        |  |  |

# Table 1. C2000 MCU Documentation

7

| C2000 MCU Product Family Technical Documentation Abstract                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| These technical reference manuals (TRM) detail the integration, environment, functional description, and the programming models for e peripheral and subsystem. These are single TRMs or multiple peripheral guides as listed below: |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                                                                                                                                                                                                                      | TMS320F2802x- See the list of documents under the Device<br>Support section in<br>TMS320F28027/28026/28023/28022/28021/28020/280200 Piccolo<br>Microcontrollers Data Manual (SPRS523) or TMS320x28xx, 28xxx<br>DSP Peripherals Reference Guide (SPRU566) cross reference guide                                                                                                                                                           |  |  |  |  |  |

| Piccolo Technical Reference Manual (TRM)                                                                                                                                                                                             | TMS320F2803x - See the list of documents under the Device<br>Support section in<br>TMS320F28030/28031/28032/28033/28034/28035 Piccolo<br>Microcontrollers Data Manual (SPRS584) or TMS320x28xx, 28xxx<br>DSP Peripherals Reference Guide (SPRU566) cross reference guide                                                                                                                                                                 |  |  |  |  |  |

|                                                                                                                                                                                                                                      | TMS320x2806x Piccolo Technical Reference Manual (SPRUH18) - single TRM                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| TMS320F2833x Digital Signal Controllers (DSCs) Microcontrollers<br>Data Manual (SPRS439) - Delfino                                                                                                                                   | Technical data manual that describes the package, pin outs, and brief functional overview of all modules and electrical timings.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| TMS320F2823x DSC Silicon Errata (SPRZ272) - Delfino                                                                                                                                                                                  | Describes silicon exceptions for system workaround and production readiness of the silicon.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Delfino Technical Reference Manual (TRM)                                                                                                                                                                                             | This technical reference manual (TRM) details the integration, the environment, the functional description and the programming models for each peripheral and subsystem. See the list of documents under the Device Support section in the <i>PMSM3-1:</i> Sensored Field Oriented Control of 3-Phase PM Synchronous Motor User's Guide (SPRU439) or TMS320x28xx, 28xxx DSP Peripherals Reference Guide (SPRU566) cross reference guide. |  |  |  |  |  |

| TMS320C28x CPU and Instruction Set Reference Guide (SPRU430)                                                                                                                                                                         | This document describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x 32-bit fixed-point CPU. It also describes emulation features available on these devices.                                                                                                                                                                                                                              |  |  |  |  |  |

| TMS320C28x Floating Point Unit and Instruction Set Reference Guide (SPRUEO2)                                                                                                                                                         | This document describes the CPU architecture, pipeline, instruction set, and interrupts of the C28x floating-point DSP.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

#### Table 1. C2000 MCU Documentation (continued)

# 2.2 Targeted Applications and Product Safety Constraints

The C2000 MCU family is targeted primarily for appliance and industrial application spaces and can address general-purpose safety applications.

As these devices are mass market product rather than custom product, it cannot be said that a specific implementation configuration can be assumed. It is expected that the same modules used for the general function in the appliances space will be used for safety critical functions in industrial, power conversion and energy conversion markets. Energy conversion, like the solar inverter, is an emerging example that is increasingly complex and looking for compliance to functional safety standards within the product and equipment level.

In the case of overlapping requirements between target systems, TI has attempted to design the device respecting the most stringent requirement. For example, the fault tolerant time intervals for typical motor drives can be within few 10s of milliseconds. The C2000-based system can address fault tolerant times similar to these intervals or better. C2000 MCU's overall response can reach < 10 ms fault tolerant time interval.

The C2000 MCU's device is designed to meet most of the safety features mentioned in the IEC60730 standards or equivalent. While these devices have several hardware safety features, the application level software is the critical part that adds value to the hardware features and enforces safety discipline and to meet functional safety compliance. A properly designed product using the C2000 MCUs should be capable of meeting safety requirements, if the designers use the device within its stated specifications and implement the required diagnostic hardware and software as stated in this document. System integrator should ensure component and system safety concepts are assessed and adhered during its development and product life cycle.

# 3 C2000 MCU Development Process for Management of Systematic Faults

For a safety critical development, it is necessary to manage both systematic and random faults. Texas Instruments has created a unique development process for safety critical semiconductors that greatly reduce probability of systematic failure. This process builds on a standard quality managed development as the foundation for safety critical development. The TI MCU teams use this process across all its family of MCUs that cater to industrial and automotive applications.

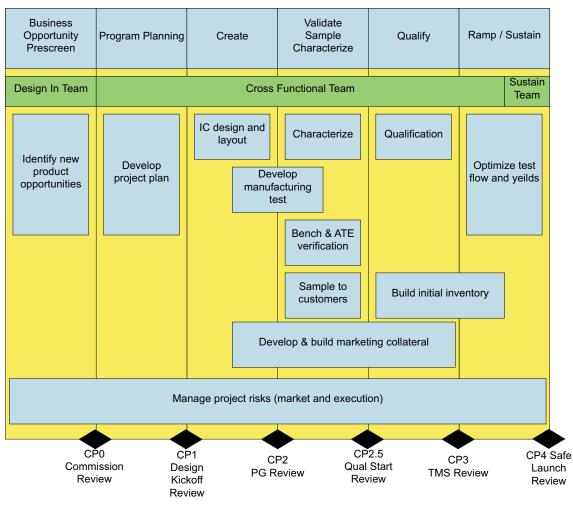

# 3.1 TI Standard Automotive MCU and C2000 MCU Development Process

Texas Instruments has been developing microcontrollers for industrial and automotive markets that require safety and non-safety applications for over twenty years. Industrial and automotive markets have strong requirements on quality management and high product reliability. Though not explicitly developed for compliance to a functional safety standard, the TI standard MCU development process already featured many elements necessary to manage systematic faults. This development process can be considered to be Quality Managed (QM), but does not achieve an IEC 61058 Safety Integrity Level (SIL) or ISO 26262 Automotive Safety Integrity Level (ASIL). The TI standard MCU automotive development process is certified compliant to ISO TS 16949 as assessed by Det Norske Veritas Certification, Inc. (Katy, Texas) under certificate CERT-07319CC10-2004-AQ-HOU-IATF (IATF certificate No 0113679). The development is also certified compliant to ISO 9001:2008 as assessed by DNV Certification B.V. (Netherlands) under Certificate CERT-06185-2003-AQ-HOU-RvA Rev. 2. These standards explicitly apply to TI MCUs (C2000 MCUs, Hercules, TMS570S and RM48x MCUs) that are developed in the same silicon technology nodes.

The standard development process breaks development into phases:

- Business opportunity pre-screen

- Program planning

- Create

- Validate, sample and characterize

- Qualify

- Ramp to production and sustaining production

9

#### C2000 MCU Development Process for Management of Systematic Faults

www.ti.com

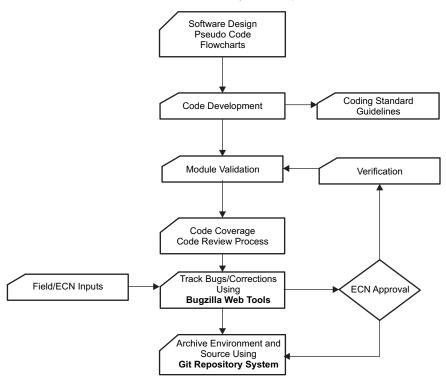

Texas Instruments Incorporated (TI) standard silicon development process is illustrated in Figure 2.

Figure 2. TI Standard MCU Automotive QM Development Process

# 3.2 C2000 MCU Development Process

The Piccolo and Delfino MCU silicon development process is as per TI MCU development methods and conforms to ISOTS16949 flow. The goal of the process development is to take the best aspects of each flow and collaborate to result in best in class capabilities to reduce systematic faults. The process flow is also targeted for compliance to IEC 61508 as well and is under a process of continuous improvement to incorporate new features. Piccolo and Delfino series of C2000 MCUs are developed to offer devices with several temperature grades to address consumer, industrial and automotive applications.

Key elements of the TI MCU process flow are:

- Assumptions on system level design, safety concept, and requirements based on TI's expertise in safety critical systems development

- Combined qualitative and quantitative or similar safety analysis techniques comprehending the sum of silicon failure modes and diagnostic techniques known to TI

- Fault estimation based on multiple industry standards as well as TI manufacturing data

- C2000 MCU development process adopts QRASAP00160 new product development processes.

# 4 Product Architecture for Management of Random Faults

For a safety critical development, it is necessary to manage both systematic and random faults. The C2000 MCU product architecture includes safety mechanisms that can help detect and respond to random faults when used correctly. This section describes the architectural safety concept and software layers that need to be adopted in C2000 MCU devices.

# 4.1 Philosophy and Architecture Partition for Safety Analysis

Piccolo and Delfino MCUs address functional safety with limited hardware assist and layers of supervisory software libraries to detect system and device failure and prompt for corrective actions. This enables simplified functional system partitioning during run time and distribute system level supervisors across the memory, peripherals and analog modules.

Piccolo MCU family offers two distinct variant of safety implementation based on its hardware capabilities. Most of the low end Piccolo (Piccolo2x) derivatives use single C28x CPU configurations, hence, the safety features are primarily software functions along with main application firmware. Piccolo3x/6x and devices has two options of enhancing the safety supervision using both C28x CPU and CLA. This configuration can offer CPU level redundancies on critical functions to implement single and dual channel systems. This is strong differentiator as it offers benefits of dissimilar instruction set and diversity during firmware execution.

# 4.2 Management of Family Variants

The Piccolo and Delfino MCUs architecture supports multiple product variants. Table 2 shows an overview of CPUs memory and peripherals that each of the Piccolo and Delfino MCU architectures support. Among these families there are a number of devices each with different flavors of peripherals. To ascertain the available CPU, memory or peripheral mix for each of these families, see the device-specific data sheet.

These products could be implemented as unique silicon designs or they may be shared silicon designs that have elements disabled or not guaranteed by specification, even if present in silicon. Only the elements that are enabled in the device as specified in the device-specific data sheet and technical reference manual are to be used for safety feature enhancements or safety software implementation. Elements that are not part of the device, even though it is supported in the superset of the device family, are not guaranteed to be present and operate.

|                                 | C2000 32-Bit Microcontrollers - MCU |              |              |                |              |              |

|---------------------------------|-------------------------------------|--------------|--------------|----------------|--------------|--------------|

|                                 | Picollo Family <sup>(1)</sup>       |              |              | Delfino Family |              |              |

|                                 | TMS320F2806x                        | TMS320F2805x | TMS320F2803x | TMS320F2802x   | TMS320F2833x | TMS320F2823x |

| 32-Bit CPU                      | 90 MHz                              | 80 MHz       | 60 MHz       | 60 MHz         | 150 MHz      | 150 MHz      |

| C28x - CPU                      | х                                   | x            | х            | х              | х            | x            |

| Floating-Point Unit (FPU)       | х                                   |              |              |                | x            |              |

| IQMath Capabilities             | х                                   | x            | х            | х              | х            | x            |

| Viterbi Complex Math Unit (VCU) | х                                   |              |              |                |              |              |

| Control Law Accelerator (CLA)   | х                                   | x            | х            |                |              |              |

| Direct Memory Access (DMA)      | х                                   |              |              |                | x            | х            |

| Memory                          |                                     |              |              |                |              |              |

| Boot ROM                        | х                                   | x            | х            | х              | х            | х            |

| Random-Access Memory (RAM)      | х                                   | x            | х            | х              | х            | x            |

| FLASH                           | х                                   | x            | х            | х              | х            | х            |

| Read-Only Memory (ROM)          | х                                   | x            | х            | х              |              |              |

| One-Time Programmable (OTP)     | х                                   | x            | х            | х              | х            | х            |

| Peripheral Interrupts (PIE)     | х                                   | x            | х            | х              | х            | х            |

| Control Peripherals             |                                     |              |              |                |              |              |

| 32-Bit CPU Timers               | х                                   | x            | х            | x              | x            | x            |

| PWM                             | x                                   | x            | х            | x              | x            | х            |

# Table 2. C2000 MCU Features List

(1) Piccolo2x also include Piccolo2x0 devices.

|                                                  | C2000 32-Bit Microcontrollers - MCU |                     |                            |                      |                      |                      |

|--------------------------------------------------|-------------------------------------|---------------------|----------------------------|----------------------|----------------------|----------------------|

|                                                  | Picollo Family <sup>(1)</sup>       |                     |                            |                      | Delfino Family       |                      |

|                                                  | TMS320F2806x                        | TMS320F2805x        | TMS320F2803x               | TMS320F2802x         | TMS320F2833x         | TMS320F2823x         |

| 32-Bit CPU                                       | 90 MHz                              | 80 MHz              | 60 MHz                     | 60 MHz               | 150 MHz              | 150 MHz              |

| High-Resolution Pulse Width<br>Modulator (HRPWM) | x                                   |                     | x                          | x                    | x                    | x                    |

| High-Resolution Capture (HRCAP)                  | х                                   |                     | x                          |                      |                      |                      |

| Quadrature Encoder Pulse (QEP)                   | х                                   | x                   | x                          | x                    | х                    | x                    |

| Communications Peripherals                       |                                     |                     |                            |                      |                      |                      |

| Univeral Serial Bus (USB)                        | х                                   |                     |                            |                      |                      |                      |

| Serial Peripheral Interface (SPI)                | х                                   | x                   | x                          |                      | х                    | х                    |

| Serial Communications Interface<br>(SCI)         | x                                   | x                   | x                          | x                    | x                    | x                    |

| Local Interconnect Network (LIN)                 | х                                   |                     | x                          |                      |                      |                      |

| Controller Area Network (CAN)                    | x                                   | x                   | x                          |                      | x                    | x                    |

| Inter-Integrated Circuit (I2C)                   | x                                   | x                   | x                          | x                    | x                    | x                    |

| Multichannel Buffered Serial Port<br>(McBSP)     | х                                   |                     |                            |                      | x                    | х                    |

| External Memory Bus                              | x                                   |                     |                            |                      | x                    | x                    |

| Analog Peripherals                               |                                     |                     |                            |                      |                      |                      |

| 2-Pin Oscillators                                | x                                   |                     | x                          | x                    | x                    | x                    |

| 0-Pin Oscillators                                | x                                   | x                   | x                          | x                    |                      |                      |

| POR and BOR                                      | x                                   | x                   | x                          | x                    |                      |                      |

| On-Chip Voltage Regulator<br>(VREG)              | x                                   | x                   | x                          | x                    |                      |                      |

| Temp Sensor                                      | x                                   | x                   | x                          | x                    |                      |                      |

| Analog-to-Digital Converter (ADC)                | х                                   | x                   | x                          | x                    | х                    | x                    |

| OPAMP                                            |                                     | x                   |                            |                      |                      |                      |

| Digital-to-Analog Converter (DAC)                | х                                   | x                   | x                          | x                    |                      |                      |

| Comparator                                       | х                                   | x                   | x                          | x                    |                      |                      |

| Packaging                                        | 80 pin<br>100 pin                   | 64 pin<br>80 pin    | 56 pin<br>64 pin<br>80 pin | 38 pin<br>48 pin     | 176 pin<br>179 pin   | 176 pin<br>179 pin   |

| Applications Space                               | Motor Control                       | Motor Control       | Motor Control              | Motor Control        | Motor Control        | Motor Control        |

|                                                  | Energy Conversion                   |                     | Energy<br>Conversion       | Energy<br>Conversion | Energy<br>Conversion | Energy<br>Conversion |

|                                                  | Power Conversion                    | Power<br>Conversion | Power Conversion           | Power Conversion     | Power Conversion     | Power<br>Conversion  |

|                                                  | Power Line Comms                    |                     |                            |                      | Automotive Radar     | Automotive<br>Radar  |

# Table 2. C2000 MCU Features List (continued)

# 4.3 Piccolo MCU Family

Piccolo MCUs address a wide range of performance levels in real time control applications. The makeup of the family is differentiated at the 32-bit CPU performance, control and analog subsystem peripherals. Table 2 provides Piccolo MCU feature set break up. For detailed resource availability, see the device-specific data sheet on that section and on the TI web sites.

Piccolo MCUs have proven many control topologies in motor and other emerging applications. Tight integration of the 32-bit CPU performance and peripherals is mandatory to make these topologies a deterministic control system. Having proven in many of these applications, at the equipment level there is a demand to reach functional safety levels. Functional safety levels are governed by many of IEC and UL standards to enforce safety discipline in hardware and software development. IEC60730 and UL1998 have published a series of safety test across any microcontroller device.

The IEC60730 software library on Piccolo MCU architecture brings out the built-in hardware features and system level diagnostics to detect failures during power up and run time of the application. Since the Piccolo family is architecturally scalable to different features and cost segments, the IEC60730 library is mostly compatible to all its devices, except that some of the software functions need some porting to match the peripheral mix used in the end application system.

# 4.3.1 Type A: C28x CPU + FPU + VCU + CLA With Control and Analog Subsystem – Piccolo6x Family

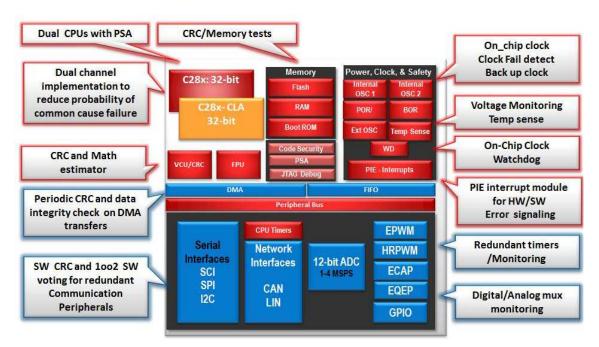

# C2000 MCU Piccolo F2806x with safety features in software C28x CPU + FPU + VCU + CLA with Control & Analog Subsystem

Figure 3. C2000 MCU Piccolo F2806x With Safety Features in Software

**Piccolo6x**: TMS320F2806x MCU is the full featured C2000 MCU with a dedicated 32-bit C28x main CPU, floating-point unit and Viterbi and math accelerators (VCU). CPU performance is further supported by an event optimized, CLA that is capable of 32-bit C28x CPU functions with floating-point precision. Having both a main C28x CPU and CLA accelerator on-chip enables many time critical functions, algorithms, and timing checks in parallel. This enables a virtual dual channel implementation by creatively partitioning CPUs and peripherals. Having two independent processors provides inherent safety for the system and protects against common cause failures.

The main CPU has a built-in 40-bit CRC checker, the parallel signature analysis (PSA) that can be used to do on-the-fly CRC calculations for any of the program code or memory blocks. This is a differentiating hardware working in parallel to the main CPU to estimate the CRC on the memory contents and CPU instructions. The IEC60730 software libraries have functions using the PSA hardware and details of its use conditions. While most MCUs can calculate CRC in software using CRC algorithms, the PSA hardware is a feature that prioritizes instruction and memory level integrity checks and enhances the safety coverage for the CPU and memory regions. In addition, the Piccolo6x architecture is capable of doing advanced CRC and math accelerations using its VCU unit. This offers a third method to do memory CRC calculations and algorithms. These features help to comply with the safety requirements easily.

Piccolo6x memory has non-volatile Flash, one-time programmable (OTP) Flash, read-only memory (BROM) and RAM blocks. PSA-based CRC or memory-based CRC and March 13 algorithms are made available to check memory integrity in periodic and power up software routines.

#### Product Architecture for Management of Random Faults

The system integrator is responsible for the functional partition of these processing engines, depending on the end application, as each application has different safety reactions and recovery times. The IEC60730 libraries enable easy implementation of safety software using the hardware and software functions.

**Control Subsystem**: Piccolo6x devices have proven control peripherals such as PWMs, enhanced capture (ECAP), and enhanced quadrature encoder pulse (EQEP) modules as part of the MCUs control subsystem. These hardware peripherals are instantiated in multiple instances on the same chip. This enables redundant channel implementation, thus enabling a higher level of safety in the end equipment. Having redundant channels enables 1002 (1 out of 2 architecture) level voting scheme on critical control channels.

The high-resolution pulse width modulator (HRPWM) module enhances the resolution of the PWM control and provides unique calibration logic to track the PWM modulation accuracy and input clock oscillator accuracy. The oscillator accuracy library functions use the SFO libraries, which use the inherent calibration logic, to measure the accuracy of the oscillator clock and PLL.

General-purpose input/output (GPIO) configuration registers are write-protected with special EALLOW instructions. Most of the GPIO inputs have a programmable de-glitching filter to screen spurious noise or debouncing. This is especially important for PWM output trip control signals, to avoid false tripping of PWM outputs.

The Control peripherals are complemented with three 32-bit CPU timers that can support time base checks, and as redundant channels to implement timing checks.

Piccolo MCUs use industry standard communication ports such as: controller area network (CAN), serial communications interface (SCI), serial peripheral interface (SPI), multichannel buffered serial port (McBSP) and inter-integrated circuit (I2C). These peripherals are often available in multiple instantiations that allow 1002 voting schemes and internal loop back paths that allow periodic serial data integrity checks.

Section 5 presents many of the functional safety diagnostics schemes that can be implemented to add safety in each of these MCU functions during run time and power up state.

**Analog Subsystem**: Piccolo6x analog subsystem supports all the necessary analog sensing and feedback channels. It has its own independent regulated power, oscillators, temperature sensor and PLL clock. At runtime, it is synchronized and tightly coupled to the main CPU and control subsystems. Piccolo MCU addresses the safety requirements of the operating clock redundancy with a minimum of two clocks sources and an additional external clock source. There are two zero-pin oscillators operating in parallel, OSC1 and OSC2, an additional on-chip crystal oscillator, and an external clock pin.

The oscillator clocks feed the on-chip watchdog module to provide time-out monitoring of time critical loops. Device reset is offered through an external pin. This is a bidirectional pin allowing on-chip watchdog reset to propagate to external devices. The reset input signal is always qualified with a deglitching filter (about 200 ns) that helps to block reset line noise due to any electrical disturbance.

The dependencies of these clock domains and recovery mechanisms are presented in the Piccolo technical reference manual (see Table 1). The on-chip regulator supports POR and BOR logic to generate under voltage detection.

Product Architecture for Management of Random Faults

#### 4.3.2 Type B: C28x CPU + CLA With Control and Analog Subsystem – Piccolo3x Family

# C2000 MCU Piccolo F2803x with safety features in software

C28x CPU + CLA with Control & Analog Subsystem

Figure 4. C2000 MCU Piccolo F2803x With Safety Features in Software

**Piccolo3x**: TMS320F2803x MCU is functionally identical to TMS320F2806x except for the FPU, VCU and USB modules. It has a dedicated 32-bit C28x main CPU. CPU performance is further supported by an event optimized, CLA that is capable of 32-bit C28x CPU functions with floating point precision. Having both a main C28x CPU and CLA on-chip enables running many time critical functions, algorithms, and timing checks in parallel. This enables a virtual dual channel implementation by creatively partitioning CPUs and peripherals. Having two independent processors provides inherent safety for the system and protects against common cause failures.

The main CPU has a built-in 40-bit CRC checker, the PSA that can be used to do on-the-fly CRC calculations for any of the program code or memory blocks. This is a differentiating hardware working in parallel to the main CPU to estimate the CRC on the memory contents and CPU instructions. The IEC60730 software libraries have functions using the PSA hardware and details of its use conditions. While most MCUs can calculate CRC in software using CRC algorithms, the PSA hardware is a feature that prioritizes instruction and memory level integrity checks and enhances the safety coverage for the CPU and memory regions. In addition, the Piccolo6x architecture is capable of doing advanced CRC and math accelerations using its VCU unit. This offers a third method to do memory CRC calculations and algorithms. These features help to comply with the safety requirements easily.

Piccolo3x memory has non-volatile Flash, OTP Flash, read-only memory (BROM) and RAM blocks. PSAbased CRC or memory-based CRC and March 13 algorithms are made available to check memory integrity in periodic and power up software routines.

The system integrator is responsible for the functional partition of these processing engines, depending on the end application, as each application has different safety reactions and recovery times. The IEC60730 libraries enable easy implementation of safety software using the hardware and software functions.

**Control Subsystem**: Piccolo3x devices have proven control peripherals such as PWMs, ECAP, and EQEP modules as part of the MCUs control subsystem. These hardware peripherals are instantiated in multiple instances on the same chip. This enables redundant channel implementation, thus enabling a higher level of safety in the end equipment. Having redundant channels enables 1002 (1 out of 2 architecture) level voting scheme on critical control channels.

The HRPWM module enhances the resolution of the PWM control and provides unique calibration logic to track the PWM modulation accuracy and input clock oscillator accuracy. The oscillator accuracy library functions use the SFO libraries, which use the inherent calibration logic, to measure the accuracy of the oscillator clock and PLL.

GPIO configuration registers are write-protected with special EALLOW instructions. Most of the GPIO inputs have a programmable de-glitching filter to screen spurious noise or debouncing. This is especially important for PWM output trip control signals, to avoid false tripping of PWM outputs.

The Control peripherals are complemented with three 32-bit CPU timers that can support time base checks, and as redundant channels to implement timing checks.

Piccolo MCUs use industry standard communication ports such as: CAN, SCI, local interconnect network (LIN), SPI, and I2C. These peripherals are often available in multiple instantiations that allow 1002 voting schemes and internal loop back paths that allow periodic serial data integrity checks.

Section 5 presents many of the functional safety diagnostics schemes that can be implemented to add safety in each of these MCU functions during run time and power up state.

**Analog Subsystem**: Piccolo3x analog subsystem supports all the necessary analog sensing and feedback channels. It has its own independent regulated power, oscillators, temperature sensor and PLL clock. At runtime, it is synchronized and tightly coupled to the main CPU and control subsystems. Piccolo MCU addresses the safety requirements of the operating clock redundancy with a minimum of two clocks sources and an additional external clock source. There are two zero-pin oscillators operating in parallel, OSC1 and OSC2, an additional on-chip crystal oscillator, and an external clock pin.

The oscillator clocks feed the on-chip watchdog module to provide time-out monitoring of time critical loops. Device reset is offered through an external pin. This pin is a bidirectional pin allowing on-chip watchdog reset to propagate to external devices. The reset input signal is always qualified with a deglitching filter (about 200 ns) that helps to block reset line noise due to any electrical disturbance.

The dependencies of these clock domains and recovery mechanisms are presented in the Piccolo technical reference manual (see Table 1). The on-chip regulator supports POR and BOR logic to generate under voltage detection.

# 4.3.3 Type B: C28x CPU + CLA With Control and Analog Subsystem – Piccolo5x Family

# C2000 MCU Piccolo F2805x with safety features in software C28x CPU + CLA with Control & Analog Subsystem

# Figure 5. C2000 MCU Piccolo F2805x With Safety Features in Software

**Piccolo5x**: TMS320F2805x MCU is functionally identical to TMS320F2803x except for the PGA, CAN and LIN modules. It has a dedicated 32-bit C28x main CPU supports fixed point and IQmath capabilities to accelerate time critical functions, and control algorithms.

The main CPU has a built-in 40-bit CRC checker, the PSA that can be used to do on-the-fly CRC calculations for any of the program code or memory blocks. This is a differentiating hardware working in parallel to the main CPU to estimate the CRC on the memory contents and CPU instructions. The IEC60730 software libraries have functions using the PSA hardware and details of its use conditions. While most MCUs can calculate CRC in software using CRC algorithms, the PSA hardware is a feature that prioritizes instruction and memory level integrity checks and enhances the safety coverage for the CPU and memory regions. In addition, the Piccolo6x architecture is capable of doing advanced CRC and math accelerations using its VCU unit. This offers a third method to do memory CRC calculations and algorithms. These features help to comply with the safety requirements easily.

Piccolo5x memory has non-volatile Flash, OTP Flash, read-only memory (BROM) and RAM blocks. PSAbased CRC or memory-based CRC and March 13 algorithms are made available to check memory integrity in periodic and power up software routines.

The system integrator is responsible for the functional partition of these processing engines, depending on the end application, as each application has different safety reactions and recovery times. The IEC60730 libraries enable easy implementation of safety software using the hardware and software functions.

**Control Subsystem**: Piccolo5x devices have proven control peripherals such as PWMs, ECAP, and EQEP modules as part of the MCUs control subsystem. These hardware peripherals are instantiated in multiple instances on the same chip. This enables redundant channel implementation, thus enabling a higher level of safety in the end equipment. Having redundant channels enables 1002 (1 out of 2 architecture) level voting scheme on critical control channels.

#### Product Architecture for Management of Random Faults

www.ti.com

The HRPWM module enhances the resolution of the PWM control and provides unique calibration logic to track the PWM modulation accuracy and input clock oscillator accuracy. The oscillator accuracy library functions use the SFO libraries, which use the inherent calibration logic, to measure the accuracy of the oscillator clock and PLL.

GPIO configuration registers are write-protected with special EALLOW instructions. Most of the GPIO inputs have a programmable de-glitching filter to screen spurious noise or debouncing. This is especially important for PWM output trip control signals, to avoid false tripping of PWM outputs.

The Control peripherals are complemented with three 32-bit CPU timers that can support time base checks, and as redundant channels to implement timing checks.

Piccolo MCUs use industry standard communication ports such as: CAN, SCI, SPI, and I2C. These peripherals are often available in multiple instantiations that allow 1002 voting schemes and internal loop back paths that allow periodic serial data integrity checks.

Section 5 presents many of the functional safety diagnostics schemes that can be implemented to add safety in each of these MCU functions during run time and power up state.

**Analog Subsystem**: Piccolo5x analog subsystem supports all the necessary analog sensing and feedback channels. It has its own independent regulated power, oscillators, temperature sensor and PLL clock. At runtime, it is synchronized and tightly coupled to the main CPU and control subsystems. Piccolo MCU addresses the safety requirements of the operating clock redundancy with a minimum of two clocks sources and an additional external clock source. There are two zero-pin oscillators operating in parallel, OSC1 and OSC2, an additional on-chip crystal oscillator, and an external clock pin.

The oscillator clocks feed the on-chip watchdog module to provide time-out monitoring of time critical loops. Device reset is offered through an external pin. This pin is a bidirectional pin allowing on-chip watchdog reset to propagate to external devices. The reset input signal is always qualified with a deglitching filter (about 200 ns) that helps to block reset line noise due to any electrical disturbance.

The dependencies of these clock domains and recovery mechanisms are presented in the Piccolo technical reference manual (see Table 1). The on-chip regulator supports POR and BOR logic to generate under voltage detection.

# 4.3.4 Type D: C28x CPU With Control and Analog Subsystem – Piccolo2x Family

# C2000 MCU Piccolo F2802x with safety features in software C28x CPU with Control & Analog Subsystem

# Figure 6. C2000 MCU Piccolo F2802x With Safety Features in Software

**Piccolo2x**: TMS320F2802x MCU is functionally identical to TMS320F2803x except for the CLA, CAN and LIN modules. It has a dedicated 32-bit C28x main CPU supports fixed point and IQmath capabilities to accelerate time critical functions, and control algorithms.

The main CPU has a built-in 40-bit CRC checker, the Parallel Signature Analysis (PSA) that can be used to do on-the-fly CRC calculations for any of the program code or memory blocks. This is a differentiating hardware working in parallel to the main CPU to estimate the CRC on the memory contents and CPU instructions. The IEC60730 software libraries have functions using the PSA hardware and details of its use conditions. While most MCUs can calculate CRC in software using CRC algorithms, the PSA hardware is a feature that prioritizes instruction and memory level integrity checks and enhances the safety coverage for the CPU and memory regions. In addition, the Piccolo6x architecture is capable of doing advanced CRC and math accelerations using its VCU unit. This offers a third method to do memory CRC calculations and algorithms. These features help to comply with the safety requirements easily.

Piccolo2x memory has non-volatile Flash, OTP Flash, read-only memory (BROM) and RAM blocks. PSAbased CRC or memory-based CRC and March 13 algorithms are made available to check memory integrity in periodic and power up software routines.

The system integrator is responsible for the functional partition of these processing engines, depending on the end application, as each application has different safety reactions and recovery times. The IEC60730 libraries enable easy implementation of safety software using the hardware and software functions.

**Control Subsystem**: Piccolo2x devices have proven control peripherals such as PWMs, ECAP, and EQEP modules as part of the MCUs control subsystem. These hardware peripherals are instantiated in multiple instances on the same chip. This enables redundant channel implementation, thus enabling a higher level of safety in the end equipment. Having redundant channels enables 1002 (1 out of 2 architecture) level voting scheme on critical control channels.

The HRPWM module enhances the resolution of the PWM control and provides unique calibration logic to track the PWM modulation accuracy and input clock oscillator accuracy. The oscillator accuracy library functions use the SFO libraries, which use the inherent calibration logic, to measure the accuracy of the oscillator clock and PLL.

GPIO configuration registers are write-protected with special EALLOW instructions. Most of the GPIO inputs have a programmable de-glitching filter to screen spurious noise or debouncing. This is especially important for PWM output trip control signals, to avoid false tripping of PWM outputs.

The Control peripherals are complemented with three 32-bit CPU timers that can support time base checks, and as redundant channels to implement timing checks.

Piccolo MCUs use industry standard communication ports such as; SCI, SPI, and I2C. These peripherals are often available in multiple instantiations that allow 1002 voting schemes and internal loop back paths that allow periodic serial data integrity checks.

Section 5 presents many of the functional safety diagnostics schemes that can be implemented to add safety in each of these MCU functions during run time and power up state.

**Analog Subsystem**: Piccolo2x analog subsystem supports all the necessary analog sensing and feedback channels. It has its own independent regulated power, oscillators, temperature sensor and PLL clock. At runtime, it is synchronized and tightly coupled to the main CPU and control subsystems. Piccolo MCU addresses the safety requirements of the operating clock redundancy with a minimum of two clocks sources and an additional external clock source. There are two zero-pin oscillators operating in parallel, OSC1 and OSC2, an additional on-chip crystal oscillator, and an external clock pin.

The oscillator clocks feed the on-chip watchdog module to provide time-out monitoring of time critical loops. Device reset is offered through an external pin. This pin is a bidirectional pin allowing on-chip watchdog reset to propagate to external devices. The reset input signal is always qualified with a deglitching filter (about 200 ns) that helps to block reset line noise due to any electrical disturbance.

The dependencies of these clock domains and recovery mechanisms are presented in the Piccolo technical reference manual (see Table 1). For more information, see Table 1. The on-chip regulator supports POR and BOR logic to generate under voltage detection.

#### 4.4 Delfino MCU Family

Delfino is high performance member of the C2000 MCU addressing a wide of industrial applications. The makeup of the family is differentiated at the 32-bit C28x CPU performance, control and analog subsystem peripherals. These offer devices offer 100 to 150MHz CPU Performance. The Table 2 above provides Delfino MCU feature set break up between F2833x and F2823x devices. For detailed resource availability, see the device-specific data sheet for that section and on the TI web site.

Integration of the 32-bit CPU performance and peripherals is mandatory to make these topologies a deterministic control system. Having proven in many of these applications, at the equipment level there is a demand to reach the emerging functional safety levels. Functional safety levels are governed by many of IEC and UL standards to enforce safety discipline in hardware and software development. IEC60730 and UL1998 have published a series of safety test across any microcontroller device. Some of the Delfino applications target IEC61508 level safety as well. These configurations are primarily in industrial drive application co-designed with companion chips to reach required level system level safety.

Since Delfino MCU's architecture is identical to the Piccolo MCU with less analog integration. The following sections will explain the device configurations. Delfino devices have to be used with companion chips to implement some of the functional safety requirements. Most of the Piccolo6x, IEC60730 software library functions are applicable to Delfino devices. Delfino version of IEC60730 will leverage the Piccolo6x library to build its system level diagnostics. Delfino family is architecturally scalable to different feature and cost segments, the IEC60730 library is mostly compatible to all of its devices, except that some of the software functions need some porting to match the peripheral mix used in the end application system.

Product Architecture for Management of Random Faults

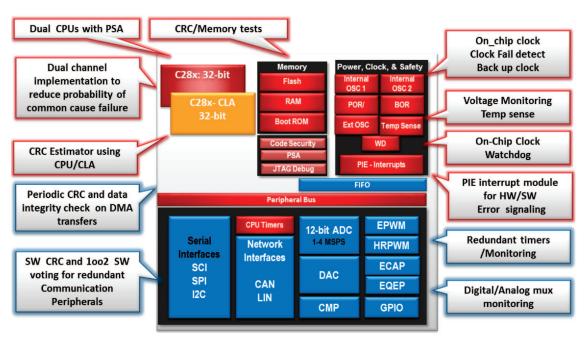

#### 4.4.1 Type C: C28x CPU + FPU With Control and Analog Subsystem – Delfino F2833x Family

# C2000 MCU Delfino F2833x with safety features in software

C28x CPU + FPU with Control & Analog Subsystem

Figure 7. C2000 MCU Delfino F2833x With Safety Features in Software

**Delfino**: TMS320F2833x MCU is the full featured C2000 MCU with a dedicated 32-bit C28x main CPU, floating point unit, designed for high performance (150MHz)). CPU performance is capable of fixed point math, IQmath and floating point precision. The main CPU has a built-in 40-bit CRC checker, the PSA that can be used to do on-the-fly CRC calculations for any of the program code or memory blocks. This is a differentiating hardware working in parallel to the main CPU to estimate the CRC on the memory contents and CPU instructions. The IEC60730 software libraries have functions using the PSA hardware and details of its use conditions. While most MCUs can calculate CRC in software using CRC algorithms, the PSA hardware is a feature that prioritizes instruction and memory level integrity checks and enhances the safety coverage for the CPU and memory regions.

Delfino memory has non-volatile Flash, OTP Flash, read-only memory (BROM) and RAM blocks. PSAbased CRC or memory-based CRC and March 13 algorithms are made available to check memory integrity in periodic and power up software routines.

The system integrator is responsible for the functional partition of these processing engines, depending on the end application, as each application has different safety reactions and recovery times. The IEC60730 libraries enable easy implementation of safety software using the hardware and software functions.

**Control Subsystem**: Delfino devices have proven control peripherals such as PWMs, ECAP, and EQEP modules as part of the MCUs control subsystem. These hardware peripherals are instantiated in multiple instances on the same chip. This enables redundant channel implementation, thus enabling a higher level of safety in the end equipment. Having redundant channels enables 1002 (1 out of 2 architecture) level voting scheme on critical control channels.

The HRPWM module enhances the resolution of the PWM control and provides unique calibration logic to track the PWM modulation accuracy and input clock oscillator accuracy. The oscillator accuracy library functions use the SFO libraries, which use the inherent calibration logic, to measure the accuracy of the oscillator clock and PLL.

GPIO configuration registers are write-protected with special EALLOW instructions. Most of the GPIO inputs have a programmable de-glitching filter to screen spurious noise or debouncing. This is especially important for PWM output trip control signals, to avoid false tripping of PWM outputs.

The Control peripherals are complemented with three 32-bit CPU timers that can support time base checks and as redundant channels.

Delfino MCUs use industry standard communication ports such as; CAN, SCI, SPI, McBSP and I2C. These peripherals are often available in multiple instantiations that allow 1002 voting schemes and internal loop back paths that allow periodic serial data integrity checks.

Section 5 presents many of the functional safety diagnostics schemes that can be implemented to add safety in each of these MCU functions during run time and power up state.

**Analog Subsystem**: Delfino analog subsystem supports all the necessary analog sensing and feedback channels. It has limited analog resources compared to the Piccolo family. Analog enhancement is primarily on the ADC convertor module. On-chip ADC is pipeline architecture capable of 12.5 MSPS to integrate sophisticated DSP algorithms in automotive radar and solar invertor applications. The device needs dual rail external 3.3 V and 1.8 V power supplies. It supports a crystal oscillator, external clock in and a PLL clock. PLL also supports a limp mode clock for clock recovery for safe shut down during input clock failure. External clock voltage monitors and check-micro helps to meet necessary functional safety compliance.

The oscillator clocks feed the on-chip watchdog module to provide time-out monitoring of time critical loops. Device reset is offered through an external pin. This pin is a bidirectional pin allowing on-chip watchdog reset to propagate to external devices. The reset input signal is always qualified with a deglitching filter (about 200 ns) that helps to block reset line noise due to any electrical disturbance.

# 4.4.2 Type D: C28x CPU With Control and Analog Subsystem – Delfino F2823x Family

# C2000 MCU Delfino F2823x with safety features in software C28x CPU with Control & Analog Subsystem

Figure 8. C2000 MCU Delfino F2823x With Safety Features in Software

**Delfino**: TMS320F2823x MCU is functionally identical to TMS320F2833x family except for the floatingpoint unit. For more details on this family, see Table 2.

# 4.5 C2000 MCUs Operating States

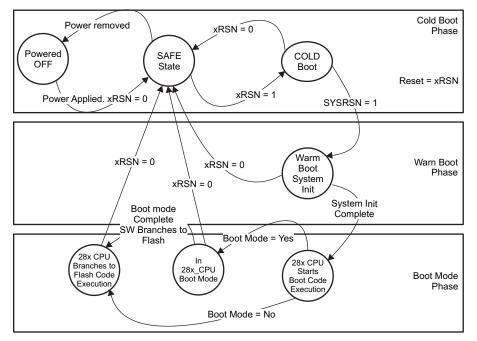

The C2000 MCU products have a common architectural definition of operating states. These operating states should be observed by the system developer in their software and system level design concepts. The operating states state machine is shown in Figure 9 and described below.

Figure 9. Piccolo and Delfino MCUs Operating States

- Powered Off This is the initial operating state of the C2000 MCUs. No power is applied to either core (V<sub>DD</sub> –1.8 V/1.2 V) or I/O power supply (V<sub>DDIO</sub> –3.3 V) and the device are non-functional. This state can only transition to the safe state, and can only be reached from the safe state.

- Safe In the safe state, the 28x CPU and its subsystems are powered but non-operational. The XRSN (power-on reset, also known as cold reset) is asserted by the system but is not released until power supplies have ramped to a stable state. The internal voltage monitor (POR and BOR) safety mechanism also continues to assert the SYSRSN internal to the device if power supplies are not within a minimum operational range. When the product is in the safe state, the CPUs and peripherals are non-functional. Output drivers are tri-stated and input/output pins are kept in an input only state.

- Cold Boot In the cold boot state, key analog elements, digital control logic, and debug logic are initialize for future use. The CPUs and the peripherals remain powered but non-operational. When the cold boot process is completed, the SYSRSN signal is internally released, leading to the warm boot stage.

- Warm Boot The warm boot mode resets digital logic and enables the C28x CPU. The C28x\_CPU begins executing software from Boot ROM, initializes the system and awaits boot mode. There is no hardware interlock to say that warm boot is completed; this is a software decision in C28x Boot code.

- Operational and Boot Phase In this state, only the C28x CPU enters Boot phase, checks for boot modes and enters boot function if valid else C28x CPU branches to flash memory to do software initialization and application code execution defined for the end application.

#### C2000 MCU Architecture Safety Mechanisms and Assumptions of Use

## 4.6 Management of Exception and Errors

The Piccolo and Delfino MCU product architectures leverage CPU interrupt and peripheral interrupt expansion (PIE) blocks for event triggers and preemption of software functions. These interrupts can be prioritized using the PIE module and respond to respective interrupt flags from various peripherals. These interrupts can also be activated using software interrupts instruction such as TRAP. All the hardware safety mechanism use these interrupt flags to generate error conditions to the CPU. The IEC60730 safety library routines can be tied to either hardware interrupt flags or software interrupt initiated functions to preempt CPU to do necessary safety recovery or reach safe state. The IEC60730 libraries support an error and exception reporting function using the on-chip UART and SCI port, providing an external communication port-based error function allows system error logging during validation and runtime use of the application. This function can be easily customized in the end application based on the error reporting needs. For details of PIE and CPU interrupt mapping, see the Piccolo or Delfino MCU technical reference manuals (see Table 1).

# 5 C2000 MCU Architecture Safety Mechanisms and Assumptions of Use

You, as a system and equipment manufacturer or designer, are responsible to ensure that your systems (any TI hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested TI products, and other materials) is provided for reference only. You understand and agree that your use of TI components in safety critical applications is entirely at your risk, and that you (as buyer) agree to defend, indemnify, and hold harmless TI from any and all damages, claims, suits, or expense resulting from such use. In this section, the safety mechanisms for each major functional block of the C2000 MCU architecture are summarized and general assumptions of use are provided. This information should be used to determine the strategy for utilizing functional safety mechanisms. The details of each safety mechanism can be found in the device-specific technical reference manual for the MCU used.

TI classifies technical recommendations for the use of safety mechanisms into a number of categories. The TI recommendations should not be considered infallible. There are many diverse ways to implement safe systems and alternate safety mechanisms may be possible that can provide support to achieve desired safety metrics. The categories of recommendation are as follows: