# TMS320C6211/TMS320C6211B Digital Signal Processors Silicon Errata

Silicon Revisions 1.0, 1.1, 2.1, 2.2, 3.0, and 3.1

SPRZ154L October 1999 Revised May 2004

Copyright © 2004, Texas Instruments Incorporated

## **REVISION HISTORY**

This silicon errata revision history highlights the technical changes made to the SPRZ154K revision to make it an SPRZ154L revision.

**Scope:** Applicable updates to the C62x device family, specifically relating to the C6211 and C6211B devices, have been incorporated.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 13             | Updated the second paragraph under Details for Advisory 3.1.1, EMIF: Async Read Setup Uses Write Setup Value. |

## Contents

| 1 | Introduction .  |                                                                                                                                                                                                                     | 5  |  |  |  |

|---|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

|   | 1.1 Quality an  | d Reliability Conditions                                                                                                                                                                                            | 5  |  |  |  |

|   | TMX Defin       | ition                                                                                                                                                                                                               | 5  |  |  |  |

|   |                 | ition                                                                                                                                                                                                               |    |  |  |  |

|   |                 | ition                                                                                                                                                                                                               |    |  |  |  |

|   |                 |                                                                                                                                                                                                                     |    |  |  |  |

| 2 |                 | n 3.1 Known Design Exceptions to Functional Specifications and Usage Notes                                                                                                                                          |    |  |  |  |

|   | 0               | tes for Silicon Revision 3.1                                                                                                                                                                                        |    |  |  |  |

|   | EMIF: L2 (      | HPI: Illegal Memory Access Can Result in Unexpected HPI Behavior       7         EMIF: L2 Cache Operations Block Other EDMA Operations to EMIF       6         (C671x/C621x Devices: All Silicon Revisions)       8 |    |  |  |  |

|   |                 | 21x Asynchronous Writes Setup Timing (C671x/C621x Devices: All Silicon Revisions)                                                                                                                                   |    |  |  |  |

|   |                 | vision 3.1 Known Design Exceptions to Functional Specifications                                                                                                                                                     |    |  |  |  |

|   | Advisory 3.1.1  | EMIF: Async Read Setup Uses Write Setup Value                                                                                                                                                                       |    |  |  |  |

|   | Advisory 3.1.2  | EMIF: Control Signals Not Inactive Before Asserting HOLDA                                                                                                                                                           |    |  |  |  |

|   | Advisory 3.1.3  | EMIF: One Cycle Asynchronous Write Setup                                                                                                                                                                            |    |  |  |  |

|   | Advisory 3.1.4  | JTAG: Boundary Scan Shift-DR Register Is Latched on the Falling Edge of TCK                                                                                                                                         |    |  |  |  |

|   | Advisory 3.1.5  | EDMA/L2 Controller: Potential EDMA Lockout From L2 SRAM                                                                                                                                                             |    |  |  |  |

|   | ,               | Example GEL File                                                                                                                                                                                                    | 19 |  |  |  |

|   | Advisory 3.1.6  | EMIF: Data Corruption can Occur in SDRAM When HOLD Feature is Used                                                                                                                                                  |    |  |  |  |

|   | Advisory 3.1.7  | EDMA: EDMA Blocked from Accessing L2 During Long String of Stores to the Same Bank in L2 RAM                                                                                                                        |    |  |  |  |

| 3 | Silicon Revisio | n 3.0 Known Design Exceptions to Functional Specifications and Usage Notes                                                                                                                                          | 28 |  |  |  |

|   | 3.1 Usage Not   | tes for Silicon Revision 3.0                                                                                                                                                                                        | 28 |  |  |  |

|   | HPI: Illega     | I Memory Access Can Result in Unexpected HPI Behavior                                                                                                                                                               | 28 |  |  |  |

|   | 3.2 Silicon Re  | vision 3.0 Known Design Exceptions to Functional Specifications                                                                                                                                                     | 28 |  |  |  |

|   | Advisory 3.0.1  | HPI: HPID Read/Write Accesses Must Be Terminated with a Fixed-Mode Access                                                                                                                                           | 28 |  |  |  |

| 4 | Silicon Revisio | n 2.2 Known Design Exceptions to Functional Specifications                                                                                                                                                          | 30 |  |  |  |

|   | Advisory 2.2.2  | HPI: Read Data Corrupted in Fixed-Address Mode and FETCH Read Requests                                                                                                                                              | 30 |  |  |  |

|   | Advisory 2.2.4  | JTAG: Boundary Scan Does Not Function                                                                                                                                                                               | 31 |  |  |  |

|   | Advisory 2.2.6  | HPI: Write Request During HPI Timeout Causes HPI Lock-Up                                                                                                                                                            | 31 |  |  |  |

|   | Advisory 2.2.7  | HPI: HRDY Behavior                                                                                                                                                                                                  | 32 |  |  |  |

| 5 | Silicon Revisio | n 2.1 Known Design Exceptions to Functional Specifications                                                                                                                                                          | 33 |  |  |  |

| 6 | Silicon Revisio | n 1.1 Known Design Exceptions to Functional Specifications                                                                                                                                                          | 33 |  |  |  |

|   | Advisory 1.1.1  | EMIF: ARDY Sampled During Entire Strobe Period                                                                                                                                                                      | 33 |  |  |  |

|   | Advisory 1.1.3  | Clock: CLKOUT1 Only Available in PLL x4 Mode                                                                                                                                                                        | 33 |  |  |  |

|   | Advisory 1.1.4  | JTAG: Boundary Scan Output Shift                                                                                                                                                                                    |    |  |  |  |

|   | Advisory 1.1.5  | JTAG: TCK Always Required                                                                                                                                                                                           |    |  |  |  |

|   | Advisory 1.1.6  | Interrupt: EXT_INT4 Synchronized to CLKOUT2                                                                                                                                                                         |    |  |  |  |

|   | 2               | $\cdot$ – $\cdot$                                                                                                                                                                                                   |    |  |  |  |

## TMS320C6211/TMS320C6211B Silicon Errata

| Advisory 1.1.8   | HPI: Software Handshaking Causes Corrupt Read Data                        | 29 |

|------------------|---------------------------------------------------------------------------|----|

| Advisory 1.1.9   | EDMA: User PaRAM Access During EDMA Active Events May Corrupt PaRAM       | 29 |

| Advisory 1.1.14  | EDMA: Interrupt 0 Incorrectly Set in CIPR                                 | 29 |

| Advisory 1.1.15  | L1 Hangs on Access to SRAM Address Mapped as Cache                        | 30 |

| Advisory 1.1.16  | L1D Cache: Data Corruption if L1D Powered Up to Wrong State               | 30 |

|                  | Assembly Code (bug.asm)                                                   | 32 |

|                  | Linker File (Ink.cmd)                                                     | 32 |

| Advisory 1.1.17  | EDMA: Extra Elements Transferred in Element Synchronization Mode (FS = 0) | 33 |

| Advisory 1.1.18  | EMIF: EMIF Address Lines Are In Undefined States Upon Exiting Reset –     |    |

|                  | May Cause Problems in Shared Memory System                                | 34 |

| Silicon Revision | 1.0 Known Design Exceptions to Functional Specifications                  | 35 |

| Advisory 1.0.7   | EDMA: SDINT and External Interrupts Not Received by EDMA                  | 35 |

| Advisory 1.0.10  | EMIF: Potential Reset Problem When CLKOUT2 is Tied to ECLKIN              | 35 |

| Advisory 1.0.12  | Access to Invalid Address in Interrupt Selector Space                     | 36 |

| Advisory 1.0.13  | Interrupt Selector Values Reversed for McBSP Interrupts                   | 36 |

|                  |                                                                           |    |

7

## 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320C6211 and TMS320C6211B digital signal processors. [See the *TMS320C6211, TMS320C6211B Fixed-point Digital Signal Processors* data sheet (literature number SPRS073).] These exceptions are applicable to the TMS320C6211 and TMS6211B devices (256-pin Ball Grid Array, GFN suffix).

For additional information, see the latest version of *TMS320C6000 DSP Peripherals Overview Reference Guide* (literature number SPRU190).

The advisory numbers in this docuemnt are not sequential. Some advisories have been moved to the next revision and others have been removed and documented in the user's guide. When advisories are moved or deleted, the remaining advisory numbers remain the same and are not resequenced.

## 1.1 Quality and Reliability Conditions

### **TMX Definition**

Texas Instruments (TI) does not warranty either (1) electrical performance to specification, or (2) product reliability for products classified as "TMX." By definition, the product has not completed data sheet verification or reliability performance qualification according to TI Quality Systems Specifications.

The mere fact that a "TMX" device was tested over a particular temperature range and voltage range should not, in any way, be construed as a warranty of performance.

### **TMP Definition**

TI does not warranty product reliability for products classified as "TMP." By definition, the product has not completed reliability performance qualification according to TI Quality Systems Specifications; however, products are tested to a published electrical and mechanical specification.

### **TMS** Definition

Fully-qualified production device

## 1.2 Revision Identification

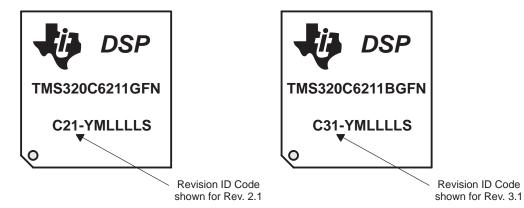

The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the GFN package is shown in Figure 1 and the revision ID codes are listed in Table 1. The revision ID described here is not to be confused with the CPU revision ID that is in the Control Status Register.

NOTE: Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

## Figure 1. Example, Revision ID Code for TMS320C6211 and TMS320C6211B (GFN)

Silicon revision is identified by a code on the chip. The code is of the format Cxx-YMLLLLS. If xx is 10, then the silicon is revision 1.0. If xx is 11 then the silicon is revision 1.1 and so on.

| Revision ID Code | Silicon Revision | Comments                                                                                                                                  |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 10               | 1.0              | TMX320C6211                                                                                                                               |

| 11               | 1.1              | TMX320C6211                                                                                                                               |

| 21               | 2.1              | TMS320C6211                                                                                                                               |

| 22               | 2.2              | TMS320C6211<br>Silicon Revision 2.2 is functionally the same as revision<br>2.1. It is optimized from revision 2.1 for yield improvement. |

| 30               | 3.0              | TMS320C6211B                                                                                                                              |

| 31               | 3.1              | TMS320C6211B                                                                                                                              |

## Table 1. Revision ID Codes

# 2 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications and Usage Notes

## 2.1 Usage Notes for Silicon Revision 3.1

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

## HPI: Illegal Memory Access Can Result in Unexpected HPI Behavior

On C6211/C6211B all silicon revisions, the DSP has a reserved memory range that is mapped to the internal FIFO of the HPI for EDMA engine usage. This reserved memory range is located at 0x60000000 – 0x7FFFFFFF in the memory map. If CPU code (or a host access) happens to read/write from/to this memory range, the internal HPI state machine can be corrupted, causing one or more of the following occurrences:

- Host reads/writes through the HPI fail. HPI reads return incorrect data, and/or HPI writes result in incorrect data being written.

- Host reads/writes through the HPI take an unexpectedly long time. The HRDY signal stays high (not ready) for an extended period of time.

- HPI locks up. HRDY stays high indefinitely.

The most common cause of this illegal access is uninitialized or stray pointers. To verify that the DSP program does not perform this illegal memory access, the user can use the Advanced Event Triggering tools featured in Code Composer Studio<sup>™</sup> Integrated Development Environment (IDE) version 2.1 or later, with the latest emulation driver. Below are the step-by-step instructions on how to trap a CPU access to the memory range 0x6000000 – 0x7FFFFFFF:

- 1. Start Code Composer Studio<sup>™</sup> IDE with the proper setup and GEL file.

- 2. Load the program.

- 3. Under the *Tools* menu, select Advanced Event Triggering > Event Analysis

- 4. Right-click on the bottom left panel that appears, select "Set Hardware Watchpoint".

- 5 Name the watchpoint; choose to watch for "Data Memory Reads" or "Data Memory Writes"; select the inclusive range start address (0x6000000) and end address (0x7FFFFFF); select the data size from 32-, 16-, or 8-bit to watch for word, halfword, or byte reads/writes, respectively. Then, click Apply.

- 6 The watchpoint now is enabled, indicated by the blue "E" icon. Now, run the program.

- 7. When a read/write to the specified memory range is detected, the CPU halts, and the blue "E" icon changes to a red "T" icon.

Code Composer Studio is a trademark of Texas Instruments.

#### Notes:

The CPU halts a few cycles *after* the specified memory access is detected. Without a CPU stall, the number of cycles is around 4 cycles. This means that when the CPU halts, the PC points to a few instructions after the one that caused the trap to trigger.

The hardware watchpoint restricts the trap to be set up for either read *or* write accesses, but not both. Therefore, the user may need to repeat this procedure several times for each read and write trap.

The above step-by-step method only catches illegal accesses made by the CPU, and does *not* catch illegal accesses made by the EDMA or a peripheral that uses the EDMA.

# EMIF: L2 Cache Operations Block Other EDMA Operations to EMIF (C671x/C621x Devices: All Silicon Revisions)

When using the L2 cache on the C671x/C621x devices, for a given EMIF-to-CPU frequency ratio, an L2 writeback or L2 writeback-invalidate operation may block other EDMA requests from accessing the EMIF until the operation completes. If the other EDMA requests to the EMIF have hard real-time deadlines, these deadlines may be missed if the deadline is shorter than the time required to complete the L2 writeback operation. The McBSP and McASP peripherals are most sensitive to this issue, as the buffering local to the McBSP/McASP peripheral can only hold data for at most one sample at a time before data loss occurs.

On the C671x/C621x devices, all cache requests to EMIF address ranges are serviced on the highest priority level of the EDMA (priority 0). All programmed EDMA or QDMA transfers (e.g., EDMA transfers to service the McBSP or paging data from EMIF to/from L2) and peripheral-initiated transfers (such as HPI) are limited to using priority 1 or priority 2 queues of the EDMA; therefore an L2 writeback or L2 writeback-invalidate operation may block the lower priority request.

Program-initiated cache coherency operations (such as L2 writeback and L2 writeback-invalidate operations) are submitted to the EDMA as a long string of cache operations. For block-based writeback commands, the maximum length of the cache writeback operation is under user control via the programmed address range. The length of the range writeback directly impacts the amount of time that the cache traffic may block other accesses to EMIF. The total potential block-out time equals the amount of time for the cache transfer and is calculated as follows:

Cache transfer size \* EMIF clock cycle time = Total potential block-out time

For example, if the user performs an L2 writeback operation to external memory for 2048 words with a 100-MHz EMIF, the external EMIF bus may be blocked for: 2048 words \* 10 ns  $\cong$  20 µs.

Global cache operations (such as L2 writeback-all or L2 writeback-invalidate-all) are also submitted to the EDMA as a long string of cache operations. However, the length of the global cache operation is not controllable by the user and can be as long as the depth of the L2 cache size (up to 64 Kbytes). If the user performs an L2 writeback-all operation to external memory using a 100-MHz EMIF, and L2 is set to the maximum cache size, the external EMIF bus may be blocked for 16 384 words \* 10 ns  $\cong$  160 µs. Since this can block the EMIF for long periods of time, the user should avoid using global cache operations at the same time as real-time data transfers. In general, this is not a limiting factor since global cache operations are primarily performed during system initialization, task switches, or other non real-time code segments.

As the sample rate is system-dependent, the user must calculate the time between serial samples to determine the best approach to avoid data loss. The user may break large cache operations into smaller blocks, and transmit each of these blocks using the CACHE\_wblnvL2() and CACHE\_wbL2() CSL functions. By breaking the large cache operations into smaller blocks, other peripherals are then allowed to access the EDMA.

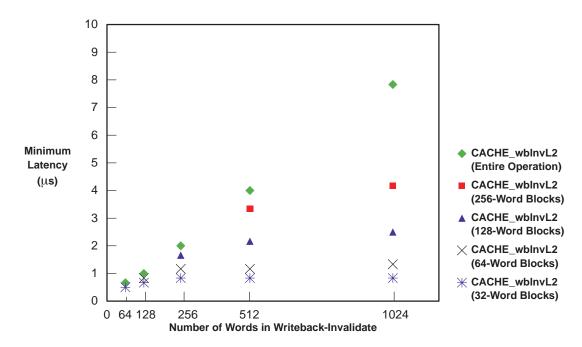

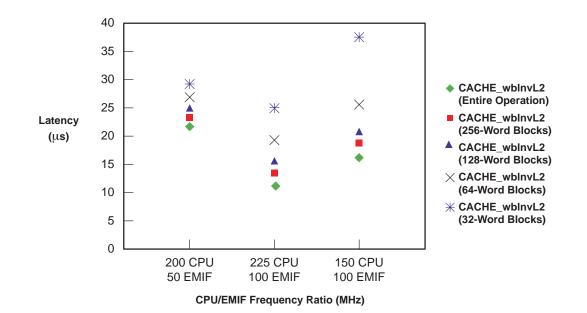

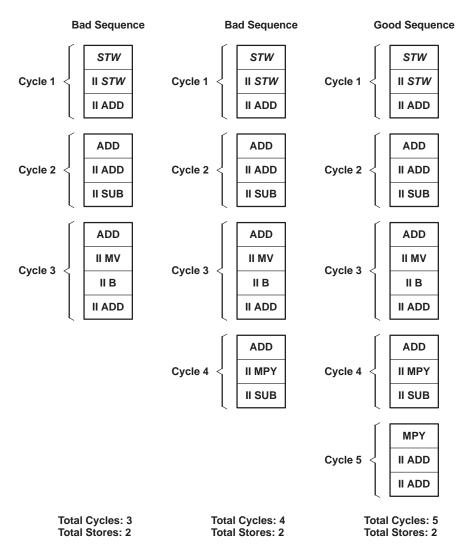

If the EMIF frequency is more than half of the CPU frequency, the device is able to service the L2 writeback requests faster than the requests can be issued, leaving some EMIF bandwidth available to service other EDMA requests, so the block-out problem is less noticeable. Therefore, breaking down cache operations into smaller blocks is more critical when the EMIF frequency is less than half of the CPU frequency. Figure 2 shows the minimum required latency between McBSP transfers to EMIF at 200-MHz CPU and 50-MHz EMIF when breaking down the cache operations. These McBSP transfers were performed with concurrent cache operations to EMIF, creating a block-out scenario. With the 1024-word cache writeback-invalidate operation broken into 32-word blocks, the McBSP is able to perform almost 10 times faster. The performance improvement is similar when breaking down the writeback-only operation.

## Figure 2. Minimum Required Latency Between McBSP Events for a Successful Transfer with Concurrent L2 Writeback-Invalidates at 200-MHz CPU and 50-MHz EMIF, Using Entire Operations and Block Breakdown

For example, if the CPU is running at 200 MHz with a 50-MHz EMIF and you have a McBSP hard real-time deadline of 5  $\mu$ s, Figure 2 shows that a 1024-word L2 writeback-invalidate may cause data loss since back-to-back McBSP events can only be serviced at ~8  $\mu$ s. By breaking down the L2 writeback-invalidate into 256-word blocks, you can then meet the 5- $\mu$ s McBSP deadline. In other words, when performing a 1024-word L2 writeback-invalidate operation with the CPU and EMIF conditions cited above, the McBSP events can be serviced in ~8  $\mu$ s for the entire operation (one whole block), in ~4  $\mu$ s when breaking it into 256-word blocks, in ~2.5  $\mu$ s when breaking it into 128-word blocks, etc.

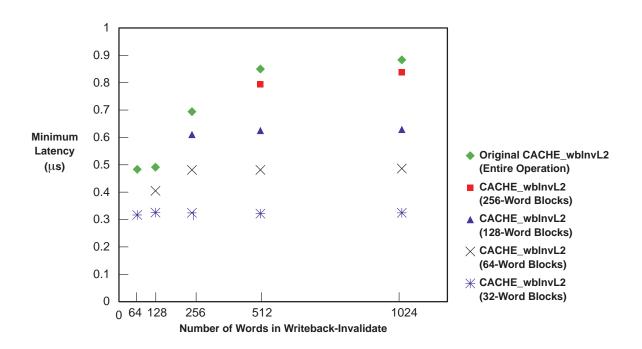

When the CPU is set to 225 MHz and the EMIF is set to 100 MHz, breaking down the cache operations will still improve the block-out problem. Figure 3 shows the improvement in the McBSP's performance with this frequency ratio.

## Figure 3. Minimum Required Latency Between McBSP Events for a Successful Transfer With Concurrent Writeback-Invalidates at 225-MHz CPU and 100-MHz EMIF, Using Entire Operations and Block Breakdown

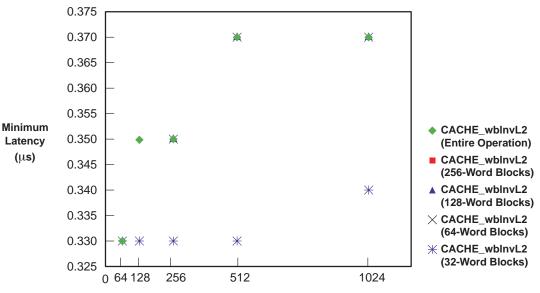

When the CPU is set to 150 MHz and the EMIF is set to 100 MHz, there is virtually no benefit from breaking down the coherency cache operations. Figure 4 shows the McBSP's performance with this frequency ratio.

Number of Words in Writeback-Invalidate

## Figure 4. Minimum Required Latency Between McBSP Events for a Successful Transfer With Concurrent Writeback-Invalidates at 150-MHz CPU and 100-MHz EMIF, Using Entire Operations and Block Breakdown

Breaking down the cache operations into smaller blocks takes longer to complete than performing the entire cache function as one large block. Figure 5 shows how much extra overhead is incurred by breaking down an L2 writeback-invalidate operation to transfer 1024 words with different sized blocks and at various frequency ratios. Notice that for the 200-MHz CPU and the 50-MHz EMIF frequency ratio, where the new functions are most critical for peripherals such as the McBSP, the least overhead is incurred.

# Figure 5. 1024-Word L2 Writeback-Invalidate Performance at Various Frequency Ratios With Old and New CACHE-wblnvL2()

To avoid cache operations blocking other time-sensitive EDMA accesses, observe the following guidelines:

- 1. Avoid placing real-time data in EMIF address range. Instead, real-time data should be placed in the L2 address range.

- 2. If data must be placed in the EMIF address range:

- Avoid global cache operations in favor of block-based cache operations.

- Block-based cache operations should be submitted in small blocks, such that the total amount of time that the EMIF is blocked is less than the amount of time between serial samples.

### C671x/C621x Asynchronous Writes Setup Timing (C671x/C621x Devices: All Silicon Revisions)

For a C671x/C621x asynchronous write cycle, the address (EA) and strobe ( $\overline{CE}$  and  $\overline{BE}$ ) signals have setup time or WRSETUP cycles as programmed in the EMIF CE Control Register. However, the data lines (ED) may become valid one cycle later than the address (EA) and strobe ( $\overline{CE}$  and  $\overline{BE}$ ) signals. In other words, the setup period of the ED may be one cycle less than the programmed value in the WRSETUP field of the EMIF CE Control Register. The exact ED setup timing depends on the access width and EMIF bus width as follows:

- Access Size ≤ EMIF Bus Width

- For EMIF access size less than or equal to the EMIF bus width, every asynchronous write has data line (ED) setup of one less than the programmed value in the WRSETUP field of the CE Control Register. For example, for every 32-bit access (CPU instruction STW) on a 32-bit-wide EMIF, the ED setup is one cycle less than the value programmed in the WRSETUP field, while the CE, BE, and EA setup are exactly as programmed in the WRSETUP field.

- Access Size > EMIF Bus Width

- For EMIF access size greater than the EMIF bus width, the first write will have ED setup one cycle less than the programmed value in the WRSETUP field. Remaining writes for the same write command will have ED setup matching the WRSETUP field. The CE, BE, and EA setup are also exactly as programmed in the WRSETUP field. For example, for every 32-bit access (CPU instruction STW) on an 8-bit-wide EMIF, the ED setup for the first byte is one cycle less than the value programmed in the WRSETUP field, but the ED setup for the remaining three bytes is exactly as programmed in the WRSETUP field.

Therefore, users should configure the WRSETUP field properly to ensure sufficient ED setup time. For example, if ED setup requires 3 cycles, the WRSETUP field should be programmed to 4.

## 2.2 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications

| Advisory 3.1.1        | EMIF: Async Read Setup Uses Write Setup Value                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1.0, 1.1, 2.1, 2.2, 3.0, and 3.1                                                                                                                                                                                        |

| Details:              | When the EMIF is performing read from async memory and write to SDRAM continuously, the EMIF sometimes incorrectly uses the async's Write Setup (CECTLx[31:28]) as its Read Setup (CECTLx[19:16]) value.                |

|                       | This advisory only applies when EMIF reads from async memory and performs accesses to SDRAM. Other modes are not affected.                                                                                              |

| Workaround:           | Use the <i>same r</i> ead setup and write setup value in the appropriate fields of CE Space Control Register (CECTLx).                                                                                                  |

| Advisory 3.1.2        | EMIF: Control Signals Not Inactive Before Asserting HOLDA                                                                                                                                                               |

| Revision(s) Affected: | 1.0, 1.1, 2.1, 2.2, 3.0, and 3.1                                                                                                                                                                                        |

| Details:              | Within the same EMIF clock cycle as the HOLDA signal is asserted, the EMIF deasserts its control signals. This may cause the control signals to be floating in asserted state, and may cause undesired memory accesses. |

|                       | This advisory only applies if the HOLDA signal is used.                                                                                                                                                                 |

## TMS320C6211/TMS320C6211B Silicon Errata

**Workaround**: Connect a weak pull up resistor (~1K) to each  $\overline{CE}$  pin where  $\overline{HOLDA}$  signal is used.

| Advisory 3.1.3        | EMIF: One Cycle Asynchronous Write Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1.0, 1.1, 2.1, 2.2, 3.0, and 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:              | The EMIF may give only one EMIF clock cycle of async write setup, instead of the value programmed in the EMIF CE Space Control Register. This condition <i>only</i> occurs when an async write is issued while there is an ongoing async read within the same or different CE space. This may result in async write data corruption if the setup/strobe time of the async memory is not met.                                                                                                                                                                                      |

| Workaround:           | For robust operation, it must be assumed that in the above condition, the EMIF gives only one EMIF clock cycle of write setup to async memory, independent of the write setup value programmed in the CE Space Register. Most asynchronous memory latches write data at the rising edge of WE, which sometimes can workaround the problem. Therefore, care must be taken such that write setup (one cycle) + write strobe (programmable) meets the write setup/strobe requirement of the async memory. Slowing down the EMIF clock may be needed to ensure that the timings meet. |

| Advisory 3.1.4        | JTAG: Boundary Scan Shift-DR Register Is Latched on the Falling Edge of TCK                                                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 3.0 and 3.1                                                                                                                                                                                                            |

| Details:              | The Boundary Scan Shift-DR Register is latched on the falling edge of TCK, instead of the rising edge of TCK. This causes boundary scan hardware/software to see an extra cell when the chip is in boundary scan mode. |

| Workaround:           | The BSDL files for this part have been modified to reflect this advisory.                                                                                                                                              |

| Advisory 3.1.5        | EDMA/L2 Controller: Potential EDMA Lockout From L2 SRAM                                                                                                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 1.0, 1.1, 2.1, 2.2, 3.0, and 3.1                                                                                                                                                                                                                                                                                  |

| Details:              | Under certain conditions, an EDMA transfer can be denied the use of L2 for a longer period of time than expected. This can cause the EDMA to miss data transfers that have real-time service requirements (such as certain serial port transfers). This condition may manifest itself in the following phenomena: |

|                       | McBSP transmits repeated data (transmit underrun)                                                                                                                                                                                                                                                                 |

|                       | McBSP receives data late or misses data                                                                                                                                                                                                                                                                           |

|                       |                                                                                                                                                                                                                                                                                                                   |

• Audio channels in TDM mode "rotate"

- EDMA transfers triggered by timers or external interrupts do not happen or happen late

- EDMA transfers take longer than expected

- EDMA events are missed

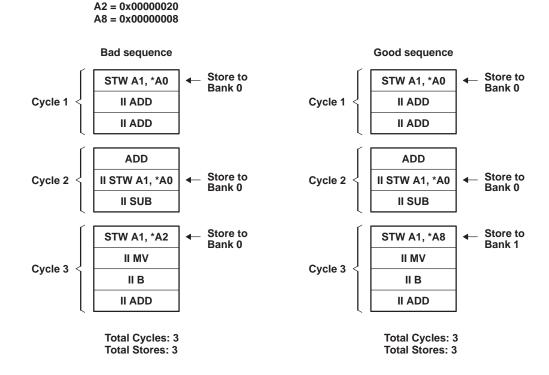

This problem is very sensitive to code/execution alignment. Any minor edit to code can make the problem seem to disappear. The scenario is *only* applicable when *all* of the following five conditions are true:

- 1. L2 is allocated as *both* cache and SRAM.

- 2. EDMA is transferring into or out of L2 SRAM

- 3. There is an L1P miss that also misses in L2, and must be fetched from external memory

- 4. This "missed" instruction is immediately followed by a section of code that produces a flood of stores that miss L1D, but hit in L2 cache or L2 SRAM

- 5. The "flood of stores" happens at a rate of at least 1 every other CPU cycle

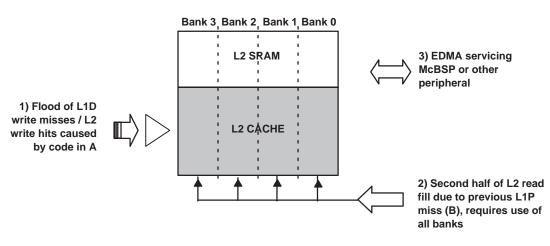

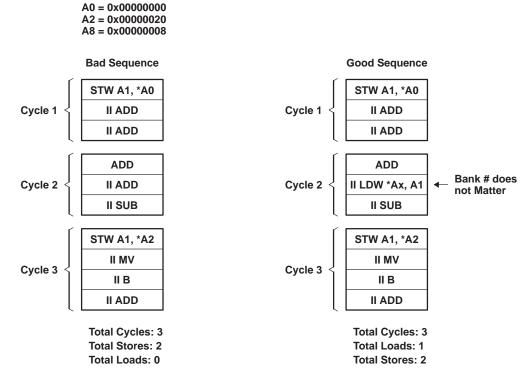

In this scenario, the next CPU fetch packet does not reside in either L1P or L2 cache; therefore, it causes an L1P and L2 miss. An L2 cache line (128 bytes, 4 fetch packets) must be fetched from external memory. The fetch from external memory is split into two requests (two halves) of 64 bytes, or two fetch packets each. In this document, the two halves are labeled A and B, respectively, as shown in Figure 6. The first half (A) to arrive in L2 is the half in which the missed fetch packet resides. This first half is immediately forwarded to L1P so that CPU can resume execution before the second half (B) is fetched from external memory. The second half of the L2 line (B) is to be fetched and written to L2 later.

L2

EDMA/L2 Controller: Potential EDMA Lockout From L2 SRAM (Continued)

Note: The #) Indicates the order of Occurrence/Priority

## Figure 6. Problem Scenario

At this time, the CPU executes the newly returned code in A (in the first 2 fetch packets returned). The cache architecture increases write throughput by not performing write-allocate in case of L1D miss. All CPU stores that miss in L1D are sent directly to L2. This code in A contains a series (flooding) of stores that miss L1D, but hit in L2. These stores are generated at a rate of at least 1 every other cycle.

The lockout condition occurs only when the second half (B) of the L2 cache line fill starts. When the B is ready, it attempts to write to L2. It will be unable to do so, however, because the line fill operation accesses all four banks of L2 whereas one bank is always busy servicing the higher priority L1D misses from the code in A. Thus, the line fill (B) cannot complete until the flood of writes from A has stopped. The line fill stays at the head of queue in the EDMA controller, so any other EDMA transfers that access L2 will also be blocked until the flood of stores has stopped *and* the L2 line fill (B) has completed.

The amount of time that an EDMA transfer is locked out of L2 is determined by the code running on the DSP (A), and ultimately by the amount of time that L1D write misses are happening in succession. When all of the conditions are met, the second half of the L2 line fill and the EDMA will be locked out of L2 as long as the flood of stores is sustained.

Certain library functions that satisfy all of the above problem conditions may fall into this EDMA lockout problem. As an example, the memcpy library routine involves a series of CPU writes at a rate >= 1 write per every 2 cycles. THE EDMA lockout problem may exist if all other conditions are satisfied. The workarounds stated below may also be used in this case.

| <ul> <li>They access external memory directly, and lockout does not occur. Since the DSP does not keep external coherency, L1/L2 caches do not know of external memory being modified. If this section in external memory is cached, frequent cache cleans may be needed so that the caches are coherent with external memory.</li> <li>If L2 is all SRAM, then there will not be second half of L2 fill (B). When there is L11 miss, L2 controller will only fetch L1P line size in a single request. The cache line i immediately passed to L1P by the L2 controller.</li> <li>The flooding of write misses by itself cannot lock out the EDMA from L2 for an extended period of time. The EDMA and the write misses can access L2 concurrently, provided that EDMA and the L1D write misses access different L2 banks.</li> <li>NOTE: The lockout does not occur for L1D read misses in A that hit or miss in the L2. If an L1D read miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores happening by stalling the CPU until the entire L2 line fill has completed.</li> <li>Workaround:</li> <li>If the problem exists, perform the following steps:         <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> </ol> </li> <li>Software Workaround         Code Modification:         <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.         </li> <li>Make sure that any algorithm or c</li></ul></li></ul> |             | EDMA/L2 Controller: Potential EDMA Lockout From L2 SRAM (Continued)                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>They access external memory directly, and lockout does not occur. Since the DSP does not keep external coherency, L1/L2 caches do not know of external memory being modified. If this section in external memory is cached, frequent cache cleans may be needed so that the caches are coherent with external memory.</li> <li>If L2 is all SRAM, then there will not be second half of L2 fill (B). When there is L11 miss, L2 controller will only fetch L1P line size in a single request. The cache line i immediately passed to L1P by the L2 controller.</li> <li>The flooding of write misses by itself cannot lock out the EDMA from L2 for an extended period of time. The EDMA and the write misses can access L2 concurrently, provided that EDMA and the L1D write misses access different L2 banks.</li> <li>NOTE: The lockout does not occur for L1D read misses in A that hit or miss in the L2. If an L1D read miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores happening by stalling the CPU until the entire L2 line fill has completed.</li> <li>Workaround:</li> <li>If the problem exists, perform the following steps:         <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> </ol> </li> <li>Software Workaround         Code Modification:         <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.         </li> <li>Make sure that any algorithm or c</li></ul></li></ul> | Exceptions: | The lockout problem does not exist if L2 is configured to be all cache or all SRAM:                                                                                                                                                                                                                                                                                                      |

| <ul> <li>miss, L2 controller will only fetch L1P line size in a single request. The cache line i immediately passed to L1P by the L2 controller.</li> <li>The flooding of write misses by itself cannot lock out the EDMA from L2 for an extended period of time. The EDMA and the write misses can access L2 concurrently, provided that EDMA and the L1D write misses access different L2 banks.</li> <li>NOTE: The lockout does not occur for L1D read misses in A that hit or miss in the L2. If an L1D read miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores happening by stalling the CPU until the entire L2 line fill has completed.</li> <li>Workaround: If the problem exists, perform the following steps:         <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>A the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> </ol> </li> <li>Software Workaround         <ol> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write misse severy other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses that the second half of the L2</li> </ol> </li></ul>                                                                                                                                                                        |             | They access external memory directly, and lockout does not occur. Since the DSP does not keep external coherency, L1/L2 caches do not know of external memory being modified. If this section in external memory is cached, frequent cache cleans                                                                                                                                        |

| <ul> <li>period of time. The EDMA and the write misses can access L2 concurrently, provided that EDMA and the L1D write misses access different L2 banks.</li> <li>NOTE: The lockout does not occur for L1D read misses in A that hit or miss in the L2. If an L1D read miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores happening by stalling the CPU until the entire L2 line fill has completed.</li> <li>Workaround: If the problem exists, perform the following steps:         <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> </ol> </li> <li>Software Workaround         <ol> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             |             | miss, L2 controller will only fetch L1P line size in a single request. The cache line is                                                                                                                                                                                                                                                                                                 |

| <ul> <li>miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores happening by stalling the CPU until the entire L2 line fill has completed.</li> <li>Workaround: If the problem exists, perform the following steps: <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> </ol> </li> <li>Software Workaround</li> <li>Code Modification: <ol> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> </ol> </li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | period of time. The EDMA and the write misses can access L2 concurrently, provided that the                                                                                                                                                                                                                                                                                              |

| <ol> <li>Use the simulator tool described below to detect and pinpoint locations of potential problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> <li>Software Workaround</li> <li>Code Modification:         <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | NOTE: The lockout does not occur for L1D read misses in A that hit or miss in the L2. If an L1D read miss hits in L2, there is no L2 line fill to trigger the problem. Lockout also cannot happen if an L1D read miss also misses L2. For coherency reason, in this case L2 prevents the flood of stores from happening by stalling the CPU until the entire L2 line fill has completed. |

| <ul> <li>problems.</li> <li>At the code locations where the simulator points, perform the software workarounds described below.</li> <li>Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> <li>Software Workaround</li> <li>Code Modification: <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Workaround: | If the problem exists, perform the following steps:                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>described below.</li> <li>3. Apply the compiler tools workaround described below. Use this step <i>only</i> if no other workaround is feasible.</li> <li>Software Workaround</li> <li>Code Modification: <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>workaround is feasible.</li> <li>Software Workaround</li> <li>Code Modification: <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther<br/>This will allocate them in L1D, preventing the L1D write misses from occurring. Re<br/>that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin<br/>writes inserts gaps in the write sequence such that writes occur at a frequency slo<br/>than 1 write miss every other cycle. The term "long" is based on the system<br/>requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Code Modification:</li> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther<br/>This will allocate them in L1D, preventing the L1D write misses from occurring. Re<br/>that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin<br/>writes inserts gaps in the write sequence such that writes occur at a frequency slo<br/>than 1 write miss every other cycle. The term "long" is based on the system<br/>requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Avoid the flood of L1D write misses. Pre-read all data locations prior to writing ther<br/>This will allocate them in L1D, preventing the L1D write misses from occurring. Re<br/>that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin<br/>writes inserts gaps in the write sequence such that writes occur at a frequency slo<br/>than 1 write miss every other cycle. The term "long" is based on the system<br/>requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | Software Workaround                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>This will allocate them in L1D, preventing the L1D write misses from occurring. Re that L1D read misses do not cause problems.</li> <li>Make sure that any algorithm or code segment that naturally produces a long strin writes inserts gaps in the write sequence such that writes occur at a frequency slo than 1 write miss every other cycle. The term "long" is based on the system requirements. Gaps in the L1D write misses means that the second half of the L2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | Code Modification:                                                                                                                                                                                                                                                                                                                                                                       |

| writes inserts gaps in the write sequence such that writes occur at a frequency slo<br>than 1 write miss every other cycle. The term "long" is based on the system<br>requirements. Gaps in the L1D write misses means that the second half of the L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | This will allocate them in L1D, preventing the L1D write misses from occurring. Recall                                                                                                                                                                                                                                                                                                   |

| fill is given a chance to access L2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | writes inserts gaps in the write sequence such that writes occur at a frequency slower                                                                                                                                                                                                                                                                                                   |

EDMA/L2 Controller: Potential EDMA Lockout From L2 SRAM (Continued)

Code Location:

- Run the algorithm or code segment that contains A from internal SRAM. There will not be L2 code read fill (A or B) coming into L2. The simulator can be used to detect such code segment. See simulator section below for details.

- Ensure the problematic segment of algorithm or code is in cache. This can be accomplished by issuing any CPU read/load instruction from the beginning of the problematic code segment in external memory, that will cause both L1D and L2 miss. Assuming the code segment is not yet in L1/L2 cache, Performing CPU load instruction generates an L1D request, and CPU stalls until the code missed and data is returned from L2. After the load instruction, code segment will reside in the L2 cache, and an L2 read fill due to L1P miss will not occur.

### Tools

### C6x1x Simulator

The simulator can be used to detect potential EDMA lock-out problem. This capability is featured in the simulator as part of Code Composer Studio version 2.1 package.

This version of simulator includes the detection logic to monitor the amount of CPU stores that miss in L1D but hit in L2 cache or SRAM, which could possibly lock out the EDMA from accessing L2 because of the conditions described above.

The user can input a window size limit (*W*) in which the stores are monitored. During simulation run, if *W*/2 or more of such stores occur within *W* cycles, simulator will halt and a warning message will be printed. A log file is automatically generated and stored as "L2\_write\_hits.log" in the CCS "Start in Directory" (default to MYPROJECTS). The user can run past the warning to find other potential problems, but the log file will have only the last case detected.

There are two ways to activate this capability: