# TI Designs 100-A Current Source Reference Design Using Two Power Modules in Parallel

# TEXAS INSTRUMENTS

# **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

# **Design Resources**

#### TIDA-00582 PTH08T250W

Tool Folder Containing Design Files Product Folder

ASK Our E2E Experts WEBENCH® Calculator Tools

### **Design Features**

- Facilitates low supply voltages at very high DC currents at 100 A or more

- Low external component count

- High power density in a small package

- High-current design using a fully tested and qualified power module

### **Featured Applications**

- FPGA Core Rails

- Blade Servers

- Telecom Base Stations

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

#### 1 Description

Powering servers and memory cards requires the generation of low supply voltages at very high DC currents approaching 100 A or more. In addition to the high-current supply requirements, dynamic load requirements are extremely demanding. The load may quickly go from an inactive low-current state to a fully processing high-current state while requiring precise voltage regulation.

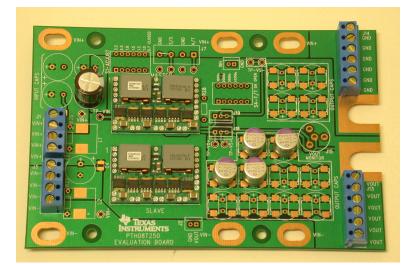

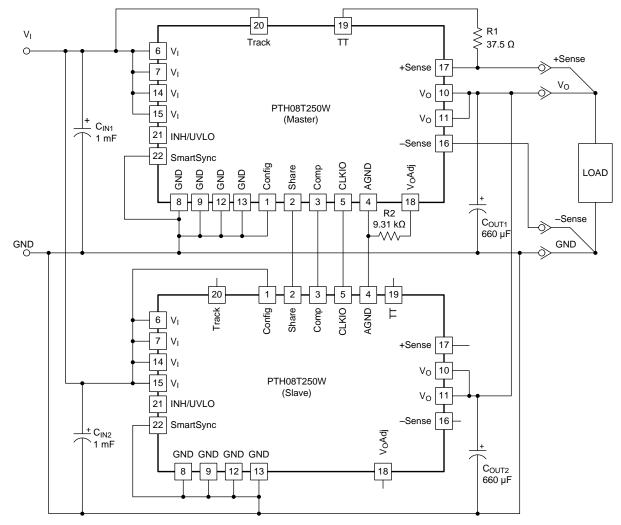

A stand-alone, dual-phase power module like the Texas Instruments (TI) PTH08T250W can supply up to 50 A of output load current. However, the PTH08T250W incorporates a stackable controller feature that allows the outputs of multiple modules to be connected in parallel, thereby producing a reliable solution capable of supplying a load current of 100 A or more. Configuring a PTH08T250W as a master and each additional module as a slave allows start-up and transient conditions to be controlled by a single module. Figure 10 shows a typical two-module solution where all of the features and inputs are controlled by the master device while the slave inputs are left open.

#### 2 **Design Features**

The PTH08T250W operates over a wide 4.5- to 14-V input voltage range and generates a positive output voltage of 0.7 to 3.6 V. Additionally, the PTH08T25xW family of power modules is designed to meet a very tight 1.5% DC tolerance, deliver exceptional transient response, and have the ability to synchronize to an external frequency.

#### 3 Specifications

#### **Table 1. Operating Parameters**

|                        | PARAMETER      | TEST CONDITIONS | MIN | TYP MAX | UNIT |  |

|------------------------|----------------|-----------------|-----|---------|------|--|

| INPUT CHARACTERISTICS  |                |                 |     |         |      |  |

| V <sub>IN</sub>        | Input voltage  |                 | 4.5 | 14      | V    |  |

| OUTPUT CHARACTERISTICS |                |                 |     |         |      |  |

| V <sub>OUT</sub>       | Output voltage |                 | 0.7 | 3.6     | V    |  |

| I <sub>OUT</sub>       | Output current |                 |     | 100     | А    |  |

# 4 Test Data

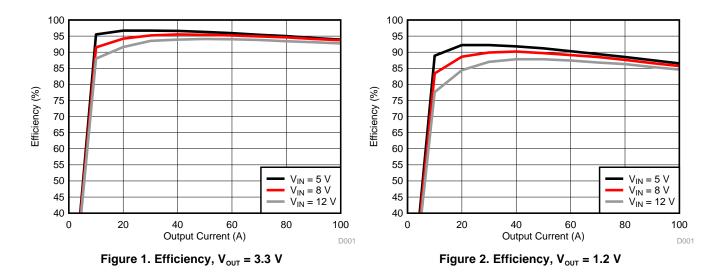

# 4.1 Efficiency

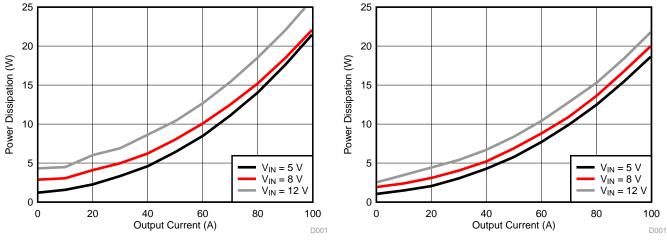

# 4.2 Power Dissipation

Figure 3. Power Dissipation, V<sub>out</sub> = 3.3 V

Figure 4. Power Dissipation, V<sub>out</sub> = 1.2 V

Test Data

www.ti.com

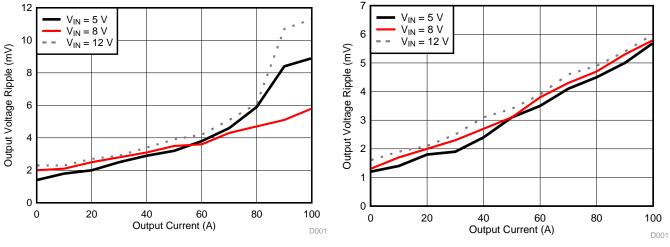

# 4.3 Output Voltage Ripple

Figure 5. Output Voltage Ripple,  $V_{out}$  = 3.3 V

Figure 6. Output Voltage Ripple, V<sub>out</sub> = 1.2 V

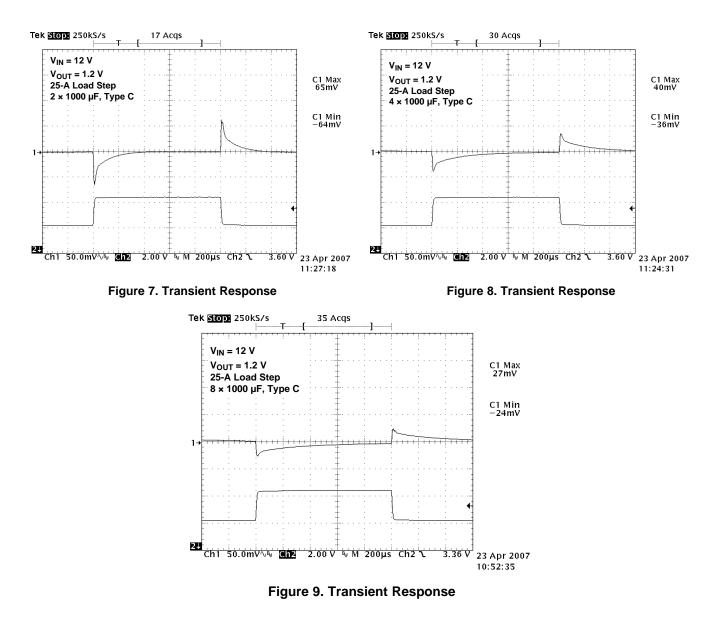

# 4.4 Transient Response Waveforms

Design Files

#### www.ti.com

# 5 Design Files

# 5.1 Schematic

Figure 10. 100-A Current Source Design Schematic

To download the full EDA schematic, see the design files at TIDA-00582.

# 5.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00582.

# 5.3 PCB Layout

6

Pay special attention to the board layout for this parallel application. These items determine the amount of current each solution can deliver:

- amount of board space

- number of layers

- amount of copper

- A careful layout maintains the interconnection pins as clean as possible.

- Route the power planes, (V<sub>IN</sub>, V<sub>OUT</sub>, and GND) to the power pins in a tight, short, and wide path.

- Prevent the VIN plane from running above or below the V<sub>out</sub> plane wherever possible helps reduce

overall switching noise.

- Maintain a short and tight path from the output of each module to the load minimizes losses.

- Route the +Sense and –Sense connections to the load in a direct path, closely coupled with one another. The layout around these traces should be isolated as much as possible to avoid picking up switching noise. Additionally, connecting the ±Sense lines through a surface-mount resistor to the load allows a resistor with a value between 1 Ω and 2 Ω to be placed in the sense path to aid in filtering.

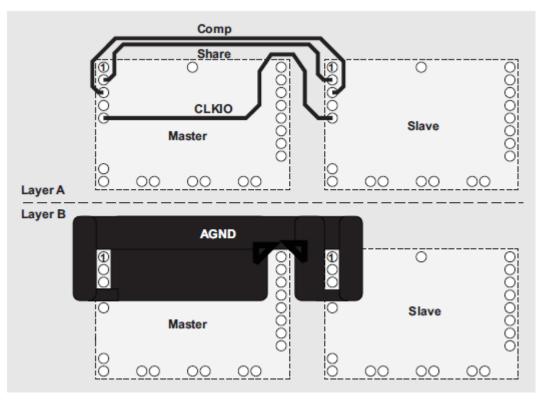

- Ensure to isolate the three interconnection traces (Share, Comp, and CLKIO) from the rest of the board to prevent switching noise from aggravating the signals to the slave modules.

- Because AGND acts as a shield ensure that it runs on an adjacent layer to the other three traces.

- Route the CLKIO trace to maintain a slight distance from the Comp trace to reduce the chance of clock pulses disturbing the Comp signal.

- See Figure 11 for an example layout of the interconnection pins. The three interconnection traces are routed on one layer, and the AGND is routed as a copper area that shields the three traces on an adjacent layer. When multiple modules are operated in parallel, an eight-layer layout with 2-oz. copper is recommended to improve thermal conduction. Increased copper thickness is required to distribute the higher current over the power planes. Increased airflow is also strongly recommended to help the copper remove the heat associated with the higher power solution.

Figure 11. Board Layout Interconnection Pins

# 5.3.1 Parallel Connections

When multiple modules are operated in parallel, the control of each device feature is set only on the master device. A device is configured as a master by connecting the Config pin to the power GND. All slave devices must connect the Config pin to VIN. The slave devices must leave all other control pins open (connect the SmartSync pin to the GND). See Table 2 for pin connections of the master and slave modules. See Figure 11 in the Section 5.3 section.

| PIN NAME                | MASTER                                                                               | SLAVE                              |  |

|-------------------------|--------------------------------------------------------------------------------------|------------------------------------|--|

| V <sub>IN</sub>         | Connect to the input bus.                                                            | Connect to the input bus.          |  |

| V <sub>OUT</sub>        | Connect to the output bus.                                                           | Connect to the output bus.         |  |

| GND                     | Connect to the common power GND.                                                     | Connect to the common power GND.   |  |

| INH/UVLO                | Use for inhibit control and UVLO adjustment. If unused, leave open-<br>circuit.      | No connection. Leave open-circuit. |  |

| V <sub>OUT</sub> Adjust | Use to set the output voltage. Connect $R_{SET}$ resistor between this pin and AGND. | No connection. Leave open-circuit. |  |

| +Sense                  | Connect to the output voltage either at the load or at the module.                   | No connection. Leave open-circuit. |  |

| –Sense                  | Connect to the output GND either at the load or at the module.                       | No connection. Leave open-circuit. |  |

| Track                   | Connect to Track control. If unused, connect to VIN.                                 | No connection. Leave open-circuit. |  |

| TurboTrans              | Connect TurboTrans resistor, RTT, between this pin and +Sense pin.                   | No connection. Leave open-circuit. |  |

| SmartSync               | Connect to an external clock. If unused, connect to GND.                             | Connect to the common power GND.   |  |

| Config                  | Connect to the common power GND.                                                     | Connect to the input bus.          |  |

| Share                   | Connect to pin 2 of the slave.                                                       | Connect to pin 2 of the master.    |  |

| Comp                    | Connect to pin 3 of the slave.                                                       | Connect to pin 3 of the master.    |  |

| AGND                    | Connect to pin 4 of the slave.                                                       | Connect to pin 4 of the master.    |  |

| CLKIO                   | Connect to pin 5 of the slave.                                                       | Connect to pin 5 of the master.    |  |

Table 2. Master and Slave Pin Connections

To download the layer plots, see the design files at TIDA-00582.

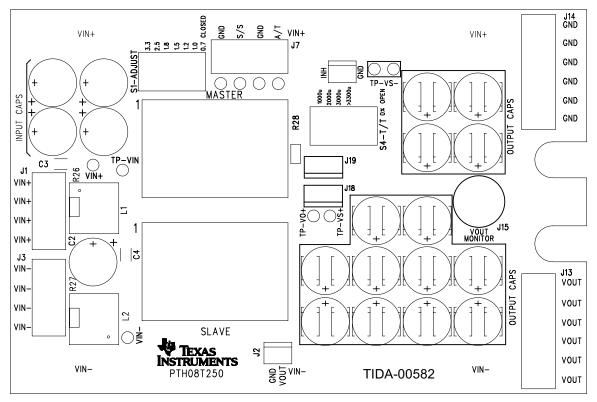

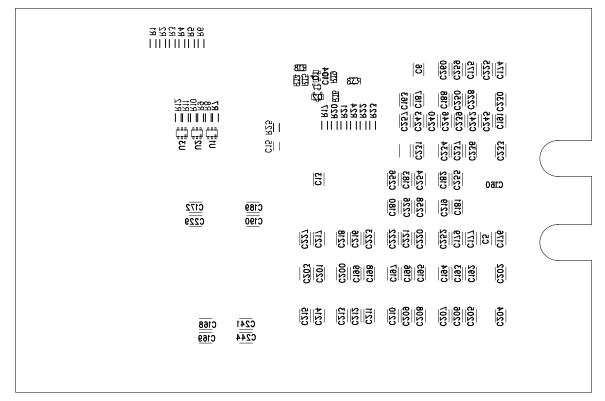

# 5.4 TIDA-00582 Assembly Drawing and PCB Layout

Figure 12. Top Layer (Top View)

Figure 13. Bottom Layer (Bottom View)

# 5.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00582

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated