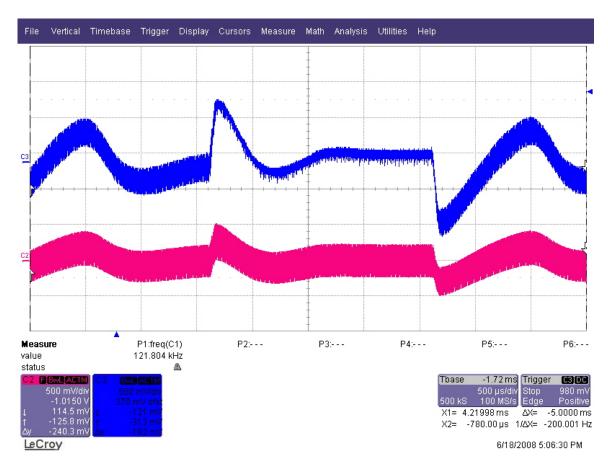

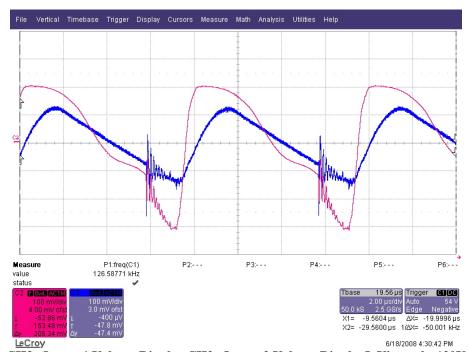

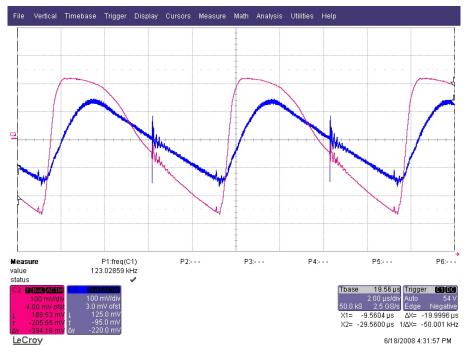

### 1 Main Waveforms

The converter is operating in Discontinuous Mode in all its range of operation, from minimum to maximum main peak input Voltage, at full Output load, 50mA Output1 (5V), 100mA Output2 (13.5V). Switching frequency is fs=125kHz. Duty cycle is D=0.37 at 120V peak input, D=0.11 at 375V peak input.

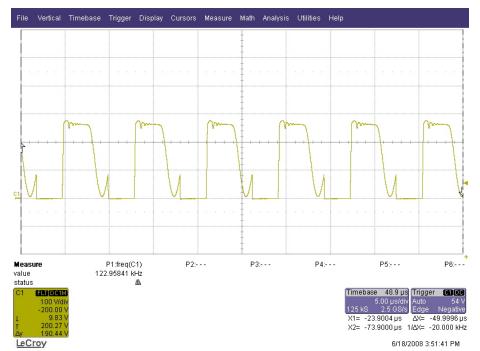

Primary Drain Voltage @ Vin peak=120V, 5V-50mA, 13.5V-100mA output

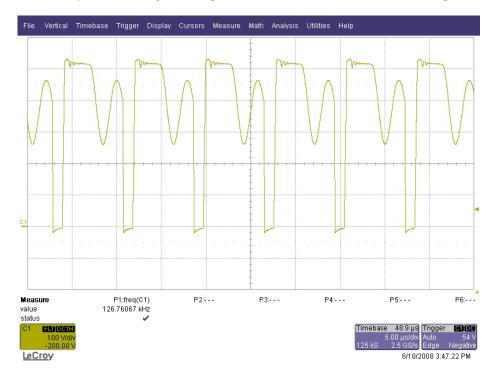

Primary Drain Voltage @ Vin peak=375V, 5V-50mA, 13.5V-100mA output

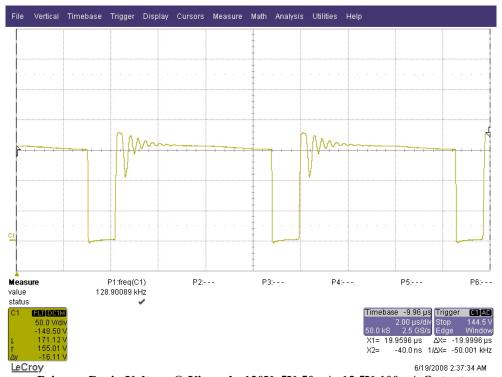

Primary Drain Voltage @ Vinpeak=120V, 5V-50mA, 13.5V-100mA Output when Output1 is shorted (Vout1<0.2V). The current limitation is set at Iout1=250mA @ Iout2=100mA. Same value for Iout2 limitation @ Iout1=50mA

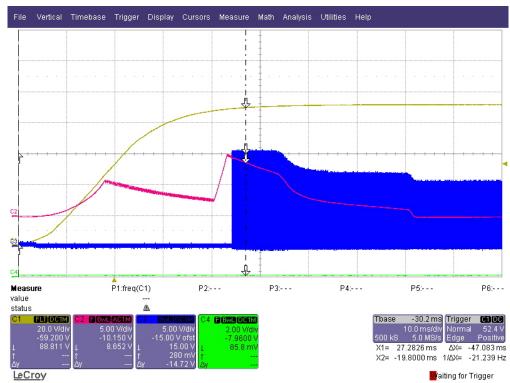

Start-up waveforms of the circuit, with connected Output full loads @ Vinpeak=90V. CH1 is Input Voltage (DC), CH2 is BIAS, CH3 is Primary Mosfet Gate pulsing

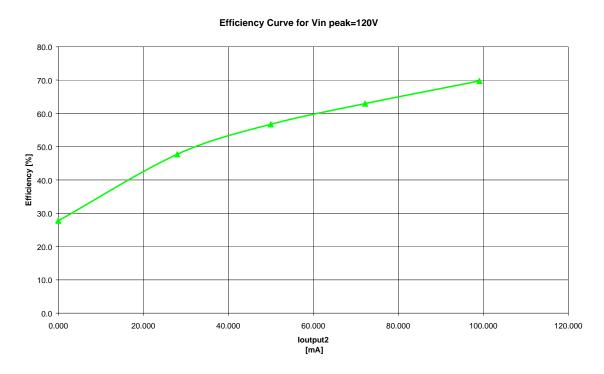

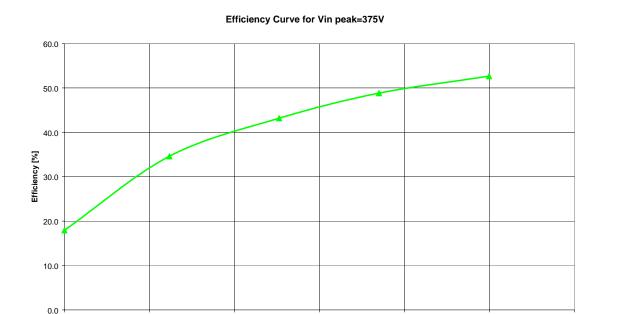

# 2 Efficiency and Load Regulation

The efficiency diagrams are shown in the figures below for the minimum (120V), and maximum (375V) peak Input Voltage, as a function of the Output2 current.

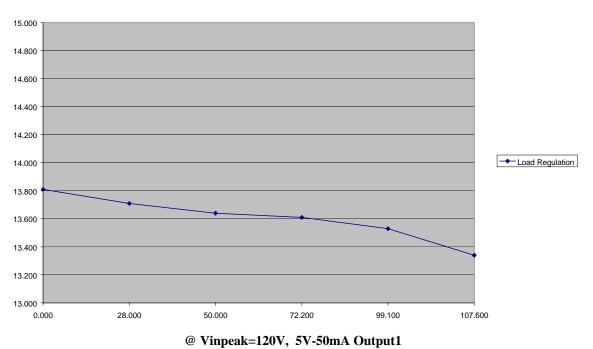

The following table shows the measured values for <u>Vin peak=120V</u>:

| Vin[V] | lin[mA] | Vout1[V]          | Vout2[V] | lout1[mA] | lout2[mA] | Pin[W] | Pout1[W] | Pout2[W] | η%   |

|--------|---------|-------------------|----------|-----------|-----------|--------|----------|----------|------|

| 119.90 | 7.700   | 5.157             | 13.810   | 49.700    | 0.000     | 0.923  | 0.256    | 0.000    | 27.8 |

| 120.20 | 11.200  | 5.156             | 13.710   | 50.100    | 28.000    | 1.346  | 0.258    | 0.384    | 47.7 |

| 119.90 | 13.800  | 5.158             | 13.640   | 49.700    | 50.000    | 1.655  | 0.256    | 0.682    | 56.7 |

| 120.20 | 16.400  | 5.156             | 13.610   | 50.100    | 72.200    | 1.971  | 0.258    | 0.983    | 63.0 |

| 119.90 | 19.100  | 5.157             | 13.530   | 49.700    | 99.100    | 2.290  | 0.256    | 1.341    | 69.7 |

|        |         |                   |          |           |           |        |          |          |      |

| 119.00 | 18.700  | 5.156             | 13.340   | 25.400    | 107.600   | 2.225  | 0.131    | 1.435    | 70.4 |

| 100.10 | 4.000   | 5 45 <del>5</del> | 40.000   |           |           | 0.504  | 0.000    | 0.000    |      |

| 120.10 | 4.200   | 5.157             | 13.300   | 0.000     | 0.000     | 0.504  | 0.000    | 0.000    | 0.0  |

Last value is taken with both Outputs open to verify Output Voltage Regulation in that condition.

0.000

100.000

120.000

60.000

loutput2 [mA] 80.000

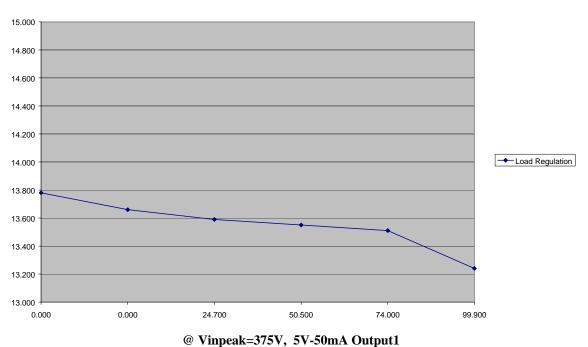

The following table shows the measured values for **Vin peak=375V**:

40.000

20.000

| Vin[V] lin[mA] Vout1[V] Vout2[V] lout1[mA] lout2[mA] Pin[W] Pout1[W] Po | ut2[W] η%         |

|-------------------------------------------------------------------------|-------------------|

| <b>376.70</b> 3.800 <b>5.157 13.780 49.800 0.000</b> 1.431 0.257 0      | 0.000 <b>17.9</b> |

| <b>374.20</b> 4.600 <b>5.157 13.660 50.100 24.700</b> 1.721 0.258 0     | 0.337 <b>34.6</b> |

| <b>376.70</b> 5.800 <b>5.158 13.590 49.800 50.500</b> 2.185 0.257 0     | 0.686 <b>43.2</b> |

| <b>374.20</b> 6.900 <b>5.158 13.550 50.100 74.000</b> 2.582 0.258 1     | 1.003 <b>48.8</b> |

| <b>376.70</b> 8.100 <b>5.158 13.510 49.800 99.900</b> 3.051 0.257 1     | 1.350 <b>52.7</b> |

| 274.20 7.000 <b>F.456 42.240 25.400 407.600</b> 2.056 0.424 4           | 1 40F <b>F3 6</b> |

| <b>374.20</b> 7.900 <b>5.156 13.240 25.400 107.600</b> 2.956 0.131 1    | 1.425 <b>52.6</b> |

| <b>375.20</b> 3.100 <b>5.159 13.300 0.000 0.000</b> 1.163 0.000 0       | <b>0.0</b> 0.0    |

Last value is taken with both Outputs open to verify Output Voltage Regulation in that condition.

#### Output2 Load Regulation for Vinpeak=120V

#### Output2 Load Regulation for Vinpeak=375V

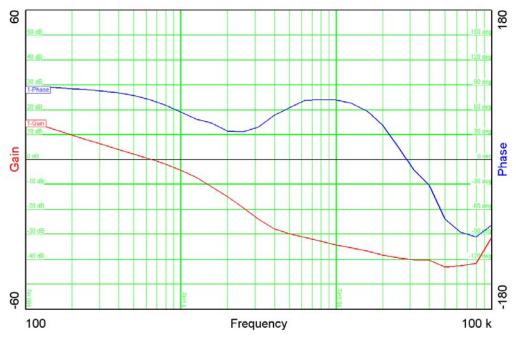

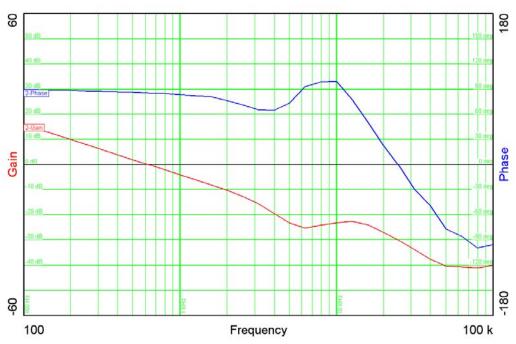

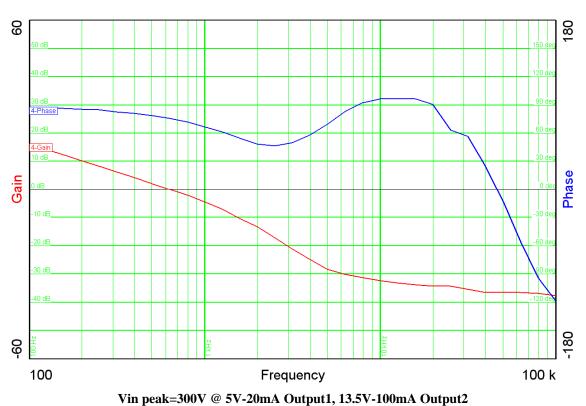

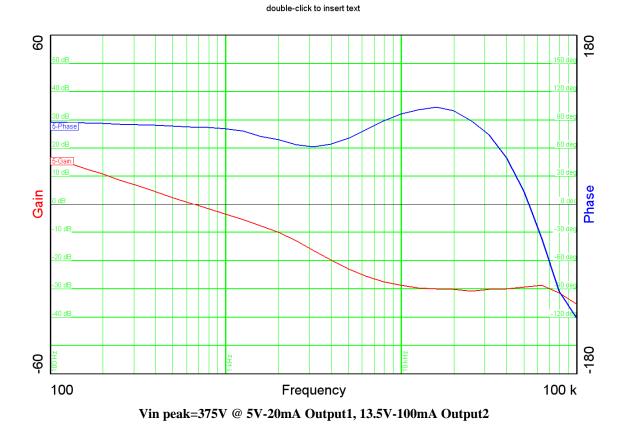

# 3 Control Loop Frequency Response

The figures below show the open loop response at full load on Output1 and Output2, for the minimum, at Vin peak=200V, Vin peak=300V and maximum peak Input Voltages.

Vin peak=120V @ 5V-20mA Output1, 13.5V-100mA Output2

double-click to insert text

Vin peak=200V @ 5V-20mA Output1, 13.5V-100mA Output2

double-click to insert text

cuk-200 v e 2 v 20mmi Outputi, 15.2 v 100mmi

### 4 Load Transients

The figures below show the response to load transients. The current on Output2 is stepping from no load to full 100mA load and viceversa, with Output1 at full load.

CH2 5V-20mA Output1, CH3 13.5V stepping load Output2

# 5 Output Ripple Voltage

The output ripple voltage is shown in the figure below, for the two Outputs at full load.

CH3: Output1 Voltage Ripple, CH2: Output2 Voltage Ripple @ Vin peak=120V

CH3: Output1 Voltage Ripple, CH2: Output2 Voltage Ripple @ Vin peak=375V

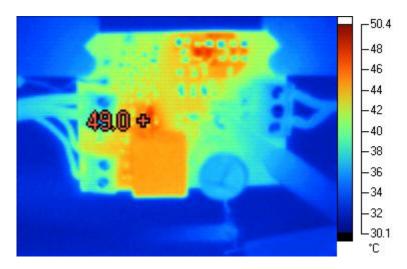

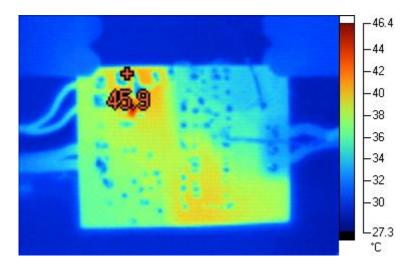

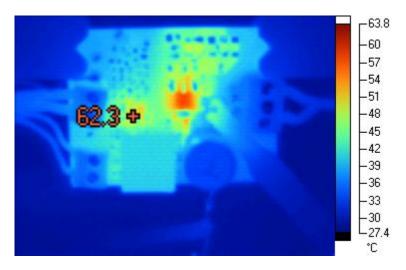

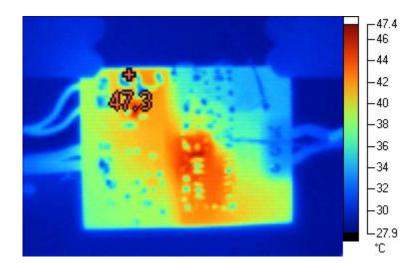

# 5 Thermal Images

The thermal images of board (top and bottom) are shown in the following pictures at minimum and maximum Input Voltage and Output1 and Output2 full load, with evidence of the hottest point. Tamb=25°C.

TOP Side Vin=120V peak, full Outputs Load

BOTTOM Side Vin=120V peak, full Outputs Load

TOP Side Vin=375V peak, full Outputs Load

BOTTOM Side Vin=120V peak, full Outputs Load

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated