# **GC5018 Daughtercard**

SLWU031 - February 2006

# GC Studio Reference

#### IMPORTANT NOTICE

THE PRODUCTS ORDERED HEREUNDER ARE EXPERIMENTAL, DEVELOPMENTAL OR PROTOTYPE PRODUCTS. THE PRODUCT SPECIFICATIONS ARE PRELIMINARY & SUBJECT TO CHANGE WITHOUT NOTICE. TI MAKES NO WARRANTY, EITHER EXPRESSED, IMPLIED OR STATUTORY, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A SPECIFIC PURPOSE, AS TO THESE PRODUCTS AND TI DOES NOT REPRESENT THAT A FINAL PRODUCTION VERSION WILL BE SOLD BY TI.

# Contents

| 1. GC5018 Daughtercard and GC101 EVM Setup                          | 4  |

|---------------------------------------------------------------------|----|

| 2. GC Studio and the GC5018/GC101 Evaluation Hardware               | 5  |

| 2.1. GC Studio Installation                                         | 5  |

| 2.1.1. Required Elements                                            | 5  |

| 2.1.2. GC Studio Installation Instructions                          | 5  |

| 2.2. GC Studio Projects                                             | 6  |

| 2.2.1. Creating a New GC Studio Project for a UMTS Configuration    | 6  |

| 2.2.2. Capturing the GC5018 Test Bus Output                         | 35 |

| 2.2.3. Creating a New GC Studio Project to exercise the Channel AGC | 42 |

| 2.2.4. GC5018 Projects included in the GC Studio Release            | 64 |

| 2.2.5. GC Studio References                                         | 66 |

| 3. GC5018 Daughtercard Description                                  | 66 |

| 3.1. GC5018 Daughtercard to GC101 Motherboard Signal Description    | 68 |

| 3.2. GC5018 Daughtercard Jumpers                                    | 68 |

| 3.3. GC5018 Daughtercard Power Supplies                             | 68 |

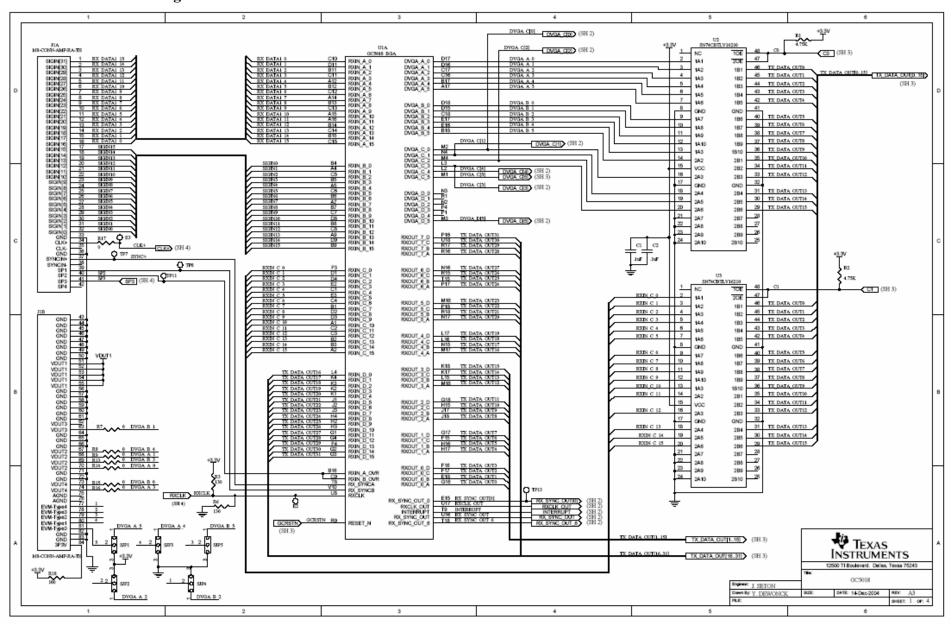

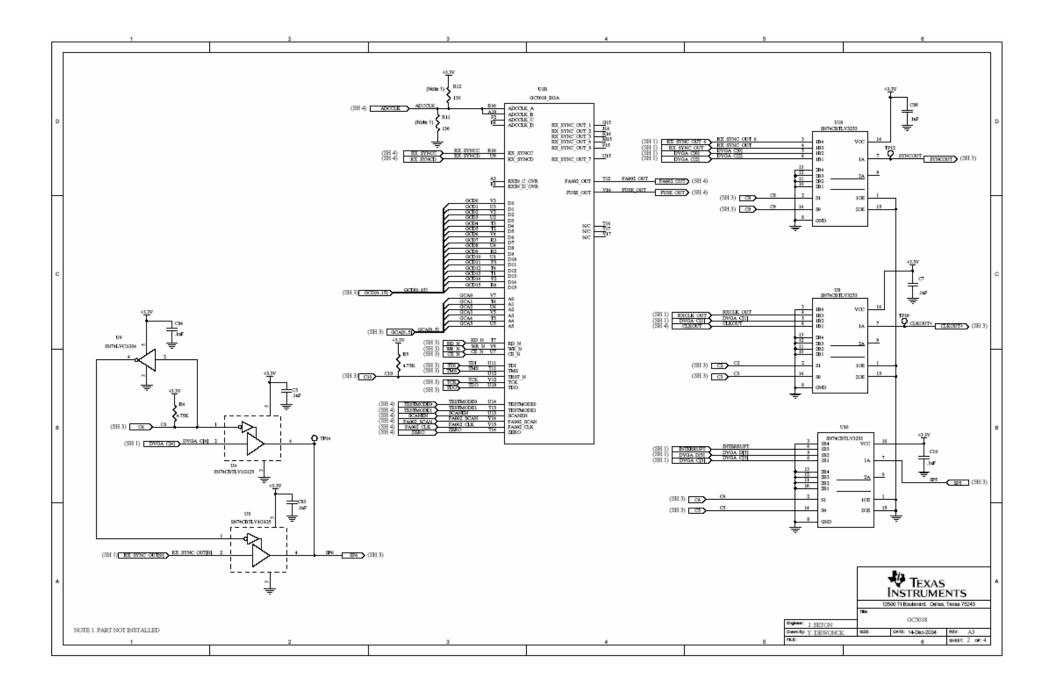

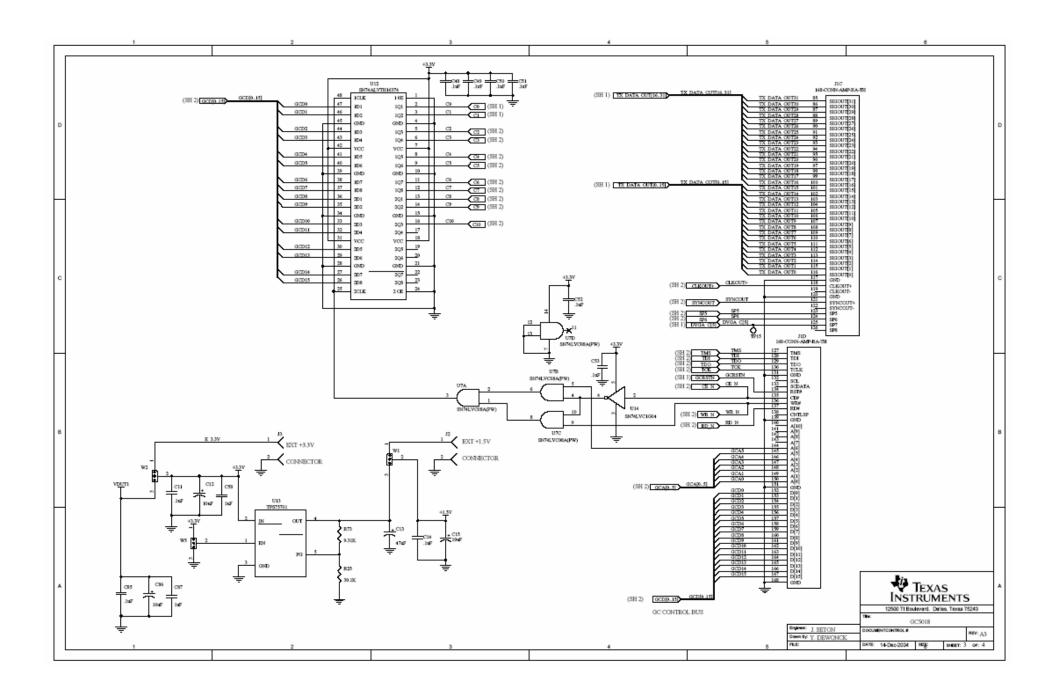

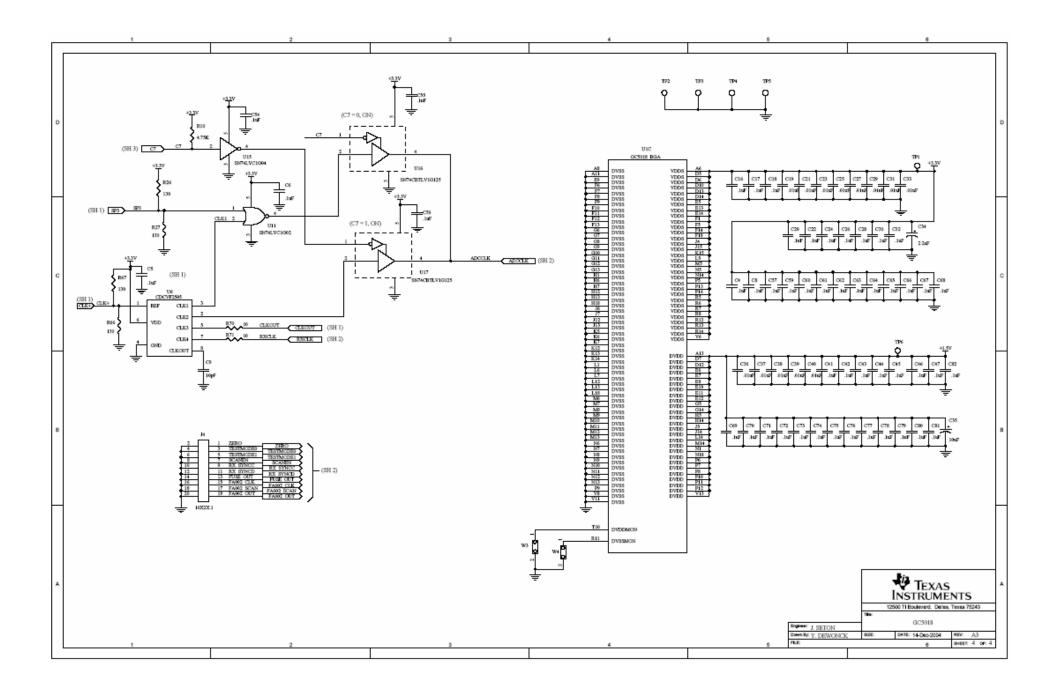

| 4. Detailed GC5018 Daughtercard Schematic                           | 69 |

### 1. GC5018 Daughtercard and GC101 EVM Setup

The GC5018 daughtercard combined with the GC101 motherboard provide a hardware evaluation platform for development of application specific settings for the GC5018. To operate the system, simply plug the GC5018 daughtercard into the DIMM socket on the GC101 motherboard, connect the parallel port interface cable to the GC101 and Host Computer (PC), and connect the power supply to the GC101.

Figure 1. GC101 EVM and GC5018 Daughtercard

#### 2. GC Studio and the GC5018/GC101 Evaluation Hardware

GC Studio includes a software "plug-in" to control the GC101 motherboard, GC5018 daughtercard and the GC5018 device. Input data from a text file on the host computer (PC) is loaded into the GC101 input memory and used to stimulate the GC5018 input ports. Output data from the GC5018 is captured in the GC101 capture memory and transferred to the host computer. GC Studio configures the GC5018 internal registers using the interactive GUI.

Several GC Studio projects for the GC5018 are included in the installation. These projects can be used as the starting point for creating new experiments as desired.

#### 2.1. GC Studio Installation

#### 2.1.1. Required Elements

GC101 evaluation motherboard, the external 5V power supply for the GC101 and a ECP parallel port enhanced speed cable.

GC Studio software, downloaded or provided on a CD

GC5018 Rev B or Rev C daughtercard

Host Computer (PC) with BIOS supporting ECP mode for LPT1, running Win98 Rel 2, WinME, Win2000 SP1, WinXP Home or WinXP Professional.

Administrator Group Privileges

#### 2.1.2. GC Studio Installation Instructions

Locate the "GC Studio\_Setup.exe" file on the CD or in the downloaded location on the host computer and double click on it to install.

#### 2.2. GC Studio Projects

Several projects (sometimes referred to as experiments) are provided for the GC5018 in the GC Studio release. Users can execute these existing projects and create and save new projects using the GC Studio GUI interface.

GC Studio will come with Example files, and if modifying those, it is suggested to save the new file under different name from the original one.

#### 2.2.1. Creating a New GC Studio Project for a UMTS Configuration

For this example, the new project will configure the GC5018 to process a UMTS signal. The GC5018 configuration details are as follows:

- A single real UMTS carrier is applied to the GC5018 rxin\_a inputs with a simulated sample rate of 76.8Msps and an IF frequency of 19.2MHz.

- Simulated rxclk to the gc5018 is 153.6MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured to process the signal

- The mixer/nco shifts the real 19.2MHz IF to a complex signal centered at DC.

- The DC centered signal is zero stuffed to increase the rate from 76.8Msps to 153.6Msps. This is required, as the CIC uses only full rxclk rate input signals.

- The CIC filter is programmed to decimate by 10 using a m=2 comb section configuration. The output sample rate at the CIC output is 15.36Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 40 tap filter, which is the maximum length that can be computed with rxclk at 153.6MHz and the CFIR output rate of 7.68Msps.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

# Start GC Studio

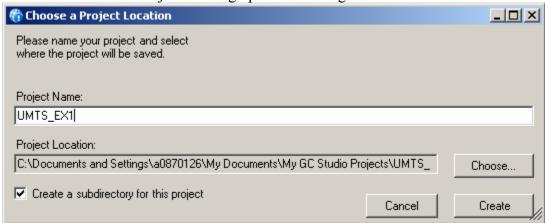

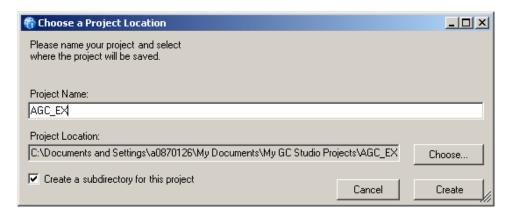

Click on File > New Project to bring up the following window.

Choose a name for this new project, and click create.

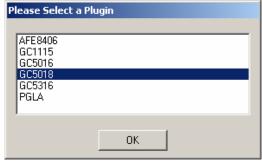

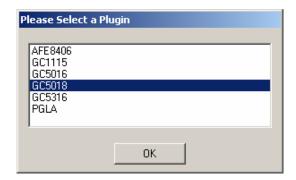

Select GC5018 for the Plugin and click OK. Click next on the following pop-up.

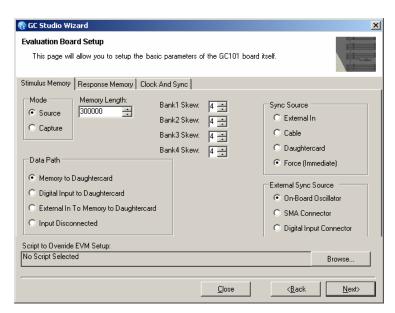

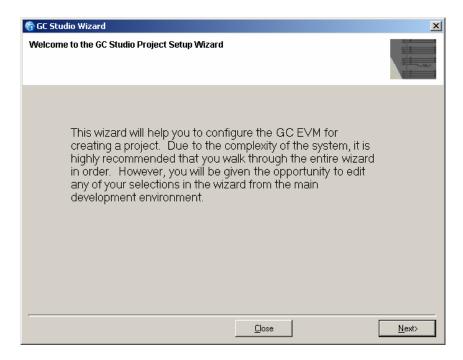

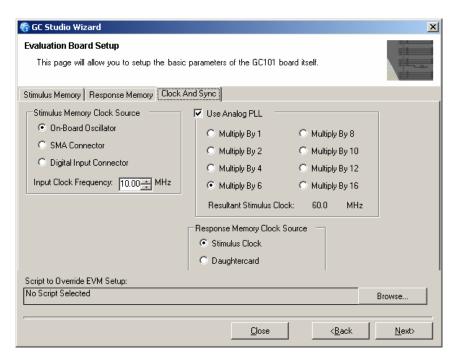

Using the wizard style interface, setup the GC101 evaluation board, then click next. The memory length should be set to "N" frames of data (300000 is the default value).

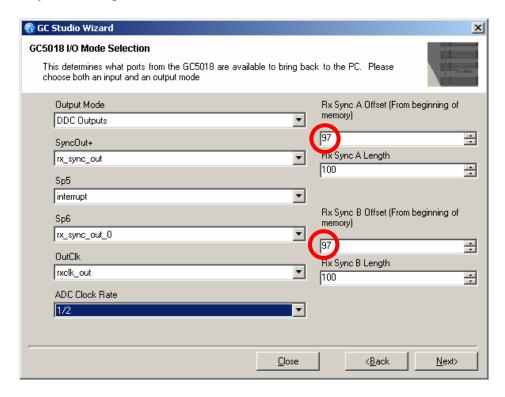

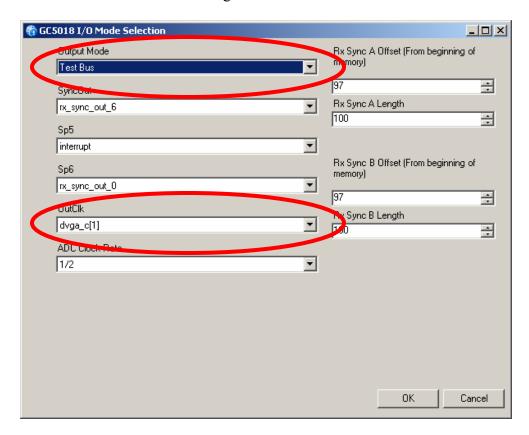

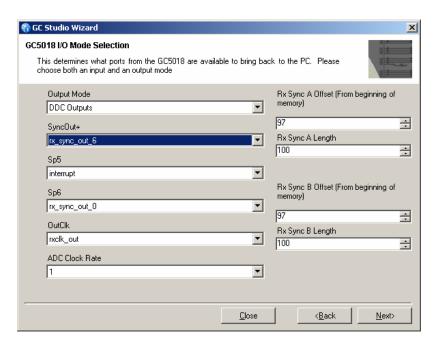

Setup the GC5018 I/O mode selection as shown and click next. In this example, be sure the ADC clock rate is set to ½. The parameters on the right tell the capture when the data is valid and how long the SYNC is. The top parameter (circled in red below) should match the length of the capture memory, or be longer.

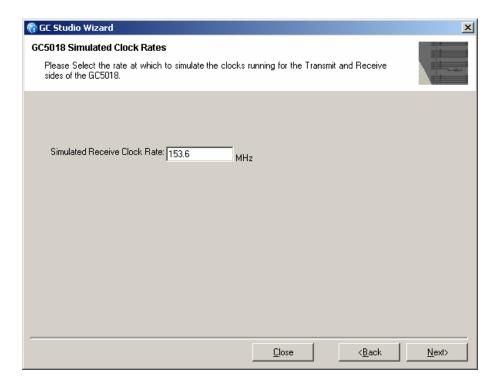

Set the simulated clock rate to 153.6MHz and click next.

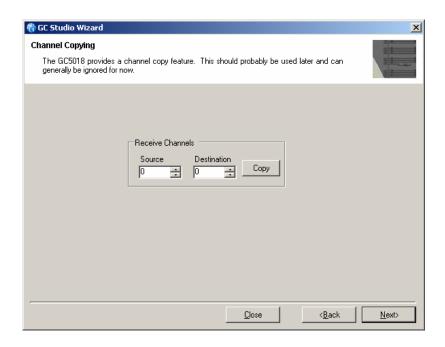

Channel Copying will be skipped for now, click Next.

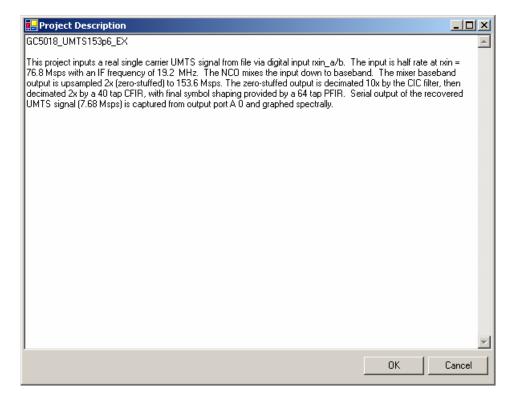

Project Description allows user to briefly describe the project details and will appear every time the project is selected for loading.

Click Next.

# Click Finish.

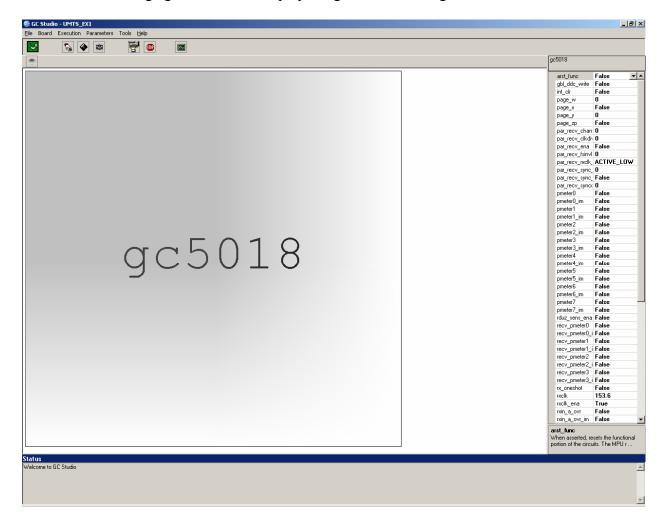

Click on the large gc5018 box to display the global control registers.

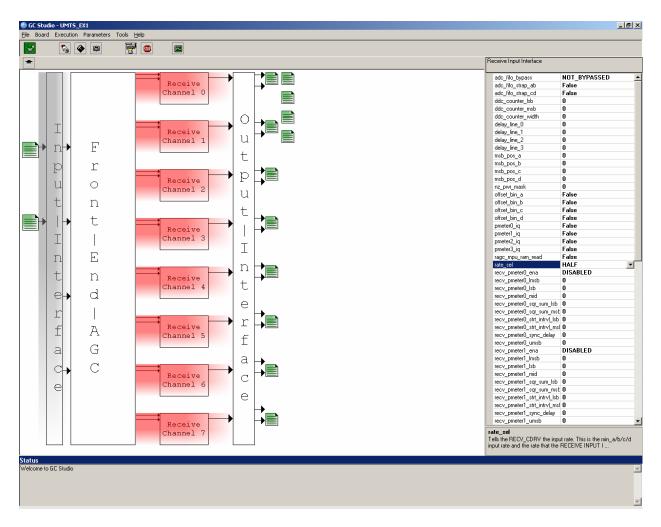

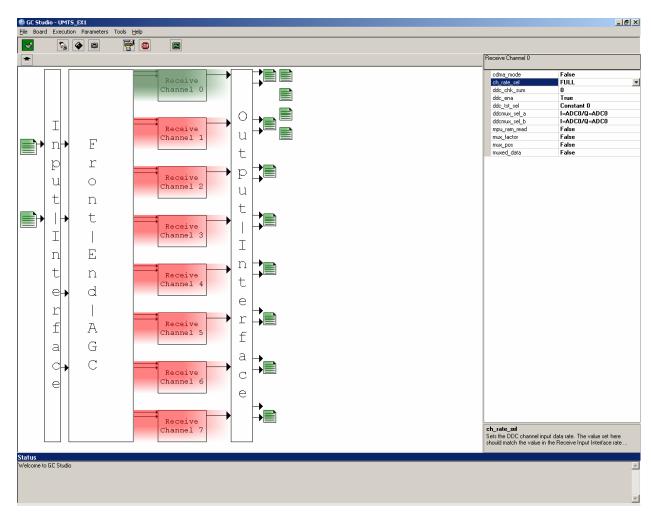

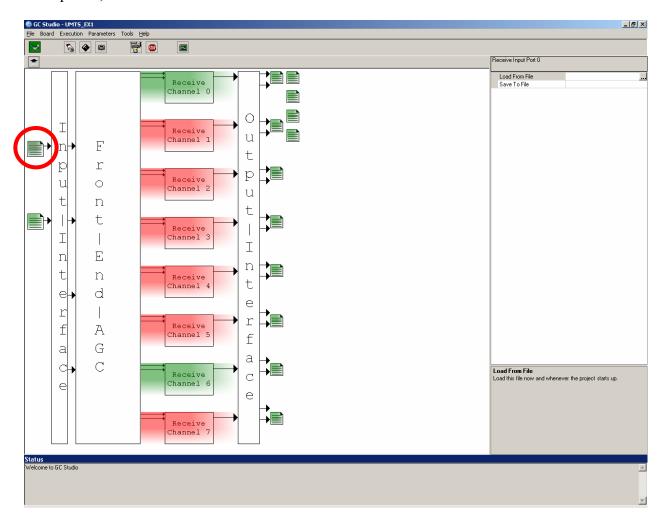

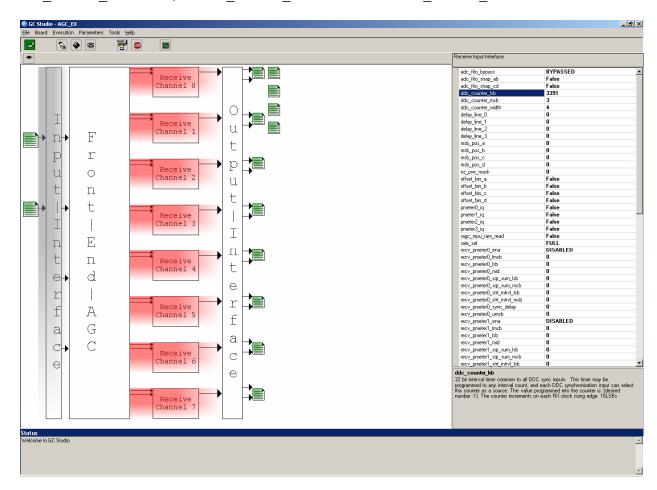

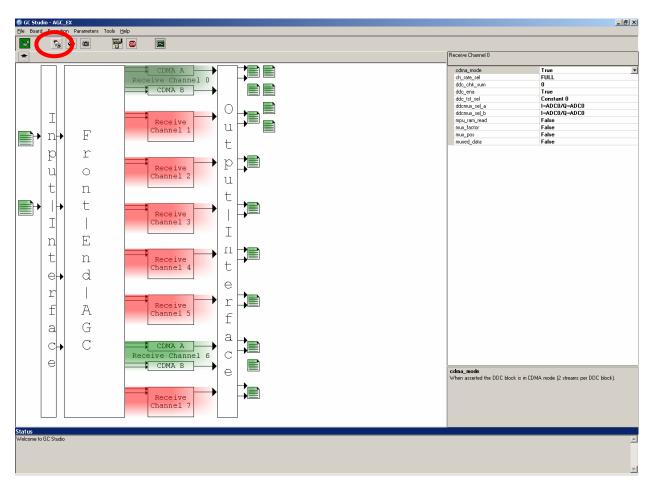

Next, double click on the gc5018 block to "push down" one level into the gc5018. This level contains the blocks of: Input Data File, Input Interface, Front End AGC, Eight Receive Channels, Output interface and Output Data Files.

Click on the Input Interface block to display and edit the receive input interface registers. Set rate\_sel to half; this will configure the GC5018 for input samples at ½ the rxclk rate. Set adc\_fifo\_bypass to NOT BYPASSED to enable the rxin\_a/b/c/d input FIFO circuits. The input data format can be set to offset binary or twos complement.

Also, Receive Power Meters (Wideband Power Meters) are provided for the inputs and could be set according to the datasheet explanation. This example will not use Power Meter Functions.

Front End AGC is not used in this example, and the function and parameters are discussed in the datasheet. An example file demonstrating the performance of the Front End AGC (RAGC) could be supplied upon request.

Click on the upper Receive Channel 0 block, the top most red block in the previous picture. Set ddc\_ena to True. The top most receive channel will be changed to green since it has been enabled.

"cdma\_mode" is set to FALSE, setting the channel for UMTS function. In this setting, the DDC can process 8 UMTS carriers.

"ddcmux\_sel\_X" (where X = a or b) determines where the data comes from into the Receive channel. ADC0 is the top file input, ADC1 is the bottom. Other inputs are not used for the GC5018 board.

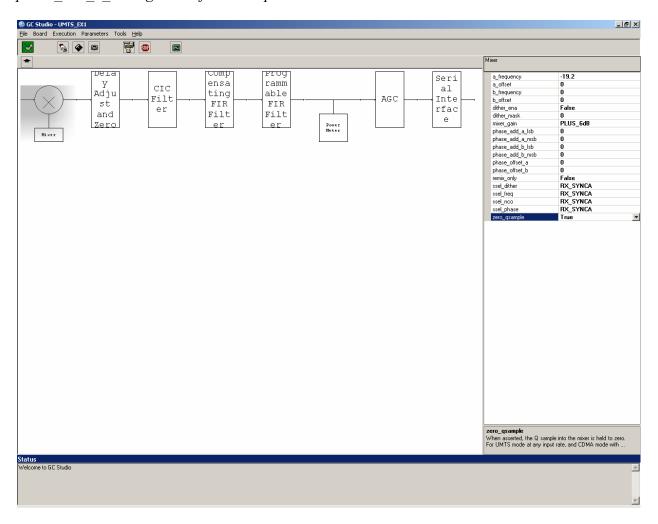

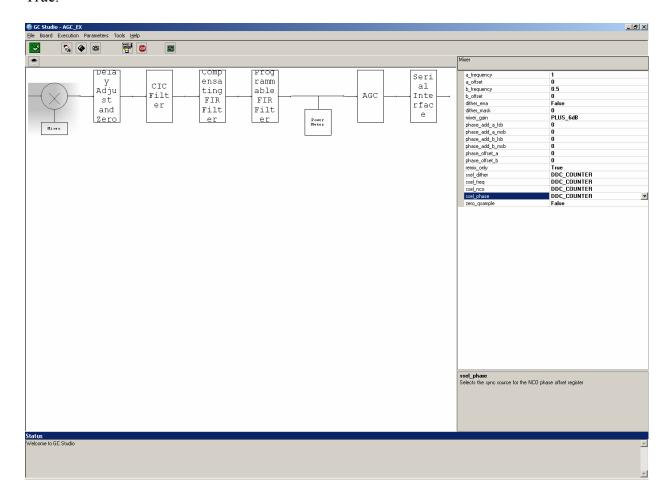

Double click on the Receive Channel 0 block to push down into this channel. The block diagram now shows the sub blocks in the receive channel, and the registers to configure it.

Select the mixer/nco block (left most block). Since the input is a real signal, set the a\_frequency to either +19.2 MHz or -19.2 MHz. The b\_frequency setting is not used when the channel is in UMTS mode. Set zero\_qsample to True (only I input is valid).

GC Studio will calculate the required values for the phase\_add\_a\_msb and phase add a lsb registers after the experiment is executed.

There will be a 6 dB loss through the mixer due to the complex mixing. Therefore, the "mixer gain" option can add 6 dB gain if set.

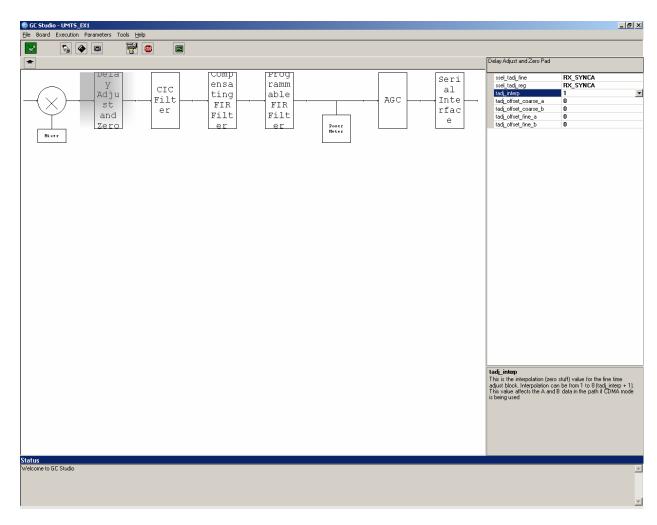

Select the Delay Adjust and Zero Stuff block. Because the input sample rate is set to ½ the rxclk rate, this block is automatically configured by GC Studio to interpolation by 2, inserting a zero sample between each actual sample before being applied to the CIC filter. "tadj interp" is set to 1 for an interpolation by 2.

This moves the 76.8Msps input signal stream to the 153.6Msps rxclk rate. The tadj\_offset\_coarse and tadj\_offset\_fine settings allow the user to adjust the delay between various receive channels if desired.

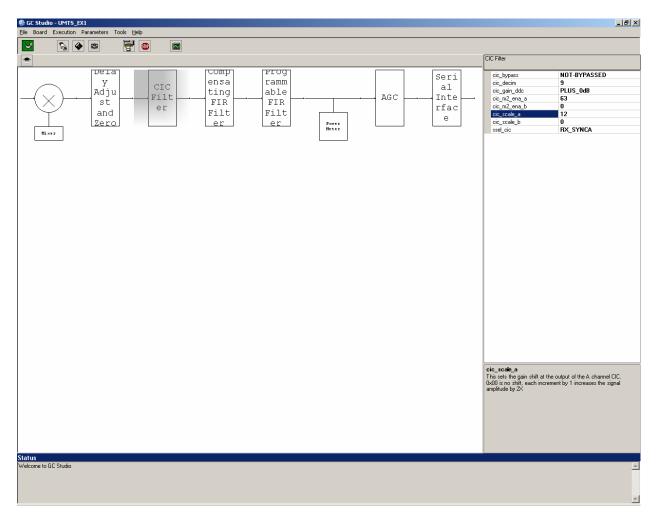

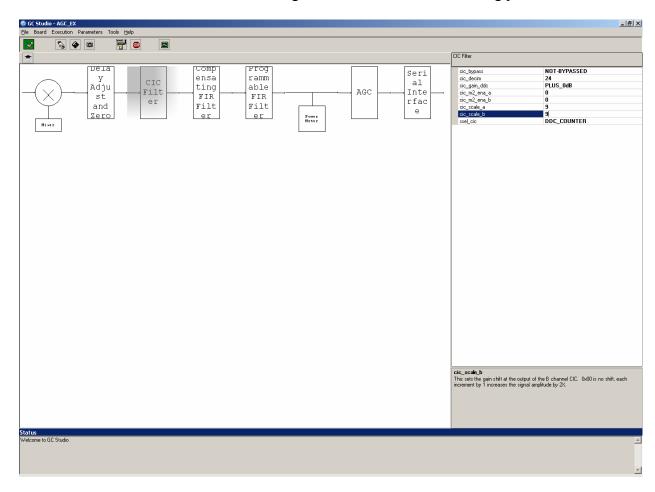

Click on the CIC filter block and set the registers as shown in the following panel. The decimation in the CIC is set to 10x, resulting in a 15.36Msps CIC output rate. The "cic\_decim" parameter should be set to the desired decimation (10) minus one.

Therefore, the output rate of the CIC block (input to the CFIR block) is at 4x symbol rate for UMTS (15.36 MSPS).

For this example, all 6 CIC comb stages are set to m=2 (63 decimal = 111111 in binary).

See the datasheet CIC gain equation for appropriate "cic\_scale\_X" (where X = a or b) parameter setting, and to avoid CIC block saturation.

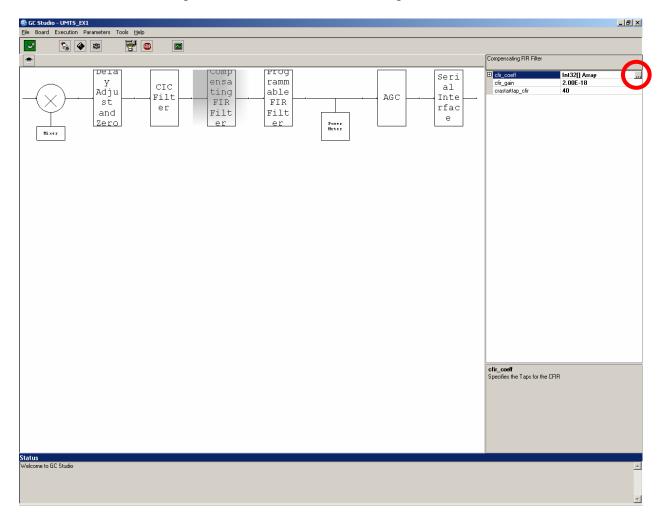

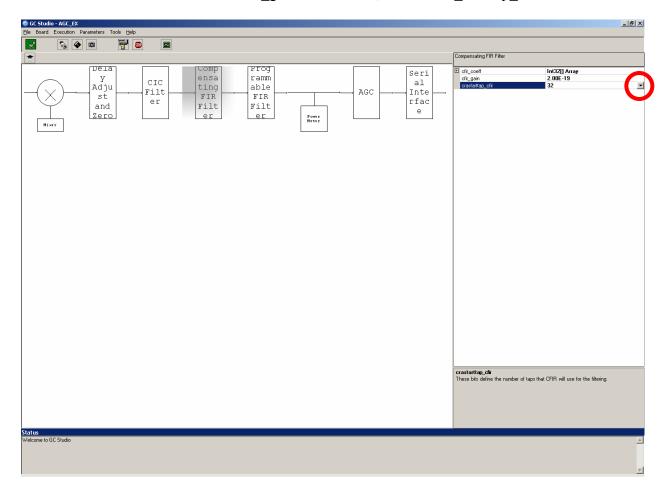

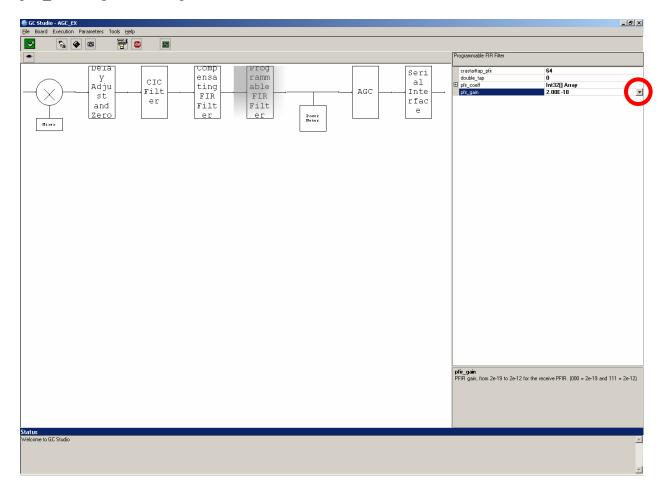

Select the CFIR block and set the cfir\_gain to 2.00E-18, and the cra\_starttap\_cfir to 40 taps. The maximum number of taps in CFIR for UMTS example is calculated as twice the rxclk rate over the CFIR output rate – in this case  $2 \times 153.6e6 / 7.68e6 = 40$  taps. See the datasheet CFIR description for more details on CFIR tap calculation.

Next, select the cfir\_coeff register setting by clicking on it, and then click on the browse button, circled in red on the panel above, to open the Edit Filter window and fill in the CFIR filter tap weights.

The CFIR is the compensation filter that compensates for the CIC droop. Therefore, the user should realize that the maximum number of taps actually is the convolved response of the filter and compensation filter (usually a three tap filter).

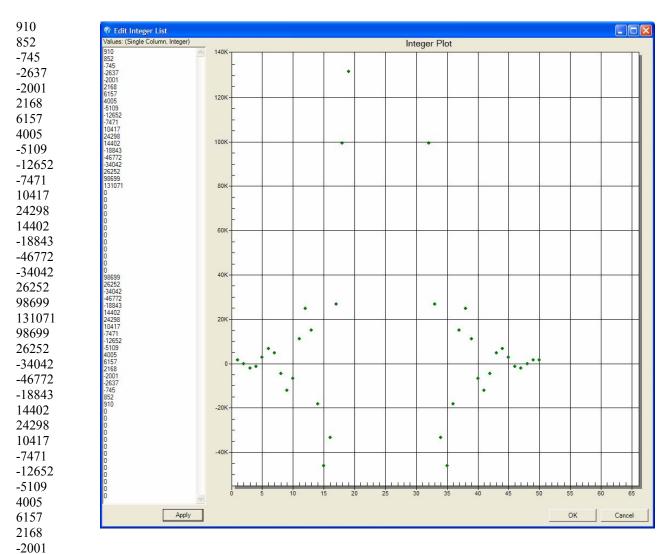

The CFIR tap weights are entered as shown. Note the first 20 taps are entered as the first 20 entries, and then 12 lines are skipped before entering the second 20. This is due to the GC5018 coefficient RAM being split into (2) 32 word blocks. See the datasheet for more details if necessary.

For this example, the CFIR tap weights are ...

-2637 -745 852 910 0

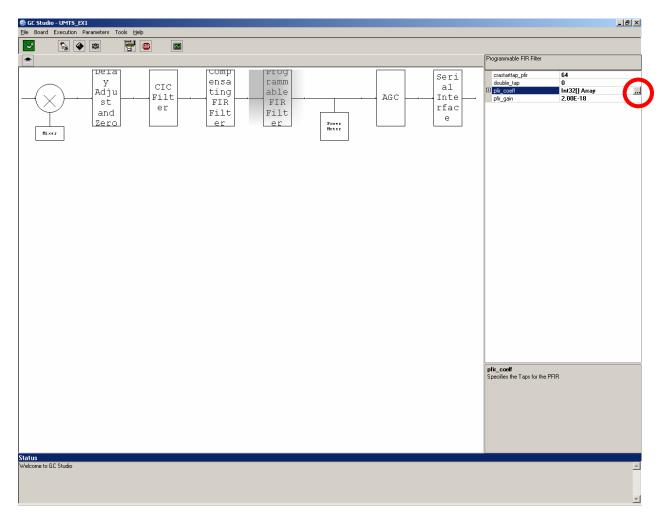

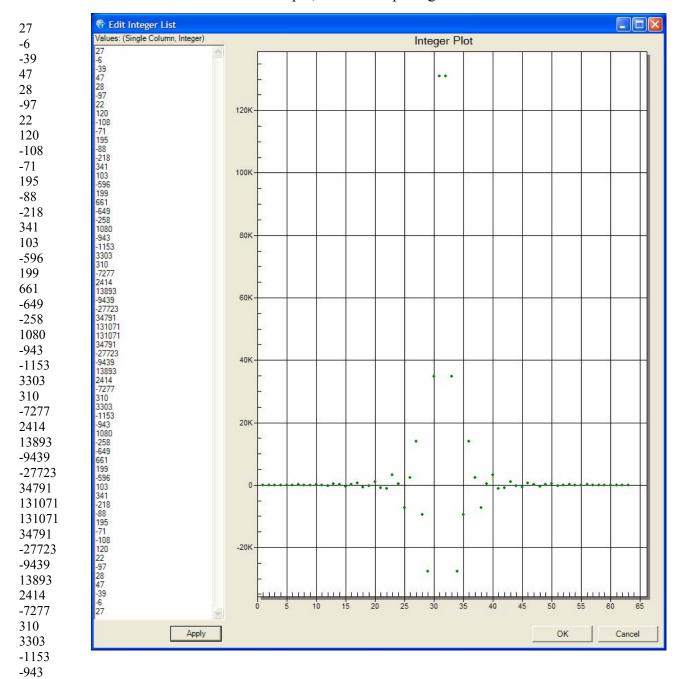

Select the PFIR block, set the pfir\_gain to 2.00E-18, and crastarttap\_pfir to 64. Select the pfir\_coeff register, and again select the browse button. The maximum number of taps in PFIR for UMTS example is calculated as four times the rxclk rate over the CFIR output rate – The maximum number of available taps in PFIR is 64, therefore, all 64 taps are available for this example. See the datasheet CFIR description for more details on CFIR tap calculation.

Next, select the pfir\_coeff register settings by clicking on it, and then click on the browse button, circled in red on the panel above, to open the Edit Filter window and fill in the PFIR filter tap weights.

The PFIR in this example is an RRC filter with a = 0.22. However, the user must understand that the shape of the filter will slightly change if windowing is used, and that needs to be compensated appropriately.

The PFIR tap weights are entered as shown. For the 64 tap PFIR in this example, all coefficient are used. For this example, the PFIR tap weights are ...

1080 -258 -649 661 199 -596 103 341 -218 -88 195 -71 -108 120 22 -97 28 47 -39 -6 27

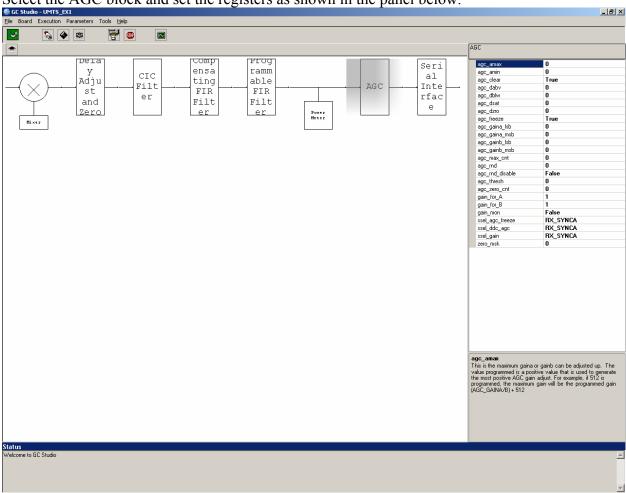

Select the AGC block and set the registers as shown in the panel below.

The gain\_for\_A value is set unity, the agc\_freeze and agc\_clear are both set to True for this example. This puts the AGC in unity fixed gain mode. GC Studio will calculate the required values for the agc\_gaina\_msb and the agc\_gaina\_lsb registers after the experiment is executed.

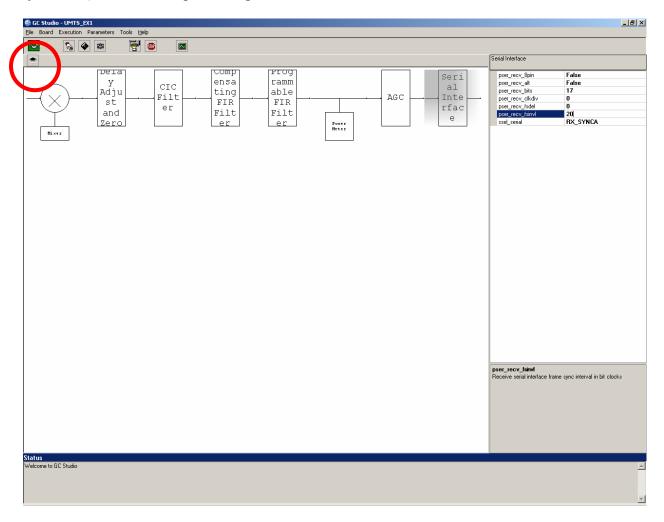

Select the Serial Interface block and set the parameters as indicated. The maximum number of data bits on the serial output is 18. Since the overall decimation is greater than that (CIC decimation = 10 times CFIR decimation = 2) all 18 bits are available on the output, and "pser\_recv\_bits" parameter is set to 17 (# of output bits -1).

"pser\_recv\_fsinvl" parameter determines how often the frame sync will come on the serial output and in this case is equal to the overall decimation (20).

"pser\_recv\_clkdiv" parameter allows the user to divide the output clock rate from the rxclk. This is an useful feature at high input data rates and high decimations, to slow down the output clock (that may be used) for baseband processing.

After verifying the values for the serial interface, click the arrow circled in red in panel above to pop up one level in the GC5018 hierarchy.

Receive Channel 0 has now been configured to process:

a UMTS signal at 76.8Msps with a 19.2MHz IF

mixer/nco block shifts the signal to DC

zero stuff block interpolates by 2x, moving the 76.8Msps signal to 153.6Msps

CIC block decimates by 10x to 15.36Msps

40 tap CFIR compensates for the CIC droop, filters and decimates the signal to

7.68Msps

64 tap PFIR filters the signal

channel AGC is set to a fixed gain of unit

serial interface is used to output the baseband signal

The GC5018 daughter card configuration uses rx\_sync\_out\_6 as the strobe indicating when the serial output data starts each transfer. We'll copy the receive channel 0 configuration to receive channel 6 so the strobe will be present in the captured GC101 data.

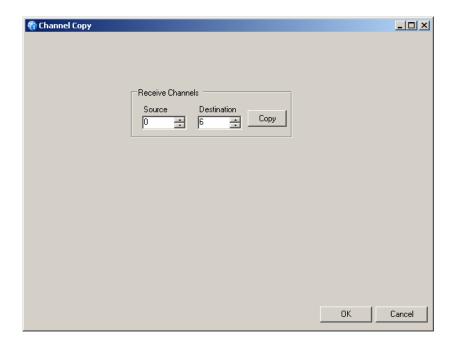

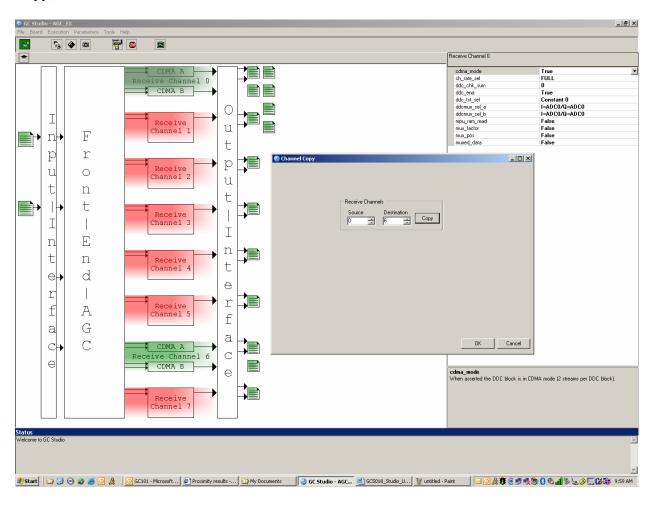

Select "Parameters > GC5018 Channel Copy" to bring up the Channel Copy panel below. With channel 0 selected as the source, and channel 6 is selected as the destination, click Copy, and then click OK.

The block diagram should now show both channels 0 and 6 active (green).

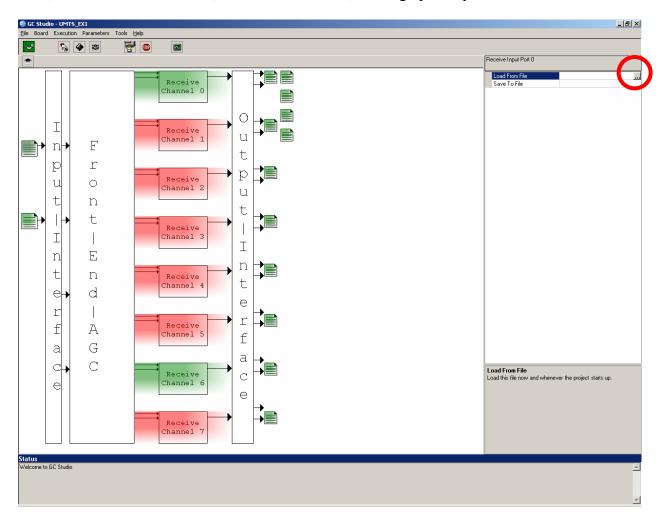

Input data presented to the gc5018 pins comes from text format data files. Two input file icons can be seen in the block diagram to the left of the Input Interface block. Click on the top icon, circled in red below.

The upper file icon is connected to the rxin\_a input port, and the lower is connected to the rxin\_b input port.

Next, click on the browse icon, circled in red below, to bring up the open file window.

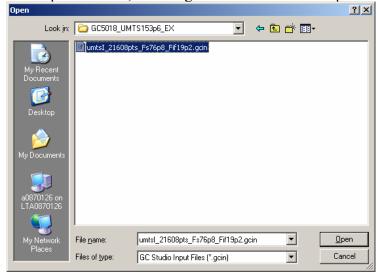

Navigate to and select the "umtsI\_21608pts\_Fs76p8\_Fif19p2.gcin" file, and click open. Repeat for the lower input file icon, selecting the same file as the input file.

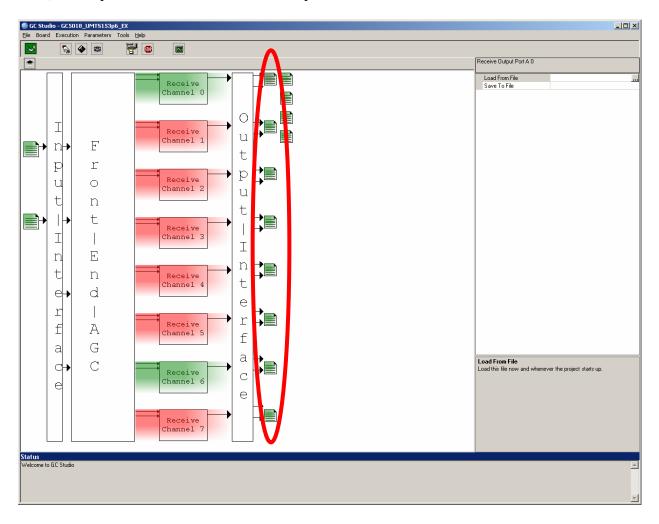

Also, the output data can be stored in the output file.

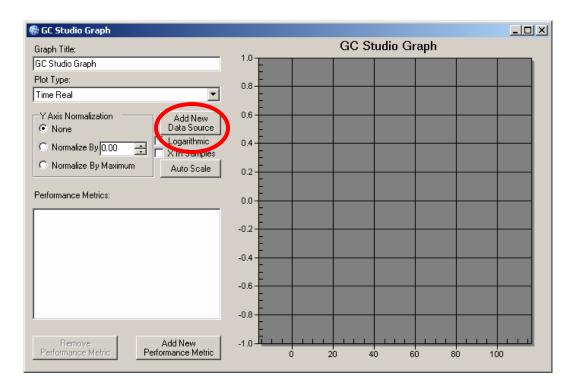

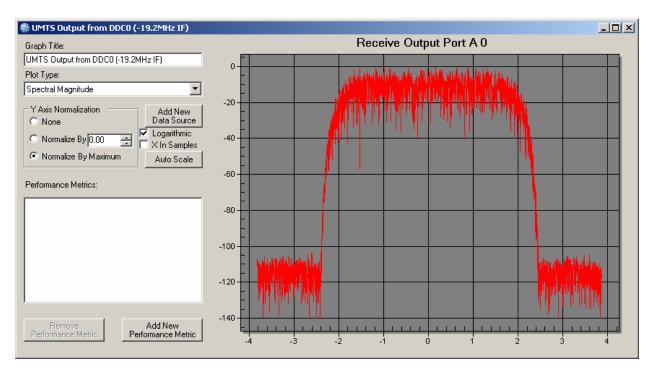

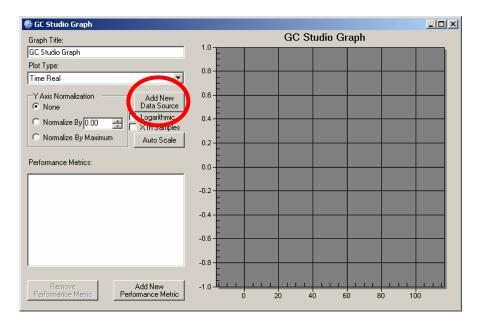

Next, click on the graph button, circled in red below, to open the graph panel.

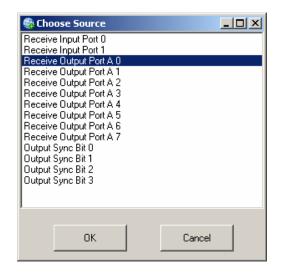

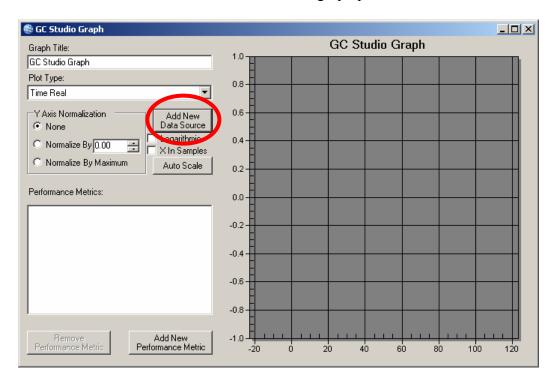

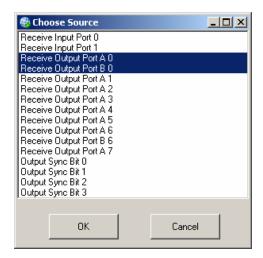

Click the Add New Data Source button circled in red above.

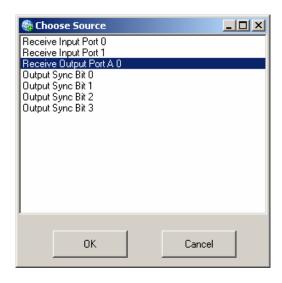

In the Choose Source panel, select both Receive Output Port A 0, and click OK.

In the graph panel, set the Plot Type to Spectral Magnitude, and check Logarithmic.

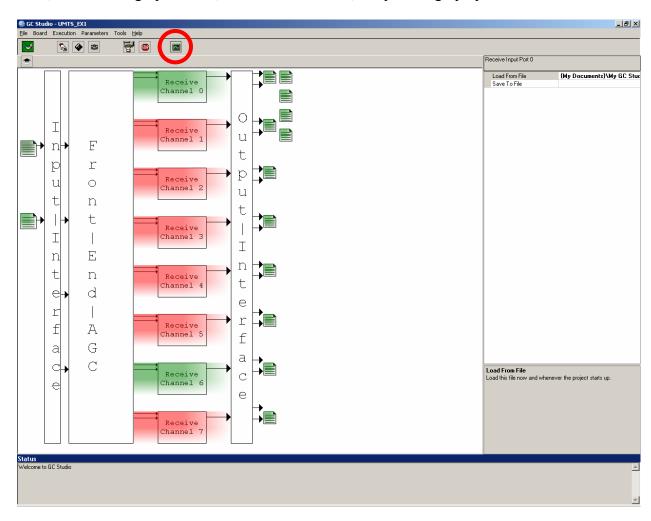

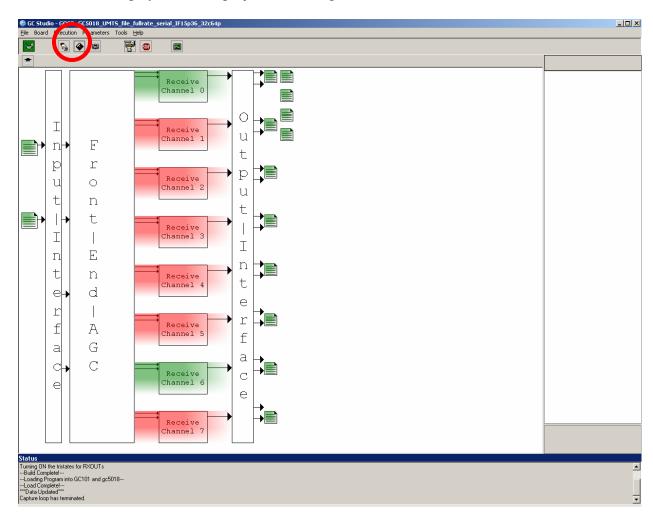

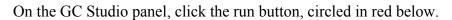

On the GC Studio panel, click the Build and Load buttons, circled in red below. The buttons will turn grey while the project is running.

The graph window will be automatically updated with the results.

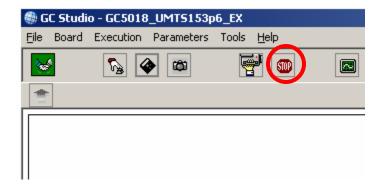

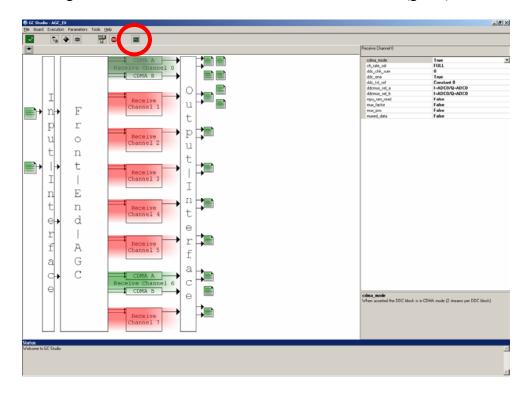

On the GC Studio panel, click on the stop button, shown circled in red below, to stop the experiment, then select File > Save Project to save this project.

Close the GC Studio Graph Window.

The GC Studio software also allows the user to extract the internal register values into the file that could make programming the device much less complicated than doing it "by hand"

Select "Tools", then "Export Device Programming File..."

The file will be saved in a two-column format where the first column is the register locations, and the second is the 16-bit values:

### 2.2.2. Capturing the GC5018 Test Bus Output

The GC5018 includes a test bus allowing the user to view internal digital signals. When the test bus is enabled, the rxin\_c and rxin\_d digital ADC input ports become outputs and the dvga\_c and dvga\_d ports are multiplexed to carry test bus data. The result is a 36 bit wide output port and 3 additional signals.

| testbus(35:0) | rxin_d(15:0), dvga_c(3:2), rxin_c(15:0), dvga_c(5:4) |

|---------------|------------------------------------------------------|

| dvga_c(1)     | test bus clock                                       |

| $dvga_c(0)$   | test bus sync                                        |

| dvga d(5)     | test bus aflag                                       |

The GC101 evaluation platform captures a 36 bit signal into the response memory. When selecting the various test bus sources, the signals selected in the I/O Mode Selection window must be set correctly.

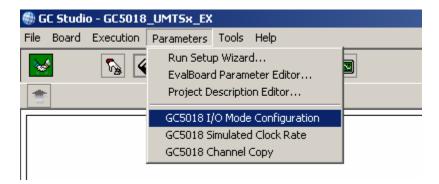

Starting from the previous UMTS example experiment, select Parameters > GC5018 I/O Mode Configuration.

The Output Mode is set to Test Bus and the test bus output clock on  $dvga\_c(1)$  is selected as the OutClk source when using the test bus.

The other signals captured as SyncOut+, Sp5 and Sp6 should be configured as required for the specific test bus signal (Sp7 is always dvga\_c(5)). The test bus output clock is used to load the response memory, and is controlled by the tst rate sel.

| Test Bus Signal                  | SyncOut+  | Sp5         | Sp6         | OutClk    | tst_rate_sel     |

|----------------------------------|-----------|-------------|-------------|-----------|------------------|

| DDC PFIR in UMTS mode            | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | 2*CIC decimation |

| DDC PFIR in CDMA mode            | dvga_c(2) | $dvga_d(5)$ | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC CFIR in UMTS mode            | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | 2*CIC decimation |

| DDC PFIR in CDMA mode            | dvga_c(2) | $dvga_d(5)$ | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC TADJ-A                       | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC TADJ-B CDMA mode only        | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC NCO-SINE in UMTS mode only   | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| DDC NCO-COSINE in UMTS mode only | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| DDC CIC in UMTS mode             | dvga_c(2) | dvga_c(3)   | $dvga_c(4)$ | dvga_c(1) | CIC decimation   |

| DDC CIC in CDMA mode             | dvga_c(2) | $dvga_d(5)$ | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC AGC in UMTS mode             | dvga_c(2) | dvga_c(3)   | $dvga_c(4)$ | dvga_c(1) | 2*CIC decimation |

| DDC AGC in CDMA mode             | dvga_c(2) | $dvga_d(5)$ | dvga_c(4)   | dvga_c(1) | RXCLK Rate       |

| DDC MIXER-A                      | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| DDC MIXER-B CDMA mode only       | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| DDC DDCMUX-A                     | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| DDC DDCMUX-B CDMA mode only      | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

| RXIN_A and RXINB FIFO            | dvga_c(2) | dvga_c(3)   | dvga_c(4)   | dvga_c(1) | ADC Clock Rate   |

Using the setup from the previous UMTS example, the NCO sine test bus source is a 20 bit signal output on the dvga\_c(3:2) + rxin\_c(15:0) + dvga\_c(5:4) pins. Selecting dvga\_c(4) for Sp6, dvga\_c(3) for Sp5 and dvga\_c(2) for SyncOut+ is required. The daughtercard always connects dvga\_c(5) to the capture memory Sp7 bit. The 20 bit sine and cosine signals can be captured and analyzed using the I/O mode selection as shown above.

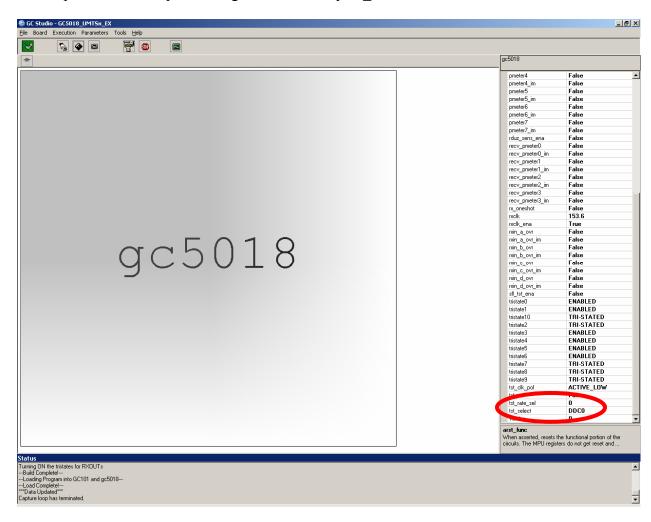

The NCO clock runs at the same clock frequency as the input data. The test clock should therefore be configured to provide a rxclk/2 output by setting tst\_rate\_sel to 1. The test bus output in this example is using DDC0 as set by tst\_sel.

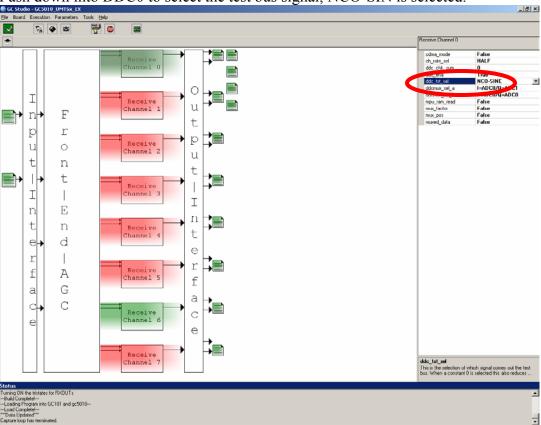

Push down into DDC0 to select the test bus signal, NCO-SIN is selected.

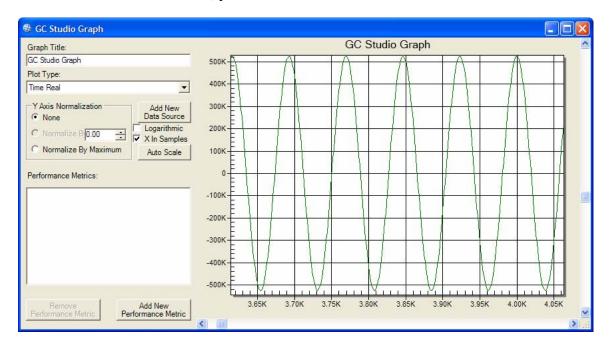

Push down into DDC0, and select the Mixer block. Set a\_frequency to 1MHz. Open a new graph window, and run the experiment.

Click the Add New Data Source button on the graph panel.

When the Test Bus is selected as the Output Mode, only the one Output Port is available. Select Receive Output Port A 0 and click OK.

Click the X in Samples box. With the DDC0 NCO programmed for 1MHz, the output can be viewed in the graph panel. To zoom in, left click and drag in the graph – to zoom in this far, you'll need to zoom in a few times.

Stop the experiment, then select File > Save Project As ... to save this project under a new name.

Close the Graph window.

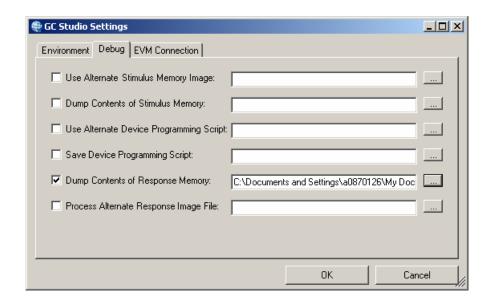

The raw response memory can be captured in a text format by selecting the option in the Tools > Options window.

The format of the file is hexadecimal, with the 32 bit response memory as the first 8 characters, a space, and then a single character for the other 4 special bits {sp7, sp6, sp5, syncout+}.

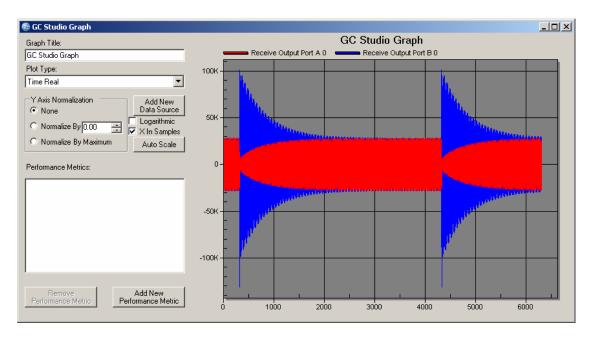

# 2.2.3. Creating a New GC Studio Project to exercise the Channel AGC

For this example, the new project will use the GC5018 self test circuits to force a constant as the input signal, set the channel NCO to generate a tone, and exercise the channel AGC function in CDMA mode.

### Start GC Studio

Click on File > New Project to bring up the following window.

Choose a name for this new project, and click create.

Select GC5018 for the Plugin and click OK. Click next on the following pop-up.

Using the wizard style interface, setup the GC101 evaluation board, then click next.

Set up the Stimulus Memory and Response Memory parameters. Then, set up the clock parameters:

Setup the GC5018 I/O mode selection and click next.

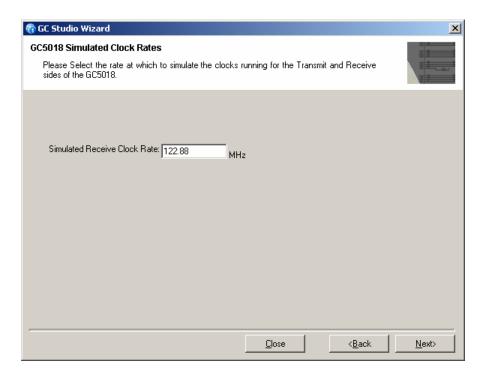

Set the simulated clock rate to 122.88MHz and click next.

# Click Next on Channel Copying.

## Click Next

Project Description allows user to enter a brief description of the project including the key parameters. When done, click Next.

Click Finish.

Click on the large gc5018 box to display the global control registers. Set slf\_tst\_ena to True to enable the self test circuits.

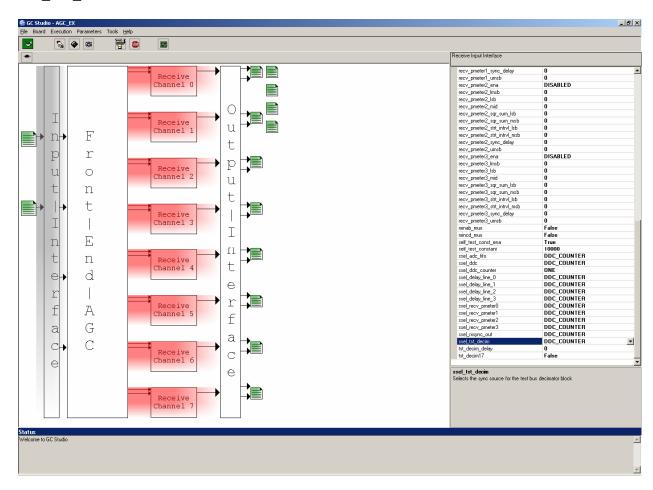

Next, double click on the gc5018 block to "push down" one level into the gc5018. Click on the Input Interface block to display and edit the receive input interface registers. The DDC counter will be used in this experiment to internally generate a repetitive synchronization pulse. Program the adc\_fifo\_bypass to BYPASSED, the ddc counter width to 4, the ddc counter msb to 3 and the ddc counter lsb to 3391.

With the Input Interface block still selected, scroll down (using the scroll bar at the right edge of the window) and set the remaining registers. Set the self\_test\_const\_ena register to True, and the self\_test\_constant to 10000. These settings will replace the input data normally presented at the rxin\_a/b/c/d input ports with an internally generated constant value.

Set the ssel\_adc\_fifo, ssel\_ddc, ssel\_delay\_line\_0, ssel\_delay\_line\_1, ssel\_delay\_line\_2, ssel\_delay\_line\_3, ssel\_recv\_pmeter0, ssel\_recv\_pmeter1, ssel\_recv\_pmeter2, ssel\_recv\_pmeter3, ssel\_rxsync\_out and ssel\_tst\_decim to DDC\_COUNTER. Set ssel\_ddc\_counter\_to\_ONE.

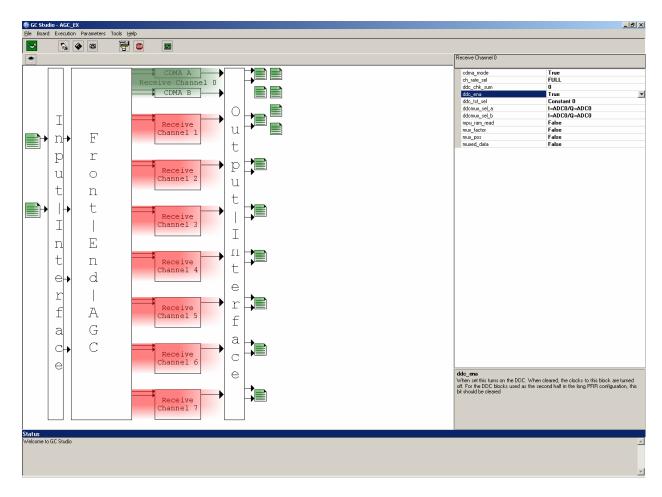

Click on the upper Receive Channel 0 block, the top most red block in the previous picture. Set cdma\_mode to True and ddc\_ena to True. The top most receive channel will be re-drawn as a split (or shared CDMA channel) and changed to green since it has been enabled. The split Receive Channel 0 figure indicates channel 0 is configured to process two CDMA streams.

Double click on the split Receive Channel 0 block to push down into this channel. The block diagram now shows the sub blocks in the receive channel, and the registers to configure it.

Select the mixer/nco block (left most block). In CDMA mode, the receive channel processed two streams, listed in the registers as a and b settings. Set the a\_frequency to 1 MHz and the b\_frequency to 0.5 MHz as shown below. *GC Studio will calculate the required values for the phase\_add registers after the experiment has been run.* Set the ssel\_dither, ssel\_freq, ssel\_nco and ssel\_phase to DDC\_COUNTER. Set remix\_only to True.

Click on the CIC filter block and set the registers as shown in the following panel.

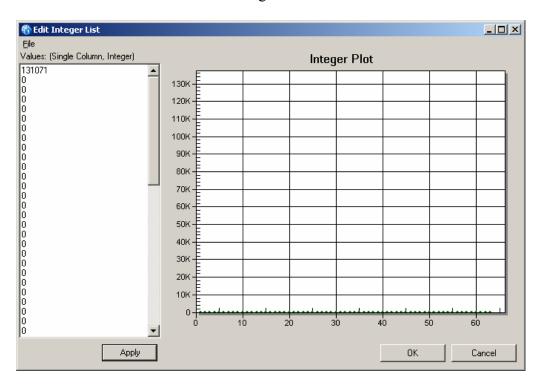

Select the CFIR block and set the cfir\_gain to 2.00E-19, and the cra\_starttap\_cfir to 32.

Next, select the cfir\_coeff register setting by clicking on it, and then click on the browse button, circled in red on the panel above, to open the Edit Filter window and fill in the CFIR filter tap weights.

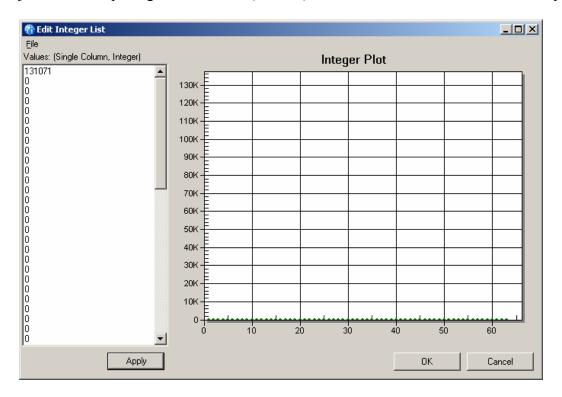

For this project, we will set just the first tap weight to full scale (131071) and the 63 others to zero. Click OK after entering all the values.

Select the PFIR block, set the pfir\_gain to 2.00E-18, and crastarttap\_pfir to 64. Select the pfir\_coeff register, and again select the browse button.

Set just the first tap weight to full scale (131071) and 63 other to zero in the Edit Filter panel.

\_ B × **№ №** 9 0 рета comp ensa Prog ramm egc\_emax

apc\_ania

apc\_daby

apc\_dbay

apc\_dbay

apc\_dbay

apc\_dbay

apc\_dbay

apc\_dbay

apc\_dbay

apc\_dbay

apc\_gbay

apc\_gainb\_ibb

apc\_gainb\_ibb

apc\_gainb\_ibb

apc\_max\_craft

apc\_may

ap CIC Ađju able AGC Inte Filt FIR FIR and Filt Filt е Power Heter False

DDC\_COUNTER

DDC\_COUNTER

DDC\_COUNTER ssel\_gain Selects the sync source for the DDC AGC gain register.

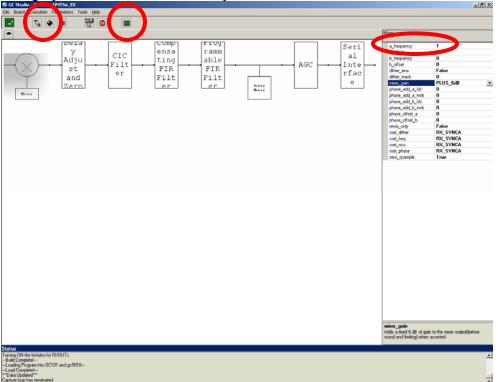

Select the AGC block and set the registers as shown in the panel below.

The gain\_for\_A value is set to an initial gain of 2 which will produce a signal much lower than the target signal level. GC Studio converts this variable to the appropriate register setting for agc\_gaina\_msb and agc\_gain\_lsb. Similarly, the gain\_for\_B value is set to 25 which will produce a signal much larger than the target signal level. GC Studio will calculate the required values for the agc\_gaina\_lsb, agc\_gaina\_msb, agc\_gainb\_lsb and agc\_gainb\_msb registers after the experiment has been run.

Each time the DDC\_COUNTER initializes the AGC, the loop will respond to the signal level present and increase the a channel gain while decreasing the b channel gain.

**№** ◆ **©** 9 0 рета comp ensa Prog ramm pser\_recv\_8pin pser\_recv\_alt pser\_recv\_bits pser\_recv\_clkdiv pser\_recv\_fsdel y Adju CIC al Inte able Filt AGC FIR FIR and Filt Filt Power Heter

ssel\_serial

Selects the sync source for the DDC serial interface state machines

Select the Serial Interface block and set the parameters as indicated.

After verifying the values for the serial interface, click the arrow circled in red in panel above to pop up one level in the GC5018 hierarchy.

Receive Channel 0 has now been configured to generate sinusoidal inputs using a constant and the nco block. The CIC is configured to decimate by 25, and the CFIR and PFIR filters are programmed with a single full scale non-zero coefficient to pass the decimated sinusoids to the AGC block.

The GC5018 daughter card configuration uses rx\_sync\_out\_6 as the strobe indicating when the serial output data starts each transfer. We'll copy the receive channel 0 configuration to receive channel 6 so the strobe will be present in the captured GC101 data.

Select Parameters > GC5018 Channel Copy to bring up the Channel Copy panel below. With channel 0 is selected as the source, and channel 6 is selected as the destination, click Copy, and then click OK.

The block diagram should now show both channels 0 and 6 active (green).

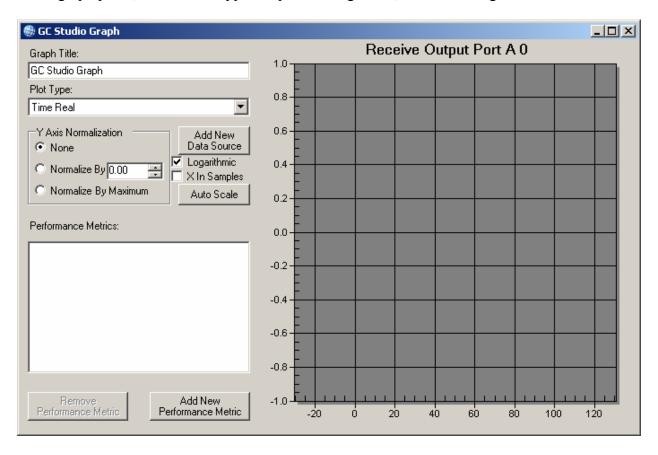

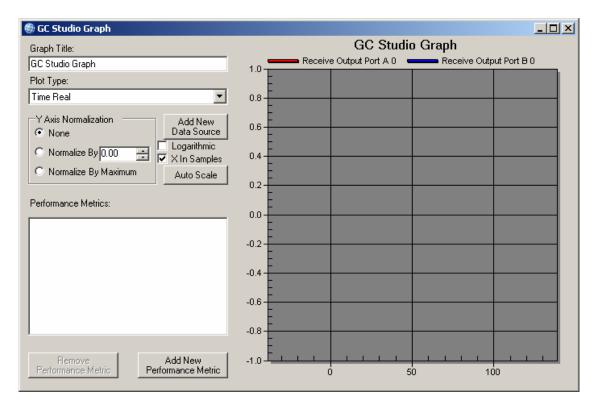

Click on the graph button, circled in red above, to open the graph panel shown below.

Click the Add New Data Source button circled in red above.

In the Choose Source panel, select both Receive Output Port A 0 and Receive Output Port B 0.

In the graph panel, set the Plot Type to Time Real, and check the X in Samples box.

The graph window will be automatically updated with the results.

The B channel gain initially is too large and the A channel gain is initially too small. The AGC loop adjusts the gain of both channels to the same programmed target level. Each time the internally generated DDC counter generates a pulse, the AGC loop accumulator is reset and acquisition is restarted.

On the GC Studio panel, click File > Save Project to save this project.

# 2.2.4. GC5018 Projects included in the GC Studio Release

The following example projects are included in the GC Studio Release

### UMTS153p6

- A UMTS carrier is applied to the GC5018 inputs with a simulated sample rate of 76.8Msps and an IF frequency of 19.2MHz.

- Simulated rxclk to the gc5018 is 153.6MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured to process the signal

- The mixer/nco shifts the 19.2MHz IF to DC.

- The DC centered signal is zero stuffed to increase the rate from 76.8Msps to 153.6Msps. This is required, as the CIC uses only full rxclk rate input signals.

- The CIC filter is programmed to decimate by 10 using a m=2 comb section configuration. The output sample rate at the CIC output is 15.36Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 40 tap filter, which is the maximum length that can be computed with rxclk at 153.6MHz and the CFIR output rate of 7.68Msps.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

#### **UMTS**

- A UMTS carrier is applied to the GC5018 inputs with a simulated sample rate of 61.44Msps and an IF frequency of 15.36MHz.

- Simulated rxclk to the gc5018 is 122.88MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured to process the signal

- The mixer/nco shifts the 15.36MHz IF to DC.

- The DC centered signal is zero stuffed to increase the rate from 61.44Msps to 122.88Msps. This is required, as the CIC uses only full rxclk rate input signals.

- The CIC filter is programmed to decimate by 8 using a m=2 comb section configuration. The output sample rate at the CIC output is 15.36Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 32 tap filter, which is the maximum length that can be computed with rxclk at 122.88MHz and the CFIR output rate of 7.68Msps.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

#### CDMA2000

- A 3 carrier CDMA2000 signal is applied to the GC5018 inputs with a simulated sample rate of 78.6432Msps and an IF frequency of 9.83MHz.

- Simulated rxclk to the gc5018 is 78.6432MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured in CDMA mode and therefore processes two CDMA channels, referred to as A and B.

- A channel mixer/nco shifts the 11.08MHz carrier to DC, the B channel shifts the 8.58MHz carrier to DC.

- The CIC filter is programmed to decimate by 16 using a m=2 comb section configuration. The output sample rate at the CIC output is 4.9152Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 32 tap filter, which is the maximum length that can be computed with rxclk at 78.6432MHz and the CFIR output rate of 4.9152Msps.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

#### TD-SCDMA

- A 3 carrier TD-SCDMA signal is applied to the GC5018 inputs with a simulated sample rate of 76.8Msps and an IF frequency of 9.6MHz.

- Simulated rxclk to the gc5018 is 76.8MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured in CDMA mode and therefore processes two TD-SCDMA channels, referred to as A and B.

- A channel mixer/nco shifts the 11.2MHz carrier to DC, the B channel shifts the 8MHz carrier to DC.

- The CIC filter is programmed to decimate by 15 using a m=2 comb section configuration. The output sample rate at the CIC output is 5.12Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 28 tap filter, which is the maximum length that can be computed with rxclk at 76.8MHz and the CFIR output rate of 5.12Msps.

- The 60 tap PFIR provides final symbol shaping and filtering. 60 taps is the maximum length that can be computed with a 76.8MHz rxclk and 5.12Msps output rate

- Channel AGC is configured as fixed unity gain

- Baseband data is decimated by 2 in the output interface, and then transmitted and captured using the serial interface at the full rxclk rate.

#### 2.2.5. GC Studio References

For more information on GC Studio, see the GC Studio User's Manual included with the software distribution. GC Studio also contains a powerful scripting language for expert users, see the SCR GC101 Language Reference also included in the software distribution. Selecting Help > User's Manuals in the GC Studio menu to these documents.

# 3. GC5018 Daughtercard Description

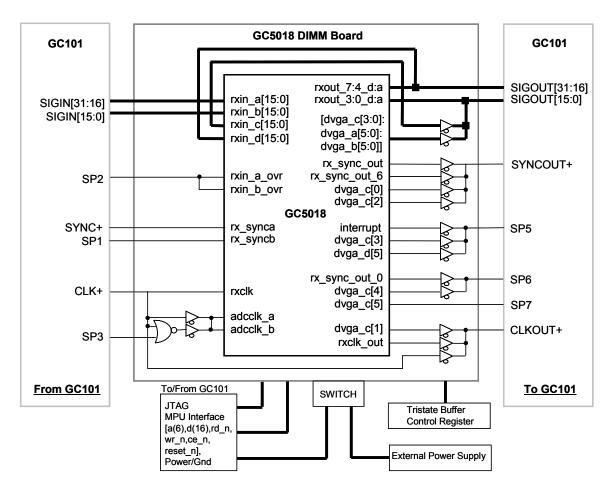

Figure 2. GC5018 Daughtercard Block Diagram

# 3.1. GC5018 Daughtercard to GC101 Motherboard Signal Description

The GC5018 Daughtercard has a PC-133 form-factor that utilizes the 168 pin DIMM memory connector. The 168 pin interface signals are divided into several groups:

# Memory Input Bus – 36 data inputs used to stimulate the GC5018 inputs

| SIGIN(35)    | also called SP3   | clock gating signal for adcclk_a and adcclk_b |

|--------------|-------------------|-----------------------------------------------|

| SIGIN(34)    | also called SP2   | rxin_a_ovr and rxin_b_ovr input signals       |

| SIGIN(33)    | also called SP1   | sync_b input signal                           |

| SIGIN(32)    | also called SYNC+ | sync_a input signal                           |

| SIGIN(31:16) |                   | rxin_a(15:0) input data                       |

| SIGIN(15:0)  |                   | rxin_b(15:0) input data                       |

# Memory Output Bus – 36 data output from selected GC5018 outputs captured by the GC101

| SIGOUT(35)    | also called SP7      | $dvga_c(5)$                              |

|---------------|----------------------|------------------------------------------|

| SIGOUT(34)    | also called SP6      | dvga_c(4) or rx_sync_out_0               |

| SIGOUT(33)    | also called SP5      | dvga_c(3), dvga_d(5) or interrupt        |

| SIGOUT(32)    | also called SYNCOUT+ | rx_sync_out, rx_sync_out_6, dvga_c(0) or |

|               |                      | dvga_c(2)                                |

| SIGOUT(31:16) |                      | rxout_7:4_d:a baseband DDC data or       |

|               |                      | rxin_d(15:0) testbus output              |

| SIGOUT(15:0)  |                      | rxout_3:0_d:a baseband DDC data or       |

|               |                      | rxin $c(15:0)$ testbus output            |

### Clock

| CLK+   | rxclk clock for GC5018; can be used as a full rate or gated clock source when |

|--------|-------------------------------------------------------------------------------|

|        | combined with the gating signal SP3 for the adcclk_a and adcclk_b inputs.     |

| CLKOUT | clock signal from the daughtercard to the GC101; rxclk, rxclk_out from the    |

|        | gc5018 or dvga_c(1).                                                          |

## Microprocessor Control Bus – Bus to program the internal registers

| 16 bit bidirectional data | d(15:0)                                             |

|---------------------------|-----------------------------------------------------|

| 11 bit address            | lower 6 bits connect to a(5:0) on the GC5018        |

|                           | bit 7 is used to address a control registers on the |

|                           | GC5018 daughter card                                |

| CE#, RD#, WR#, and RST#   | ce_n, rd_n, wr_n and rst_n on the GC5018            |

## <u>JTAG</u>

JTAG – 5 pin JTAG Test Port for GC5018 TRST#, TCK, TMS, TDI, TDO trst\_n, tck, tms, tdi and tdo on the GC5018

### Power and Ground

VDUT1 – 3.3V power from GC101 EVM to the daughtercard GND

See the GC101 EVM Manual for the 168 pin connector table. Detailed schematics for the GC5018 daughtercard can be found in Section 4.

### 3.2. GC5018 Daughtercard Jumpers

- 3.3V power for the GC5018 daughtercard can be supplied by the GC101 motherboard or an external power supply. A regulator on the daughtercard can be used to generate the 1.5V core supply voltage or an external supply can be used.

- Jumper W1 Selects source for GC5018 core 1.5V power position 1:2 selects an external supply connected to J2 for the 1.5V core supply position 2:3 selects the regulator on the daughtercard as the 1.5V core supply

- Jumper U13 Enables the +1.5V regulator when jumper in 2:3 (center:on) position Disables the +1.5V regulator when jumper in 1:2 (off:center) position

- Jumper W2 Selects source for GC5018 I/O 3.3V power position 1:2 selects an external supply connected to J3 for the 3.3V I/O supply position 2:3 selects the GC101 motherboard as the source for the 3.3V I/O supply

- Jumper W3 pin 1 is DVDDMON testpoint, DO NOT INSTALL A JUMPER. Jumper W4 pin 1 is DVSSMON testpoint, DO NOT INSTALL A JUMPER.

### 3.3. GC5018 Daughtercard Power Supplies

The GC5018 core power supply is 1.5V. The daughtercard includes a regulator that can be used to supply this 1.5V to the GC5018 or an external power supply can be connected at J2. The regulator can be enabled or disabled via the jumper located below U13 and above TP3.

The GC5018 I/O power supply is 3.3V, and can be supplied by the GC101 motherboard or an external power supply connected to J3.

## 4. Detailed GC5018 Daughtercard Schematic