# OMAP5910 Dual-Core Processor Universal Serial Bus (USB) and Frame Adjustment Counter (FAC) Reference Guide

Literature Number: SPRU677 October 2003

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated

# **Read This First**

#### About This Manual

This document describes the universal serial bus (USB) and frame adjustment counter (FAC) host of the OMAP5910 multimedia processor.

#### **Notational Conventions**

This document uses the following conventions.

☐ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### Related Documentation From Texas Instruments

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

*OMAP5910 Dual-Core Processor MPU Subsystem Reference Guide* (literature number SPRU671)

OMAP5910 Dual-Core Processor DSP Subsystem Reference Guide (literature number SPRU672)

OMAP5910 Dual-Core Processor Memory Interface Traffic Controller Reference Guide (literature number SPRU673)

*OMAP5910 Dual-Core Processor System DMA Controller Reference Guide* (literature number SPRU674)

*OMAP5910 Dual-Core Processor LCD Controller Reference Guide* (literature number SPRU675)

OMAP5910 Dual-Core Processor Universal Asynchronous Receiver/Transmitter (UART) Devices Reference Guide (literature number SPRU676)

OMAP5910 Dual-Core Processor Universal Serial Bus (USB) and Frame Adjustment Counter (FAC) Reference Guide (literature number SPRU677)

OMAP5910 Dual-Core Processor Clock Generation and System Reset Management Reference Guide (literature number SPRU678)

OMAP5910 Dual-Core Processor General-Purpose Input/Output (GPIO) Reference Guide (literature number SPRU679)

*OMAP5910 Dual-Core Processor MMC/SD Reference Guide* (literature number SPRU680)

OMAP5910 Dual-Core Processor Inter-Integrated Circuit (I2C) Controller Reference Guide (literature number SPRU681)

*OMAP5910 Dual-Core Processor Timer Reference Guide* (literature number SPRU682)

OMAP5910 Dual-Core Processor Inter-Processor Communication Reference Guide (literature number SPRU683)

*OMAP5910 Dual-Core Processor Camera Interface Reference Guide* (literature number SPRU684)

OMAP5905 Dual-Core Processor Multichannel Serial Interface (MCSI) Reference Guide (literature number SPRU685)

*OMAP5910 Dual-Core Processor Micro-Wire Interface Reference Guide* (literature number SPRU686)

OMAP5910 Dual-Core Processor Real-Time Clock (RTC) Reference Guide (literature number SPRU687)

OMAP5910 Dual-Core Processor HDQ/1-Wire Interface Reference Guide (literature number SPRU688)

OMAP5910 Dual-Core Processor PWL, PWT, and LED Peripheral Reference Guide (literature number SPRU689)

OMAP5910 Dual-Core Processor Multichannel Buffered Serial Port (McBSP)

Reference Guide (literature number SPRU708)

#### **Trademarks**

OMAP and the OMAP symbol are trademarks of Texas Instruments.

# **Contents**

| 1 | USB          | Host Controller 1                                                                             | 1   |

|---|--------------|-----------------------------------------------------------------------------------------------|-----|

| 2 | <b>USB</b> ( | Open Host Controller Interface Functionality       1         OHCI Controller Overview       1 |     |

|   | 2.2          | OMAP5910 USB Host Controller/OHCI Specification Differences                                   |     |

|   |              | 2.2.1 Power Switching Output Pins Not Supported                                               |     |

|   |              | 2.2.2 Overcurrent Protection Input Pins Not Supported 1                                       |     |

|   |              | 2.2.3 HMC MODE and Top-Level Pin Multiplexing and OHCI Registers                              |     |

|   |              | 2.2.4 No Ownership Change Interrupt                                                           |     |

|   |              | 2.2.5 Valid Address Ranges for Pointers to Data Structures                                    |     |

|   | 2.3          | OMAP5910 Implementation of OHCI Specification for USB                                         |     |

|   |              | 2.3.1 Isochronous TD OFFSETX/PSWX Values                                                      | 5   |

|   |              | 2.3.2 OMAP5910 USB Host Controller Endpoint Descriptor (ED)                                   |     |

|   |              | List Head Pointers 1                                                                          | 6   |

| 3 | HERI         | Host Controller Registers 1                                                                   | 7   |

| 3 | 3.1          | USB Host Controller Reserved Registers and Reserved Bit Fields                                |     |

|   | 3.1          | Endianism and USB Host Controller Registers                                                   |     |

|   | 3.3          | USB Host Controller Registers, USB Reset, and USB Clocking                                    |     |

|   |              |                                                                                               |     |

| 4 | USB          | Host Controller Interrupt Sources5                                                            | 5   |

|   | 4.1          | OHCI Interrupts                                                                               | 55  |

|   |              | 4.1.1 OHCI Scheduling Overrun Interrupt 5                                                     | 55  |

|   |              | 4.1.2 OHCI HcDoneHead Writeback Interrupt 5                                                   | 55  |

|   |              | 4.1.3 OHCI Start Of Frame Interrupt                                                           | 55  |

|   |              | 4.1.4 OHCI Resume Detect Interrupt 5                                                          | 55  |

|   |              | 4.1.5 OHCI Unrecoverable Error Interrupt                                                      |     |

|   |              | 4.1.6 OHCI Frame Number Overflow                                                              |     |

|   |              | 4.1.7 OHCI Root Hub Status Change                                                             |     |

|   |              | 4.1.8 OHCI Ownership Change Interrupt                                                         |     |

|   | 4.2          | Local Bus MMU Interrupts                                                                      | 6   |

| 5 | USBI         | Pin Multiplexing 5                                                                            | . 7 |

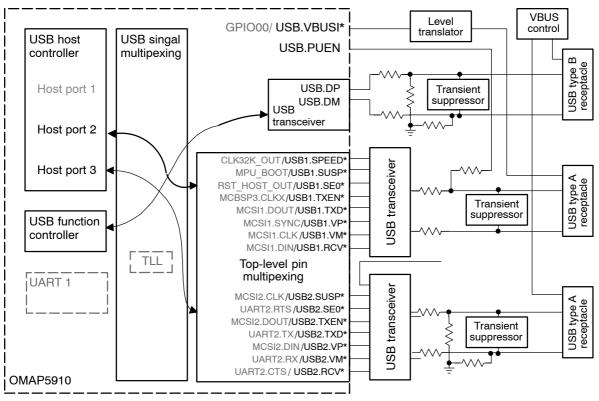

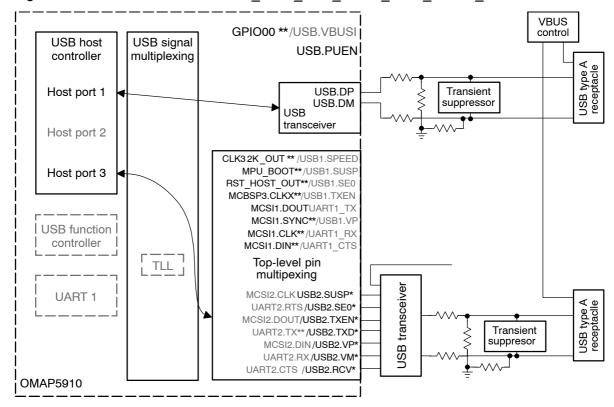

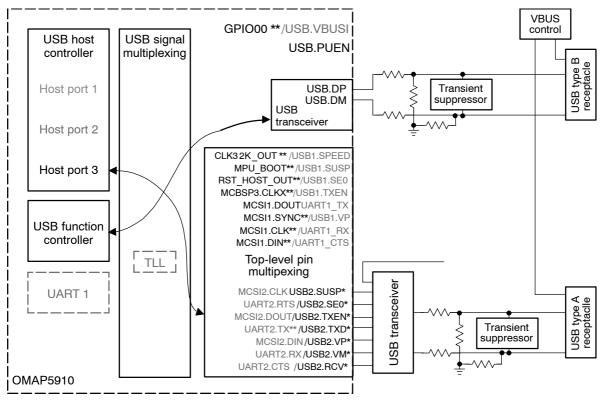

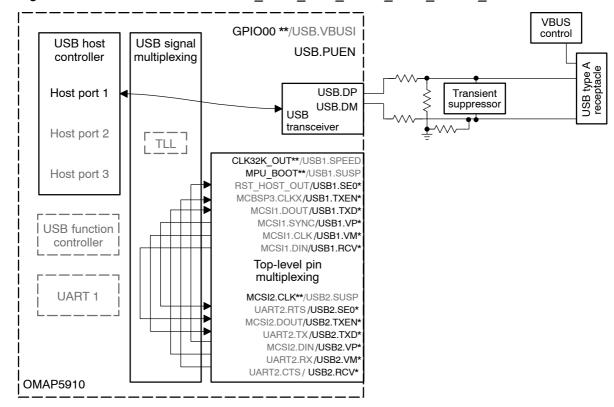

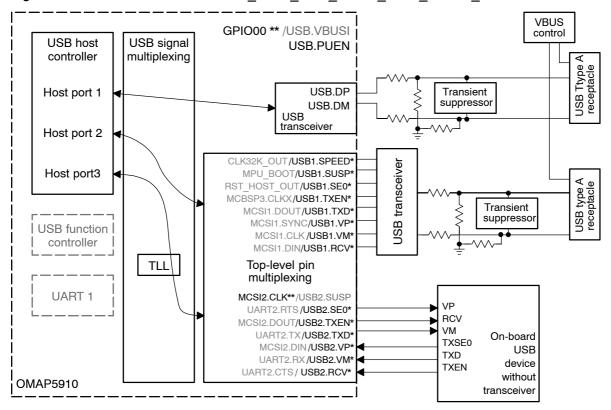

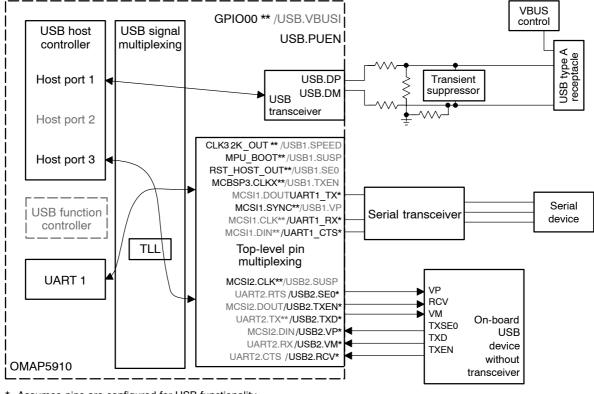

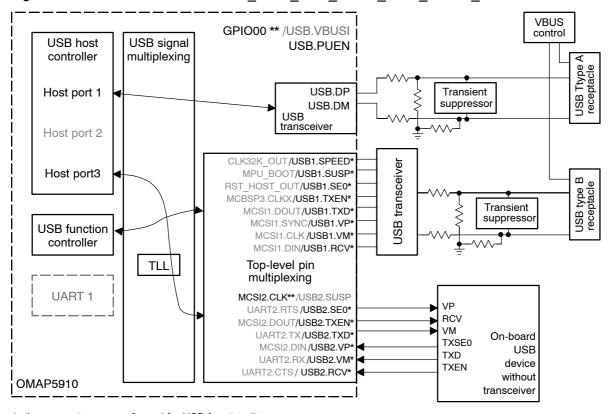

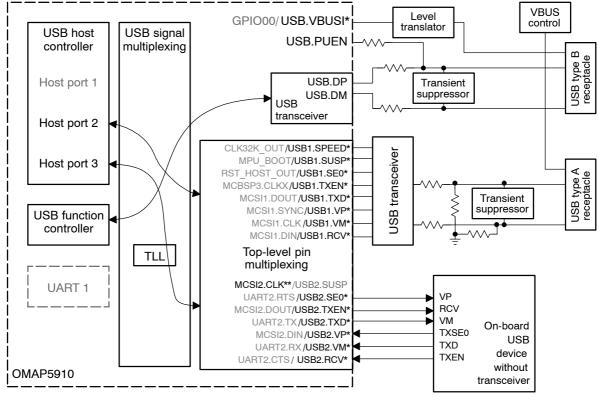

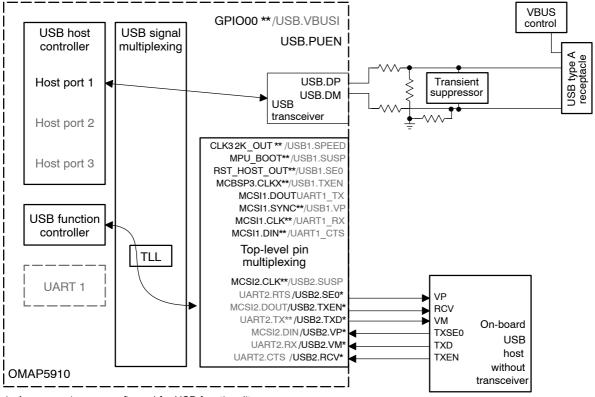

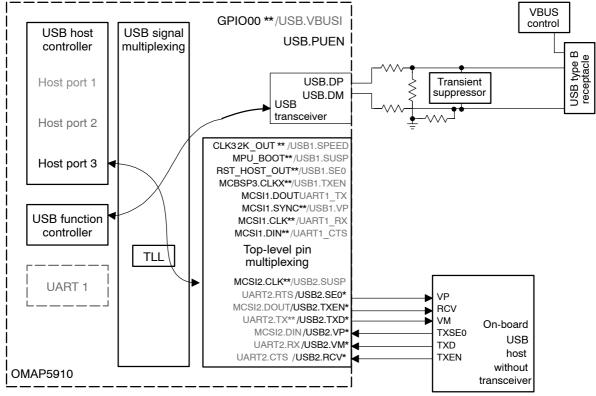

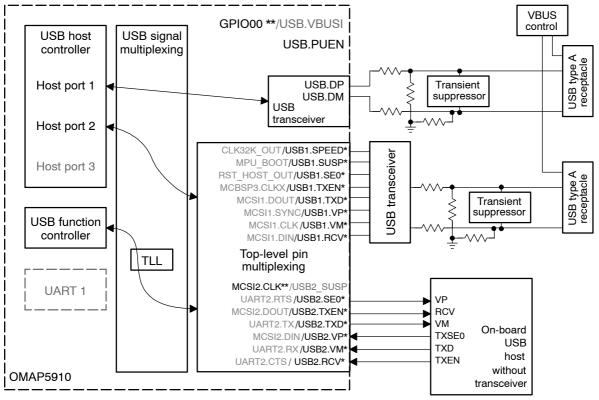

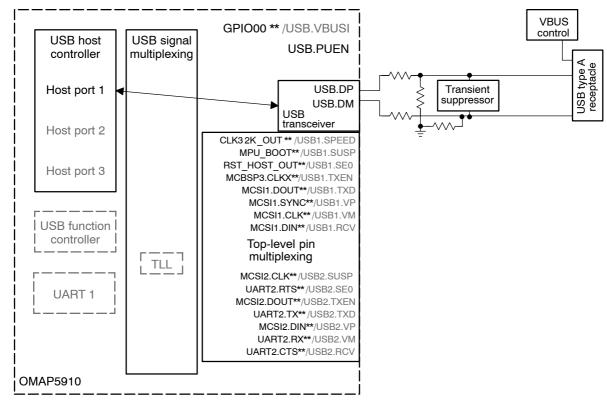

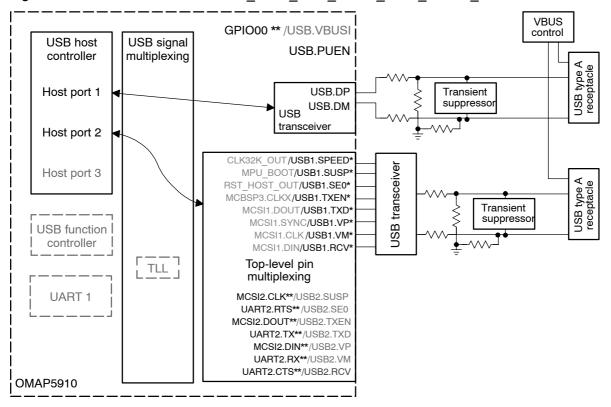

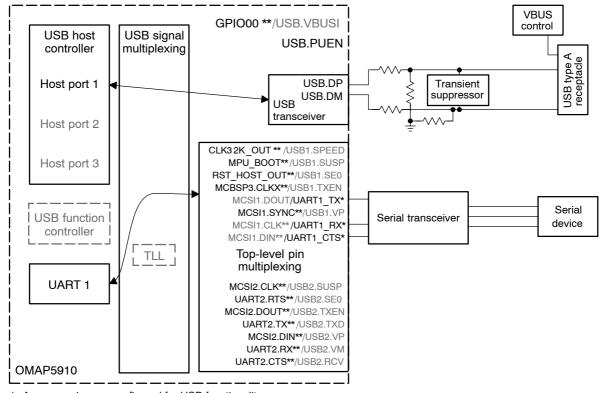

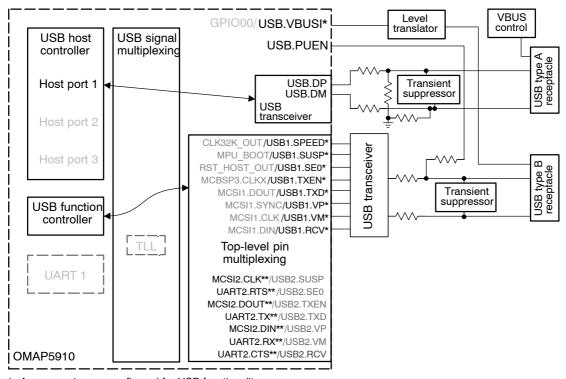

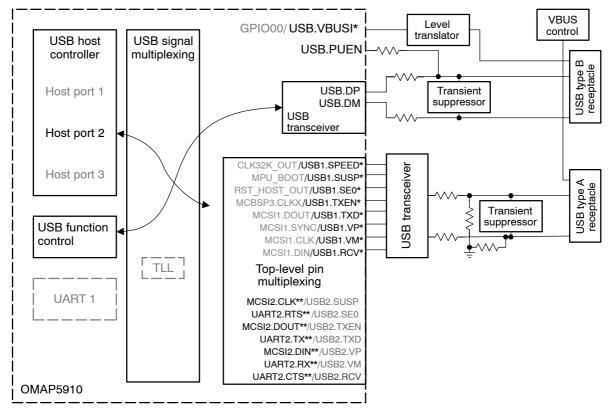

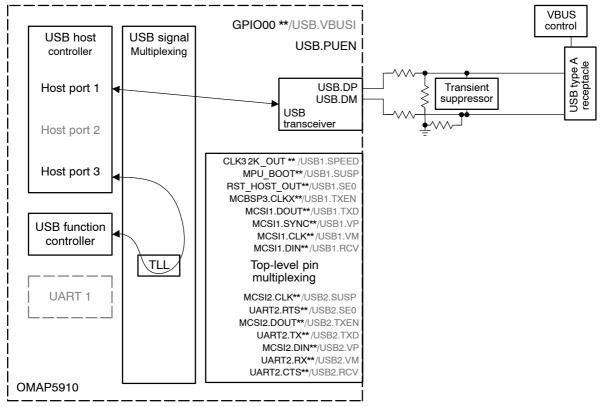

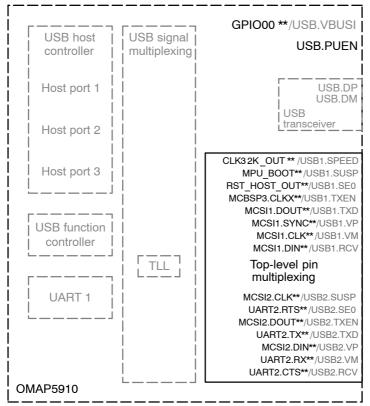

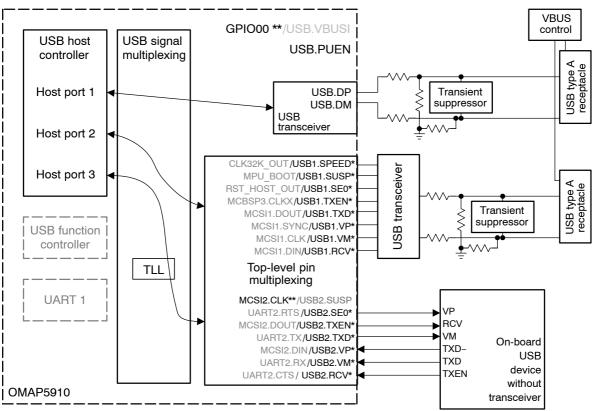

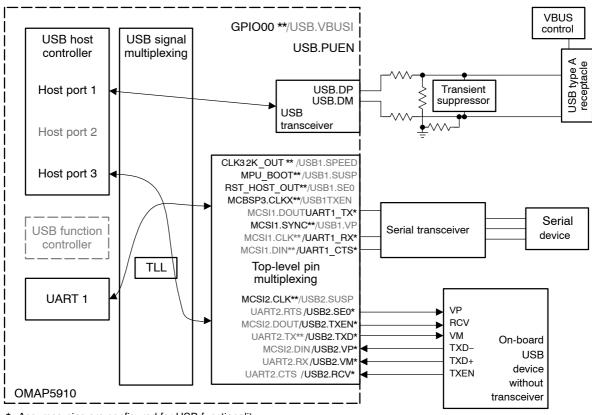

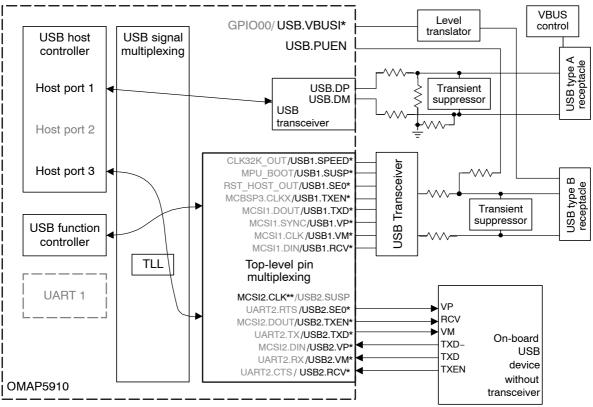

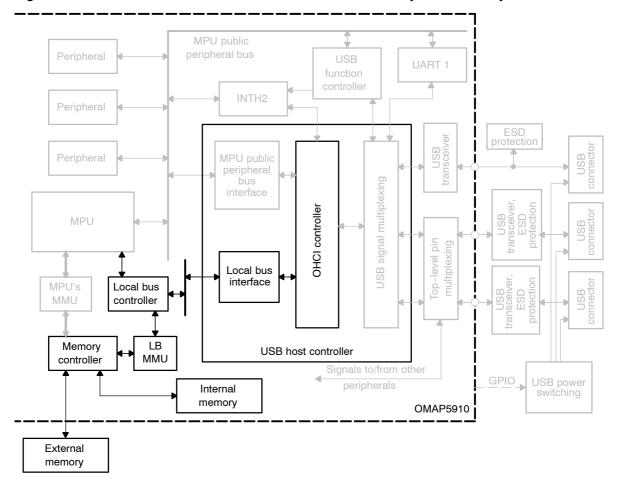

| • | 5.1          | Host Controller Connectivity With USB Transceivers                                            |     |

|   | 5.2          | USB Function Controller Connectivity With USB Transceivers                                    |     |

|   | 5.3          | On-Board Transceiverless Connection Using                                                     |     |

|   | 5.5          | OMAP5910 Transceiverless Link Logic                                                           | 30  |

|   |              |                                                                                               |     |

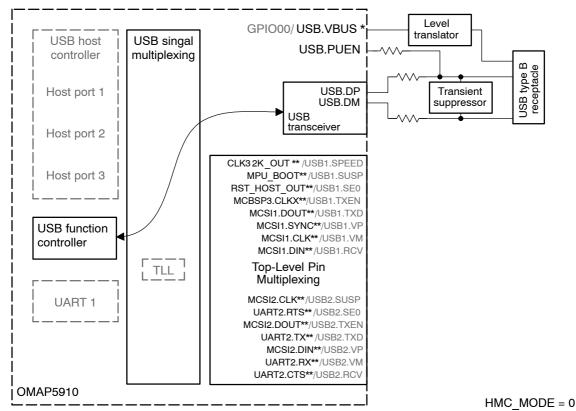

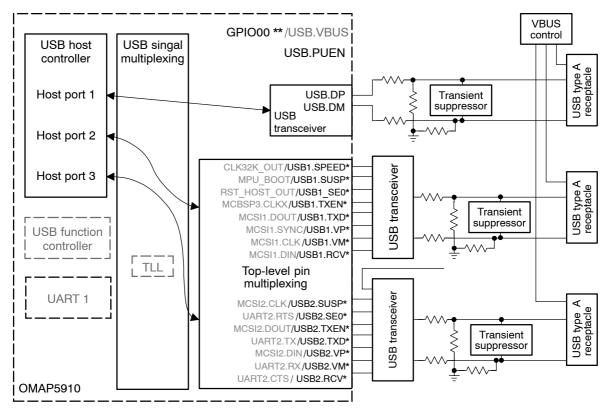

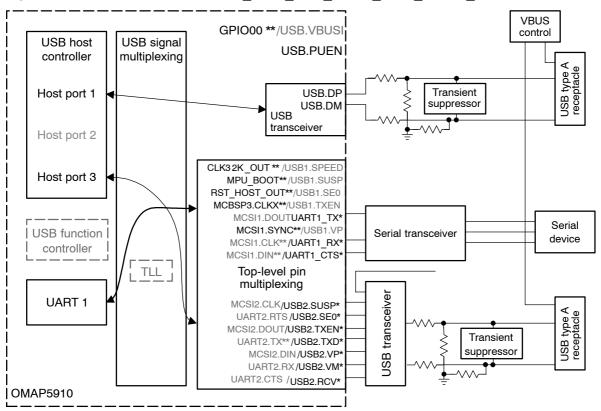

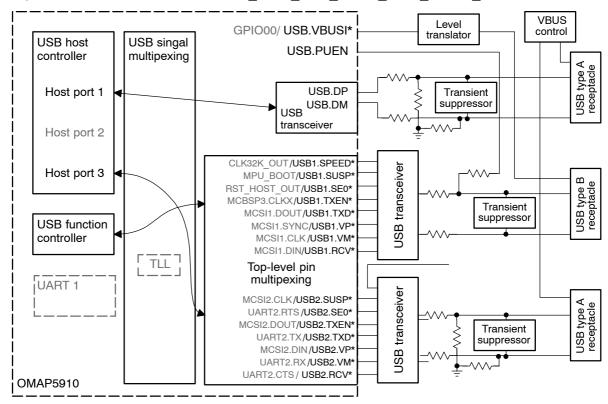

|   | 5.4        |         | ignal Multiplexing Mode Diagrams                                                   |         |

|---|------------|---------|------------------------------------------------------------------------------------|---------|

|   | 5.5<br>5.6 |         | Shown as Unconnected                                                               |         |

|   |            |         |                                                                                    |         |

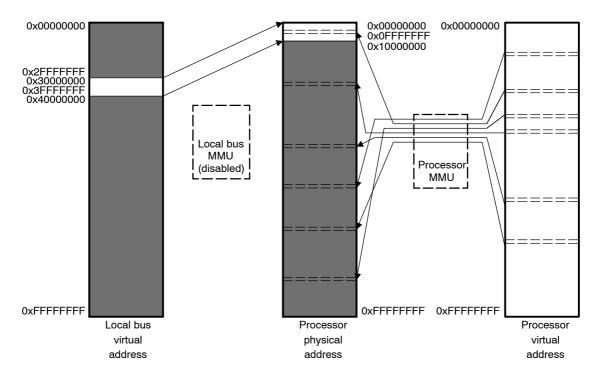

| 6 |            |         | ontroller Access to System Memory                                                  |         |

|   | 6.1        |         | Bus Virtual Addressing                                                             |         |

|   | 6.2        |         | Coherency in OHCI Data Structures and Data Buffers                                 |         |

|   | 6.3        |         | Bus Addressing and OHCI Data Structure Pointers                                    | 97      |

|   |            | 6.3.1   | MPUVAtoLBVA()—MPU Virtual Address to Local Bus Virtual Address Conversion Function | 97      |

|   |            | 6.3.2   | LBVAtoMPUVA()—Local Bus Virtual Address to MPU Virtual Address                     | 07      |

|   |            |         | Conversion Function                                                                | 98      |

|   |            | 6.3.3   | MPUVAtoPA()—MPU Virtual Address to Physical Address Conversion Function            | ΩQ      |

|   |            | 6.3.4   | LBVAtoPA()—Local Bus Virtual Address to Physical Address Conversion                | 90      |

|   |            | 0.0.4   | Function                                                                           | 99      |

|   |            | 6.3.5   | PAtoLBVA()—Physical Address to Local Bus Virtual Address Conversion                |         |

|   |            |         | Function                                                                           | 99      |

|   |            | 6.3.6   | PAtoMPUVA()—Physical Address to MPU Virtual Address Conversion Function            | 99      |

|   |            | 6.3.7   | Physical, MPU Virtual, and Local Bus Virtual Addresses—an Example                  |         |

|   | 6.4        | NULL    | Pointers                                                                           |         |

|   | 6.5        | Endiar  | nism and USB Host Controller Access to System Memory                               | 103     |

|   |            | 6.5.1   | Endianism and OHCI Endpoint and Transfer Descriptors                               | 103     |

|   |            | 6.5.2   | Endianism and OHCI Data Buffers                                                    | 104     |

| 7 | ОМА        | P5910 L | ocal Bus                                                                           | . 105   |

| - | 7.1        |         | gister Descriptions                                                                |         |

|   | 7.2        |         | U Time-out Register (LB MPU TIMEOUT)                                               |         |

|   | 7.3        |         | ld Timer Register (LB HOLD TIMER)                                                  |         |

|   | 7.4        |         | prity Register (LB_PRIORITY_REG)                                                   |         |

|   | 7.5        |         | ck Divider Register (LB CLOCK DIV)                                                 |         |

|   | 7.6        |         | ort Address Register (LB ABORT ADD)                                                |         |

|   | 7.7        |         | ort Data Register (LB ABORT DATA)                                                  |         |

|   | 7.8        |         | ort Status Register (LB ABORT STATUS)                                              |         |

|   | 7.9        |         | Q Output Register (LB IRQ OUTPUT)                                                  |         |

|   | 7.10       | LB IRC  | Q Input Register (LB_IRQ_INPUT)                                                    | 112     |

|   | 7.11       |         | Bus Initialization                                                                 |         |

|   | 7.12       | Local E | Bus Virtual Addressing                                                             | 113     |

| 8 | ОМА        | P5910 L | ocal Bus MMU                                                                       | 114     |

| _ | 8.1        |         | 5910 Local Bus MMU Registers                                                       |         |

|   | 8.2        |         | Bus MMU Programming for USB Host Controller Operation                              |         |

|   |            | 8.2.1   | Local Bus MMU Page Size and the USB Host Controller                                |         |

|   |            | 8.2.2   | Local Bus MMU and Page Protection                                                  |         |

|   |            | 8.2.3   | Local Bus MMU Page Miss                                                            |         |

|   |            |         | ·g- ···· · · · · · · · · · · · · · · ·                                             | · · — · |

| 9  | USB   | Host Controller Reset and Clock Control              | 129  |

|----|-------|------------------------------------------------------|------|

|    | 9.1   | USB Host Controller Clock Control                    | 129  |

|    | 9.2   | Initializing ULPD to Generate the 48-MHz Clock       | 129  |

|    | 9.3   | USB Host Controller Hardware Reset                   | 130  |

|    | 9.4   | USB Host Controller OHCI Reset                       | 130  |

|    | 9.5   | USB Host Controller Power Management                 | 130  |

|    | 9.6   | Local Bus Clock                                      |      |

| 10 | ΟΜΔΙ  | P5910 USB Hardware Considerations                    | 132  |

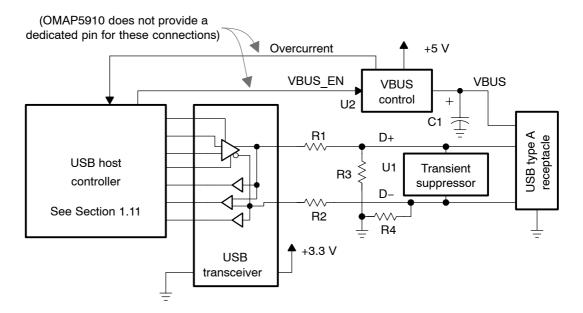

|    | 10.1  | VBUS Power Switching For USB Type A Host Receptacles |      |

|    | 10.2  | Transient Suppression for USB Connectors             |      |

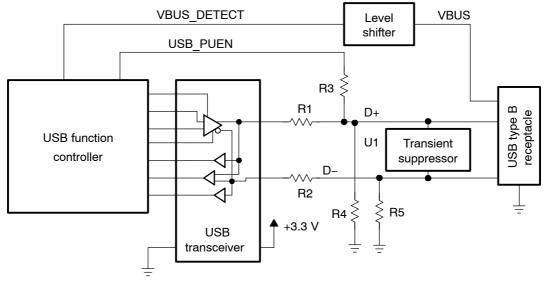

|    | 10.3  | VBUS Monitoring for USB Function Controller          |      |

|    | 10.4  | USB D+ Pullup Enable for USB Function Controller     |      |

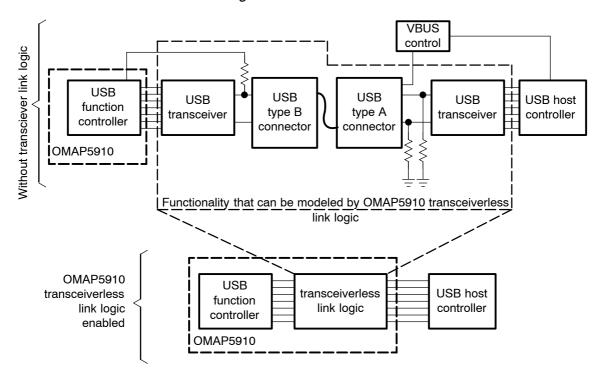

|    | 10.5  | Port Passthrough Mode                                |      |

|    | 10.6  | UART1 Connectivity when CONF_MOD_USB_HOST_HMC_MODE_R | 100  |

|    | 10.0  | = 2, 10, 18, and 24                                  | 133  |

|    | 10.7  | MPU BOOT Signal Sharing                              |      |

|    | 10.8  | USB D+, D- Pulldown for USB Function Controller      |      |

|    |       |                                                      |      |

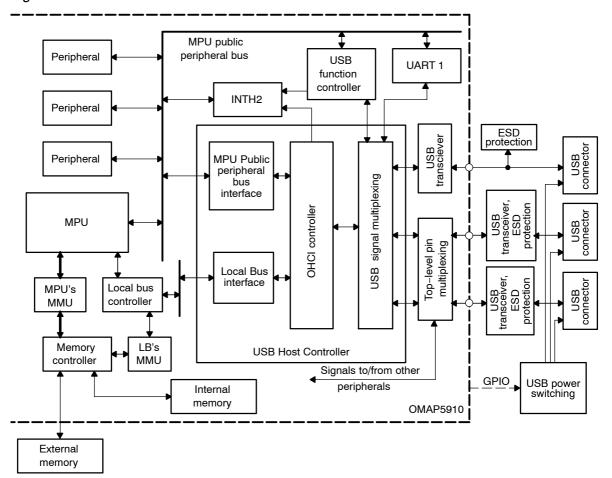

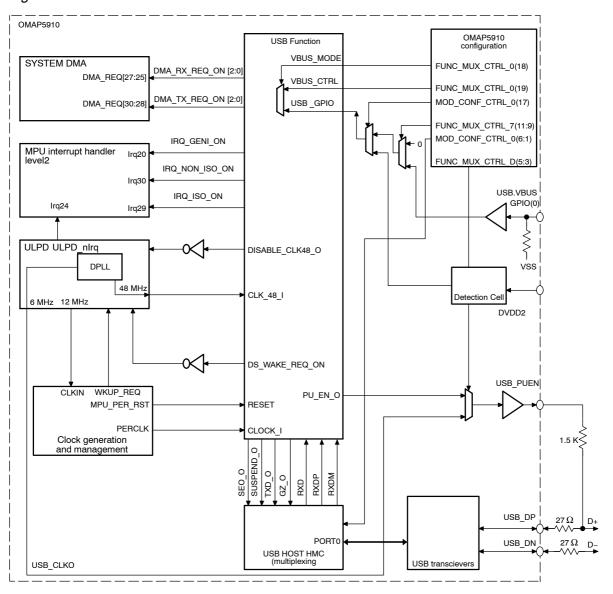

| 11 |       | view of the OMAP5910 USB Functional Module           |      |

|    | 11.1  | OMAP5910 Inputs/Outputs                              |      |

|    | 11.2  | USB Function Interrupts                              |      |

|    | 11.3  | USB Function Clocks and Reset                        |      |

|    | 11.4  | USB Function DMA Requests                            |      |

|    | 11.5  | USB Detection                                        |      |

|    |       | 11.5.1 Software Detection                            | 138  |

|    |       | 11.5.2 Hardware Detection                            |      |

|    |       | GPIO0 Detection                                      | 139  |

|    |       | I/O Power Supply Detection                           | 139  |

|    | 11.6  | Software Disconnect                                  | 140  |

| 12 | Regis | ster Map                                             | 141  |

|    | 12.1  | Revision Register (REV)                              |      |

|    |       | 12.1.1 REV NB                                        |      |

|    | 12.2  | Endpoint Selection Register (EP NUM)                 |      |

|    |       | 12.2.1 Setup FIFO Select (Setup Sel)                 |      |

|    |       | 12.2.2 TX/RX FIFO Select (EP_Sel)                    |      |

|    |       | 12.2.3 Endpoint Direction (EP_Dir)                   |      |

|    |       | 12.2.4 Endpoint Number (EP_Num)                      |      |

|    | 12.3  | Data Register (DATA)                                 |      |

|    |       | 12.3.1 Transmit/Receive FIFO Data (DATA)             |      |

|    | 12.4  | Control Register (CTRL)                              |      |

|    |       | 12.4.1 Clear Halt Endpoint (Clr Halt)                |      |

|    |       | 12.4.2 Set Halt Endpoint (Set Halt)                  |      |

|    |       | 12.4.3 Set FIFO Enable (Set_FIFO_En)                 |      |

|    |       | 12.1.5 Oct. 11 O Eliable (Oct. 11 O_Eli)             | 1 70 |

|       | 12.4.4 Clear Endpoint (Clr_EP)                                  | 149 |

|-------|-----------------------------------------------------------------|-----|

|       | 12.4.5 Endpoint Reset (Reset_EP)                                | 149 |

| 12.5  | Status Register (STAT_FLG)                                      | 150 |

|       | 12.5.1 Isochronous Missed IN Token (Miss_In)                    | 151 |

|       | 12.5.2 Isochronous Receive Data Flush (Data_Flush)              | 151 |

|       | 12.5.3 Isochronous Receive Data Error (ISO_Err)                 | 152 |

|       | 12.5.4 Isochronous FIFO Empty (ISO_FIFO_Empty)                  | 152 |

|       | 12.5.5 Isochronous FIFO Full (ISO_FIFO_Full)                    | 152 |

|       | 12.5.6 Endpoint Halted Flag (EP_Halted)                         | 153 |

|       | 12.5.7 Transaction Stall (STALL)                                | 153 |

|       | 12.5.8 Transmit Non-Acknowledge (NAK)                           | 153 |

|       | 12.5.9 Transaction Acknowledge (ACK)                            | 154 |

|       | 12.5.10 FIFO Enable (FIFO_En)                                   | 154 |

|       | 12.5.11 Non-Isochronous FIFO Empty (Non_ISO_FIFO_Empty)         | 154 |

|       | 12.5.12 Non-Isochronous FIFO Full (Non_ISO_FIFO_Full)           | 155 |

| 12.6  | Receive FIFO Status Register (RXFSTAT)                          | 155 |

|       | 12.6.1 Receive FIFO Byte Count (RXF_Count)                      | 155 |

| 12.7  | System Configuration Register 1 (SYSCON1)                       | 156 |

|       | 12.7.1 Device Configuration Locked (Cfg_lock)                   | 156 |

|       | 12.7.2 NAK Enable (Nak_En:)                                     | 157 |

|       | 12.7.3 Self-Powered (Self_Pwr)                                  | 157 |

|       | 12.7.4 Shutoff Disable (SOFF_Dis)                               | 157 |

|       | 12.7.5 External Pullup Enable (Pullup_En)                       | 158 |

| 12.8  | System Configuration Register 2 (SYSCON2)                       | 159 |

|       | 12.8.1 Remote Wakeup (Rmt_Wkp)                                  | 159 |

|       | 12.8.2 Stall Command (Stall_Cmd)                                | 160 |

|       | 12.8.3 Device Cond (Dev_Cfg)                                    | 160 |

|       | 12.8.4 Clear Cond (Clr_Cfg)                                     | 160 |

| 12.9  | Device Status Register (DEVSTAT)                                | 161 |

|       | 12.9.1 Remote Wakeup Enabled (R_WK_OK)                          | 162 |

|       | 12.9.2 USB Reset Signaling (USB_Reset)                          | 162 |

|       | 12.9.3 Suspended State (SUS)                                    | 162 |

|       | 12.9.4 Cond State (CFG)                                         | 163 |

|       | 12.9.5 Addressed State (ADD)                                    | 163 |

|       | 12.9.6 Default State (DEF)                                      | 163 |

|       | 12.9.7 Attached State (ATT)                                     | 163 |

| 12.10 | Start of Frame Register (SOF)                                   |     |

|       | 12.10.1 Frame Timer Locked (FT_Lock)                            | 164 |

|       | 12.10.2 Time Stamp OK(TS_OK)                                    |     |

|       | 12.10.3 Time Stamp Number(TS)                                   |     |

| 12.11 | Interrupt Enable Register (IRQ_EN)                              |     |

|       | Interrupt Source Register (IRQ_SRC)                             |     |

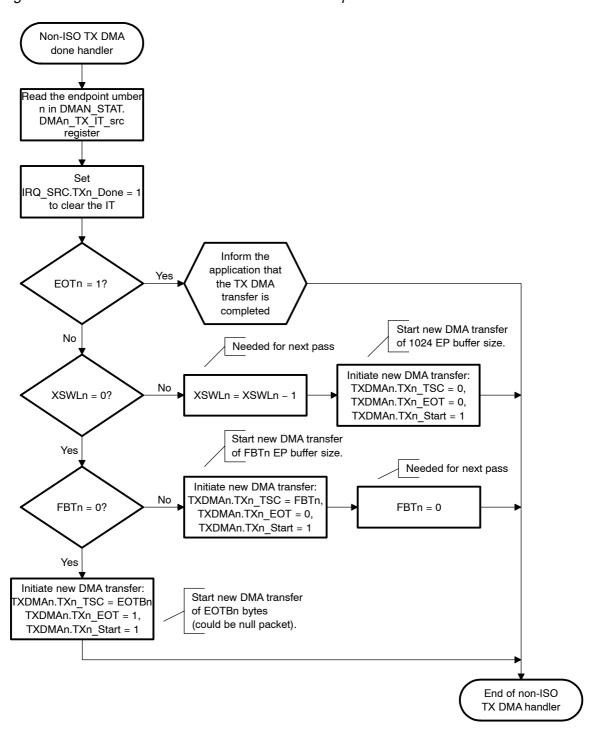

|       | 12.12.1 Transmit DMA CH.n Done Interrupt Flag (TXn_Done)        | 168 |

|       | 12.12.2 RX DMA CH.n Transactions Count Interrupt Flag (RXn_Cnt) |     |

|       | 12.12.3 Receive DMA CH.n EOT Interrupt Flag (RXn_EOT)                | . 169 |

|-------|----------------------------------------------------------------------|-------|

|       | 12.12.4 Start Of Frame Interrupt Flag (SOF)                          |       |

|       | 12.12.5 OUT Transaction Endpoint n Interrupt Flag (EPn_RX)           | . 170 |

|       | 12.12.6 IN Transaction Endpoint n Interrupt Flag (EPn_TX)            | . 170 |

|       | 12.12.7 Device State Changed Interrupt Flag (DS_Chg)                 |       |

|       | 12.12.8 Setup Transaction Interrupt Flag (Setup)                     |       |

|       | 12.12.9 OUT Transaction Endpoint 0 Interrupt Flag (EP0_RX)           | . 171 |

|       | 12.12.10 IRQ_SRC[0].EP0_TX: IN Transaction Endpoint 0 Interrupt Flag |       |

| 12.13 | Non-Isochronous Endpoint Interrupt Status Register (EPN_STAT)        | . 171 |

|       | 12.13.1 Receive Endpoint Interrupt Source (EPn_RX_IT_src)            | . 172 |

|       | 12.13.2 Transmit Endpoint Interrupt Source (EPn_TX_IT_src)           | . 172 |

| 12.14 | Non-Isochronous DMA Interrupt Status Register (DMAN_STAT)            | . 173 |

|       | 12.14.1 DMA Receive Single Byte (DMAn_RX_SB)                         |       |

|       | 12.14.2 DMA Receive Interrupt Source (DMAn_RX_IT_src)                | . 174 |

|       | 12.14.3 DMA Transmit Interrupt Source (DMAn_TX_IT_src)               | . 174 |

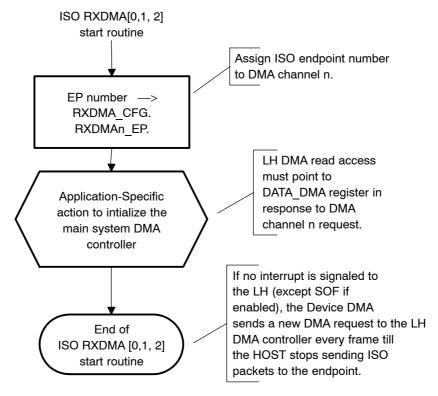

| 12.15 | Receive DMA Channels Configuration Register (RXDMA_CFG)              | . 175 |

|       | 12.15.1 Receive Endpoint Number for DMA Channel 2 (RXDMA2_EP)        | . 175 |

|       | 12.15.2 Receive Endpoint Number for DMA Channel 1 (RXDMA1_EP)        | . 176 |

|       | 12.15.3 Receive Endpoint Number for DMA Channel 0 (RXDMA0_EP)        | . 176 |

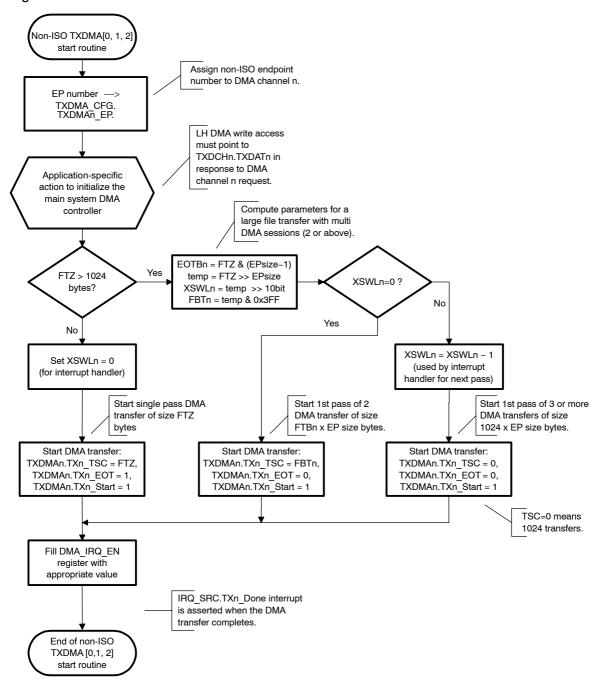

| 12.16 | Transmit DMA Channels Configuration Register (TXDMA_CFG)             | . 177 |

|       | 12.16.1 Transmit Endpoint Number for DMA Channel 2 (TXDMA2_EP)       | . 177 |

|       | 12.16.2 Transmit Endpoint Number for DMA Channel 1 (TXDMA1_EP)       | . 178 |

|       | 12.16.3 Transmit Endpoint Number for DMA Channel 0 (TXDMA0_EP)       | . 178 |

| 12.17 | DMA FIFO Data Register (DATA_DMA)                                    | . 179 |

|       | 12.17.1 DMA FIFO Data(DATA_DMA)                                      | . 179 |

| 12.18 | Transmit DMA Control Registers (TXDMA0TXDMA2)                        |       |

|       | 12.18.1 Transmit DMA Ch.n End of Transfer (TXn_EOT)                  | . 180 |

|       | 12.18.2 Transmit DMA Ch.n Start (TXn_Start)                          | . 181 |

|       | 12.18.3 Transmit DMA Ch.n Transfer Size Counter (TXn_TSC)            | . 181 |

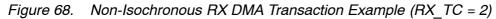

| 12.19 | Receive DMA Control Registers (RXDMARXDMA2)                          | . 182 |

|       | 12.19.1 Receive DMA Ch.n Transfer Stop (RXn_Stop)                    | . 182 |

|       | 12.19.2 Receive DMA Ch.n Transactions Count (RXn_TC)                 | . 182 |

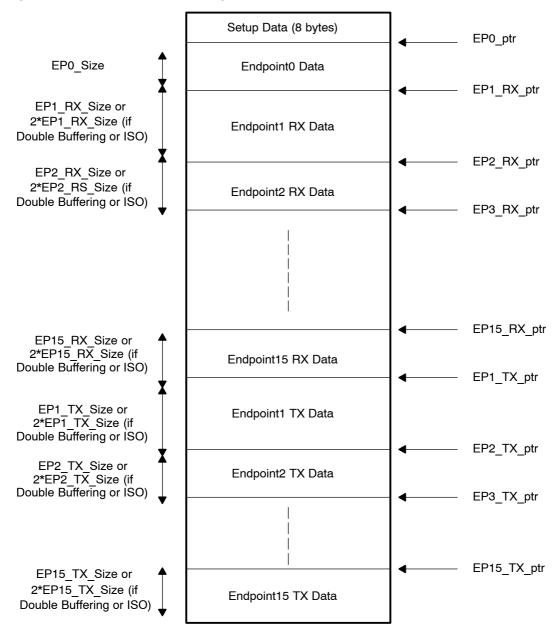

| 12.20 | Endpoint 0 Configuration Register (EP0)                              | . 183 |

|       | 12.20.1 Endpoint 0 FIFO Size (EP0_Size)                              |       |

|       | 12.20.2 Endpoint 0 Pointer (EP0_ptr)                                 | . 183 |

| 12.21 |                                                                      |       |

|       | 12.21.1 Receive Endpoint n Valid (EPn_RX_Valid)                      |       |

|       | 12.21.2 Receive Endpoint n Double-Buffer (EPn_RX_Db)                 |       |

|       | 12.21.3 Receive Endpoint n Size (EPn_RX_Size)                        |       |

|       | 12.21.4 Receive Isochronous Endpoint n(EPn_RX_Iso)                   |       |

|       | 12.21.5 Receive Endpoint n Pointer (EPn_RX_ptr)                      |       |

| 12.22 | Transmit Endpoint Configuration Registers (EP1_TXEP15_TX)            |       |

|       | 12.22.1 EPn_TX[15].EPn_TX_Valid: Transmit Endpoint n Valid           |       |

|       | 12.22.2 Transmit Endpoint n Double-Buffer(EPn TX Db)                 | . 187 |

|    |      | 12.22.3  | Transmit Endpoint n Size (EPn TX Size)                           | 188 |

|----|------|----------|------------------------------------------------------------------|-----|

|    |      |          | Transmit Isochronous Endpoint n (EPn_TX_Iso)                     |     |

|    |      |          | Transmit Endpoint n Pointer (EPn_TX_ptr)                         |     |

|    | HOD: | <b>T</b> | tions                                                            | 400 |

| 13 |      |          |                                                                  |     |

|    | 13.1 |          | ochronous, Non-Setup OUT (USB HOST -> LH) Transactions           |     |

|    |      | 13.1.1   | Non-Isochronous, Non-Control OUT Endpoint Handshaking Conditions |     |

|    |      |          | Acknowledged Transactions (ACK)                                  |     |

|    |      | 10.1.0   | Non-Acknowledged Transactions (NAK)                              |     |

|    |      | 13.1.2   | Non-Isochronous, Non-Control OUT Transaction Error Conditions    |     |

|    |      |          | STALLed Transactions                                             |     |

|    |      |          | Packet Errors                                                    |     |

|    |      | 10.1.0   | Sequence Bit Errors                                              |     |

|    | 40.0 |          | Non-Isochronous, Non-Control OUT Endpoint FIFO Error Conditions  |     |

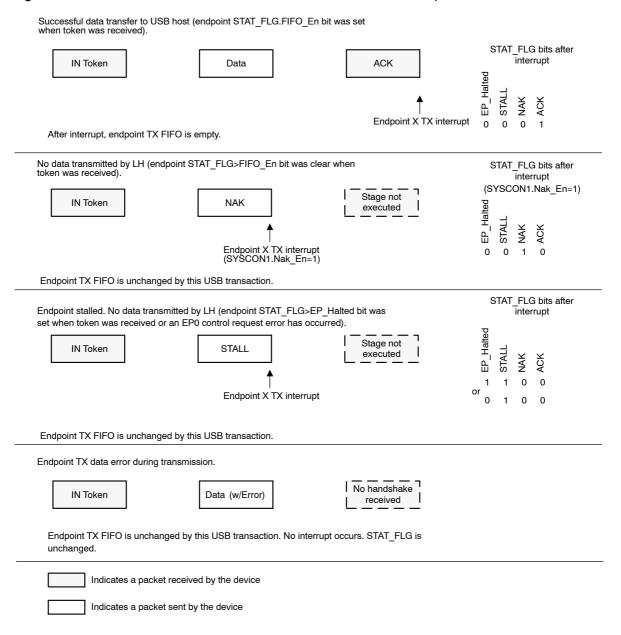

|    | 13.2 |          | ochronous IN (LH->USB HOST) Transactions                         |     |

|    |      | 13.2.1   | gg                                                               |     |

|    |      |          | Acknowledged Transactions (ACK)                                  |     |

|    |      | 4000     | Non-must Transactions (NAK)                                      |     |

|    |      | 13.2.2   | Non-Isochronous IN Transaction Error Conditions                  |     |

|    |      |          | STALLed Transactions                                             |     |

|    |      |          | Packet Errors                                                    |     |

|    | 40.0 |          |                                                                  |     |

|    | 13.3 |          | nous OUT (USB HOST-> LH) Transactions                            |     |

|    |      | 13.3.1   | Isochronous OUT Endpoint Handshaking                             |     |

|    |      |          | Isochronous OUT Transaction Error Conditions                     |     |

|    |      |          | Isochronous OUT Endpoint FIFO Error Conditions                   |     |

|    | 13.4 |          | nous IN (LH->USB HOST) Transactions                              |     |

|    |      |          | Isochronous IN Endpoint Handshaking                              |     |

|    |      |          | Isochronous IN Transaction Error Conditions                      |     |

|    |      |          | Isochronous IN Endpoint FIFO Error Conditions                    |     |

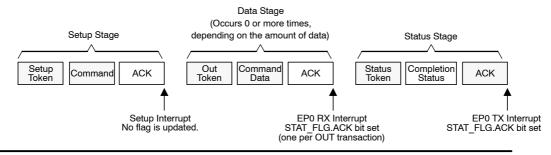

|    | 13.5 |          | Transfers on Endpoint 0                                          |     |

|    |      | 13.5.1   | Autodecoded Control Write Transfers                              |     |

|    |      |          | Autodecoded Control Write Transfer Handshaking                   |     |

|    |      |          | Autodecoded Control Write Transfer Error Conditions              |     |

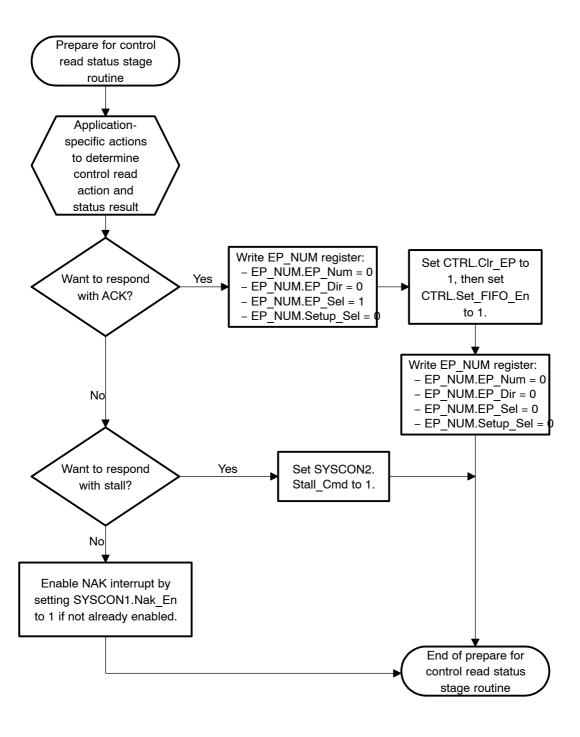

|    |      | 13.5.2   | Autodecoded Control Read Transfers                               |     |

|    |      |          | Autodecoded Control Read Transfer Handshaking                    |     |

|    |      |          | Autodecoded Control Read Transfer Error Conditions               |     |

|    |      | 13.5.3   |                                                                  |     |

|    |      |          | Specific Local Host Required Actions                             |     |

|    |      |          | Non-Autodecoded Control Write Transfer Handshaking               |     |

|    |      |          | Non-Autodecoded Control Write Transfer Error Conditions          |     |

|    |      | 13.5.4   | Non-Autodecoded Control Read Transfers                           |     |

|    |      |          | Non-Autodecoded Control Read Transfer Handshaking                |     |

|    |      |          | Non-Autodecoded Control Read Transfer Error Conditions           | 214 |

|                      |                                                                                                   |                                                                                                            | Autodecoded Versus Non-Autodecoded Control Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                      |                                                                                                   | 13.5.6                                                                                                     | Note on Control Transfers Data Stage Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 217                                                                       |

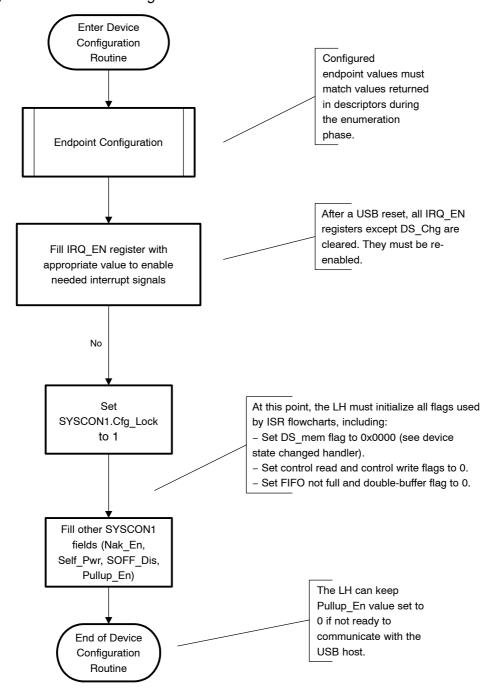

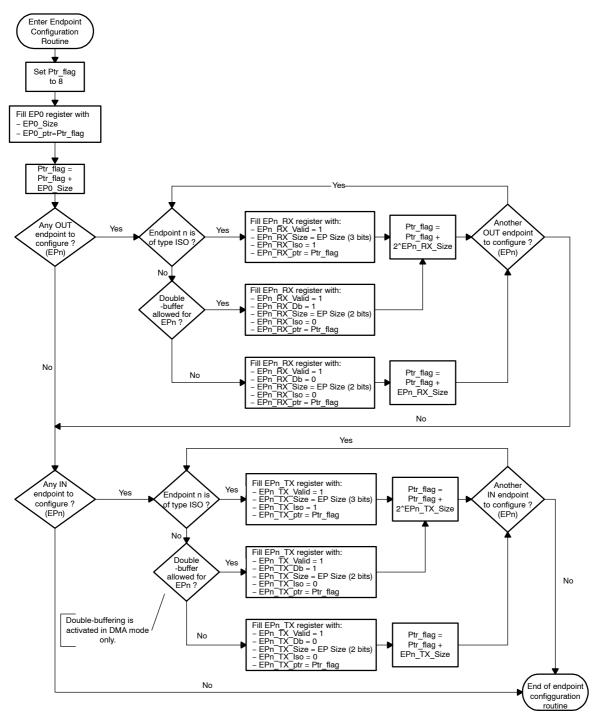

| 14                   | Devic                                                                                             | e Initial                                                                                                  | ization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 219                                                                       |

|                      |                                                                                                   |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

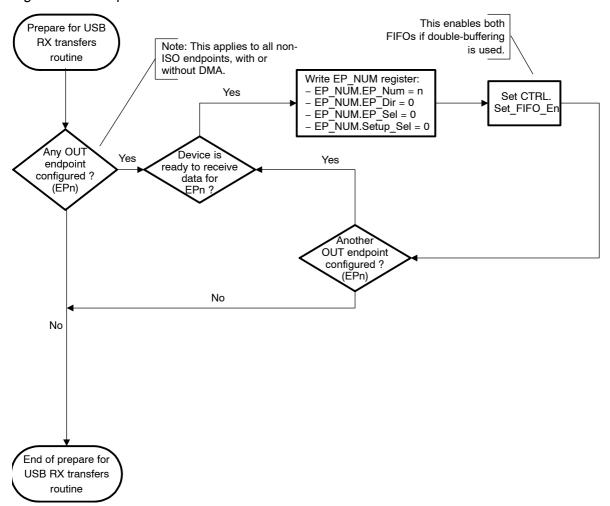

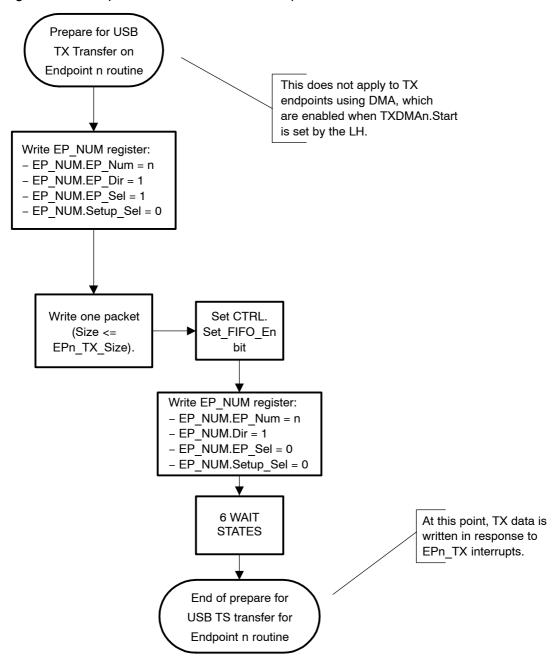

| 15                   | Prepa                                                                                             | ring for                                                                                                   | Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223                                                                       |

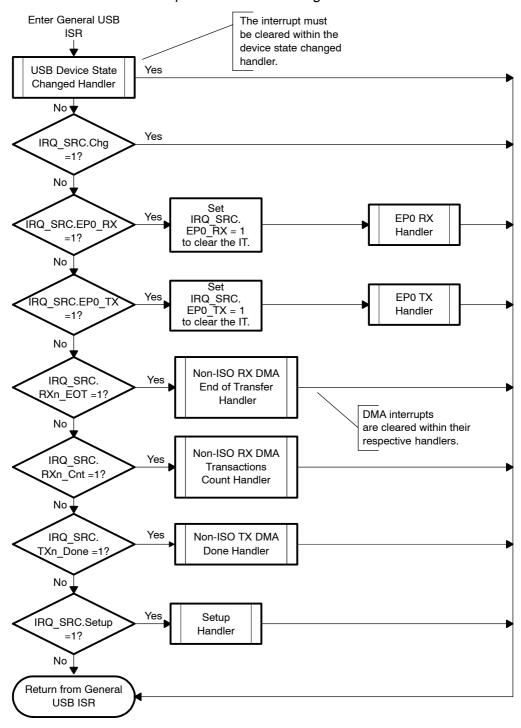

| 16                   | Interru                                                                                           | upt Serv                                                                                                   | vice Routine (ISR) Flowcharts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 226                                                                       |

|                      | 16.1                                                                                              | •                                                                                                          | ant Note on USB Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

|                      | 16.2                                                                                              | _                                                                                                          | the General USB Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

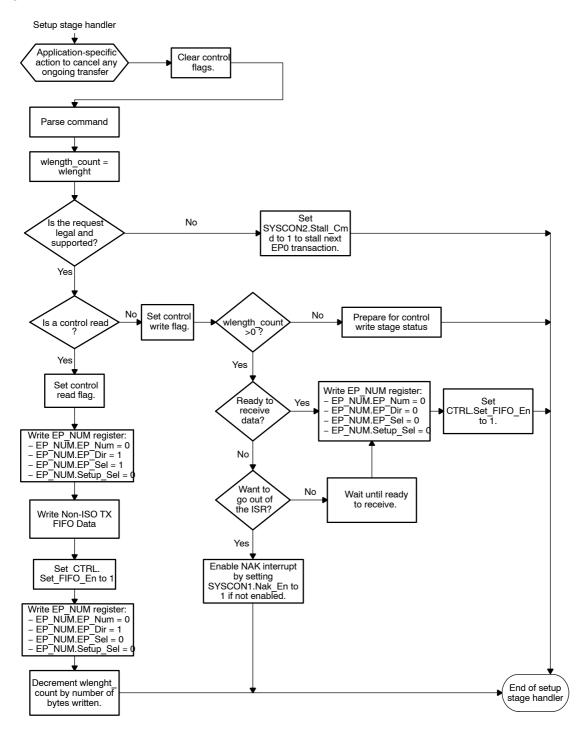

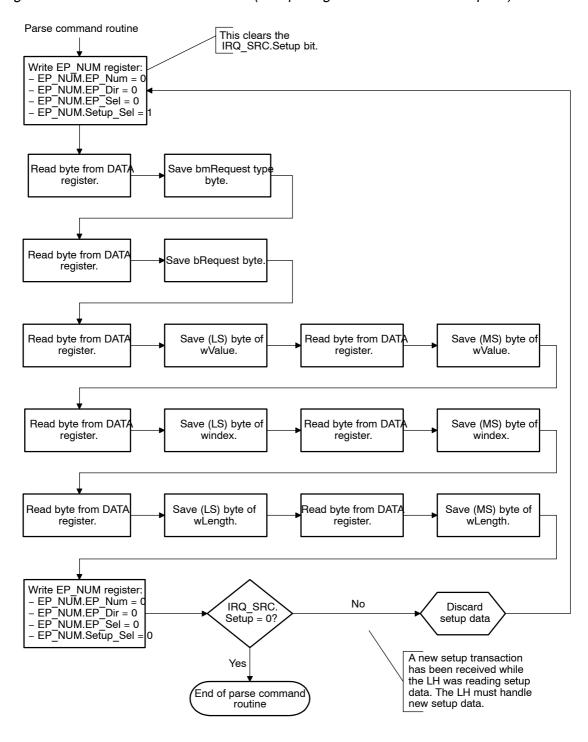

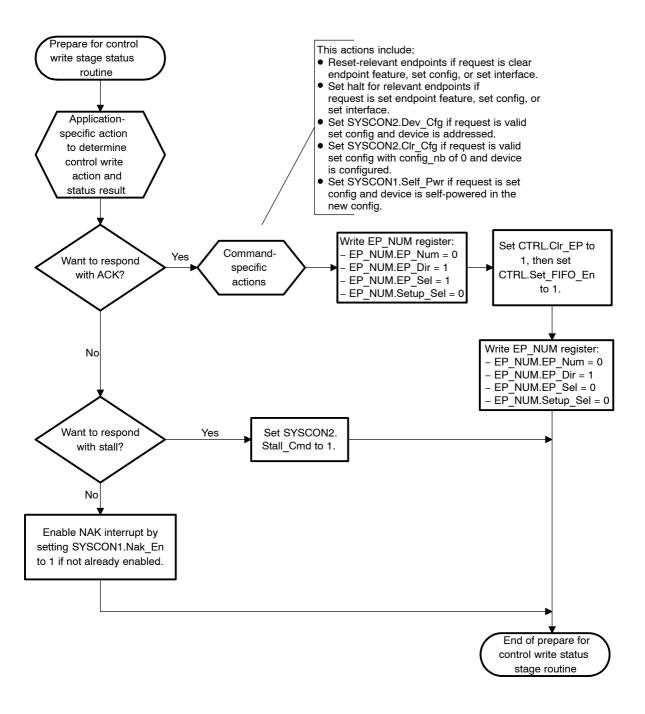

|                      | 16.3                                                                                              | •                                                                                                          | nterrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

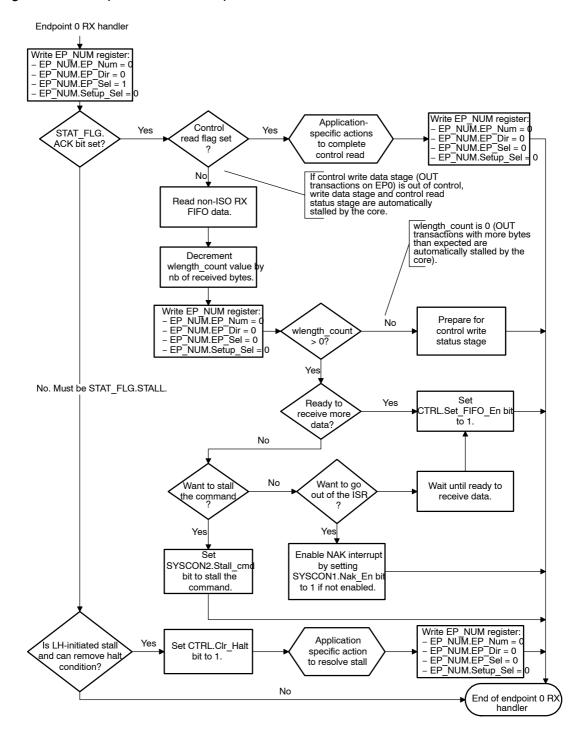

|                      | 16.4                                                                                              |                                                                                                            | nt 0 RX Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|                      | 16.5                                                                                              |                                                                                                            | nt 0 TX Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

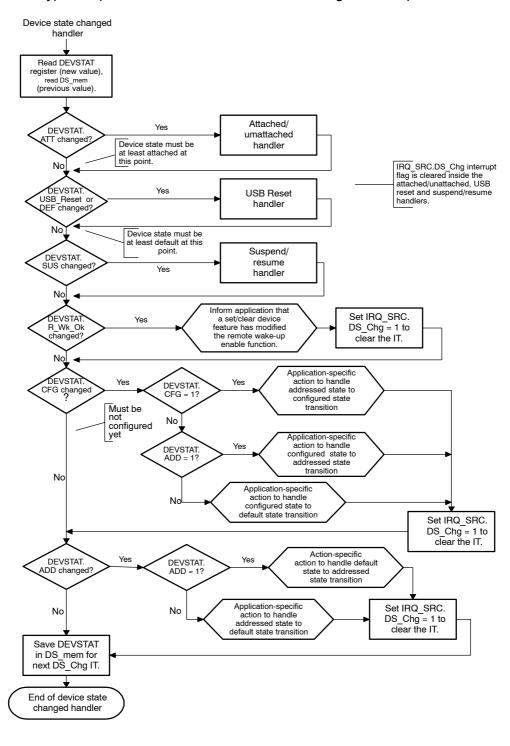

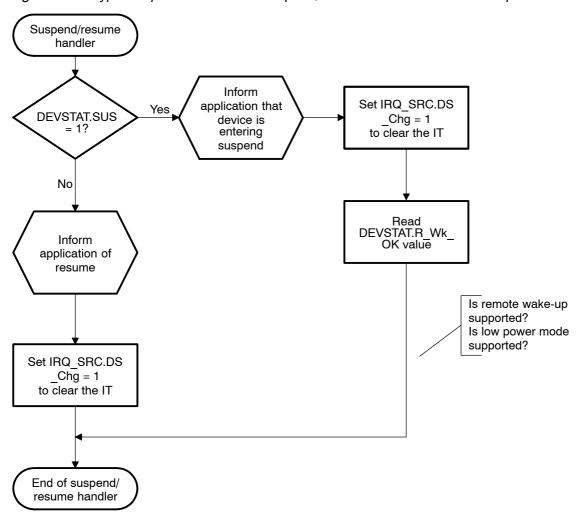

|                      | 16.6                                                                                              |                                                                                                            | States Changed Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

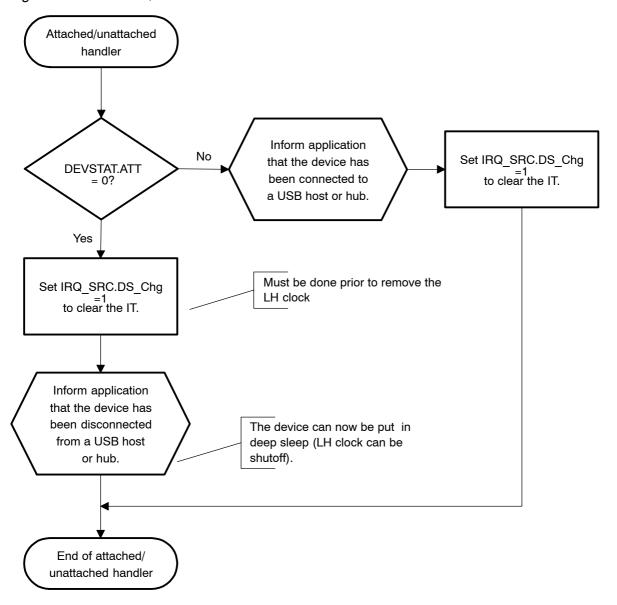

|                      | 16.7                                                                                              |                                                                                                            | States Attached/Unattached Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

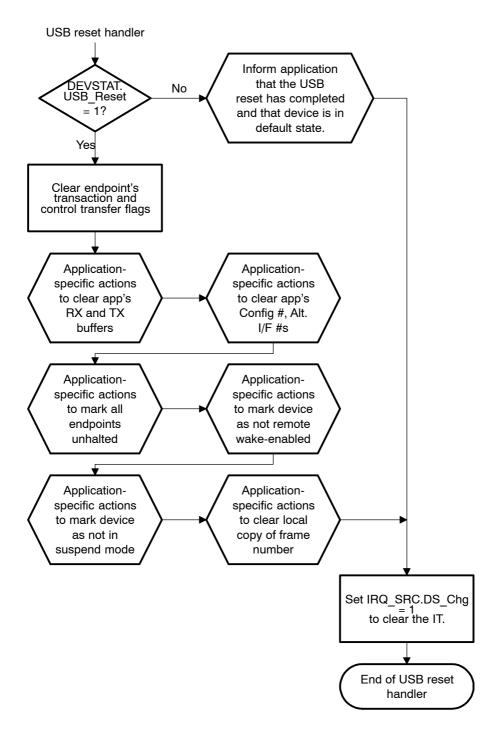

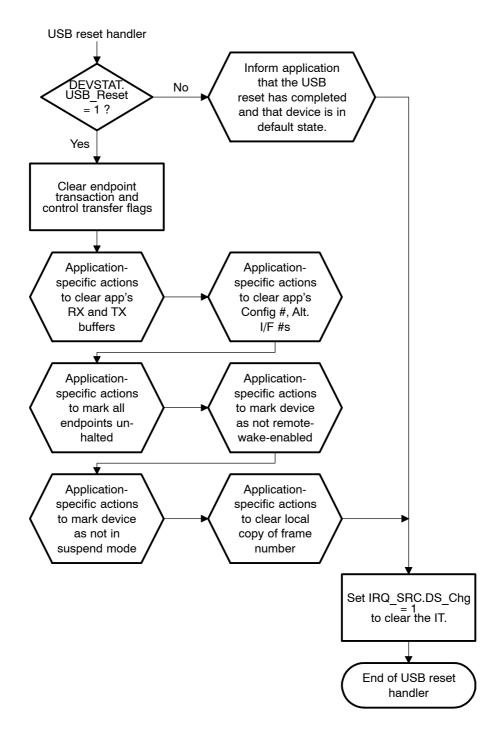

|                      | 16.8<br>16.9                                                                                      |                                                                                                            | eset Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

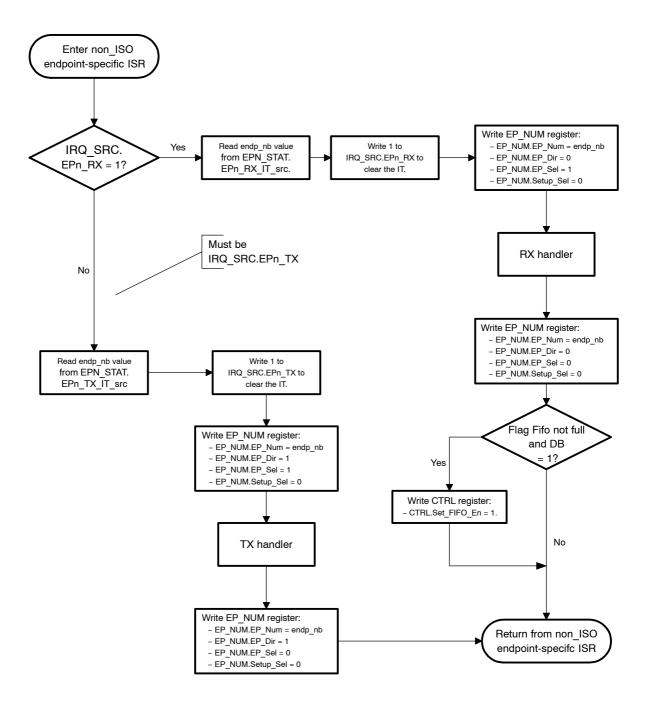

|                      |                                                                                                   |                                                                                                            | ן the Non-Isochronous Endpoint-Specific Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

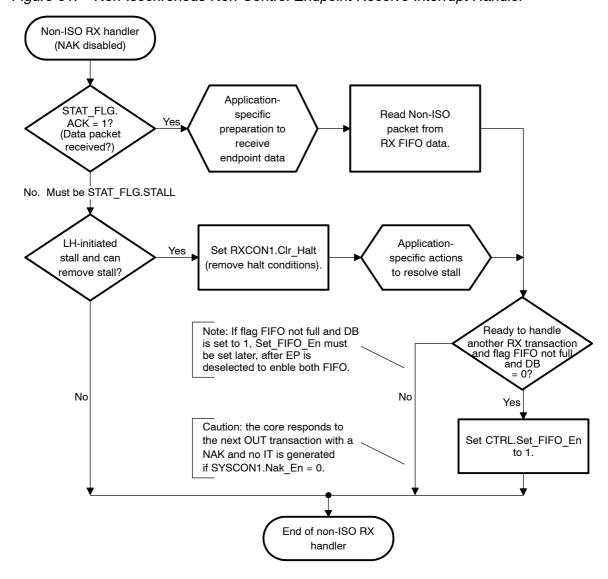

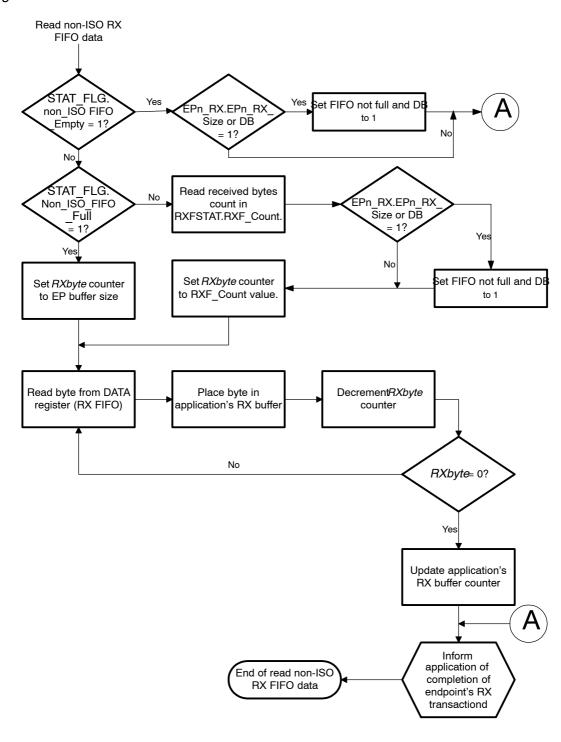

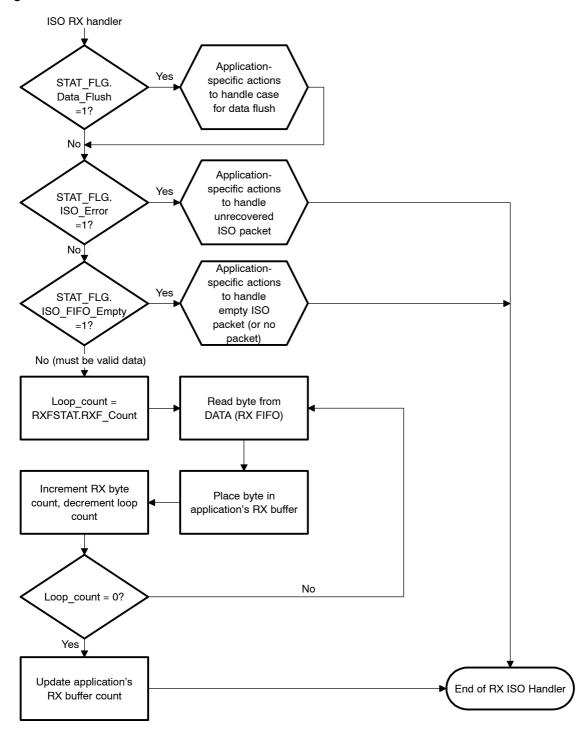

|                      |                                                                                                   |                                                                                                            | ochronous, Non-Control OUT Endpoint Receive Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

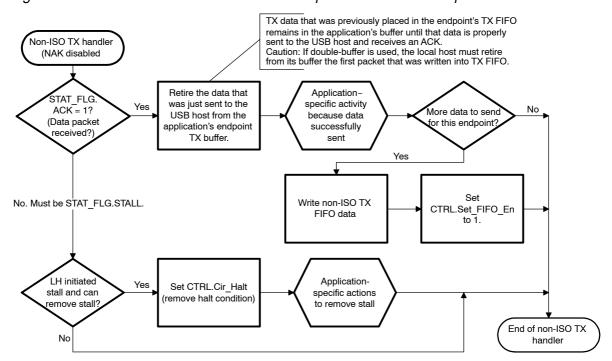

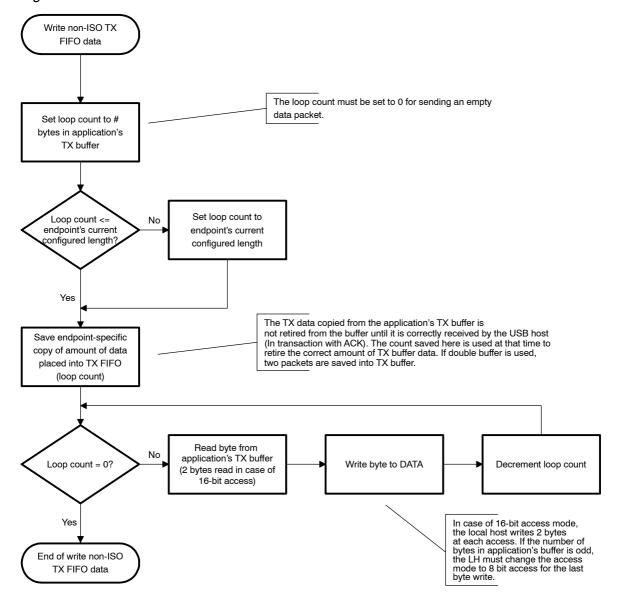

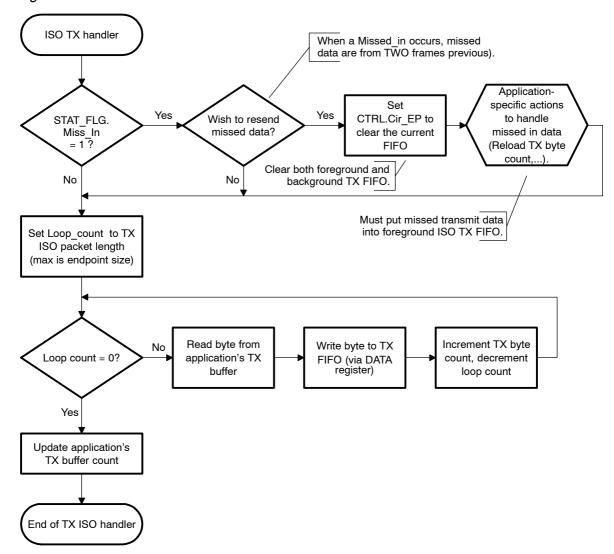

|                      |                                                                                                   |                                                                                                            | ochronous, Non-Control IN Endpoint Transmit Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

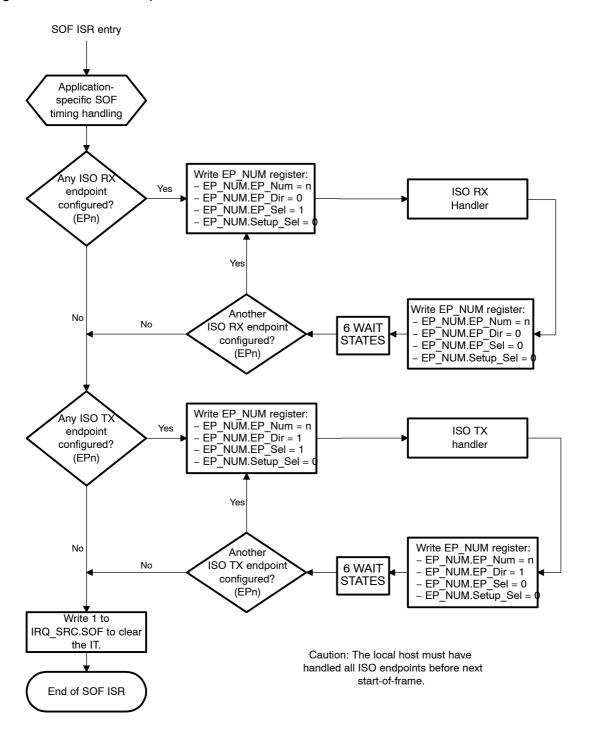

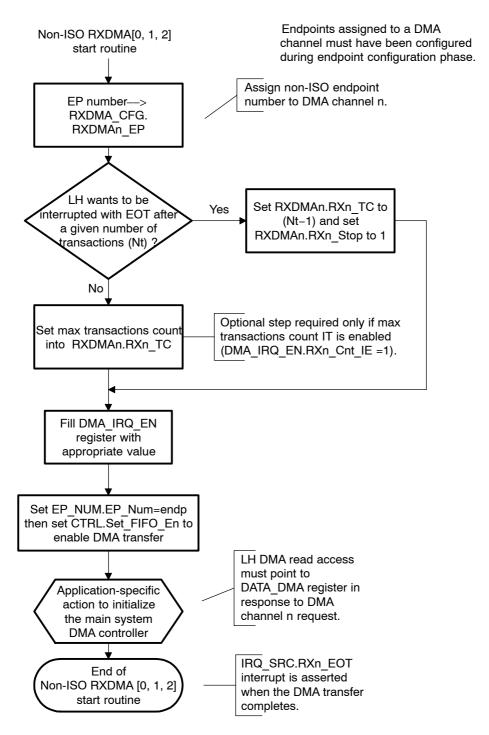

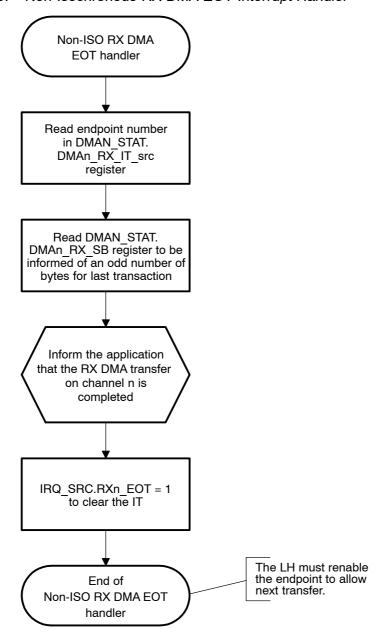

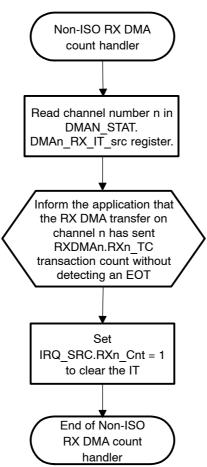

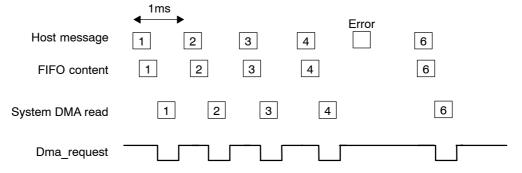

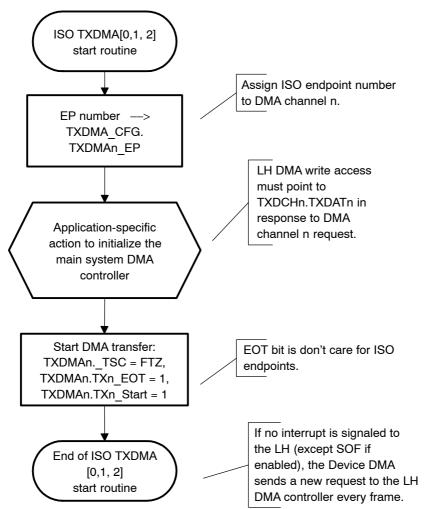

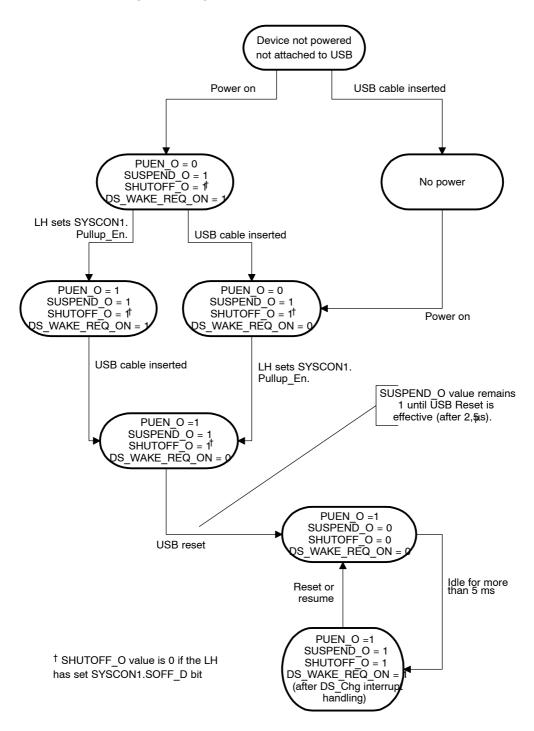

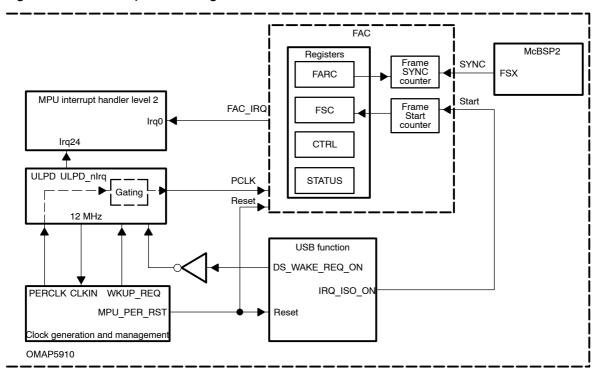

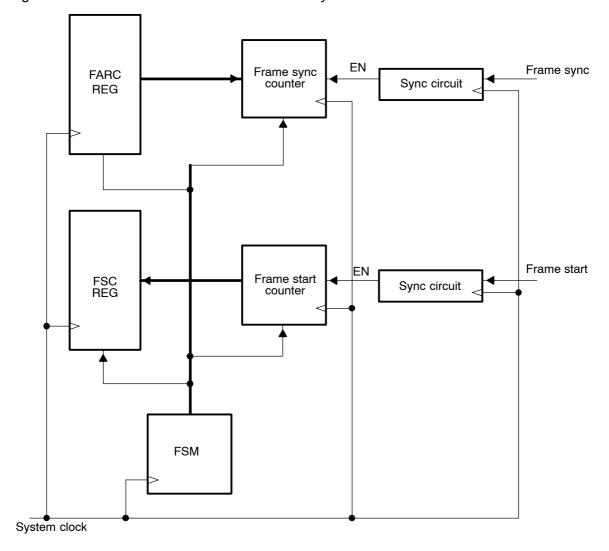

|                      |                                                                                                   |                                                                                                            | terrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |