**DRV3946-Q1** SLVSHN6A - DECEMBER 2023 - REVISED JUNE 2024

## DRV3946-Q1 Dual Channel Automotive Solenoid Driver with Current Regulation, **Clamping and Diagnostics**

#### 1 Features

- AEC-Q100 qualified for automotive applications

- Temperature grade 1: –40°C to +125°C, T<sub>A</sub>

- **Functional Safety-Compliant**

- Developed for functional safety applications

- Documentation to aid ISO26262 system design is available

- Systematic integrity up to ASIL D

- Hardware integrity up to ASIL C

- Highly integrated solenoid driver targeted at automotive EV contactor relay and solenoid control applications

- Integration of power supplies, current regulation, diagnostics, and safety functions

- High-efficiency solenoid driving with configurable peak and hold current settings

- Built-in-self-test and diagnostic functions for power supplies, interfaces, drivers, and monitors

- Architecture for reliable operation with redundant power supplies, low-side and highside drivers, and secondary monitoring logic

- Up to 28V (40V abs. max) operating voltage

- Integrated modified half-bridge

- For charging, recirculation and clamping

- Typical  $R_{DS(ON)}$ : 37m $\Omega$  (low-side), 57m $\Omega$  (high-

- Quick Turn Off with integrated clamp circuits

- High-side clamp with redundant low-side clamp

- Low-side load control by single wire connection

- Allows external high-side switch for redundant

- ± 5% accurate Low and High-side current sense

- Analog load current feedback pin (IPROPI)

- Internal control mode:

- Closed loop PWM current regulation

- Configurable peak time, peak and hold currents

- External control mode:

- Vary duty cycle at fixed PWM frequency

- Vary PWM frequency at fixed duty cycle

- 4-wire, addressable, 24-bit SPI with CRC

- Allows multiple devices to operate on same SPI

- All devices on shared SPI bus can receive broadcast commands

- Comprehensive protection and diagnostics:

- Device built-in-self-test

- Load monitoring for open/short detection

- Sensing loss of control during driver ON and

- Forced relay open for undercurrent or undervoltage

- Redundant pin shut-off

- Fault notification on nFAULT pin

#### 2 Applications

- **EV Contactor relays**

- Peak and hold solenoids

- On and off relays

- Proportional solenoids

- Battery Disconnect Units (BDUs)

- Battery Junction Boxes (BJBs)

- Power Distribution Boxes (PDBs) **Active Suspension Systems**

- Vehicle Control Units (VCUs)

#### **Package Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE     | PACKAGE SIZE<br>(NOM) <sup>(2)</sup> |  |  |

|----------------------------|-------------|--------------------------------------|--|--|

| DRV3946-Q1                 | HTSSOP (28) | 9.7mm X 4.4mm                        |  |  |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length x width) is a nominal value and includes pins, where applicable.

#### **Device Information**

| KEY FEATURES                                              |

|-----------------------------------------------------------|

| Can drive two solenoids with high-efficiency              |

| Low on-resistance power stage                             |

| Integrated clamp circuits for quick turn off              |

| Closed-loop PWM current regulation                        |

| Configurable peak and hold currents and timing parameters |

| Up to 20kHz PWM frequency options                         |

| Comprehensive on and off-state diagnostics                |

| Addressable 24-bit SPI                                    |

#### 3 Description

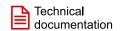

The DRV3946-Q1 is a highly integrated solution to drive two solenoids for automotive applications such as contactor relays in EV battery management systems. It includes power supplies, current sensing and current regulation, configurable peak and hold currents and associated timings, and diagnostics and protection functions. It also incorporates several unique functions that enhance performance compared to traditional discrete solenoid drivers. These functions include integrated redundant clamp circuits to quickly discharge the load current, an addressable SPI, and modified half-bridge driver stage with low on-resistance switches.

The device controls solenoid loads through a single wire low-side connection and can pair with an external high-side switch (that can be shared) for redundant shut-off function. Integrated switches perform charging, recirculation and clamping. The device supports internal and external current control modes. The PWM frequency is configurable, with added low frequency dithering using automatic pseudo random frequencies generation and wave shaping. Internal PWM current control loop leads to reduced software development, since MCU current control loop is not needed. The DRV3946-Q1 supports flexible current control parameters to support wide range of solenoid types. Configurable peak and hold current and corresponding timing parameters allow system level power saving.

The DRV3946-Q1 is targeted to be functional safety-compliant, with ASIL-C rated functional safety goal for relay control and avoiding unintended operation. The device supports comprehensive protection and diagnostic features, such as continuous monitoring of load for open and short detection, on and off-state diagnostics, voltage monitors, short protection and high voltage rated IOs.

An addressable SPI allows multiple devices to be controlled on a shared SPI bus. In addition to reducing required MCU resources, the addressable SPI incorporates a broadcast command structure that can enable all devices on the shared addressed bus to take certain actions simultaneously. The SPI incorporates multiple robustness functions including a CRC, address readback capability, and various bus fault detection mechanisms.

Simplified Schematic

#### **Table of Contents**

| 1 Features1         | 5 Mechanical, Packaging, and Orderable Information |

|---------------------|----------------------------------------------------|

| 2 Applications1     | 5.1 Package Option Addendum4                       |

| 3 Description2      | 5.2 Tape and Reel Information                      |

| 4 Revision History3 | ·                                                  |

#### **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision * (December 2023) to Revision A (June 2024) | Page |

|----|------------------------------------------------------------------|------|

| •  | Updated Functional Safety text                                   | 1    |

| •  | Updated text on broadcast command                                | 1    |

#### 5 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### 5.1 Package Option Addendum

#### **Packaging Information**

| Orderable<br>Device | 40     | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> |        | MSL Peak<br>Temp <sup>(3)</sup> | Op Temp (°C) | Device<br>Marking <sup>(4) (5)</sup> |

|---------------------|--------|--------------|--------------------|------|-------------|-------------------------|--------|---------------------------------|--------------|--------------------------------------|

| DRV3946QPW<br>PRQ1  | ACTIVE | HTSSOP       | PWP                | 28   | 2500        | RoHS & Green            | NIPDAU | Level-3-260C-1<br>68 HR         | -40 to 125   | 3946                                 |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PRE PROD Unannounced device, not in production, not available for mass market, nor on the web, samples not available.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: DRV3946-Q1

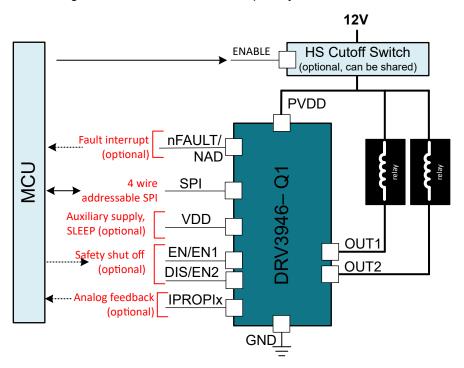

#### 5.2 Tape and Reel Information

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

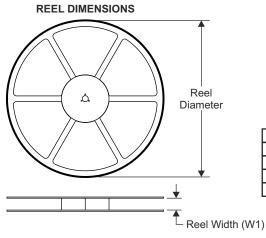

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV3946QPWPRQ1 | HTSSOP          | PWP                | 28   | 2500 | 330.0                    | 16.4                     | 6.75       | 10.1       | 1.8        | 12.0       | 16.0      | Q1               |

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV3946QPWPRQ1 | HTSSOP       | PWP             | 28   | 2500 | 356.0       | 356.0      | 35.0        |

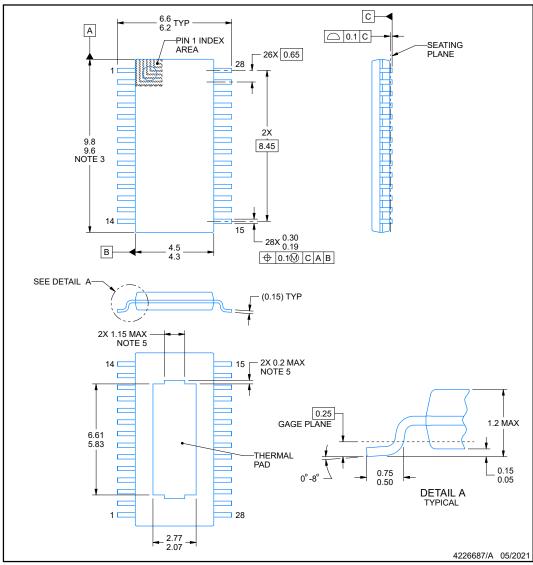

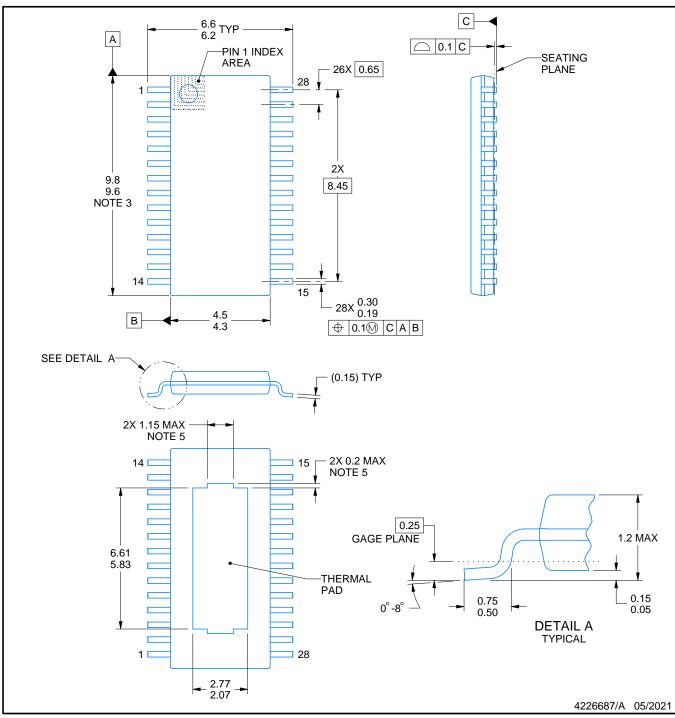

**PWP0028T**

#### **PACKAGE OUTLINE**

### PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ or may not be present.

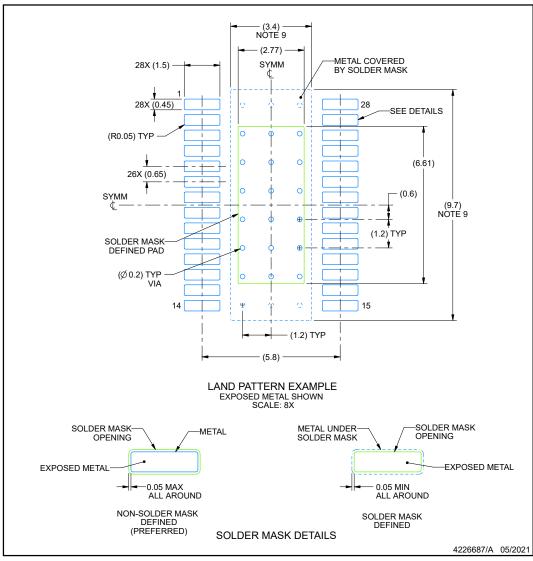

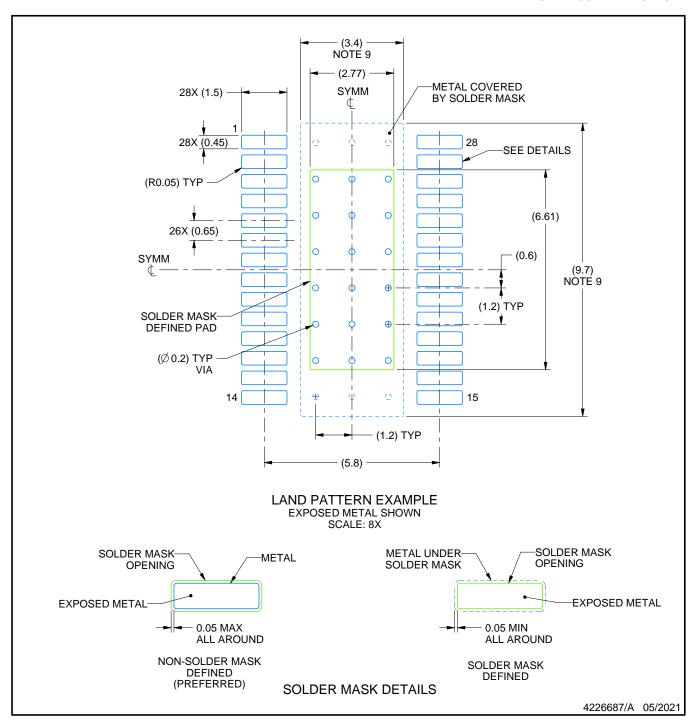

#### **EXAMPLE BOARD LAYOUT**

#### **PWP0028T**

#### PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

- 6. Publication IPC-7351 may have alternate designs.

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- Size of metal pad may vary due to creepage requirement.

Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

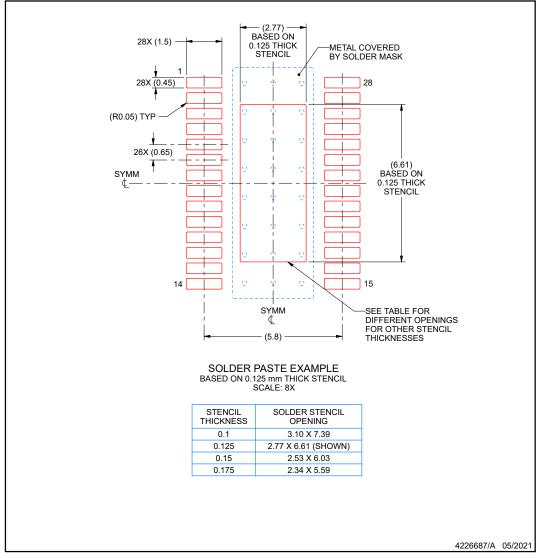

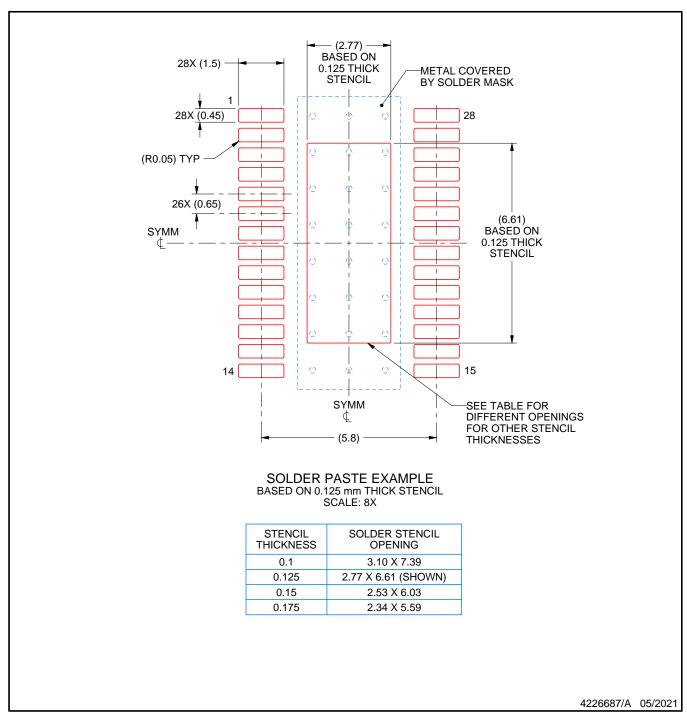

#### **EXAMPLE STENCIL DESIGN**

#### **PWP0028T**

#### PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- design recommendations.

12. Board assembly site may have different recommendations for stencil design.

www.ti.com 8-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| DRV3946QPWPRQ1        | Active | Production    | HTSSOP (PWP)   28 | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | 3946             |

| DRV3946QPWPRQ1.A      | Active | Production    | HTSSOP (PWP)   28 | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | 3946             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

SMALL OUTLINE PACKAGE

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

SMALL OUTLINE PACKAGE

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025