## UC1846-SP Class-V, Radiation Hardened PWM Controller

### 1 Features

- QML-V Qualified, SMD 5962-86806

- 5962P8680603VxA:

- Radiation Hardness Assurance (RHA) up to 30-krad(Si) Total Ionizing Dose (TID)

- Passes Functional and Specified Post-Radiation Parametric Limits at 45 krad at LDR (10 mrad(Si)/s) per 1.5x Over Test as Defined in MIL-STD-883 Test Method 1019.9 Paragraph 3.13.3.b

- Exhibits Low-Dose Rate Sensitivity but Remains Within the Pre-Radiation Electrical Limits at 30-krad Total Dose Level, as Allowed by MIL-STD-883, TM1019

- Automatic Feed-Forward Compensation

- Programmable Pulse-by-Pulse Current Limiting

- Automatic Symmetry Correction in Push-Pull Configuration

- Enhanced Load Response Characteristics

- Parallel-Operation Capability for Modular Power Systems

- Differential Current-Sense Amplifier With Wide Common-Mode Range

- Double-Pulse Suppression

- 500-mA (Peak) Totem-Pole Outputs

- $\pm 1\%$  Bandgap Reference

- Undervoltage Lockout (UVLO)

- Soft-Start Capability

- Shutdown Terminal

- 500-kHz Operation

### 2 Applications

- DC-DC Converters

- Satellite Buses and Payloads

- Space Launch Vehicles

- Undersea Cabling

- Available in Military Temperature Range ( $-55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ )

- Supports Various Topologies:

- Flyback, Forward, Buck, Boost

- Push-Pull, Half-Bridge, Full Bridge With External Interface Circuit

### 3 Description

The UC1846-SP control devices provide all of the necessary features to implement fixed frequency, current mode control schemes while maintaining a minimum external parts count. The superior performance of this technique can be measured in improved line regulation, enhanced load response characteristics, and a simpler, easier-to-design control loop. Topological advantages include inherent pulse-by-pulse current limiting capability, automatic symmetry correction for push-pull converters, and the ability to parallel power modules while maintaining equal current sharing.

Protection circuitry includes built-in UVLO and programmable current limit in addition to soft-start capability. A shutdown function is also available which can initiate either a complete shutdown with automatic restart or latch the supply off.

Other features include fully latched operation, double-pulse suppression, deadline adjust capability, a  $\pm 1\%$  trimmed bandgap reference, and low outputs in the OFF state.

### Device Information<sup>(1)</sup>

| PART NUMBER   | PACKAGE            | BODY SIZE (NOM)           |

|---------------|--------------------|---------------------------|

| UC1846-SP     | CDIP (16)          | 6.92 mm $\times$ 19.56 mm |

|               | CFP (16)           | 6.73 mm $\times$ 10.30 mm |

|               | LCCC (20)          | 8.89 mm $\times$ 8.89 mm  |

|               | KGD <sup>(2)</sup> | N/A                       |

| UC1846-SP RHA | CDIP (16)          | 6.92 mm $\times$ 19.56 mm |

|               | CFP (16)           | 6.73 mm $\times$ 10.30 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

(2) KGD = known good die

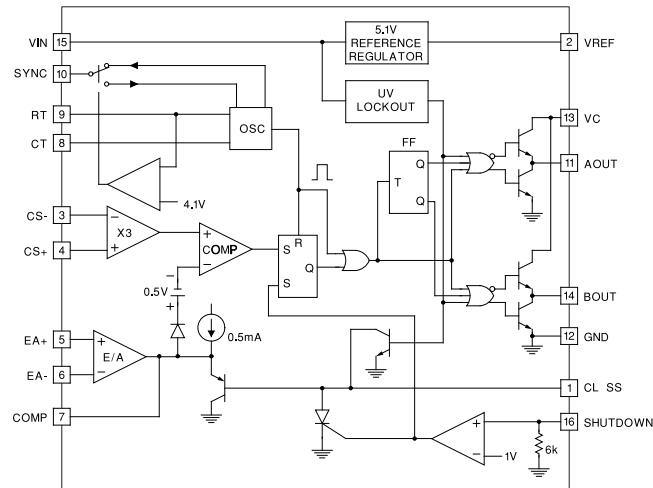

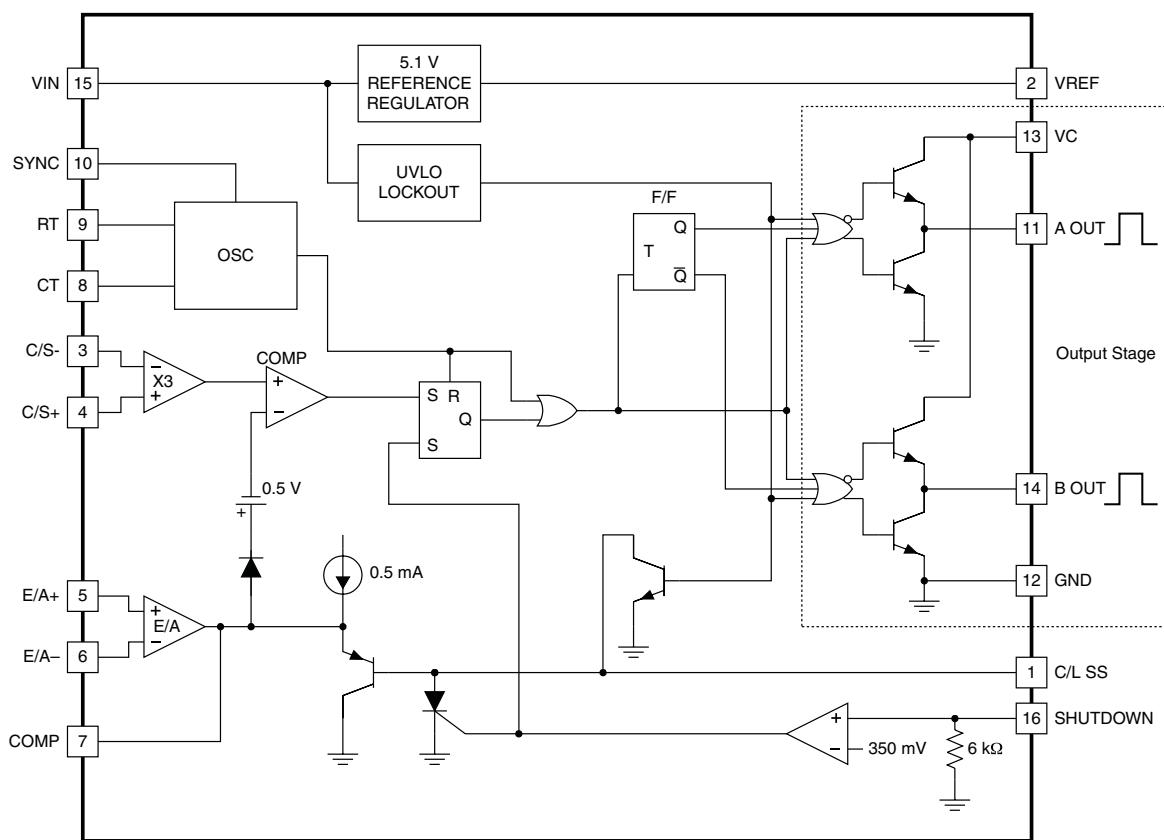

### Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|          |                                              |          |           |                                                                         |           |

|----------|----------------------------------------------|----------|-----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Features</b> .....                        | <b>1</b> | 7.4       | Device Functional Modes .....                                           | <b>13</b> |

| <b>2</b> | <b>Applications</b> .....                    | <b>1</b> | <b>8</b>  | <b>Application and Implementation</b> .....                             | <b>15</b> |

| <b>3</b> | <b>Description</b> .....                     | <b>1</b> | 8.1       | Application Information.....                                            | <b>15</b> |

| <b>4</b> | <b>Revision History</b> .....                | <b>2</b> | 8.2       | Typical Applications .....                                              | <b>15</b> |

| <b>5</b> | <b>Pin Configuration and Functions</b> ..... | <b>3</b> | <b>9</b>  | <b>Power Supply Recommendations</b> .....                               | <b>22</b> |

| <b>6</b> | <b>Specifications</b> .....                  | <b>6</b> | <b>10</b> | <b>Layout</b> .....                                                     | <b>22</b> |

|          | 6.1 Absolute Maximum Ratings .....           | 6        | 10.1      | Layout Guidelines .....                                                 | 22        |

|          | 6.2 ESD Ratings.....                         | 6        | 10.2      | Layout Example .....                                                    | 22        |

|          | 6.3 Recommended Operating Conditions .....   | 6        | <b>11</b> | <b>Device and Documentation Support</b> .....                           | <b>23</b> |

|          | 6.4 Thermal Information .....                | 6        | 11.1      | Receiving Notification of Documentation Updates                         | 23        |

|          | 6.5 Electrical Characteristics.....          | 7        | 11.2      | Community Resources.....                                                | 23        |

|          | 6.6 Typical Characteristics .....            | 8        | 11.3      | Trademarks .....                                                        | 23        |

| <b>7</b> | <b>Detailed Description</b> .....            | <b>9</b> | 11.4      | Electrostatic Discharge Caution .....                                   | 23        |

|          | 7.1 Overview .....                           | 9        | 11.5      | Glossary .....                                                          | 23        |

|          | 7.2 Functional Block Diagram .....           | 9        | <b>12</b> | <b>Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>23</b> |

|          | 7.3 Feature Description.....                 | 9        |           |                                                                         |           |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <b>Changes from Revision C (October 2015) to Revision D</b>                                                                                                                  |    | <b>Page</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|

| • Changed title of data sheet from <i>UC1846-SP Rad-Tolerant Class-V, Current-Mode PWM Controller</i> : to <i>UC1846-SP Class-V, Radiation Hardened PWM Controller</i> ..... | 1  | 1           |

| • Added new RHA features to <i>Features</i> section .....                                                                                                                    | 1  | 1           |

| • Added RHA package options to <i>Device Information</i> table .....                                                                                                         | 1  | 1           |

| • Changed shutdown threshold from 1.0 V : to 350 mV throughout document .....                                                                                                | 1  | 1           |

| • Added <i>Receiving Notification of Documentation Updates</i> to <i>Device and Documentation Support</i> section .....                                                      | 23 | 23          |

| <b>Changes from Revision B (October 2011) to Revision C</b>                                                                                                                                                                                                                                                                                          |   | <b>Page</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|

| • Added <i>ESD Ratings</i> table, <i>Feature Description</i> section, <i>Device Functional Modes</i> , <i>Application and Implementation</i> section, <i>Power Supply Recommendations</i> section, <i>Layout</i> section, <i>Device and Documentation Support</i> section, and <i>Mechanical, Packaging, and Orderable Information</i> section ..... | 1 | 1           |

| • Added KGD package to <i>Device Information</i> .....                                                                                                                                                                                                                                                                                               | 1 | 1           |

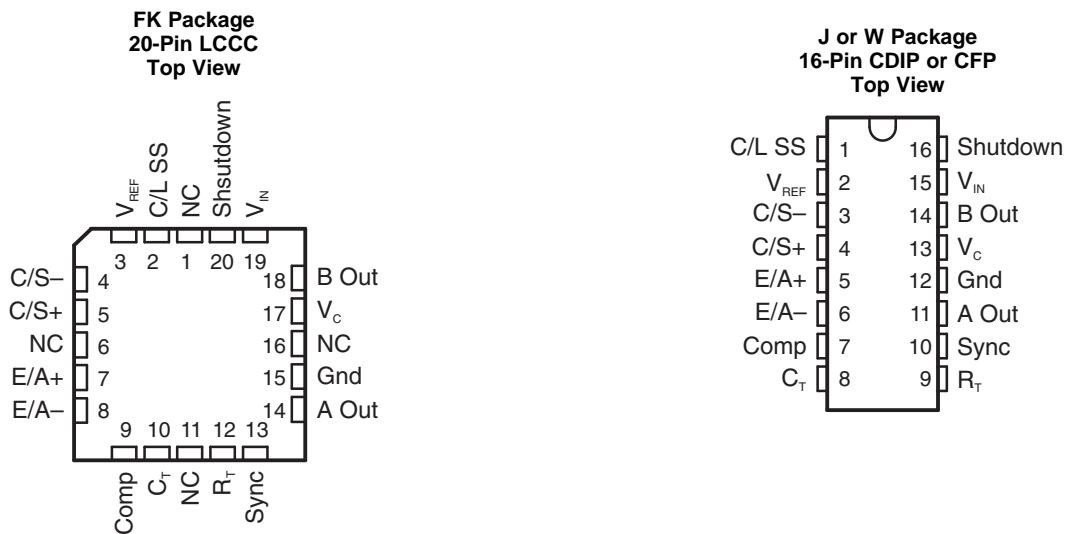

## 5 Pin Configuration and Functions

### Pin Functions

| PIN      |             |          | I/O | DESCRIPTION                                                                                                                                                                                                                   |

|----------|-------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | CDIP or CFP | LCCC     |     |                                                                                                                                                                                                                               |

| CL SS    | 1           | 2        | I   | Current limit/soft-start.                                                                                                                                                                                                     |

| VREF     | 2           | 3        | O   | 5.1-V internally generated reference.                                                                                                                                                                                         |

| CS-      | 3           | 4        | I   | Inverting input of current sense operational amplifier.                                                                                                                                                                       |

| CS+      | 4           | 5        | I   | Non-Inverting input of current sense operational amplifier.                                                                                                                                                                   |

| EA+      | 5           | 7        | I   | Non-Inverting input of error amplifier.                                                                                                                                                                                       |

| EA-      | 6           | 8        | I   | Inverting input of error amplifier.                                                                                                                                                                                           |

| COMP     | 7           | 9        | O   | Output of error amplifier.                                                                                                                                                                                                    |

| CT       | 8           | 10       | I   | Timing capacitance. Capacitor connected from CT to ground is charged via current established by RT pin via current mirror. Output pulse dead time is determined by the size of the capacitor during capacitor discharge time. |

| RT       | 9           | 12       | I   | Determines oscillator frequency. VREF sources thru RT to create a current which is mirrored to CT pin.                                                                                                                        |

| SYNC     | 10          | 13       | I/O | Sync pin is an output under normal operation when RT is above 4.1-V sync output high. Sync pin is an input when RT pin is high and CT pin tied low.                                                                           |

| AOUT     | 11          | 14       | O   | Output driver (source/sink).                                                                                                                                                                                                  |

| GND      | 12          | 15       | —   | Ground connection.                                                                                                                                                                                                            |

| VC       | 13          | 17       | I   | Gate drive collector supply voltage. Decouple with capacitor.                                                                                                                                                                 |

| BOUT     | 14          | 18       | O   | Output driver (source/sink).                                                                                                                                                                                                  |

| VIN      | 15          | 19       | I   | Input voltage decouple with capacitor.                                                                                                                                                                                        |

| SHUTDOWN | 16          | 20       | I   | Shutdown threshold 350 mV. Voltage above threshold latches off oscillator.                                                                                                                                                    |

| NC       | —           | 1, 6, 11 | —   | No connect.                                                                                                                                                                                                                   |

**Bare Die Information**

| DIE THICKNESS | BACKSIDE FINISH        | BACKSIDE POTENTIAL | BOND PAD METALLIZATION COMPOSITION | BOND PAD THICKNESS |

|---------------|------------------------|--------------------|------------------------------------|--------------------|

| 15 mils       | Silicon with backgrind | Floating           | AlCu2%                             | 2000 nm            |

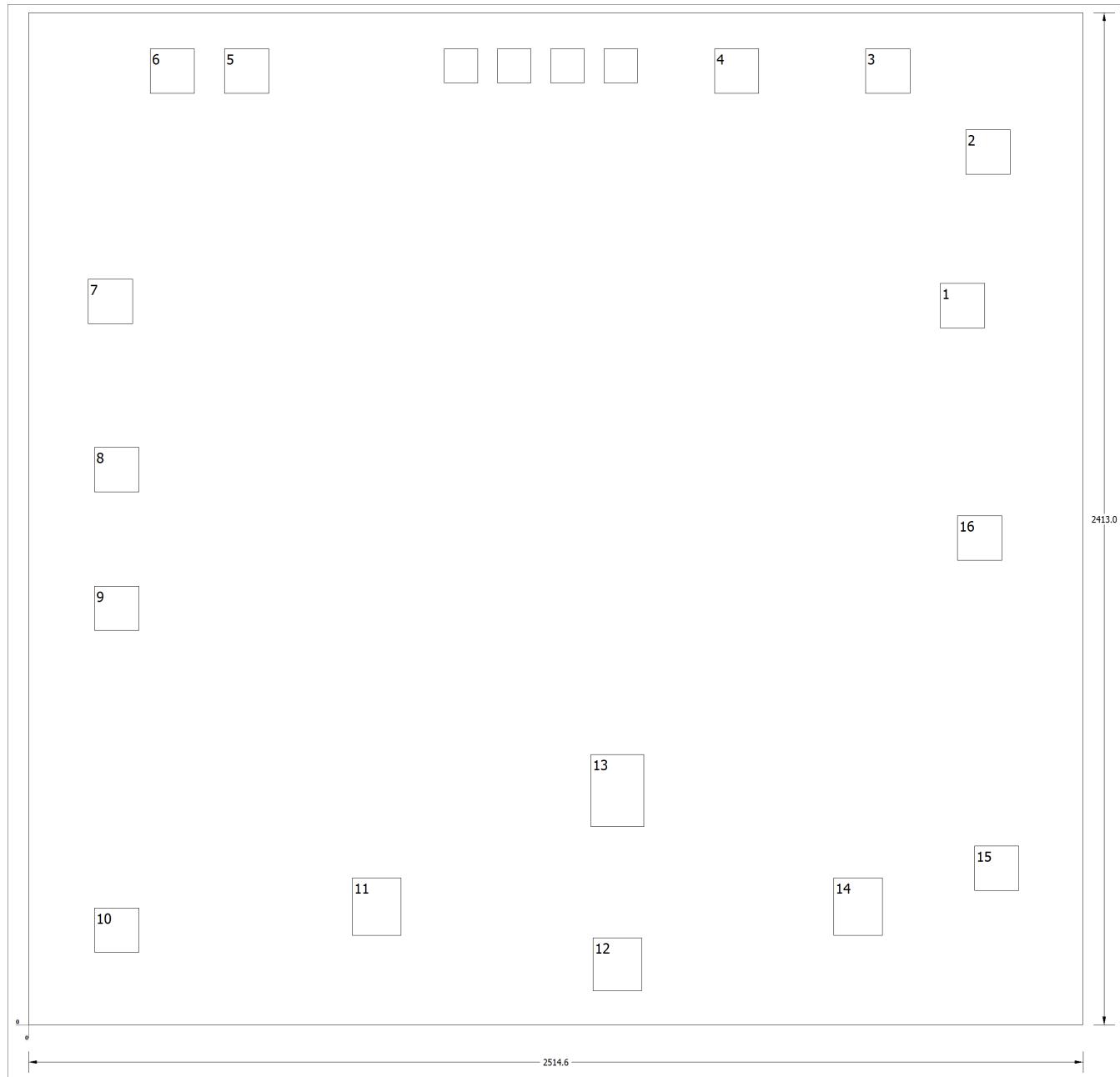

**Bond Pad Coordinates in Microns**

| DESCRIPTION              | PAD NUMBER | X MIN   | Y MIN   | X MAX   | Y MAX   |

|--------------------------|------------|---------|---------|---------|---------|

| Current limit/soft-start | 1          | 2174.24 | 1661.16 | 2280.92 | 1767.84 |

| VREF                     | 2          | 2235.2  | 2026.92 | 2341.88 | 2133.6  |

| (-) Current sense        | 3          | 1996.44 | 2219.96 | 2103.12 | 2326.64 |

| (+) Current sense        | 4          | 1635.76 | 2219.96 | 1742.44 | 2326.64 |

| (+) Error amplifier      | 5          | 467.36  | 2219.96 | 574.04  | 2326.64 |

| (-) Error amplifier      | 6          | 289.56  | 2219.96 | 396.24  | 2326.64 |

| Compensation             | 7          | 142.24  | 1671.32 | 248.92  | 1778    |

| CT                       | 8          | 157.48  | 1270    | 264.16  | 1376.68 |

| RT                       | 9          | 157.48  | 939.8   | 264.16  | 1046.48 |

| SYNC                     | 10         | 157.48  | 172.72  | 264.16  | 279.4   |

| OUTPUT A                 | 11         | 772.16  | 213.36  | 889     | 350.52  |

| GROUND                   | 12         | 1346.2  | 81.28   | 1463.04 | 208.28  |

| VC                       | 13         | 1341.12 | 472.44  | 1468.12 | 645.16  |

| OUTPUT B                 | 14         | 1920.24 | 213.36  | 2037.08 | 350.52  |

| VIN                      | 15         | 2255.52 | 320.04  | 2362.2  | 426.72  |

| SHUTDOWN                 | 16         | 2214.88 | 1107.44 | 2321.56 | 1214.12 |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|              |                                                         | MIN  | MAX      | UNIT |

|--------------|---------------------------------------------------------|------|----------|------|

| $V_{CC}$     | Supply voltage                                          |      | 40       | V    |

|              | Collector supply voltage                                |      | 40       | V    |

| $V_I$        | Analog input voltage (C/S-, C/S+, E/A+, E/A-, Shutdown) | -0.3 | $V_{IN}$ | V    |

| $I_O$        | Output current, source or sink                          |      | 500      | mA   |

|              | Reference output current                                |      | -30      | mA   |

|              | Sync output current                                     |      | -5       | mA   |

|              | Error amplifier output current                          |      | -5       | mA   |

|              | Soft-start sink current                                 |      | 50       | mA   |

|              | Oscillator charging current                             |      | 5        | mA   |

| $T_{J(max)}$ | Maximum junction temperature                            |      | 150      | °C   |

| $T_{lead}$   | Lead temperature (soldering, 10 s)                      |      | 300      | °C   |

| $T_{stg}$    | Storage temperature                                     | -65  | 150      | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to ground. Currents are positive into, negative out of the specified terminal.

### 6.2 ESD Ratings

|             |                         | VALUE                                                             | UNIT    |

|-------------|-------------------------|-------------------------------------------------------------------|---------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|       | MIN                            | NOM | MAX | UNIT |

|-------|--------------------------------|-----|-----|------|

| $T_J$ | Operating junction temperature | -55 | 125 | °C   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | UC1846-SP                                    |         |           | UNIT |      |

|-------------------------------|----------------------------------------------|---------|-----------|------|------|

|                               | J (CDIP)                                     | W (CFP) | FK (LCCC) |      |      |

|                               | 16 PINS                                      | 16 PINS | 20 PINS   |      |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 104.2   | 105.2     | N/A  | °C/W |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance    | N/A     | N/A       | N/A  | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 36.6    | 96.8      | N/A  | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 25.0    | 24.0      | N/A  | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 27.9    | 82.6      | N/A  | °C/W |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance | 8.2     | 8.5       | 9.0  | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, [SPRA953](#).

## 6.5 Electrical Characteristics

$V_{IN} = 15$  V,  $R_T = 10$  k $\Omega$ ,  $C_T = 4.7$  nF,  $T_A = T_J = -55^\circ\text{C}$  to  $125^\circ\text{C}$  (unless otherwise noted)

| PARAMETER                                                   | TEST CONDITIONS                                                                    | MIN  | TYP          | MAX          | UNIT                 |

|-------------------------------------------------------------|------------------------------------------------------------------------------------|------|--------------|--------------|----------------------|

| <b>REFERENCE</b>                                            |                                                                                    |      |              |              |                      |

| Output voltage                                              | $T_J = 25^\circ\text{C}$ , $I_O = 1$ mA                                            | 5.04 | 5.1          | 5.16         | V                    |

| Line regulation                                             | $V_{IN} = 8$ to 40 V                                                               |      | 5            | 20           | mV                   |

| Load regulation                                             | $I_L = 1$ to 10 mA                                                                 |      | 3            | 15           | mV                   |

| Temperature stability                                       | Over operating range                                                               |      | 0.4          |              | mV/ $^\circ\text{C}$ |

| Total output variation                                      | Over line, load, and temperature <sup>(1)</sup>                                    | 5    |              | 5.2          | V                    |

| Output noise voltage                                        | $10\text{ Hz} \leq f \leq 10\text{ kHz}$ , $T_J = 25^\circ\text{C}$ <sup>(1)</sup> |      | 100          |              | $\mu\text{V}$        |

| Long-term stability                                         | $T_J = 125^\circ\text{C}$ , 1000 hr                                                |      | 5            |              | mV                   |

| Short-circuit output current                                | $V_{REF} = 0$ V                                                                    | -10  | -45          |              | mA                   |

| <b>OSCILLATOR</b>                                           |                                                                                    |      |              |              |                      |

| Initial accuracy                                            | $T_J = 25^\circ\text{C}$                                                           | 39   | 43           | 47           | kHz                  |

| Voltage stability                                           | $V_{IN} = 8$ to 40 V                                                               |      | -1%          | 2%           |                      |

| Temperature stability                                       | Over operating range                                                               |      | -1%          |              |                      |

| Sync output high level                                      |                                                                                    | 3.9  | 4.35         |              | V                    |

| Sync output low level                                       |                                                                                    |      | 2.3          | 2.5          | V                    |

| Sync input high level                                       | $C_T = 0$ V                                                                        | 3.9  |              |              | V                    |

| Sync input low level                                        | $C_T = 0$ V                                                                        |      |              | 2.5          | V                    |

| Sync input current                                          | Sync = 3.9 V, $C_T = 0$ V                                                          |      | 1.3          | 1.5          | mA                   |

| <b>ERROR AMPLIFIER</b>                                      |                                                                                    |      |              |              |                      |

| Input offset voltage                                        |                                                                                    | 0.5  | 5            |              | mV                   |

| Input bias current                                          |                                                                                    | -1   | -0.6         |              | $\mu\text{A}$        |

| Input offset current                                        |                                                                                    | 40   | 250          |              | nA                   |

| Common mode range                                           | $V_{IN} = 8$ to 40 V                                                               | 0    | $V_{IN} - 2$ |              | V                    |

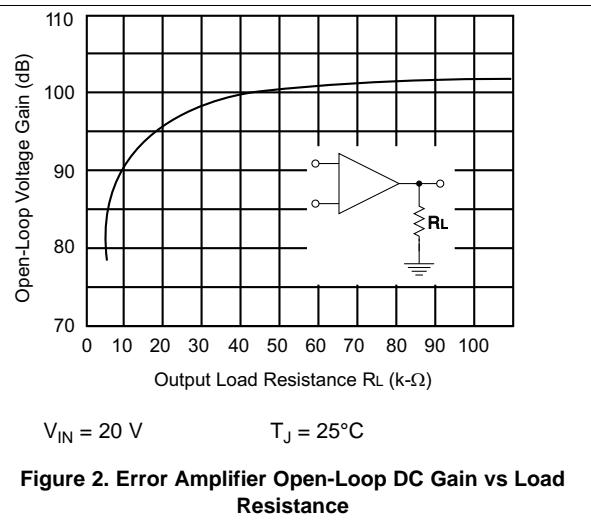

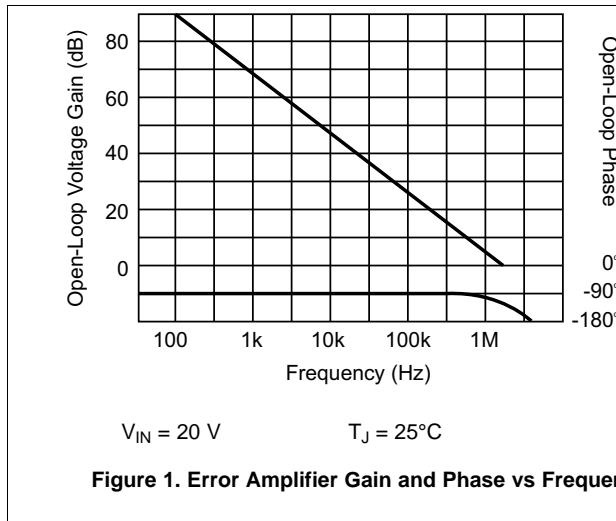

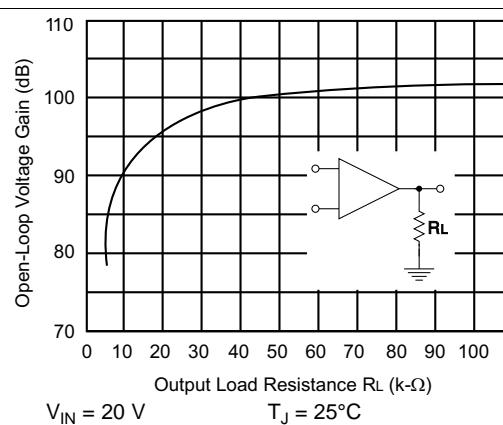

| Open-loop voltage gain                                      | $\Delta V_O = 1.2$ to 3 V, $V_{CM} = 2$ V                                          | 80   | 105          |              | dB                   |

| Unity-gain bandwidth                                        | $T_J = 25^\circ\text{C}$ <sup>(1)</sup>                                            | 0.7  | 1            |              | MHz                  |

| CMRR                                                        | $V_{CM} = 0$ to 38 V, $V_{IN} = 40$ V                                              | 75   | 100          |              | dB                   |

| PSRR                                                        | $V_{IN} = 8$ to 40 V                                                               | 80   | 105          |              | dB                   |

| Output sink current                                         | $V_{ID} = -15$ mV to -5 V, Comp = 1.2 V                                            | 2    | 6            |              | mA                   |

| Output source current                                       | $V_{ID} = 15$ mV to 5 V, Comp = 2.5 V                                              |      | -0.5         | -0.4         | mA                   |

| High-level output voltage                                   | $R_L = (\text{Comp}) 15$ k $\Omega$                                                | 4.3  | 4.6          |              | V                    |

| Low-level output voltage                                    | $R_L = (\text{Comp}) 15$ k $\Omega$                                                |      | 0.7          | 1            | V                    |

| <b>CURRENT SENSE AMPLIFIER</b>                              |                                                                                    |      |              |              |                      |

| Amplifier gain                                              | $V_{C/S-} = 0$ V, C/L SS open <sup>(2)(3)</sup>                                    | 2.5  | 2.75         | 3.1          | V/V                  |

| Maximum differential input signal ( $V_{C/S+} - V_{C/S-}$ ) | C/L SS open <sup>(2)</sup> , $R_L$ (Comp)= 15 k $\Omega$                           | 1.1  | 1.2          |              | V                    |

| Input offset voltage                                        | $V_{C/L SS} = 0.5$ V, Comp open <sup>(2)</sup>                                     |      | 5            | 25           | mV                   |

| CMRR                                                        | $V_{CM} = 1$ to 12 V                                                               | 60   | 83           |              | dB                   |

| PSRR                                                        | $V_{IN} = 8$ to 40 V                                                               | 60   | 84           |              | dB                   |

| Input bias current                                          | $V_{C/L SS} = 0.5$ V, Comp open <sup>(2)</sup>                                     | -10  | -2.5         |              | $\mu\text{A}$        |

| Input offset current                                        | $V_{C/L SS} = 0.5$ V, Comp open <sup>(2)</sup>                                     |      | 0.08         | 1            | $\mu\text{A}$        |

| Input common-mode range                                     |                                                                                    |      |              | $V_{IN} - 3$ | V                    |

| Delay to outputs                                            | $T_J = 25^\circ\text{C}$ <sup>(1)</sup>                                            | 200  | 500          |              | ns                   |

(1) Parameters ensured by design and/or characterization, if not production tested.

(2) Parameter measured at trip point of latch with  $V_{E/A+} = V_{REF}$ ,  $V_{E/A-} = 0$  V.

(3) Amplifier gain defined as:  $G = \Delta V_{\text{Comp}} / \Delta V_{C/S+}$ ;  $V_{C/S+} = 0$  to 1 V.

## Electrical Characteristics (continued)

$V_{IN} = 15$  V,  $R_T = 10$  k $\Omega$ ,  $C_T = 4.7$  nF,  $T_A = T_J = -55^\circ\text{C}$  to  $125^\circ\text{C}$  (unless otherwise noted)

| PARAMETER                                                     | TEST CONDITIONS                                              | MIN  | TYP  | MAX      | UNIT          |

|---------------------------------------------------------------|--------------------------------------------------------------|------|------|----------|---------------|

| <b>CURRENT LIMIT ADJUST</b>                                   |                                                              |      |      |          |               |

| Current limit offset                                          | $V_{C/S-} = 0$ V, $V_{C/S+} = 0$ V, comp open <sup>(2)</sup> | 0.45 | 0.5  | 0.55     | V             |

| Input bias current                                            | $V_{E/A+} = V_{REF}$ , $V_{E/A-} = 0$ V                      | -30  | -10  |          | $\mu\text{A}$ |

| <b>SHUTDOWN TERMINAL</b>                                      |                                                              |      |      |          |               |

| Threshold voltage                                             |                                                              | 250  | 350  | 400      | mV            |

| Input voltage range                                           |                                                              | 0    |      | $V_{IN}$ | V             |

| Minimum latching current ( $I_{C/S\ SS}$ ) <sup>(4)</sup>     |                                                              | 3    | 1.5  |          | mA            |

| Maximum non-latching current ( $I_{C/S\ SS}$ ) <sup>(5)</sup> |                                                              |      | 1.5  | 0.8      | mA            |

| Delay to outputs                                              | $T_J = 25^\circ\text{C}$ <sup>(1)</sup>                      | 300  | 600  |          | ns            |

| <b>OUTPUT</b>                                                 |                                                              |      |      |          |               |

| Collector-emitter voltage                                     |                                                              | 40   |      |          | V             |

| Collector leakage current                                     | $V_C = 40$ V                                                 |      | 200  |          | $\mu\text{A}$ |

| Output low-level voltage                                      | $I_{SINK} = 20$ mA                                           | 0.1  | 0.4  |          | V             |

|                                                               | $I_{SINK} = 100$ mA                                          | 0.4  | 2.1  |          | V             |

| Output high-level voltage                                     | $I_{SOURCE} = 20$ mA                                         | 13   | 13.5 |          | V             |

|                                                               | $I_{SOURCE} = 100$ mA                                        | 12   | 13.5 |          | V             |

| Rise time                                                     | $C_L = 1$ nF, $T_J = 25^\circ\text{C}$ <sup>(1)</sup>        | 50   | 300  |          | ns            |

| Fall time                                                     | $C_L = 1$ nF, $T_J = 25^\circ\text{C}$ <sup>(1)</sup>        | 50   | 300  |          | ns            |

| <b>UVLO</b>                                                   |                                                              |      |      |          |               |

| Start-up threshold                                            |                                                              | 7.7  | 8    |          | V             |

| Threshold hysteresis                                          |                                                              | 0.75 |      |          | V             |

| <b>TOTAL STANDBY CURRENT</b>                                  |                                                              |      |      |          |               |

| Supply current                                                |                                                              | 17   | 21   |          | mA            |

(4) Current into C/S SS required to latch circuit in shutdown state.

(5) Current into C/S SS assured not to latch circuit in shutdown state.

## 6.6 Typical Characteristics

## 7 Detailed Description

### 7.1 Overview

The UC1846-SP control devices provide all of the necessary features to implement fixed frequency, current mode control schemes while maintaining a minimum external parts count. The superior performance of this technique can be measured in improved line regulation, enhanced load response characteristics, and a simpler, easier-to-design control loop. Topological advantages include inherent pulse-by-pulse current limiting capability, automatic symmetry correction for push-pull converters, and the ability to parallel “power modules” while maintaining equal current sharing.

### 7.2 Functional Block Diagram

NOTE: Pin numbers shown are for the J package.

### 7.3 Feature Description

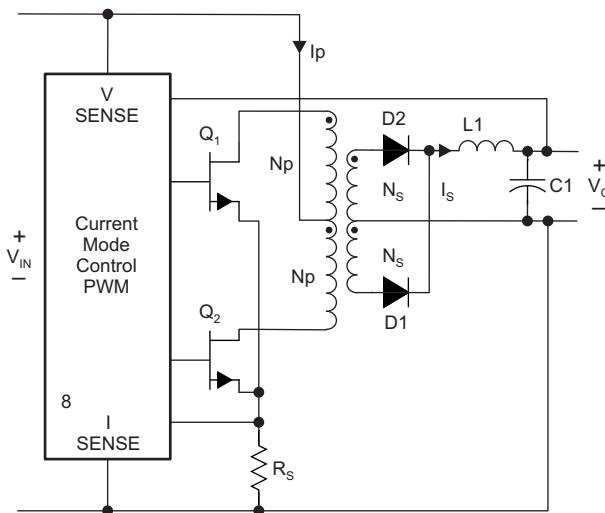

UC1846-SP is a current mode controller, used to support various topologies such as forward, flyback, half-bridge, full bridge, push-pull configurations.

Current mode control is a two-loop system. The switching power supply inductor is hidden within the inner current control loop. This simplifies the design of the outer voltage control loop and improves power supply performance in many ways, including better dynamics. The objective of this inner loop is to control the state-space averaged inductor current, but in practice the instantaneous peak inductor current is the basis for control (switch current, equal to inductor current during the on time, is often sensed). If the inductor ripple current is small, peak inductor current control is nearly equivalent to average inductor current control.

## Feature Description (continued)

The peak method of inductor current control functions by comparing the upslope of inductor current (or switch current) to a current program level set by the outer loop. The comparator turns the power switch off when the instantaneous current reaches the desired level. The current ramp is usually quite small compared to the programming level, especially when  $V_{IN}$  is low. As a result, this method is extremely susceptible to noise. A noise spike is generated each time the switch turns on. A fraction of a volt coupled into the control circuit can cause it to turn off immediately, resulting in a sub-harmonic operating mode with much greater ripple. Circuit layout and bypassing are critically important to successful operation.

The peak current mode control method is inherently unstable at duty ratios exceeding 0.5, resulting in sub-harmonic oscillation. A compensating ramp (with slope equal to the inductor current downslope) is usually applied to the comparator input to eliminate this instability. A slope compensation must be added to the sensed current waveform or subtracted from the control voltage to ensure stability above a 50% duty cycle. A compensating ramp (with slope equal to the inductor current downslope) is usually applied to the comparator input to eliminate this instability.

The pulse width modulator (PWM) of UC1846-SP is limited to a maximum duty cycle of 50%, thus it can be used in topologies such as push-pull, half bridge, full bridge, forward, flyback configurations. Limiting PWM to 50% duty cycle ensures that for isolated or transformer based topologies. The transformer is allowed to reset and prevent saturation of the transformer core.

Pulse-by-pulse symmetry correction (flux balancing) is inherent to current mode controllers and essential for the push-pull topology to prevent core saturation.

Current limit control design has numerous advantages:

1. Current mode control provided peak switch current limiting – pulse by pulse current limit.

2. Control loop is simplified as one pole due to output inductor is pushed to higher frequency, thus a two pole system turns into two real poles. Thus system reduces to a first order system thus simplifies the control.

3. Multiple converter can be paralleled and allows equal current sharing amount the various converters.

4. Inherently provides for input voltage feed-forward as any perturbation in the input voltage will be reflected in the switch or inductor current. Since switch or inductor current is a direct control input, thus this perturbation is very rapidly corrected.

5. The error amplifier output (outer control loop) defines the level at which the primary current (inner loop) will regulate the pulse width, and output voltage.

Figure 3. Push-Pull Converter Using Current Mode Control

### 7.3.1 Reference

As highlighted in the [Functional Block Diagram](#), UC1846-SP incorporates a 5.1-V internal reference regulator with  $\pm 10\%$  set point variation over temperature.

## Feature Description (continued)

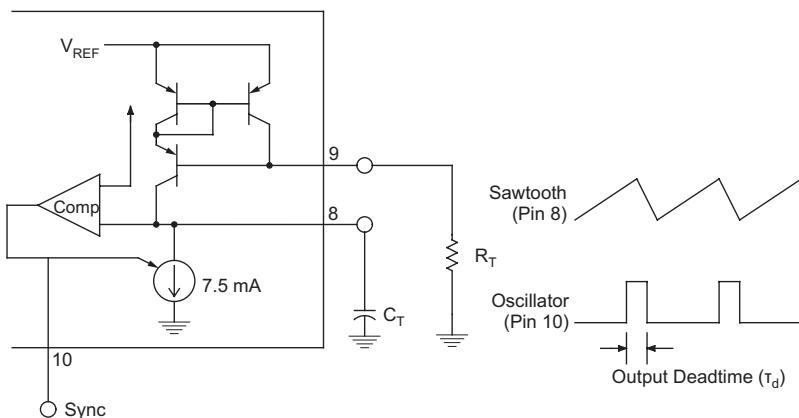

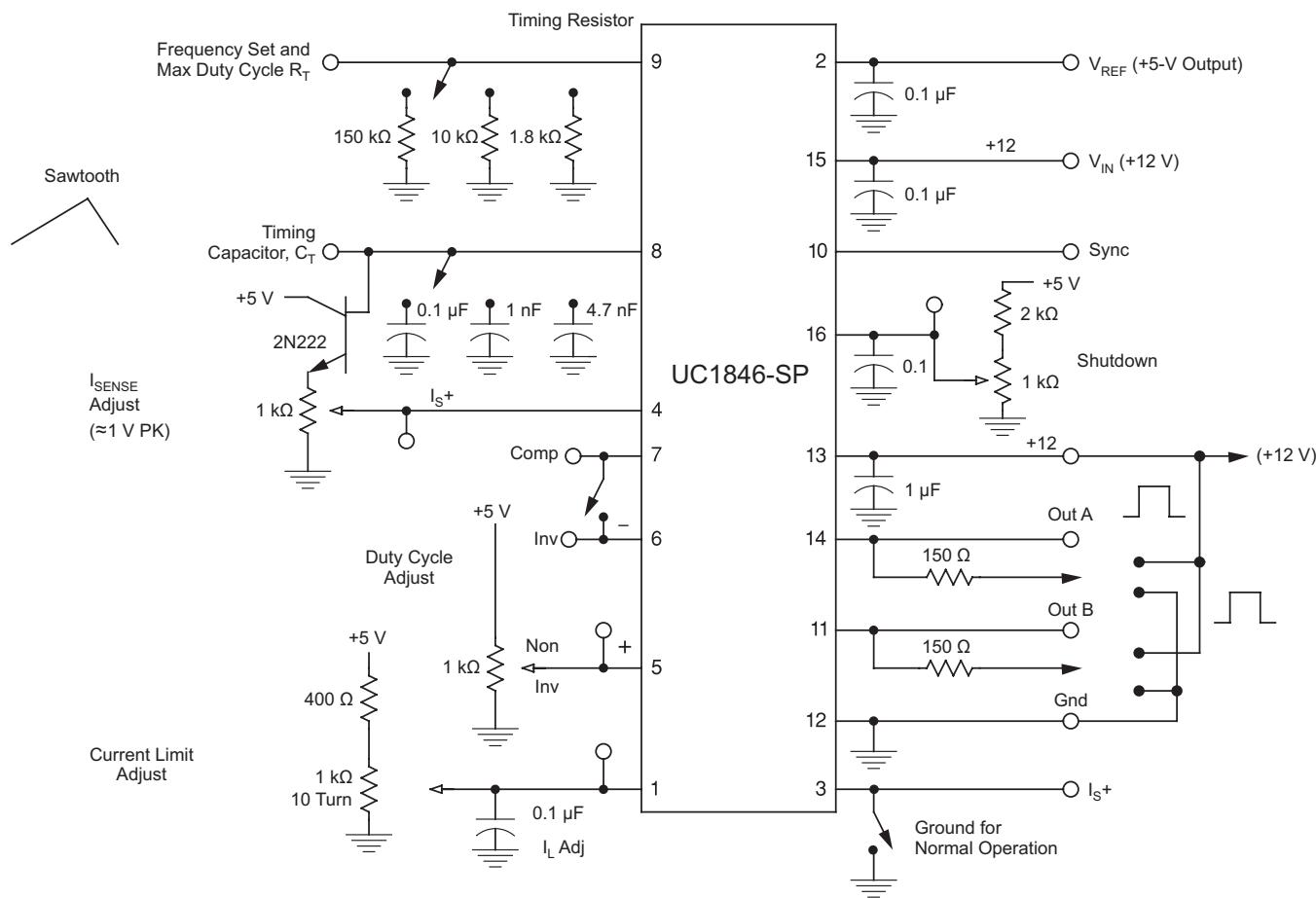

### 7.3.2 Oscillator

Figure 8 highlights the oscillator circuit. Connecting a resistor  $R_T$  from pin 9 to ground establishes a current, which is mirrored to pin 8 and charges the capacitor connected from pin 8 to ground. Maximum on time corresponds to the maximum charging time of the timing capacitor. Oscillator frequency can be determined by [Equation 5](#).

Off-time corresponds to capacitor discharge time establishes the converter dead time between the pulses according to [Equation 4](#). Internal 8-mA current sink discharges the CT pin capacitor.

### 7.3.3 Slope Compensation

For duty cycle above 50% slope compensating can be implemented by using a buffer (that is, 2N2222) and connecting base to timing capacitor pin 8, collector to VREF (5 V), a resistor in series with emitter connected to (pin 4) CS+ of differential current sense amplifier. Injecting a downslope proportional to the sawtooth into current sense amplifier.

As with any bipolar PWM IC, outputs should be protected from negatively biasing the substrate. This is typically done by using Schottky diodes from ground to each output. Failure to do this could cause spurious interruption and restart of the oscillator, dropping of output pulses and a significant increase in propagation delays.

### 7.3.4 Error Amplifier

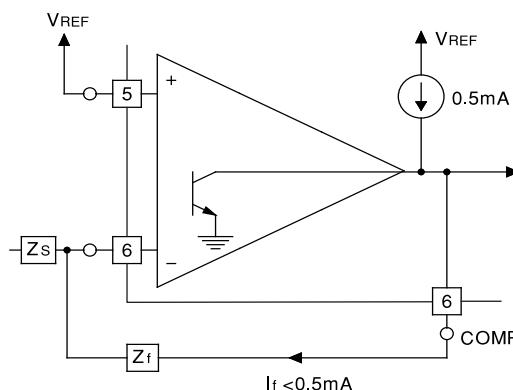

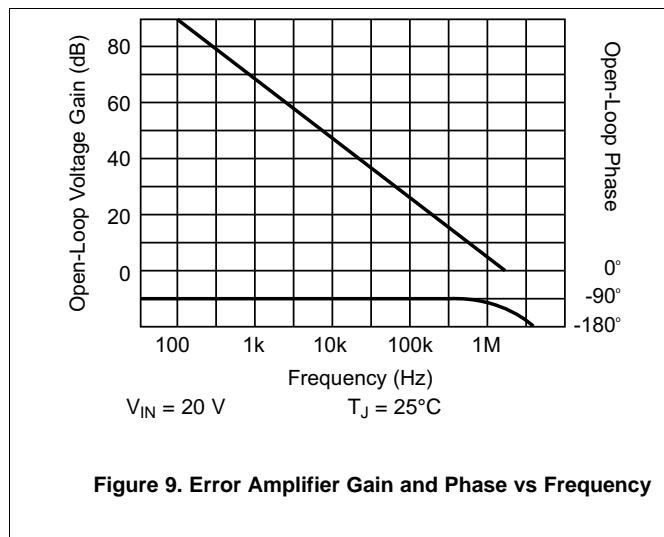

UC1846-SP incorporates an error amplifier with typical open loop gain of 100 dB and gain bandwidth of 1.5 MHz. With Source and sink capability of 10 mA and 0.5 mA respectively.

Error amplifier sources up to 0.5 mA.

**Figure 4. Error Amplifier Output Configuration**

### 7.3.5 Current Sense Amplifier

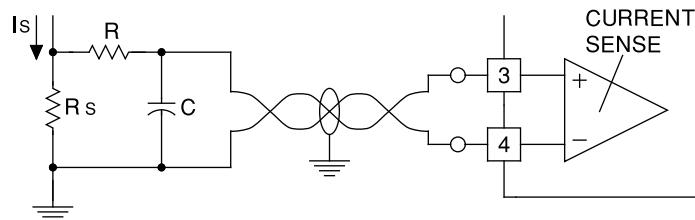

UC1846-SP incorporates a differential current sense amplifier which can eliminate ground loop problems and increase noise immunity. An R-C snubber can also be implemented thus helping in blanking the peak current spike when the switch is turned on. The input of the current sense amplifier is slew rate limited allowing lower values of filter capacitors to be used to eliminate leading edge noise.

A small RC filter may be required in some applications to reduce switch transients. Differential input allows remote, noise-free sensing.

**Figure 5. Current-Sense Amplifier Connections**

## Feature Description (continued)

In some applications, a small RC filter is required to reduce switch transients. Differential input allows remote noise sensing.

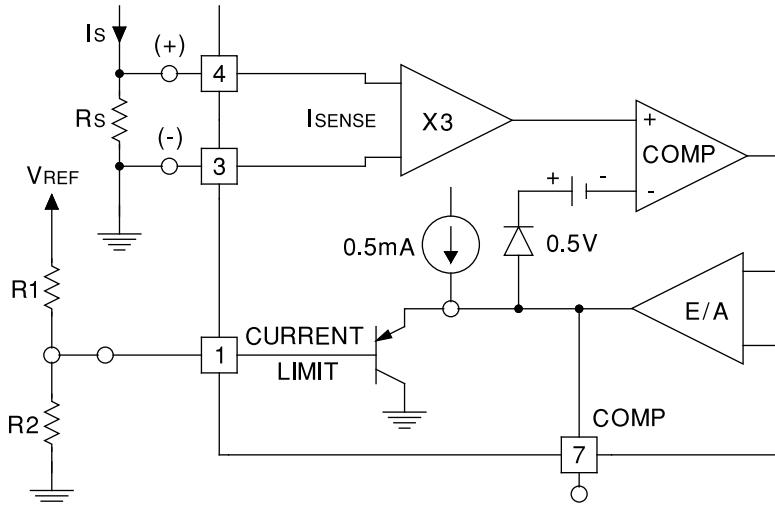

### 7.3.6 Current Limit

Over current trip point is determined by [Equation 1](#). Differential current sense amplifier has a gain of three, as shown in [Figure 6](#).

**Figure 6. Pulse-By-Pulse Current Limiting**

Referring to [Figure 6](#), [Equation 1](#) determines the peak current,  $I_s$ .

$$I_s = \frac{\left( \frac{R_2 V_{REF}}{R_1 + R_2} \right) - 0.5}{3R_s} \quad (1)$$

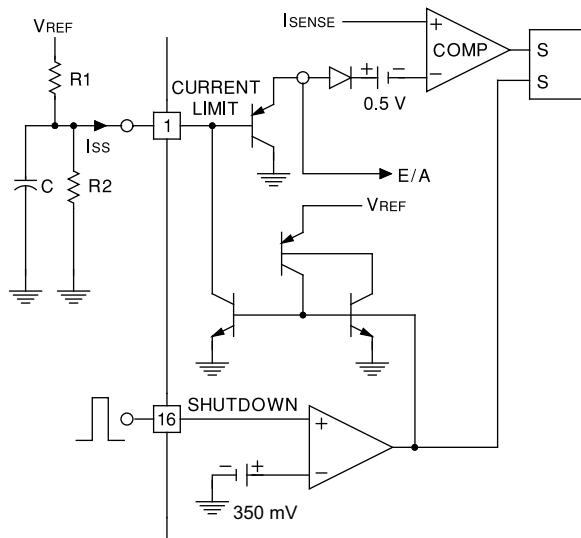

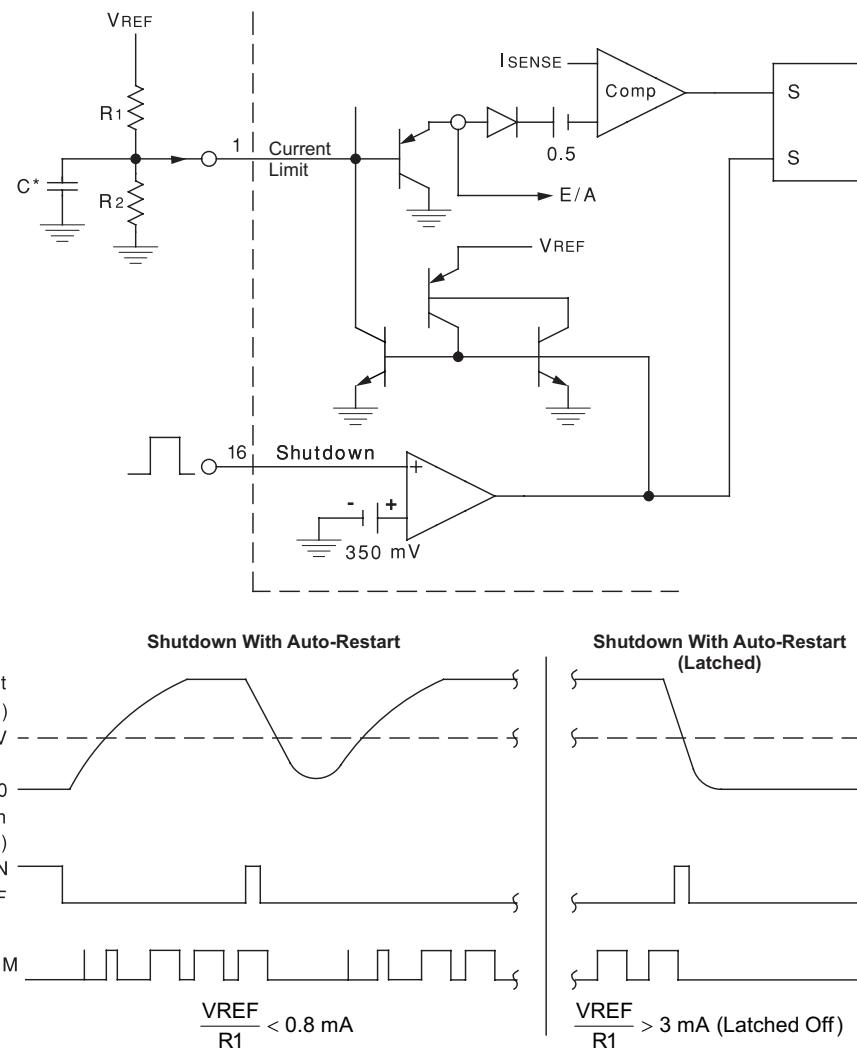

### 7.3.7 Shutdown

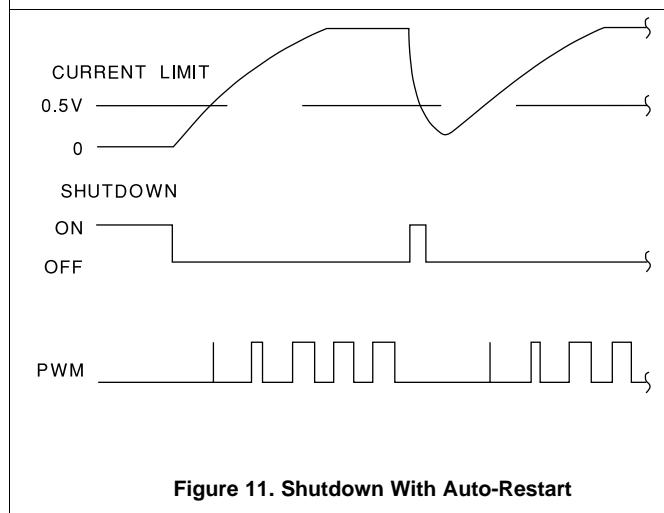

UC1846-SP incorporates a shutdown pin (pin 16). Shutdown threshold voltage is 350 mV. Exceeding the shutdown threshold voltage causes the device to shutdown.

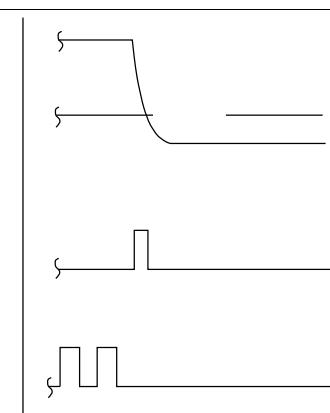

- If current into ICL\_SS  $V_{REF}/R_1 > 3\text{-mA}$  SCR holding current (minimum latch current), then the device latches off. Power recycle is required to un-latch the device.

- If  $V_{REF}/R_1 < 0.8 \text{ mA}$ , that is  $ICL\_SS < 0.8 \text{ A}$ , then this ensures that the circuit does not latch in a shutdown state.

## Feature Description (continued)

**Figure 7. Shutdown Latch**

Referring to [Figure 11](#), if

$$\frac{V_{REF}}{R1} < 0.8 \text{ mA} \quad (2)$$

the shutdown latch commutes when  $ISS = 0.8 \text{ mA}$  and a restart cycle initiates.

Referring to [Figure 12](#), if

$$\frac{V_{REF}}{R1} > 3 \text{ mA} \quad (3)$$

the device latches off until power is recycled.

### 7.3.8 Output Section

UC1846-SP incorporates high current dual totem pole output stage capable of sourcing/sinking 1.5-A peak current for fast switching of power MOSFETs and limited to 0.5-A DC current.

### 7.3.9 Undervoltage Lockout

Minimum input voltage for converter is 8 V or higher, with typical value being 7.7 V. At input voltages below the actual UVLO voltage, the devices will not operate.

### 7.3.10 Soft-Start

Connecting a capacitor from CL/SS pin 1 to ground which is charged by 0.5-mA internal current source will determine the soft-start time. If over current is also implemented as shown in [Figure 6](#), then SS charge time will be determined by charging SS capacitor by 0.5-mA current as well as current contributed by R1 resistor in charging the SS capacitor.

## 7.4 Device Functional Modes

### 7.4.1 Operation With $V_{IN} < 8 \text{ V}$ (Minimum $V_{IN}$ )

The devices operate with input voltages above 8 V. The maximum UVLO voltage is 8 V and will operate at input voltages above 8 V. The typical UVLO voltage is 7.7 V and the devices may operate at input voltages above that point. The devices also may operate at lower input voltages, the minimum UVLO voltage is not specified. At input voltages below the actual UVLO voltage, the devices will not operate.

## Device Functional Modes (continued)

### 7.4.2 Synchronization

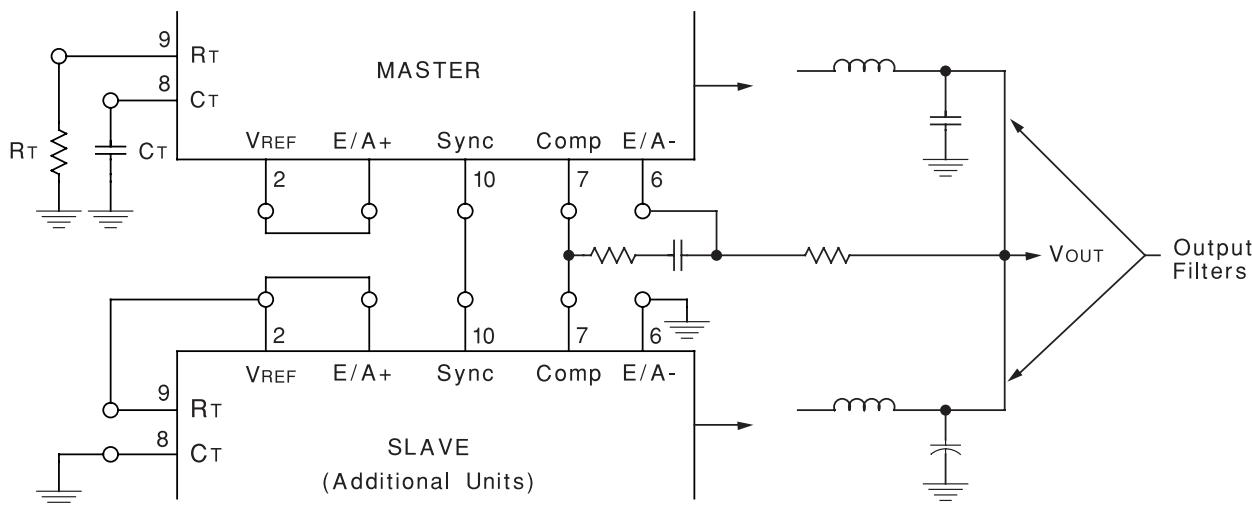

The synchronization pin (pin10) can be configured as an output for master/slave application. When the converter is configured as a master or standalone converter, SYNC (pin 10) is an output. As highlighted in the functional block diagram, voltage at RT (pin 9) is greater than 4.1-V internal threshold.

When using the part in slave configuration, SYNC pin becomes an input. Typical example of parallel operation with master/slave configuration is shown in [Figure 13](#). Slave unit CT (pin 8) is grounded and RT pin is connected to VREF (pin 2).

When using the part in slave configuration, SYNC pin becomes an input. Typical example of parallel operation with master/slave configuration is shown in [Figure 13](#). Slave unit CT (pin 8) is grounded and RT pin is connected to VREF (pin 2). Under parallel configuration two or more units can be paralleled, with COMP pins tied together each will share current equally.

### 7.4.3 Parallel Operation

Under parallel configuration two or more units can be paralleled, with COMP pins tied together each will share current equally.

[Figure 13](#) highlights typical parallel operation configuration.

## 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

UC1846-SP can be used as a controller to design various topologies such as push-pull, half-bridge, full bridge, and flyback.

The following sections highlight the topologies for oscillators, error amplifiers, and parallel configurations (paralleling two EVMs).

### 8.2 Typical Applications

#### 8.2.1 Oscillator Circuit Application

A. Output dead time is determined by the external capacitor,  $C_T$ , according to the formula:

$$\tau_d \text{ } (\mu\text{s}) = 145CT \text{ } (\mu\text{F}) \frac{ID}{ID - \frac{3.6}{RT \text{ } (k\Omega)}} \quad (4)$$

- B.  $ID$  = Oscillator discharge current at  $25^\circ\text{C}$  is typically 7.5.

- C. For large values of  $\tau_d \text{ } (\mu\text{s}) = 145CT \text{ } (\mu\text{F})$

- D. Oscillator frequency is approximated by the formula:

$$f_T \text{ } (\text{kHz}) \approx \frac{2.2}{RT \text{ } (k\Omega) \times CT \text{ } (\mu\text{F})} \quad (5)$$

**Figure 8. Oscillator Circuit**

##### 8.2.1.1 Design Requirements

**Table 1. Design Parameters**

| DESIGN PARAMETER                   | EXAMPLE VALUE                                     | REFERENCE                            |

|------------------------------------|---------------------------------------------------|--------------------------------------|

| Oscillator frequency = 200 kHz     | $R_T = 10 \text{ k}\Omega$ , $C_T = 1 \text{ nF}$ | <a href="#">Equation 4, Figure 8</a> |

| Dead time, $T_d = 75.8 \text{ ns}$ | $R_T = 10 \text{ k}\Omega$ $C_T = 1 \text{ nF}$   | <a href="#">Equation 5, Figure 8</a> |

### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Input Capacitor Selection

Load current, duty cycle, and switching frequency are several factors which determine the magnitude of the input ripple voltage. Without the input capacitor, the pulsating current of Q1 would need to be completely supplied by the host source, VIN, which commonly does not have sufficiently low output impedance. Thus there would be substantial noise on the host DC voltage source and an increase in the conducted EMI on the board. The input capacitor, CIN, effectively filters the input current so the current from the host DC source is approximately an average current.

The input ripple voltage amplitude is directly proportional to the output load current. The maximum input ripple amplitude occurs at maximum output load. Also, the amplitude of the voltage ripple varies with the duty cycle of the converter.

UC1846-SP requires a high quality ceramic, type X5R or X7R, input decoupling capacitor of at least 47  $\mu$ F of effective capacitance on the VIN input voltage pins. In some applications additional bulk capacitance may also be required for the VIN input. The effective capacitance includes any DC bias effects. The voltage rating of the input capacitor must be greater than the maximum input voltage. The capacitor must also have a ripple current rating greater than the maximum input current ripple of the UC1846-SP. The input ripple current can be calculated using [Equation 6](#).

$$I_{CIRMS} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{INMIN}} \times \frac{(V_{INMIN} - V_{OUT})}{V_{INMIN}}} \quad (6)$$

The value of a ceramic capacitor varies significantly over temperature and the amount of DC bias applied to the capacitor. The capacitance variations due to temperature can be minimized by selecting a dielectric material that is stable over temperature. X5R and X7R ceramic dielectrics are usually selected for power regulator capacitors because they have a high capacitance to volume ratio and are fairly stable over temperature. The output capacitor must also be selected with the DC bias taken into account. The capacitance value of a capacitor decreases as the DC bias across a capacitor increases.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using [Equation 7](#).

$$\Delta V_{IN} = \frac{I_{OUT} \times 0.25}{C_{IN} \times f_{SW}} \quad (7)$$

#### 8.2.1.2.2 Output Capacitor Selection

The output capacitance of a switching regulator is a vital part of the overall feedback system. The energy storage inductor and the output capacitor form a second-order low-pass filter.

In switching power supply power stages, the function of output capacitance is to store energy. The energy is stored in the capacitor's electric field due to the voltage applied. Thus, qualitatively, the function of a capacitor is to attempt to maintain a constant voltage.

The value of output capacitance of a buck power stage is generally selected to limit output voltage ripple to the level required by the specification. Since the ripple current in the output inductor is usually already determined, the series impedance of the capacitor primarily determines the output voltage ripple. The three elements of the capacitor that contribute to its impedance (and output voltage ripple) are equivalent series resistance (ESR), equivalent series inductance (ESL), and capacitance (C). The following gives guidelines for output capacitor selection.

For continuous inductor current mode operation, to determine the amount of capacitance needed as a function of inductor current ripple,  $\Delta I_L$ , switching frequency,  $f_S$ , and desired output voltage ripple,  $\Delta V_O$ , [Equation 8](#) is used assuming all the output voltage ripple is due to the capacitor's capacitance.

$$C \geq \frac{\Delta I_L}{8 \times f_S \times \Delta V_O}$$

where  $\Delta I_L$  is the inductor ripple current.

$$\bullet \quad (8)$$

Each capacitor type is characterized by its impedance and the frequency range over which it is most effective. The frequency at which the impedance reaches its minimum is determined by its ESR and ESL. It is known as the self resonant frequency of the capacitor. The self resonant frequency is considered to be the maximum usable frequency for a capacitor. Above this frequency the impedance of the capacitor begins to rise as the ESL of the capacitor begins to dominate. Note that each capacitor type has a specific frequency band over which it is most effective. Therefore, a capacitor network of multiple capacitor types is more effective in reducing impedance than just one type.

The current slew rate of a regulator is limited by its output filter inductor. When the amount of current required by the load changes, the initial current deficit must be supplied by the output capacitors until the regulator can meet the load demand.

The desired response to a large change in the load current is the first criteria. The output capacitor needs to supply the load with current when the regulator control loop can not supply the current. This happens when Load (ie: memory, processor) has a large and fast increase in current, such as a transition from no load to full load. The regulator typically needs two or more clock cycles for the control loop to see the change in load current, output voltage and adjust the duty cycle to react to the change. The output capacitor must be properly sized to supply the extra current to the Load until the control loop responds to the Load change. The output capacitance must be large enough to supply the difference in current for 2 clock cycles while only allowing a tolerable amount of droop in the output voltage. [Equation 9](#) shows the minimum output capacitance necessary to accomplish this.

$$C_O > \frac{2 \times \Delta I_{out}}{f_{sw} \times \Delta V_{out}} \quad (9)$$

Where  $\Delta I_{out}$  is the change in output current,  $f_{sw}$  is the regulators switching frequency and  $\Delta V_{out}$  is the allowable change in the output voltage. For this example, the transient load response is specified as a 5% change in  $V_{out}$  for a load step of 1 A. For this example,  $\Delta I_{out} = 1 \text{ A}$  and  $\Delta V_{out} = 0.05 \times 3.3 = 0.165 \text{ V}$ . Using these numbers gives a minimum capacitance of  $25 \mu\text{F}$ . This value does not take the ESR of the output capacitor into account in the output voltage change. For ceramic capacitors, the ESR is usually small enough to ignore in this calculation.

#### 8.2.1.2.3 Output Inductor Selection

To calculate the value of the output inductor, use [Equation 10](#).  $K_{ind}$  is a coefficient that represents the amount of inductor ripple current relative to the maximum output current. The inductor ripple current is filtered by the output capacitor. Therefore, choosing high inductor ripple currents impact the selection of the output capacitor since the output capacitor must have a ripple current rating equal to or greater than the inductor ripple current. In general, the inductor ripple value is at the discretion of the designer; however,  $K_{ind}$  is normally from 0.1 to 0.3 for the majority of applications.  $V_{inLC}$  refers to the voltage at the input of output LC filter.

$$L_1 = \frac{V_{inLC} - V_{out}}{I_{o} \times K_{ind}} \times \frac{V_{out}}{V_{inLC} \times f_{sw}} \quad (10)$$

The current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults or transient load conditions, the inductor current can increase above the calculated peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

#### 8.2.1.2.4 Switching Frequency

Initial accuracy of UC1846-SP oscillator frequency is 200 kHz  $\pm 15\%$  over the temperature range. Switching frequency selection is a trade-off between the overall design size and efficiency. Operating at lower switching frequency will result in higher efficiency at the expense of larger solution footprint.

Oscillator frequency can be determined as follows:

$$R_T = 10 \text{ k}\Omega \quad (11)$$

$$C_T = 1 \text{ nF} \quad (12)$$

$$f_T = \frac{2}{R_T \times C_T} \quad (13)$$

$$f_T = 200 \text{ kHz} \quad (14)$$

### 8.2.1.3 Application Curves

Figure 9. Error Amplifier Gain and Phase vs Frequency

Figure 10. Error Amplifier Open-Loop DC Gain vs Load Resistance

Figure 11. Shutdown With Auto-Restart

Figure 12. Shutdown Without Auto-Restart (Latched)

## 8.2.2 Parallel Operation

Slaving allows parallel operation of two or more units with equal current sharing.

**Figure 13. Parallel Operation**

### 8.2.2.1 Design Requirements

Refer to [Design Requirements](#) for the oscillator circuit design requirements.

### 8.2.2.2 Detailed Design Procedure

Refer to [Detailed Design Procedure](#) for the oscillator circuit detailed design procedure.

### 8.2.3 Soft-Start and Shutdown/Restart Functions Application

A. If  $\frac{V_{REF}}{R_1} < 0.8 \text{ mA}$ , the shutdown latch commutes when  $I_{SS} = 0.8 \text{ mA}$  and a restart cycle will be initiated.

B. If  $\frac{V_{REF}}{R_1} > 3 \text{ mA}$ , the device latches off until power is recycled.

**Figure 14. Soft-Start and Shutdown/Restart Functions**

### 8.2.4 Open-Loop Test Circuit Application

- Bypass capacitors should be low ESR and ESL type.

- Short pins 6 and 7 for unity gain testing.

**Figure 15. Open-Loop Test Circuit**

## 9 Power Supply Recommendations

The devices are designed to operate from an input voltage supply range between 8 V and 40 V. This input supply should be well regulated. If the input supply is located more than a few inches from the UC1846-SP converter additional bulk capacitance may be required in addition to the ceramic bypass capacitors. A tantalum capacitor with a value of 47  $\mu$ F is a typical choice, however this may vary depending upon the output power being delivered.

## 10 Layout

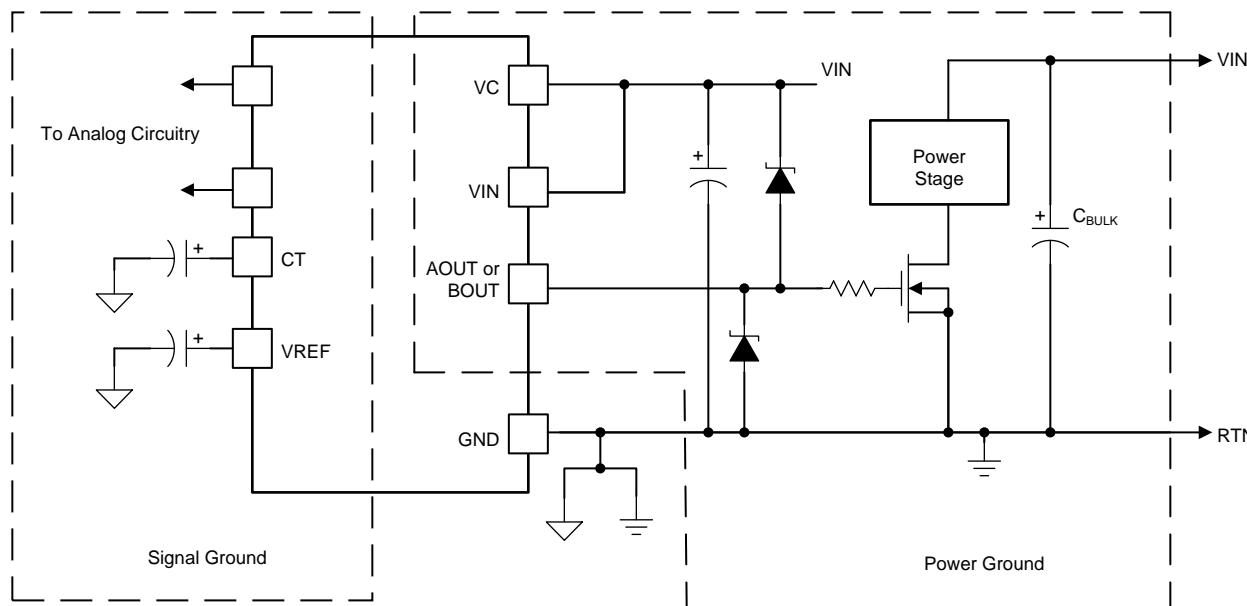

### 10.1 Layout Guidelines

Always try to use a low EMI inductor with a ferrite type closed core. Some examples would be toroid and encased E core inductors. Open core can be used if they have low EMI characteristics and are located a bit more away from the low power traces and components. Make the poles perpendicular to the PCB as well if using an open core. Stick cores usually emit the most unwanted noise.

Each output driver of these devices is capable of 2-A peak currents. Careful layout is essential for correct operation of the chip. A ground plane must be employed. A unique section of the ground plane must be designated for high di/dt currents associated with the output stages. Power ground can be separated from the rest of the ground plane and connected at a single point, although this is not necessary if the high di/dt paths are well understood and accounted for. VIN should be bypassed directly to power ground with a good high frequency capacitor. The sources of the power MOSFET should connect to power ground as should the return connection for input power to the system and the bulk input capacitor. The output should be clamped with a high current Schottky diode to both VIN and GND. Nothing else should be connected to power ground.

VREF should be bypassed directly to the signal portion of the ground plane with a good high frequency capacitor. Low ESR/ESL ceramic 1- $\mu$ F capacitors are recommended for both VIN and VREF. All analog circuitry should likewise be bypassed to the signal ground plane.

### 10.2 Layout Example

Figure 16. Layout Recommendation

## 11 Device and Documentation Support

### 11.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on [ti.com](http://ti.com). In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™ Online Community** *TI's Engineer-to-Engineer (E2E) Community*. Created to foster collaboration among engineers. At [e2e.ti.com](http://e2e.ti.com), you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 11.3 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.5 Glossary

[SLYZ022](#) — *TI Glossary*.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6)                |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|------------------------------------|

| 5962-8680601V2A       | Active        | Production           | LCCC (FK)   20  | 55   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680601V2A<br>UC1846L<br>QMLV |

| 5962-8680601V2A.A     | Active        | Production           | LCCC (FK)   20  | 55   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680601V2A<br>UC1846L<br>QMLV |

| 5962-8680601VEA       | Active        | Production           | CDIP (J)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680601VE<br>A<br>UC1846JQMLV |

| 5962-8680601VEA.A     | Active        | Production           | CDIP (J)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680601VE<br>A<br>UC1846JQMLV |

| 5962-8680603V2A       | Active        | Production           | LCCC (FK)   20  | 55   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603V2A<br>UC1846FK<br>-SP |

| 5962-8680603V2A.A     | Active        | Production           | LCCC (FK)   20  | 55   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603V2A<br>UC1846FK<br>-SP |

| 5962-8680603V9A       | Active        | Production           | XCEPT (KGD)   0 | 100   OTHER           | Yes         | Call TI                              | N/A for Pkg Type                  | -55 to 125   |                                    |

| 5962-8680603V9A.A     | Active        | Production           | XCEPT (KGD)   0 | 100   OTHER           | Yes         | Call TI                              | N/A for Pkg Type                  | -55 to 125   |                                    |

| 5962-8680603VEA       | Active        | Production           | CDIP (J)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603VE<br>A<br>UC1846J-SP  |

| 5962-8680603VEA.A     | Active        | Production           | CDIP (J)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603VE<br>A<br>UC1846J-SP  |

| 5962-8680603VFA       | Active        | Production           | CFP (W)   16    | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603VF<br>A<br>UC1846W-SP  |

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6)               |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|-----------------------------------|

| 5962-8680603VFA.A     | Active        | Production           | CFP (W)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962-8680603VF<br>A<br>UC1846W-SP |

| 5962P8680603VEA       | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962P8680603VE<br>A<br>UC1846J-SP |

| 5962P8680603VEA.A     | Active        | Production           | CDIP (J)   16  | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962P8680603VE<br>A<br>UC1846J-SP |

| 5962P8680603VFA       | Active        | Production           | CFP (W)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962P8680603VF<br>A<br>UC1846W-SP |

| 5962P8680603VFA.A     | Active        | Production           | CFP (W)   16   | 25   TUBE             | No          | SNPB                                 | N/A for Pkg Type                  | -55 to 125   | 5962P8680603VF<br>A<br>UC1846W-SP |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UC1846-SP :**

- Catalog : [UC1846](#)

- Enhanced Product : [UC1846-EP](#)

**NOTE: Qualified Version Definitions:**

- Catalog - TI's standard catalog product

- Enhanced Product - Supports Defense, Aerospace and Medical Applications

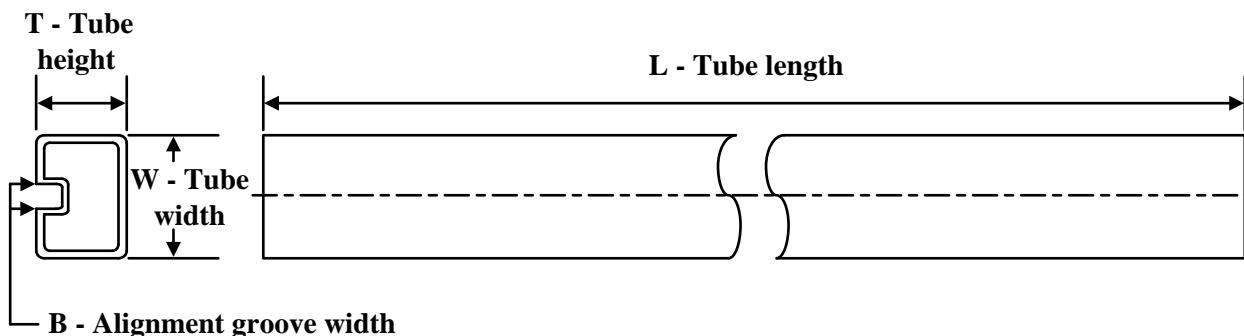

**TUBE**

\*All dimensions are nominal

| Device            | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| 5962-8680601V2A   | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| 5962-8680601V2A.A | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| 5962-8680603V2A   | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| 5962-8680603V2A.A | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| 5962-8680603VFA   | W            | CFP          | 16   | 25  | 506.98 | 26.16  | 6220   | NA     |

| 5962-8680603VFA.A | W            | CFP          | 16   | 25  | 506.98 | 26.16  | 6220   | NA     |

| 5962P8680603VEA   | J            | CDIP         | 16   | 25  | 506.98 | 15.24  | 13440  | NA     |

| 5962P8680603VEA.A | J            | CDIP         | 16   | 25  | 506.98 | 15.24  | 13440  | NA     |

| 5962P8680603VFA   | W            | CFP          | 16   | 25  | 506.98 | 26.16  | 6220   | NA     |

| 5962P8680603VFA.A | W            | CFP          | 16   | 25  | 506.98 | 26.16  | 6220   | NA     |

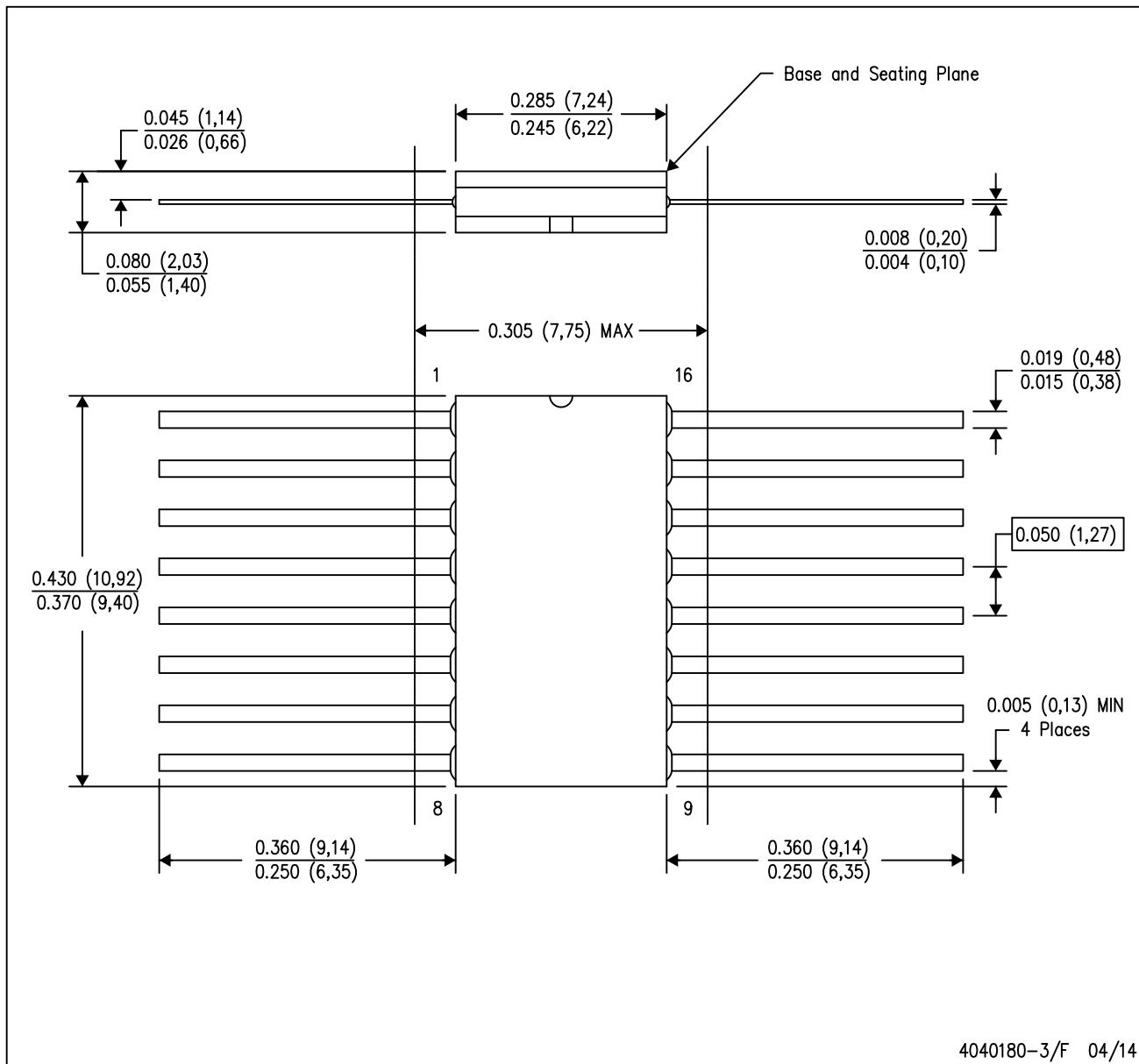

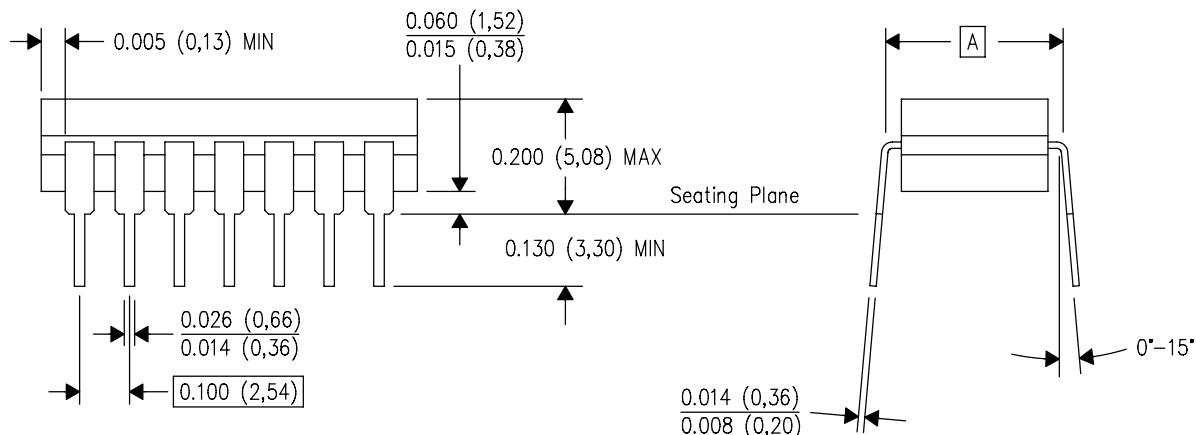

W (R-GDFP-F16)

CERAMIC DUAL FLATPACK

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL-STD 1835 GDFP2-F16

# GENERIC PACKAGE VIEW

**FK 20**

**LCCC - 2.03 mm max height**

**8.89 x 8.89, 1.27 mm pitch**

**LEADLESS CERAMIC CHIP CARRIER**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4229370VA\

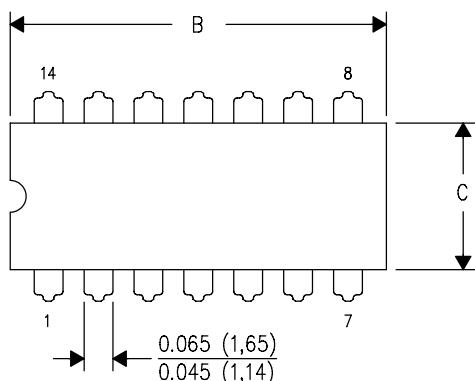

J (R-GDIP-T\*\*)

14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

| PINS **<br>DIM | 14                     | 16                     | 18                     | 20                     |

|----------------|------------------------|------------------------|------------------------|------------------------|

| A              | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC | 0.300<br>(7,62)<br>BSC |

| B MAX          | 0.785<br>(19,94)       | .840<br>(21,34)        | 0.960<br>(24,38)       | 1.060<br>(26,92)       |

| B MIN          | —                      | —                      | —                      | —                      |

| C MAX          | 0.300<br>(7,62)        | 0.300<br>(7,62)        | 0.310<br>(7,87)        | 0.300<br>(7,62)        |

| C MIN          | 0.245<br>(6,22)        | 0.245<br>(6,22)        | 0.220<br>(5,59)        | 0.245<br>(6,22)        |

4040083/F 03/03

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. This package is hermetically sealed with a ceramic lid using glass frit.

D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to [TI's Terms of Sale](#), [TI's General Quality Guidelines](#), or other applicable terms available either on [ti.com](#) or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2026, Texas Instruments Incorporated

Last updated 10/2025