# Design Considerations With Dual-Channel SR Controller UCC24624

Aki Li, Bing Lu

## ABSTRACT

The UCC24624 is a high-performance synchronous rectifier (SR) controller for LLC resonant converter applications. It integrates two channels of SR control into a single 8-pin SOIC package, minimizes the external components, and simplifies PCB layout. Many features make the UCC24624 device a good choice for the high-efficiency LLC solutions, including proportional gate drive, adjustable turn-off threshold, two-channel interlock, automatic standby mode transition, and so forth. A common use of the UCC24624 is to implement it with the LLC controller UCC25640x or a single digital controller in the primary side, used in industrial AC/DC, server PSU and telecom power applications. To accelerate the design process with the UCC24624, several common questions or concerns are discussed in this report.

#### Contents

| 1 | Gate Driving Capability        | 2 |

|---|--------------------------------|---|

| 2 | UCC24624 Power Loss Estimation | 3 |

| 3 | Turn-off Threshold Adjustment  | 5 |

| 4 | Light Load Operation           | 6 |

| 5 | References                     | 7 |

## List of Figures

| 1 | IPB072N15N3 Drain Source On-Resistance      | 2 |

|---|---------------------------------------------|---|

| 2 | Driving Capability Simulation Circuit       | 2 |

| 3 | Simulation Result of the Driving Capability | 3 |

| 4 | UCC24624 Sensed Voltage                     |   |

| 5 | SR Early Turn Off                           | 5 |

| 6 | Decreasing Turn-off Threshold Circuit       | 6 |

| 7 | Adaptive Turn-on Delay                      | 7 |

| 8 | Adding RC Filter at VD Pins                 | 7 |

|   | -                                           |   |

## List of Tables

| 1 | UCC24624 Gate Driver Characteristics |  | 3 |

|---|--------------------------------------|--|---|

|---|--------------------------------------|--|---|

# Trademarks

All trademarks are the property of their respective owners.

#### Gate Driving Capability

## 1 Gate Driving Capability

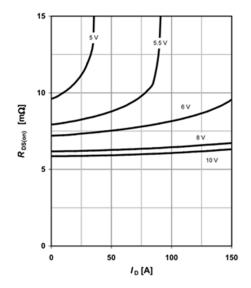

In higher power level applications, SR MOSFETs are configured in parallel, to achieve lower on-state resistance, which results in lower conduction loss and better efficiency. Meanwhile, the amplitude of the gate driver voltage V<sub>GS</sub> determines the actual drain-source on-state resistance (R<sub>DS(on)</sub>) of the MOSFET. Taking the MOSFET IPB072N15N3 as an example, Figure 1 shows the relationship between R<sub>DS(on)</sub> and different V<sub>GS</sub> amplitudes.

Figure 1. IPB072N15N3 Drain Source On-Resistance

Ideally, with the internal linear regulator, the UCC24624 device can clamp the gate driver voltage to a maximum level of 11 V with the VDD supply voltage above 11 V. This minimizes the conduction loss for MOSFETs. However, the SR MOSFET is only driven high with the full driving capability of the UCC24624 of 1.5 A during its minimum pullup time  $t_{MGPU}$  (typically 275 ns). After that, the SR MOSFET gate is kept high by a weak current source of approximately 200  $\mu$ A. Thus, it is helpful to check what the final amplitude of V<sub>GS</sub> can reach during the UCC24624  $t_{MGPU}$  interval, especially in the applications where several SR MOSFETs are in parallel.

See the *Fundamentals of MOSFET and IGBT Gate Driver Circuits Application Report*, before being turned on by UCC24624, the SR MOSFET body diode conducts first. The drain-to-source voltage V<sub>ds</sub> equals the body diode forward voltage drop. At that moment, the parasitic capacitances  $C_{GD}$  and  $C_{DS}$  are actually discharged to 0. Also, the Miller effect is not present. Thus, the full driving process is to raise the voltage across  $C_{GD}$  and  $C_{DS}$  capacitors from 0 V to the final VGS level. Taking 3 IPB072N15N3 MOSFETs in parallel as an example, a simple simulation method with Simplis is discussed as follows.

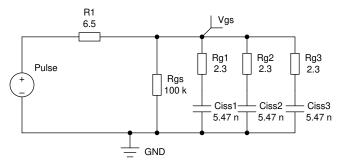

According to the dynamic characteristics in the IPB072N15N3 data sheet, the input capacitance  $C_{iss} = 5.47$  nF, the gate resistance  $R_G = 2.3 \Omega$ . If using the UCC24624 to directly drive 3 IPB072N15N3 devices, the simulation circuit is shown in Figure 2.

Figure 2. Driving Capability Simulation Circuit

The pulse source is a 275-ns width pulse with an amplitude of 11 V. R1 = 6.5  $\Omega$  refers to the VG pullup resistance inside UCC24624, as shown in Table 1. Note that R<sub>gs</sub> = 100 k $\Omega$  is selected, which is a bit larger than normal applications. Traditionally, this resistor is used to discharge the charge built up on the SR gate. Due to the weak pullup current in UCC24624, this resistor needs to have much larger value than the traditional 10-k $\Omega$  pulldown. The 100-k $\Omega$  resistance together the internal 200 µA allows the SR gate to remain at 11-V driving voltage level, after the minimum pullup time, t<sub>MGPU</sub>. The resistance is so large that it does not affect the pullup capability.

| Parameter          |                        | Test Conditions         | MIN  | TYP  | MAX   | Unit |

|--------------------|------------------------|-------------------------|------|------|-------|------|

| R <sub>VG_PU</sub> | VG pullup resistance   |                         | 3.5  | 6.5  | 11.25 | Ω    |

| R <sub>VG_PD</sub> | VG pulldown resistance |                         | 0.2  | 0.9  | 1.5   | Ω    |

| VG <sub>HI</sub>   | VG high clamp level    | $I_{VG} = 0 \text{ mA}$ | 9.95 | 10.9 | 11.68 | V    |

| Table 1. UCC24624 Ga | e Driver Characteristics <sup>(1)</sup> |

|----------------------|-----------------------------------------|

|----------------------|-----------------------------------------|

$^{(1)} \quad \text{At V}_{\text{VDD}} = 12 \text{ VDC}, \text{ C}_{\text{VG1}} = \text{C}_{\text{VG2}} = 0 \text{ pF}, \text{ C}_{\text{REG}} = 2.2 \text{ } \mu\text{F} \text{ V}_{\text{VD1}} = \text{V}_{\text{VD2}} = 0 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} = \text{T}_{\text{A}} \leq +125^{\circ}\text{C} \text{ } \text{C}_{\text{VD1}} = 10^{\circ}\text{C} \text{ } \text{C}_{\text{VD2}} = 0^{\circ}\text{C} \text{ } \text{C} \text{ } \text{C} \text{C}_{\text{VD2}} = 0^{\circ}\text{C} \text{ } \text{C} \text{ } \text{C}$

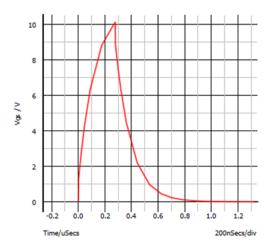

Figure 3 shows the simulation result of the driving capability, indicating that  $V_{gs}$  can be driven up to 10.1 V within the  $t_{MGPU}$  interval, which is high enough to ensure minimum  $R_{DS(on)}$  during conduction. Observing the  $R_{DS(on)}$  vs.  $V_{gs}$  curve, it can be seen when the gate voltage is above 8 V, the  $R_{DS(on)}$  reduction becomes relatively small.

Figure 3. Simulation Result of the Driving Capability

# 2 UCC24624 Power Loss Estimation

Since UCC24624 is used in LLC converters with high-switching frequency, it is important to evaluate its thermal performance. Ensure the UCC24624 device is operating within its thermal safety-related conditions. The power loss of UCC24624 can be estimated by two main portions.

The first portion is the static power loss  $P_Q$ . The  $I_{VDDRUN} = 1.1$  mA referring to the run mode is selected here. Assuming  $V_{VDD}$  is supplied by 12 V, the  $P_Q$  can be calculated with Equation 1:  $P_Q = V_{VDD} \times I_{VDDRUN} = 13.2$  mW

The second one is switching operation loss  $P_{DRV}$ . The total dynamic loss  $P_{SW}$ , due to charging or discharging the  $C_{ISS}$  capacitor, can be calculated as Equation 2 shows:

<sub>SW</sub> =

$$2 \times Q_g \times V_{gs} \times f_{sw} \times N$$

where

Ρ

- Q<sub>g</sub> is the gate charge of the MOSFET

- f<sub>sw</sub> is the gate-drive frequency

- N is the number of the MOSFET in parallel

(2)

3

(1)

www.ti.com

(4)

(7)

(8)

(9)

### UCC24624 Power Loss Estimation

Using the example application in Section 1, and assuming the LLC frequency is 200 kHz, the calculated result:

$$P_{SW} = 2 \times 70 \text{ nC} \times 10.1 \text{ V} \times 200 \text{ kHz} \times 3 = 848 \text{ mW}$$

(3)

$P_{sw}$  is dissipated in the gate drive circuits, including the driver output impedances, the external gate resistor and the internal gate mesh resistance, so  $P_{DRV}$  can be expressed

$\mathsf{P}_{\mathsf{DRV}} = \frac{\mathsf{P}_{_{\mathsf{SW}}}}{2} \, \times \, (\, \frac{\mathsf{R}_{_{\mathsf{VG}},\mathsf{PU}}}{\mathsf{R}_{_{\mathsf{VG}},\mathsf{PU}} + \mathsf{R}_{_{\mathsf{gate}}} + \mathsf{R}_{_{\mathsf{g}}}^{'}} + \frac{\mathsf{R}_{_{\mathsf{VG}},\mathsf{PD}}}{\mathsf{R}_{_{\mathsf{VG}},\mathsf{PD}} + \mathsf{R}_{_{\mathsf{gate}}} + \mathsf{R}_{_{\mathsf{g}}}^{'}} \,)$

where

- Pullup resistance  $R_{VG_{PU}} = 6.5 \Omega$

- Pulldown resistance  $R_{VG_{PD}} = 0.9 \Omega$

According to Table 1;  $R_{gate}$  refers to the external gate resistor, and takes 0 in this example.  $R'_{g}$  is the equivalent resistance of 3 IPB072N15N3 in parallel, 2.3  $\Omega$  / 3 = 0.76  $\Omega$ .

Thus, P<sub>DRV</sub> in this case can be calculated as

$$\frac{848 \text{ mW}}{2} \times \left(\frac{6.5}{6.5+0.7} + \frac{0.9}{0.9+0.76}\right) = 609 \text{ mW}$$

(5)

Therefore, the total power loss dissipated in UCC24624 is

$$P_{LOSS} = P_Q + P_{DRV} = 622.2 \text{ mW}$$

(6)

According to the Semiconductor and IC Package Thermal Metrics Application Report, the junction temperature (T<sub>J</sub>) of the UCC24624 can be estimated with Equation 7:

$$\mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{PCB}} + \Psi_{\mathsf{JB}} \times \mathsf{P}_{\mathsf{LOSS}}$$

or

$T_J = T_C + \Psi_{JT} \star P_{LOSS}$

where

- T<sub>PCB</sub> is the board temperature measured by an IR camera or fiber optic probe

- T<sub>c</sub> is the UCC24624 case-top temperature measured with a thermocouple or some other instrument

- $\Psi_{JB}$  is the junction-to-board characterization parameter

- $\Psi_{JT}$  is the junction-to-top characterization parameter from the Thermal Information table

Note that using  $\Psi_{JB}$  and  $\Psi_{JT}$ , instead of the junction-to-ambient thermal resistance  $R_{\Theta JA}$ , can greatly improve the accuracy of the junction temperature estimation, they are experimentally derived by assuming that the amount of energy leaving the IC will be similar in both the testing environment and the application environment.

As long as the recommended layout guidelines are observed, with  $\Psi_{JB}$  = 52.8°C/W and the max T<sub>J</sub> = 125°C, the maximum PCB temperature can be estimated as

$$T_{PCB} = T_{J} - \Psi_{JB} \times P_{LOSS} = 125 - 52 . 8 \times 0 . 6222 = 92 . 1^{\circ}C$$

If external resistors are used, a portion of the power loss is incurred on the external resistors and the power loss in UCC24624 could be lower, allowing the device to operate at a higher temperature environment. For example, if  $R_{gate} = 2.2 \Omega$ , the total power loss  $P_{DRV}$  is decreased to 403 mW, and it can support the maximum PCB temperature of 103.7°C.

www.ti.com

(10)

# 3 Turn-off Threshold Adjustment

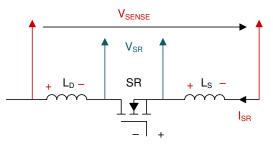

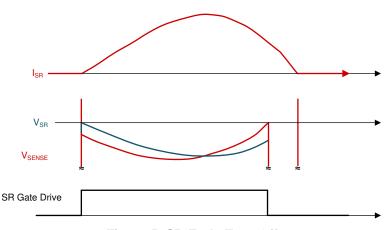

As Figure 4 shows, the V<sub>DS</sub> voltage of the SR MOSFET sensed by UCC24624 V<sub>SENSE</sub> is the combination of the MOSFET on-state resistor voltage drop VSR, together with the voltage drops on parasitic inductors  $L_D$  and  $L_S$ . Thus, V<sub>SENSE</sub> can be represented with Equation 10:

$$\mathsf{V}_{_{\mathsf{SENSE}}} = -\left[\mathsf{I}_{\mathsf{SR}} \times \mathsf{R}_{\mathsf{DS}(\mathsf{ON})} + (\mathsf{L}_{\mathsf{D}} + \mathsf{L}_{\mathsf{S}}) \times \frac{\mathsf{d}\mathsf{I}_{\mathsf{SR}}}{\mathsf{d}\mathsf{t}}\right]$$

During the SR current falling edge, the fast current slope (di/dt) creates a significant negative voltage drop across the package inductance and offset  $V_{SR}$ , causing the SR controller to detect a smaller voltage drop and turn off the SR MOSFET early, as Figure 5 shows.

Figure 4. UCC24624 Sensed Voltage

Figure 5. SR Early Turn Off

To compensate the effect of parasitic inductances, the turn-off threshold of the UCC24624 device is 10.5 mV by default, instead of typically being set as a negative threshold, since the positive voltage is always expected at zero SR current. However, with different packages for the MOSFET, this parasitic inductance could vary from 2 nH to 10 nH, and some applications might induce more parasitic inductors due to undesirable layout, so it is required to further increase the turn-off threshold to accommodate higher parasitic. As demonstrated in the *UCC24624 Dual-Channel Synchronous Rectifier Controller for LLC Resonant Converters Data Sheet*, by connecting a resistor R<sub>offset</sub> from the VSS pin to the SR MOSFET source, the voltage drop across the external resistor increases the turn-off threshold. In this way, the desired turn-off threshold V<sub>THOFF</sub> can be calculated as:

$$V_{THOFF} = 10.5 \text{ mV} + 330 \mu \text{A} \times \text{R}_{offset}$$

(11)

5

Normally, less than 70-mV offset is recommended for TO-220 MOSFET packages. Due to different layout conditions in actual applications, it is recommended to adjust the R<sub>offset</sub> value to maximize the SR MOSFET conduction time.

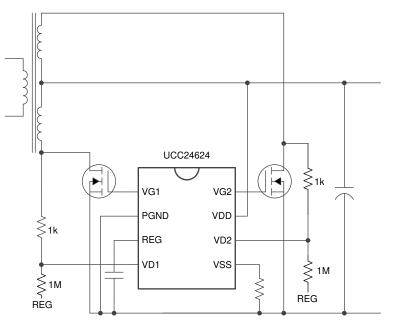

In some applications, some users would like to use a lower turn-off threshold than 10.5 mV. It is also possible to achieve it with the example circuits shown in Figure 6.

Light Load Operation

www.ti.com

Figure 6. Decreasing Turn-off Threshold Circuit

In Figure 6, a 1-M $\Omega$  resistor is added from REG pin to VD pins. When the SR MOSFET is on, its drain voltage is close to 0 V, since the REG pin voltage is well regulated to 11 V, the added 1-M $\Omega$  resistor creates an offset current of approximately 11 µA from REG pin. In this example, another 1-k $\Omega$  resistor is added from MOSFET drain to the UCC24624 VD pin. The 11-µA current creates an 11-mV offset voltage on the 1-k $\Omega$  resistor, which changes the turn-off threshold from 10.5 mV to -0.5 mV. Using this circuit with different resistor values can create other turn-off thresholds. When the SR turns off, the high voltage appears on SR drain pin. This will not cause current flowing into the UCC24624 VD pin. However, because this voltage is much higher than the 11-V REG pin voltage, this could cause a current flowing from SR drain to REG. A diode can always be inserted to prevent the current but it adds extra system cost. To minimize this current, it is desired to keep the 1-M $\Omega$  resistor with relative high value.

# 4 Light Load Operation

In some designs, LLC enters PWM mode with reduced duty cycle or burst mode to save the switching loss during light load. The UCC24624 device detects the average operation frequency of channel 1 SR MOSFET and enters standby mode operation with no gate driver signals. It also reduces its current consumption to minimize the overall control loss. The light load mode detection interval is 7.5ms. If the detected average switching frequency drops below 9 kHz, the UCC24624 enters standby mode. Once it is detected more than 15.6 kHz, the SR driving is enabled again.

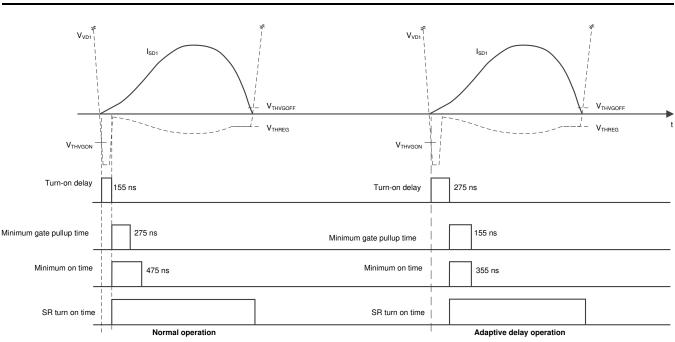

Note that for the purpose of noise immunity, after the SR is turned on, a minimum on-time blanking of 475 ns is implemented in the UCC24624. The SR keeps conducting regardless of its drain-to-source voltage. During light load operation, the duty cycle of LLC primary side might decease so much that there is not enough energy delivered to the secondary side. Thus, the minimum on-time of the UCC24624 might cause the SR MOSFETs to conduct longer than it is needed and induce a negative current from the output.

Considering such conditions, adaptive turn-on delay scheme takes effect to resolve the issue: UCC24624 monitors the SR conduction time all the time, and once its conduction time becomes less than the minimum on-time, UCC24624 increases the turn-on delay from 155ns to 275ns. Meanwhile, the minimum on-time decreases to 355ns to support light load operation, as shown in Figure 7. Additionally, the longer turn-on delay can provide better DCM ring rejection capability to avoid false turn on due to SR parasitic capacitance. Meanwhile, the minimum gate pullup time also decreases from 275 ns to 155 ns. Therefore, the final VGS amplitude could be lower than its value at heavy load conditions This further helps to reduce the switching loss during light load.

www.ti.com

Figure 7. Adaptive Turn-on Delay

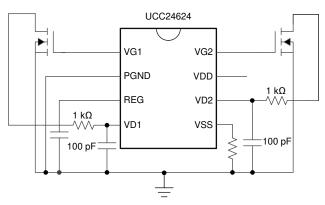

Another solution to further increase the turn-on delay and improve the noise immunity is to add an RC filter on VD pins, as Figure 8 shows. Note that the value of this RC filter should be carefully selected, since the added turn-on delay also increases the conduction loss during normal operation. A 1-k $\Omega$  resistor and < 100-pF capacitor are suggested. Besides, during some noise conditions, due to large parasitic inductances, the RC filter can also help absorb voltage spikes or negative current, so as to avoid the effect for the internal parasitic diode of UCC24624.

Figure 8. Adding RC Filter at VD Pins

# 5 References

- Texas Instruments, Fundamentals of MOSFET and IGBT Gate Driver Circuits Application Report

- Texas Instruments, Semiconductor and IC Package Thermal Metrics Application Report

- Texas Instruments, UCC24624 LLC gated driver evaluation Module

- Texas Instruments, TIDA-010081: >95% Efficiency, 1-kW analog control AC/DC reference design for 5G telecom rectifier reference design

- Texas Instruments, TIDA-010038: 94% Peak efficiency, 150W norm, 240W peak industrial AC/DC power supply with CC/CV reference design

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated