# TI TECH DAYS

# Solving Common Buck Converter Design Challenges

**Rich Nowakowski**

**Texas Instruments**

# Agenda

- 1. Reducing voltage ripple for signal chain power.

- 2. Achieving high output voltage accuracy for FPGA power.

- 3. Understanding impact of thermal SOA.

- 4. Smaller size with faster switching frequencies.

- 5. Control mode types.

- 6. Using WEBENCH® to address the latest buck converter design challenges.

# **Challenge #1: low noise for signal chain power**

# Achieving low-ripple output voltage noise without a linear regulator, using higher current DC/DC converters.

#### LDO drawbacks compound at higher currents:

- Cost penalty, but some designers may not care.

- Thermal penalty.

- Efficiency penalty.

- Size penalty.

- Paralleling LDOs is possible, but complicated.

| Attribute                | 400-kHz Design<br>with LDO | 4-MHz Design        | Advantage      |  |

|--------------------------|----------------------------|---------------------|----------------|--|

| Size                     | 640 mm <sup>2</sup>        | 195 mm <sup>2</sup> | 4-MHz design   |  |

| Full-load<br>efficiency  | 77.2%                      | 86.8%               | 4-MHz design   |  |

| Power loss               | 2.06 W                     | 1.1 W               | 4-MHz design   |  |

| IC temperature           | 57.8°C + 51.6°C            | 37.1°C              | 4-MHz design   |  |

| Transient over-<br>shoot | 146 mV                     | 35.5 mV             | 4-MHz design   |  |

| Ripple voltage           | 11.5 mV                    | 6.7 mV              | 4-MHz design   |  |

| Output voltage<br>noise  | 14.9 µV                    | 135 µV              | 400-kHz design |  |

| Solution cost            | \$9.55 at 1 Ku             | \$7.50 at 1 Ku      | 4-MHz design   |  |

• 12V to 1.8V @ 4A

No additional noise reduction techniques employed

# Low noise means different things to different designers

| Low noise<br>problem                                | Specific need                                                                                                                           | Market                                                 | IC solution                                                                                                                   | Package solution                                      | PC board solution                                                                   | System solution    |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|

| Low output<br>voltage ripple<br>(µV <sub>PP</sub> ) | High speed ADC and AFE<br>systems need to reduce the<br>output ripple to ~200µV to<br>maintain high ENOB (effective<br>number of bits). | Wireless<br>Infrastructure,<br>Test and<br>Measurement | 2 <sup>nd</sup> loop compensation, Higher Fsw<br>(reduced inductor ripple), Spread<br>Spectrum                                | Hotrod packaging,<br>RLF with integrated<br>input cap | Ferrite output filter,<br>post regulate with<br>LDO, multiple caps to<br>reduce ESL |                    |

| Phase noise<br>(μV <sub>RMS</sub> )                 | Clocking systems need low<br>phase noise from from 100Hz<br>to 100kHz 20uV <sub>RMS</sub> or less<br>output noise voltage               | Wireless<br>Infrastructure,<br>Test and<br>Measurement | optimize bandgap and optimize<br>error amplifier design for low<br>intrinsic device noise                                     |                                                       |                                                                                     |                    |

| 1/f noise                                           | Thermal and flicker noise can<br>cause errors in low frequency<br>bands                                                                 | Test and<br>Measurement                                | Reduce bandgap noise                                                                                                          |                                                       |                                                                                     |                    |

| Power supply rejection                              | ADC requires ~40dB of input<br>power supply rejection to<br>minimize cross coupling noise<br>from the input rails                       | Test and<br>Measurement                                | IC may meet the spec                                                                                                          |                                                       | Additional input<br>filtering                                                       |                    |

|                                                     | Meet FCC Unintentional<br>Radiator Limits                                                                                               | Radio and TV receivers, PE                             |                                                                                                                               | Hotrod packaging                                      |                                                                                     |                    |

| Electromagnetic<br>interference                     | Meet FCC Intentional Radiator<br>Limits                                                                                                 | Wireless<br>(WLAN and BT,<br>etc) devices              | Adjustable slew rate and/or<br>optimized gate drive, Spread<br>Spectrum                                                       | Hotrod packaging,<br>RLF with integrated<br>input cap | Good board layout to<br>minimize coupling<br>power supply noise                     | Metal<br>shielding |

| (EMI)                                               | Meet CISPR 25 Class 5                                                                                                                   | Automotive<br>applications                             | Adjustable slew rate and/or<br>optimized gate drive, Spread<br>Spectrum, allow SYNC to external<br>clock with Spread Spectrum | Hotrod packaging,<br>RLF with integrated<br>input cap | Chokes to the power<br>supply input                                                 | Metal<br>shielding |

### Low noise: tips to reduce noise conduction to the load

- High self-resonant frequency for inductor.

- Place vias for bypass capacitors between terminals.

- Keep non-ground vias spaced wide enough to allow ground planes to flow between vias

- Ramp capacitors up and down from inductor to load: 1.0uF, 2.2uF, 4.7uF, 10uF, 22uF, 47uF, 100uF, 47uF, 22uF, 10uF, 4.7uF, 2.2uF, 1.0uF.

- Mix capacitor values with 2:1 or 3:1 values and different packages.

- Use Multi-phase converter.

- Synchronized and phase-shifted multi-phase architecture increase ripple frequency and reduce ripple currents.

- Use different boot resistors and snubbers on each phase to spread noise spike frequencies.

- Use Second-stage Output Filter.

- Ferrite Bead or soft-resonating inductor between first and second stage.

- DC regulation feedback after second filter, with feed-forward capacitor from first stage to minimize loop impact of 2-stage filter.

## Low noise: two-stage output filter example

#### TPS54618-Q1 example:

- 5  $V_{\rm IN}$  to 3.3  $V_{\rm OUT}$  @ 5 A

- Fsw = 750 kHz

- Cout = 22 uF 6.3 V X5R ceramic

- L = 1 uF

- Ripple is 39 mV (~1%)

- Target ripple: 1 mV ripple

| · · · · · · · |      | · · · · · · · · ·  | Rdam              | <b>0 1 1 1</b> |               |

|---------------|------|--------------------|-------------------|----------------|---------------|

| VIN           | L1   | Rdcr1 0056         | L2                | Rdcr2 .0(      | 052<br>Vout   |

|               | 1u 1 |                    | 220n              |                |               |

|               |      | C1                 |                   |                |               |

|               |      | 7!2u               |                   |                | 65 <b>u</b>   |

| V1            |      | GeranC1esr<br>.003 | > 1 1 1 1 1 1 1 1 |                | C2esr<br>.003 |

|               |      |                    |                   |                |               |

Step #1:

- Make the second-stage capacitor 4x to 10x bigger than the first-stage capacitor. Choose 100 uF X5R.

Step#2

- Choose new resonant frequency 150 kHz. Rule of thumb (3-5x higher than loop cross-over frequency).

- Calculate second stage inductor value (L2) using equation. Choose 220 nH.

#### Step #3

Damp the second filter resonance properly. That means carefully choosing the ESR of the second inductor.

#### Step #4

• Re-compensate the loop.

$$F, res2 = \frac{1}{(2\pi * \sqrt{L2*Cs})}$$

, where  $Cs = \frac{1}{\frac{1}{C_1} + \frac{1}{C_2}}$

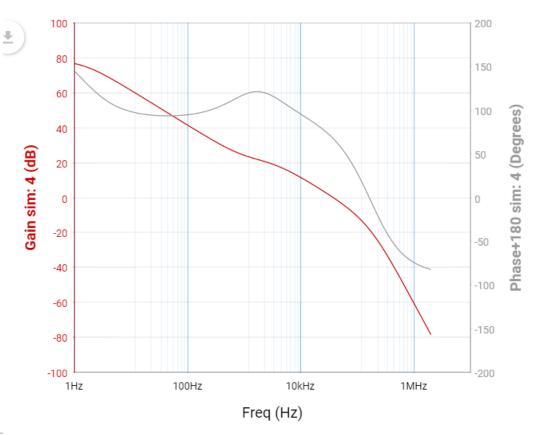

# **Two-stage filter waveform results**

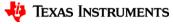

- Transfer function before and after the second LC shown. There are two resonances: 25 kHz and 150 kHz.

- Simulating the power-stage gain and phase shows the output pole at 6.5 kHz.

- Measured loop response is also shown.

- <1mV ripple achieved.</li>

# Low noise: WEBENCH example

- Create design.

- Click on "Add Input EMI Filter" from design suggestions.

- Choose "Noise Standard" and "Noise Class".

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |                     |                          |                |                        |                       | NEW DESIGN       | N MY DE       | ESIGNS ( |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|---------------------|--------------------------|----------------|------------------------|-----------------------|------------------|---------------|----------|

| Customize LM5117QPMH/NOPB - 8\<br>Input: DC8V-15V Output: 3.3Vat 10 A Temp: 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |     |                     | SELEC                    | т              | CUSTOMIZE              | SIMUL                 | АТЕ              | EXPORT        | À        |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SCHEMATIC               | PCB LAYOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BILL OF MATERIALS                    |     |                     |                          |                |                        |                       |                  |               |          |

| Efficiency: 93.8%<br>BOM Cost: \$6.10<br>Footprint: 685 mm <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Click a component to fi | nd out more informati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | on or select an alternate part.      |     |                     |                          |                |                        |                       | Q                | ରୁ ବ୍         | Ŧ        |

| CHARGE OPTIMIZATION Configuration Options In the text free 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | *                       | Or Control of Control |                                      |     |                     |                          |                |                        |                       | - Cang<br>Server | <b>O</b> rect |          |

| Backle leak Fes     back de leak     Fes     back de leak     Fes     back de leak     for     max     for     fo |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | lications. All passives and other co |     | this design may not | t be qualified for Autom | notive applica | ations. The user is re | quired to verify that | all components   | in the design | meet     |

| REDESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OPERATING VALUES        | CHARTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |     |                     |                          |                |                        |                       |                  |               |          |

| Design Suggestions Add Input EMI Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Vin (V)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V lout (A)                           | • 1 | 0 A                 | RECALCULATE              |                |                        |                       |                  |               |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Categories              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      |     |                     |                          |                |                        |                       |                  |               |          |

#### Low noise: resources

Application reports:

- Reducing output ripple and noise with the TPS84259 module.

- Not all jitter is created equal

- Reduce buck-converter EMI and voltage stress by minimizing inductive parasitics.

- <u>Reducing noise on the output of a switching regulator</u>.

- Understanding and managing buck regulator output ripple

Technical articles:

- Power tips: Designing a two-stage LC filter TPS54678 (TPS54618-Q1).

- Design a second-stage filter for sensitive applications LMZ23601.

White papers:

• <u>Simplify low-EMI design with power modules</u>.

Reference designs:

• Paralleling multiple LDOs (14A) reference design.

### **Challenge #2: voltage regulation accuracy**

# As process technology advances, processor voltage requirements are lower and require high accuracy.

#### More Expensive Virtex Ultrascale+

Recommended Operating Conditions (16 nm)

| Symbol                             | Description <sup>1, 2</sup>                                                     | Min   | Тур   | Мах   | Units |

|------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-------|

| FPGA Logic                         |                                                                                 |       |       |       |       |

| VCCINT                             | Internal supply voltage                                                         | 0.825 | 0.850 | 0.876 | V     |

|                                    | For -2LE (V <sub>CCINT</sub> = 0.72V) devices: internal supply voltage          | 0.698 | 0.720 | 0.742 | V     |

|                                    | For -3E devices: internal supply voltage                                        | 0.873 | 0.900 | 0.927 | V     |

| V <sub>CCINT_IO</sub> <sup>3</sup> | Internal supply voltage for the I/O banks                                       |       | 0.850 | 0.876 | V     |

|                                    | For -2LE (V_{CCINT} = 0.72V) devices: internal supply voltage for the I/O banks | 0.825 | 0.850 | 0.876 | V     |

|                                    | For -3E devices: internal supply voltage for the I/O banks                      | 0.873 | 0.900 | 0.927 | ٧     |

| V <sub>CCBRAM</sub>                | Block RAM supply voltage                                                        | 0.825 | 0.850 | 0.876 | V     |

|                                    | For -3E devices: block RAM supply voltage                                       | 0.873 | 0.900 | 0.927 | V     |

| VCCAUX                             | Auxiliary supply voltage                                                        | 1.746 | 1.800 | 1.854 | V     |

DS923 - Virtex UltraScale+ FPGA Data Sheet: DC and AC Switching Characteristics (v1.15)

| VCCINT  | ±3% |

|---------|-----|

| VCCBRAM | ±3% |

| VCCAUX  | ±3% |

#### Cheaper Spartan 7

#### **Recommended Operating Conditions (28 nm)**

| Symbol                             | Description                                             | Min  | Тур  | Max   | Units |

|------------------------------------|---------------------------------------------------------|------|------|-------|-------|

| FPGA Logic                         |                                                         |      |      |       |       |

| V <sub>CCINT</sub> <sup>(3)</sup>  | For -2 and -1 (1.0V) devices: internal supply voltage.  | 0.95 | 1.00 | 1.05  | v     |

| VCCINT                             | For -1L (0.95V) devices: internal supply voltage.       | 0.92 | 0.95 | 0.98  | v     |

| VCCAUX                             | Auxiliary supply voltage.                               | 1.71 | 1.80 | 1.89  | v     |

| V (3)                              | For -2 and -1 (1.0V) devices: block RAM supply voltage. | 0.95 | 1.00 | 1.05  | v     |

| V <sub>CCBRAM</sub> <sup>(3)</sup> | For -1L (0.95V) devices: block RAM supply voltage.      | 0.92 | 0.95 | 0.98  | v     |

| V <sub>CCO</sub> <sup>(4)(5)</sup> | Supply voltage for HR I/O banks.                        | 1.14 | -    | 3.465 | v     |

DS189 - Spartan-7 FPGAs Data Sheet: DC and AC Switching Characteristics (v1.9)

| VCCINT  | ±3%, ±5% |

|---------|----------|

| VCCBRAM | ±3%, ±5% |

| VCCAUX  | ±5%      |

### Voltage regulation accuracy: sources of error

#### Sources of output voltage error:

- Routing distance and trace losses of the circuit board.

- DC/DC converter:

- Temperature swings.

- Input voltage variations.

- Feedback voltage accuracy.

- Ratio of the resistor divider & tolerance of resistors.

- Voltage ripple.

- Load transients.

### Voltage regulation accuracy: DC/DC converter datasheet

#### Choose DC/DC with $V_{FB} \le 1\%$ accuracy

#### Cheaper TPS568230 17 V / 8 A

$T_J$  =-40°C to 125°C,  $V_{VIN}$  = 12 V, unless otherwise noted

| PARAMETER   |            | TEST CONDITION               | MIN | TYP | MAX | UNIT |

|-------------|------------|------------------------------|-----|-----|-----|------|

| FEEDBACK VO | LTAGE      |                              |     |     | ·   |      |

| N/          | FR voltage | T <sub>J</sub> = 25°C        | 594 | 600 | 606 | mV   |

| VFB         | FB voltage | $T_{\rm J}$ = -40°C to 125°C | 592 | 600 | 611 | mV   |

#### More expensive TPS54824 17 V / 8 A

#### $T_J$ = -40°C to 150°C, VIN = 4.5 V to 17 V (unless otherwise noted)

|                 | PARAMETER            | TEST CONDITIONS              | MIN | TYP | MAX | UNIT |

|-----------------|----------------------|------------------------------|-----|-----|-----|------|

| FB              |                      |                              |     |     |     |      |

| V               | Dogulated ER voltage | T <sub>J</sub> = 25°C        | 596 | 600 | 604 | m∨   |

| V <sub>FB</sub> | Regulated FB voltage | $T_{\rm J}$ = -40°C to 150°C | 595 | 600 | 605 | m∨   |

- Consider line and temperature changes.

- Avoid the 'front page' accuracy number.

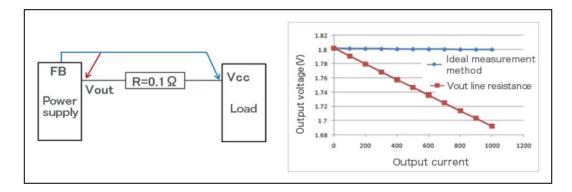

### Voltage regulation accuracy: remote sense

- Ohm's Law: V = I x R

- Line resistance cannot be eliminated, only reduced or managed.

- Waveforms with and without remote sensing.

- Notice voltage drop during load transient w/o remote sense.

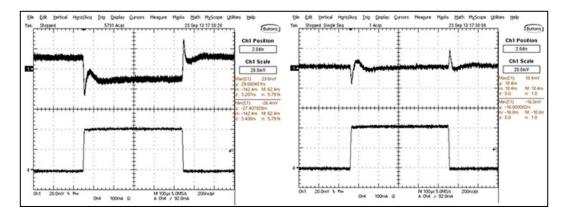

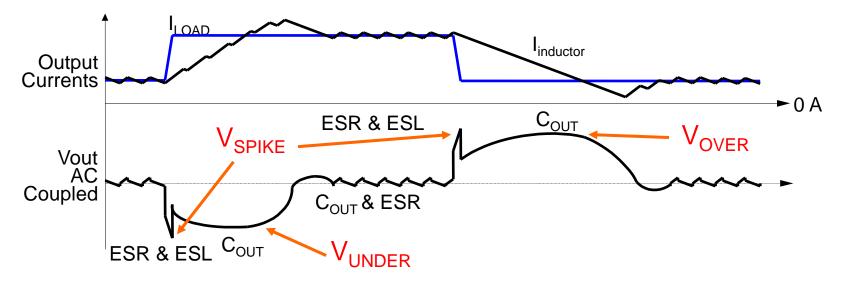

# Maintaining voltage accuracy during load transient

- Transient from light load to heavy load creates an under shoot.

- PWM delivers maximum duty until the control loop catches up.

- Output capacitor supplies load until inductor catches up.

- Similarly when load changes from heavy load to light load, output will overshoot.

- Duty cycle goes to zero,  $V_L = V_{O.}$

### Voltage regulation accuracy: ±3% & ±5% example

$$V_{\text{UNDER}} = \frac{I \times dt}{C}$$

where  $I = \frac{I_{\text{STEP}}}{2}$  (Avg. current)

$$dt = \frac{L \times dI}{D_{MAX} \times V_L} \qquad \text{where} \qquad dI = I_{\text{STEP}}, V_L = V_{\text{IN}} - V_C$$

$$V_{\text{OVER}} = \frac{L \times I_{\text{STEP}}^2}{2 \times C_{\text{O}} \times V_{\text{O}}} \text{ (V_{L} is Vout) } V_{\text{UNDER}} = \frac{L \times I_{\text{STEP}}^2}{2 \times C_{\text{O}} \times D_{\text{max}} \times (V_{\text{IN}} - V_{\text{O}})}$$

$$C_{O} > \frac{L \times I_{STEP}^{2}}{2 \times V_{OVER} \times V_{OUT}} \qquad C_{O} > \frac{L \times I_{STEP}^{2}}{2 \times V_{UNDER} \times D_{max} \times (V_{IN} - V_{OUT})}$$

#### Example: 4-A TPS62136

- Transient: 0.8-A to 3.2-A load step

- Input voltage: 12 V

- Output voltage: 1.8 V

- Inductor: 1.5 uH

- V<sub>under</sub>: 1.746 V, 1.71 V

- V<sub>over</sub>: 1.854 V, 1.89 V

Co for  $\pm 5\%$  is 26 uF Co for  $\pm 3\%$  is 44 uF

# Voltage regulation accuracy: WEBENCH example

- Transient: 1-A to 6-A load step

@ 1A/us

- Input voltage: 12 V

- Output voltage: 0.85 V

- Inductor: 470 nH

#### 3% 5%

- V<sub>under</sub>: 0.825 V, 0.808 V

- V<sub>over</sub>: 0.876 V, 0.893 V

#### Use WEBENCH to get 1% ripple and 3% transient with TPS54824.

#### Create a new DC/DC power design

WEBENCH<sup>®</sup> Power Designer creates customized power supply circuits based on your requirements. The environment gives you end-to-end power supply design capabilities that save you time during all phases of the design process. Learn more

| TPS54824 | × |

|----------|---|

|          |   |

#### Great! We found TPS54824 and auto-filled the inputs for you

| Supply type is      |            |                 |                | Vout *<br>0.85  | V | lout Max *<br>6 |  |

|---------------------|------------|-----------------|----------------|-----------------|---|-----------------|--|

| DC AC               |            |                 |                | (0.6 - 12)      |   | (0 - 8)         |  |

| Vin Min *           |            | Vin Max *       |                | Isolated Output |   |                 |  |

| 12                  | V          | 12              | V              |                 |   |                 |  |

| (4.5 - 17)          |            | (4.5 - 17)      |                |                 |   |                 |  |

| Advanced            |            |                 | ~              | Advanced        |   |                 |  |

|                     |            |                 |                |                 |   |                 |  |

| Design Cor          | sideratio  | on              |                |                 |   |                 |  |

| I want my design to |            |                 |                |                 |   |                 |  |

| Balanced Lo         | w Cost Hig | h Efficiency Sr | nall Footprint |                 |   |                 |  |

|                     |            |                 |                |                 |   |                 |  |

|                     |            |                 |                |                 |   |                 |  |

## **Voltage regulation accuracy: resources**

#### Application Reports:

- <u>Achieving Better than 1% Output Voltage Accuracy with 40A TPS546D24A, 20A</u> <u>TPS546B24A, & 10A TPS546A24A</u>

- <u>Remote Sensing for Power Supplies</u>

- Power Supply Design Considerations for Modern FPGAs

- <u>Calculating Output Capacitance to Meet Transient and Ripple Requirements of Integrated</u>

<u>POL</u>

Technical Articles:

<u>"Kollman Power Tip #18" voltage dividers and Vout accuracy</u>

On-line training:

How to meet FPGA's DC voltage accuracy and AC load transient specification

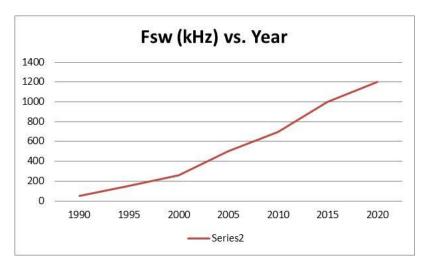

### **Challenge #3: higher switching frequency to reduce area**

# Achieve higher power density by increasing the DC/DC converter's switching frequency.

- Board space is valuable.

- Suppliers are releasing faster DC/DC converters that claim to save space.

- How much space is really saved?

- What are the trade-offs?

# Higher switching frequency: considerations

#### Switching frequency considerations:

- Minimum on-time.

- Pulse-skipping.

- Efficiency and power losses.

- LC filter area.

- Voltage ripple.

- Transient response.

- Component cost.

# Higher switching frequency: minimum on-time

Check the minimum controllable on-time in the datasheet, not the maximum oscillator frequency!

#### 100-V synchronous buck DC/DC controller with wide duty cycle

| LM5146-Q1 PWM Control |                              | Min | Тур | Max | unit |

|-----------------------|------------------------------|-----|-----|-----|------|

| t <sub>ON(MIN)</sub>  | Minimum controllable on-time |     | 40  | 60  | ns   |

| t <sub>OFF(MIN)</sub> | Minimum off-time             |     | 140 | 200 | ns   |

| DC <sub>100kHz</sub>  | Maximum duty cycle           | 98% | 99% |     |      |

| DC <sub>400kHz</sub>  |                              | 90% | 94% |     |      |

*Min.* Duty Cycle = *Min.* On time x Switching Frequency 0.06 = 60 ns x 1 MHz

Examples at 1 MHz:  $0.8 V_{OUT} = V_{INMAX} \times 0.06; V_{INMAX} = 13 V$  $3.3 V_{OUT} = V_{INMAX} \times 0.06; V_{INMAX} = 55 V$  Pulse-skipping happens when the DC/DC converter cannot extinguish the gate drive pulses fast enough to maintain the desired duty cycle.

- Converter will still regulate, but:

- Ripple voltage increases due to the pulses being further apart.

- Frequency is no longer predictable.

- Current limit may no longer work since the IC cannot respond in time.

- Control loop may be unstable. Transient response is also affected.

- Reduce Fsw, lower the input voltage, or pick a different part.

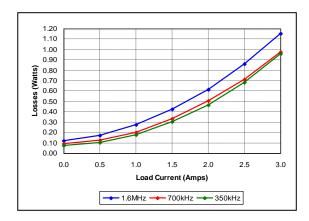

# Higher switching frequency: power loss & efficiency

#### Design example (TPS54388C-Q1):

- 5  $V_{IN}$ , 1.8  $V_{OUT}$ , 3 A, 20-mV ripple, 1A<sub>p-p</sub>

- Total power loss 350 kHz: 0.95 W

- Total power loss 1.6 MHz: 1.15 W

#### **Power losses:**

- FET driving loss (Qg \* V \* Fsw)

- FET switching loss f(Vin, lout, Ton/off, Fsw)

- FET resistance ( I<sup>2</sup> \* Rds(on))

- Inductor loss (I<sup>2</sup> \* DCR + Core losses):

- Capacitor loss (I<sub>RMS</sub><sup>2</sup> \* ESR)

- IC loss (lq)

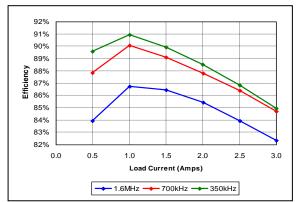

# Higher switching frequency: transient & ripple

$L = V * \Delta I / \Delta t$   $L \ge Vout * (1-D)/(\Delta I \times Fs)$  $\Delta I = 1-A \text{ peak to peak}$

- 350 kHz: L ≥ 3.3 uH → Choose 3.5 uH (84mm<sup>2</sup>)

- 1.6 MHz: L ≥ 0.7 uH → Choose 1.0 uH (41mm<sup>2</sup>)

- 350 kHz: C ≥ 36 uF → Choose 47 uF 1206 (5mm<sup>2</sup>)

- 1.6M Hz: C ≥ 7.9 uF → Choose 10 uF 0603 (1.4mm<sup>2</sup>)

Space savings: 45 mm<sup>2</sup>

Not counting keep-out

# Higher switching frequency: WEBENCH example

#### WEBENCH<sup>®</sup> POWER DESIGNER =

Q LM61

VIEW DESIGN LM61460

$\times$

А

$\sim$

#### Create a new DC/DC power design

Customer using LM61460

- $V_{IN}=24$ ,  $V_{OUT}=3.3$   $I_{OUT}=5$ Α

- What are some of the ways we can use WEBENCH to reduce the overall size of our design?

#### WEBENCH® Power Designer creates customized power supply circuits based on your requirements. The environment gives you end-to-end power supply design capabilities that save you time during all phases of the design process. Learn more

| 460 |  |  |  |

|-----|--|--|--|

|     |  |  |  |

Output Input lout Max ? Supply type is 3.3 V 5 (1 - 34.2) Isolated Output Vin Max \* 24 V 24 V Advanced  $\sim$ Advanced  $\sim$ **Design Consideration** I want my design to be

# Balanced Design Parameters

Great! We found LM61460 and auto-filled the inputs for you

# **Higher switching frequency: WEBENCH example**

#### **Optimization options**

- Beginning size with "balanced" design=146 mm<sup>2</sup>

- Efficiency 85.7%

- Now let's click

"Change

Optimization"

|            | Small Footprint Design | Low Cost Design | Balanced Design | High Efficiency Design |

|------------|------------------------|-----------------|-----------------|------------------------|

| Efficiency | 81.2 %                 | 84.1 %          | 85.7 %          | 88.4 %                 |

| Bom Cost   | \$3.74                 | \$4.74          | \$3.82          | \$4.72                 |

| Footprint  | 130 mm²                | 138 mm²         | 146 mm²         | 181 mm²                |

|            | SELECT                 | SELECT          | SELECT          | SELECT                 |

# **Higher switching frequency: resources**

**Application Notes:**

Benefits of a Multiphase Buck Converter

**Technical Articles:**

- <u>Trade-Offs In Switching High-Input-Voltage Step-Down</u>

<u>Converters at High Frequencies</u>

- <u>Choosing the optimum switching frequency of your DC/DC</u> <u>converter</u>

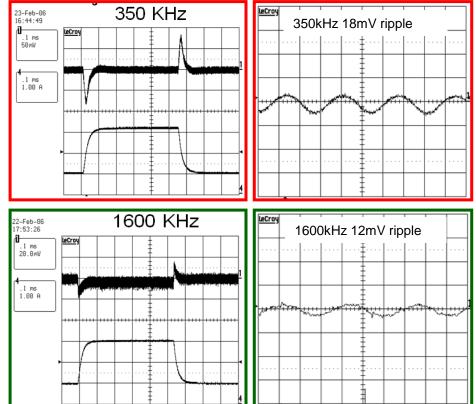

### Challenge #4: safe operating area

Will the small QFN package of the DC/DC converter or the power module handle the rated high current?

- Safe Operating Area (SOA) represents operating conditions where the maximum electrical and thermal rating of the component will not be exceeded.

- Recommended operating points are always less than the SOA limits.

- Cooler is always better for reliability.

# **SOA: using SOA curves**

- SOA curves tell the designer:

- Desired current at the desired Ta.

- Airflow is needed.

- How much margin or reserve is available.

- The farther the operating point is from the SOA boundary, the cooler the supply will operate.

- SOA curves do *not* represent thermal shutdown points. Some products will not reach shutdown until pushed past SOA limits.

- Catalog current rating may be rated under different conventions.

# **SOA: comparison**

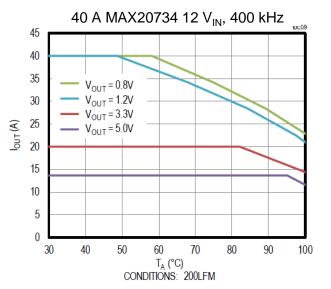

• 22A @ 84C Ta, no airflow, 30A @ 84C, 200LFM

EVM board results shown with 4 layers of 2 oz copper

4.15x9 mm QFN JEDEC  $\theta_{JA} = N/A °C/W$ EVM  $\theta_{JA} = 12°C/W$

• 40A @ 84C Ta, no airflow

EVM board results shown with 4 layer, 2 oz copper

5x7 mm Clip QFN JEDEC  $\theta_{JA} = 28.9^{\circ}$ C/W EVM  $\theta_{JA} = 8.1^{\circ}$ C/W

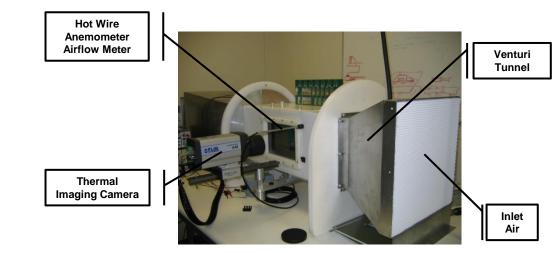

# SOA: rough estimation using SOA and $\theta_{JA}$

Output Current (A)

D003

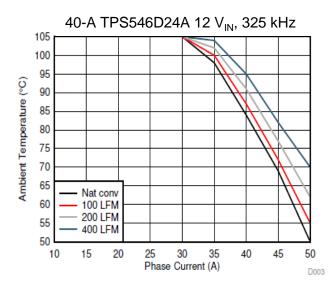

#### **TPSM84824 example:**

- 12 V<sub>IN</sub>, 3.3V<sub>OUT</sub>, 8A, 1 MHz

- $T_A = 70^{\circ}C$ , no airflow

- $\theta_{JA} = 12^{\circ}C/W$  (4 layer, 2 oz copper-100 mmx100 mm)

Will it work?

• SOA curve inspection passes 70°C T<sub>A</sub> with 5°C margin

What temperature will the module heat up to?

- 8 A @ 3.3 V dissipates 2.7W

- $2.7 \text{ W} \times 12^{\circ} \text{C/W} = 32^{\circ} \text{C}$  temp rise above ambient

- Module junction temperature will be ~102°C

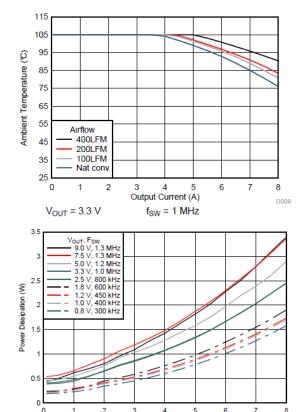

# SOA: what does WEBENCH say?

1.2

1

$(1.2 \cdot 10)$

(0.8 - 8 )

#### **TPSM84824** example:

- 12V<sub>IN</sub>, 3.3 V<sub>OUT</sub>, 8A, 1 MHz

- $T_{A} = 70^{\circ}C$ , no airflow

- $\theta_{IA} = 12^{\circ}$ C/W (4 layer, 2 oz copper-100 mmx100 mm)

Will it work?

Oh NO!

Let's try 65°C

SUCCESS!

Takeaway, We are very close to the edge with this design.

**Application Reports:**

- <u>Method of Graphing Safe Operating Area (SOA) Curves for DC-DC</u>

<u>Converters</u>

- <u>Understanding the thermal-resistance specification of DC/DC converters with</u> integrated power MOSFETs

- How to Evaluate Junction Temperature Properly with Thermal Metrics

- <u>Improving the Thermal Performance of a MicroSiP™ Power Module</u>

### **Challenge #5: control mode confusion**

#### There are a lot of control mode architectures to chose! Which one is best for my application?

| 2300 | 0.6 | Dynamic Voltage Scaling, Enable, Frequency Synchronization, Light Load<br>Efficiency, Phase Interleaving, Power Good, Synchronous Rectification,<br>UVLO Adjustable                         | Current<br>Mode |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 580  | 0.4 | Enable, Synchronous Rectification                                                                                                                                                           | D-CAP2          |

| 580  | 0.4 | Enable, Light Load Efficiency, Synchronous Rectification                                                                                                                                    | D-CAP2          |

| 2000 | 4.3 | Adjustable Current Limit, Enable, Frequency Synchronization, N/A, Over<br>Current Protection, Phase Interleaving, Power Good, Pre-Bias Start-Up,<br>Remote Sense, Synchronous Rectification | Current<br>Mode |

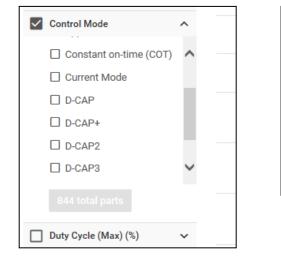

Control mode information located in the parametric search.

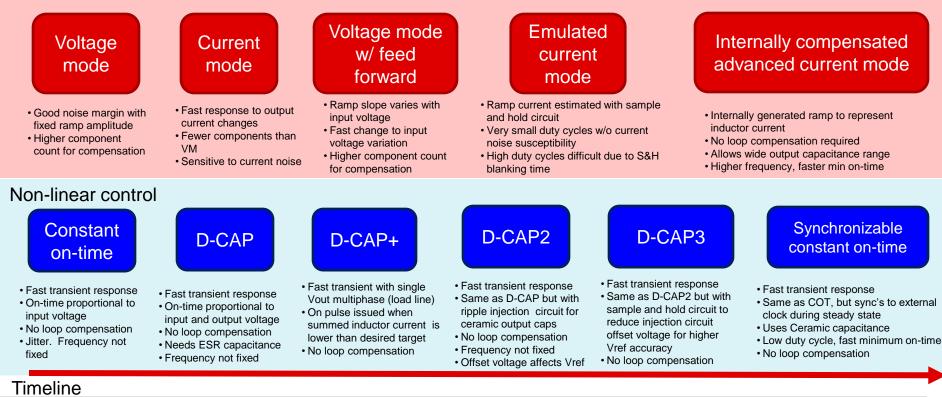

## **Control mode: history – buck converters and controllers**

#### Linear control

#### 🜵 Texas Instruments

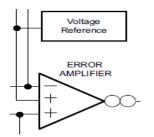

#### **Control mode: basic circuit block elements**

#### **Error amplifier**

#### Oscillator

#### **PWM comparator**

#### **One shot timer**

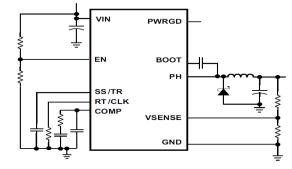

# Control mode: internal, external, or no compensation

PH

BOOT

VSENSE

GND

VIN

VIN

NC

NC

ENA

VOUT

MN)

vour)-

#### **External compensation**

- Control over gain and phase margin.

- Wide selection of filter components.

- Flexible switching frequency.

- Complex small-signal feedback network.

- Fewer external components.

- Easy design & less verification.

- Limited L & C components.

- Be careful with large number bypass capacitance.

#### No compensation

• D-CAP versions, DCS or Constant On Time (COT).

TPS54327DDA

RFG5 SV

VOUT)

- Fast transient response.

- Easy design & less verification.

- Limited L & C components.

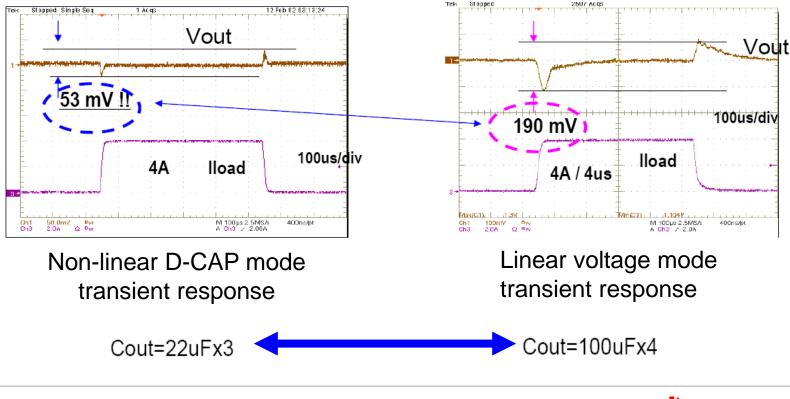

# **Control mode: linear and non-linear transient response**

# **Control mode: rules of thumb**

| Concern                | Linear control                                                                                  | Non-linear control                                                                   |

|------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Frequency behavior     | Predictable                                                                                     | Not so predictable                                                                   |

| Synchronization        | With Frequency Sync pin                                                                         | Not possible over dynamic load condition                                             |

| Transient response     | Typically slower. Needs to wait for clock pulse                                                 | Typically faster. No internal clock circuit                                          |

| Load profile           | Signal chain power, noise sensitive PCB area, static load behavior                              | Higher current, dynamic load conditions.<br>"Moving data around"                     |

| Typical market segment | Industrial, Communications, Automotive                                                          | Enterprise, Personal Electronics                                                     |

| Customer effort        | External compensation needs customer validation effort. Internal compensation limits components | Less customer validation effort. Limits external capacitance selection               |

| External components    | Most flexibility with output capacitance with external compensation                             | Limited flexibility with output capacitance, fewer Cout to meet overshoot/undershoot |

| Models                 | Average, Transient                                                                              | Transient. Average models are difficult                                              |

| WEBENCH support        | Yes. WEBENCH can help compensate                                                                | Yes                                                                                  |

In some cases, customers don't understand control mode nuances, but want "easy, or "fewer caps"

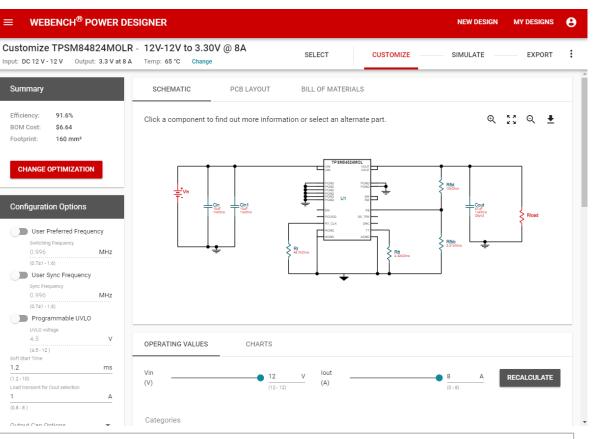

# **Control mode: WEBENCH example**

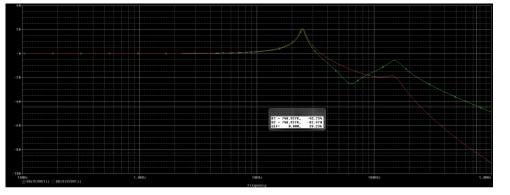

#### TPS54824 example:

- 12-14  $V_{IN}$ , 1.2  $V_{OUT}$ , 8 A

- Required Inductor from Customer AVL:

- Coilcraft

- XAL1010-822MEB

- 8.2 uH

#### Original WEBENCH design:

- 1.2 uH Coilcraft

- Switching Freq: 374.6 kHz

- Crossover Freq: 37.5 kHz

- Phase Margin: 67.8 Deg

- Gain Margin: -18.2 dB

All point to good stability.

# **Control mode: resources**

**Reference Guides:**

<u>Control-Mode Quick Reference Guide</u>

Application Reports:

- Choosing the Right Fixed-Frequency Buck-Regulator Control Strategy

- <u>Choosing the Right Variable-Frequency Buck-Regulator Control Strategy</u>

- How to Measure the Loop Transfer Function of Power Supplies

- <u>Understanding Frequency Variation in the DCS-Control™ Topology</u>

White Papers:

Internally Compensated Advanced Current Mode (ACM)

Technical Articles:

Comparing Internally-compensated Advanced Current Mode (ACM) with D-CAP3™ Control

# **Remember!**

- TI DC/DC solutions and content help customers solve their problems.

- When using Embedded Processing and Signal-Chain products, remember TI DC/DC conversion products address both processor and signal-chain power concerns.

- Use WEBENCH to help understand the trade-offs as well as find working solutions.

- Our factory applications engineers are here to help.

- <u>Check out</u>: The Essential Collection of DC/DC Buck Switching Regulator Technical Documentation.

#### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated