# Power Sharing Between Two Parallel, Four-Switch Buck-Boost Converters

Zack Liu, Youhao Xi, Kim Nielson

#### ABSTRACT

The synchronous 4-switch buck-boost controller LM5176 operates over a wide input voltage range from 4.2 V to 55 V (60 V absolute maximum) to support automotive start-stop system, industrial personal computers (IPCs), and many other applications. It produces a regulated output voltage at, above, or below the input voltage. Paralleling two LM5176 converters is an attractive way to support higher power level.

This application report presents a cost-effective solution to achieve well balanced load sharing between the two paralleled converters within 1% error, without sacrificing the overall performance including the output regulation as well as dynamic response. Design guidelines are given to help readers to design properly for practical applications.

#### Contents

| 1 | Introduction                           | 2  |

|---|----------------------------------------|----|

| 2 | Paralleling Method and its Realization | 3  |

| 3 | Test Results                           | 5  |

| 4 | Conclusion                             | 14 |

| 5 | References                             | 14 |

#### List of Figures

| 1  | Two Parallel LM5176 Converters as Power Supply                       | 3 |

|----|----------------------------------------------------------------------|---|

| 2  | Equivalent Model                                                     | 3 |

| 3  | Output I-V Characteristic Curve of Two Parallel LM5176 Converters    | 3 |

| 4  | Two Parallel LM5176 Converters with Extra Current Sharing Circuit    | 4 |

| 5  | Error of Load Current(Interleaved)                                   | 5 |

| 6  | Load Distribution of Two Phases(Interleaved)                         | 5 |

| 7  | Error of Load Current(In-Phase)                                      | 5 |

| 8  | Load Distribution of Two Phases(In-Phase)                            | 5 |

| 9  | Load Regulation of Parallel Power                                    | 6 |

| 10 | 36-V Buck Region With 40-A Load—Four Switch Nodes                    | 6 |

| 11 | 36-V Buck Region With 40-A Load—Inductor Current Waveforms           | 6 |

| 12 | 12-V Buck-Boost Region With 40-A Load—Four Switch Nodes              | 7 |

| 13 | 12-V Buck-Boost Region With 40-A Load—Inductor Current Waveforms     | 7 |

| 14 | 9-V Boost Region With 40-A Load—Four Switch Nodes                    | 7 |

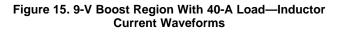

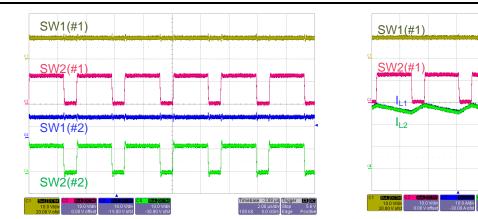

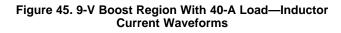

| 15 | 9-V Boost Region With 40-A Load—Inductor Current Waveforms           | 7 |

| 16 | Load Transient in 36-V Buck Region—With 20-A to 40-A Load Step       | 7 |

| 17 | Load Transient in 36-V Buck Region—With 0-A to 40-A Load Step        | 7 |

| 18 | Load Transient in 12-V Buck-Boost Region—With 20-A to 40-A Load Step | 8 |

| 19 | Load Transient in 12-V Buck-Boost Region—With 0-A to 40-A Load Step  | 8 |

| 20 | Load Transient in 9-V Boost Region—With 20-A to 40-A Load Step       | 8 |

| 21 | Load Transient in 9-V Boost Region—With 0-A to 40-A Load Step        |   |

| 22 | Output Voltage Ripple in 36-V Buck Region—No Load                    | 8 |

|    |                                                                      |   |

Power Sharing Between Two Parallel, Four-Switch Buck-Boost Converters

1

| Intro | odu | ctior |

|-------|-----|-------|

|       |     |       |

| 23 | Output Voltage Ripple in 36-V Buck Region—40-A Load                   | 8  |

|----|-----------------------------------------------------------------------|----|

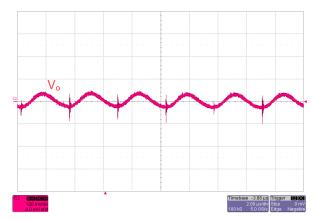

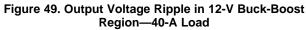

| 24 | Output Voltage Ripple in 12-V Buck-Boost Region-No Load               | 9  |

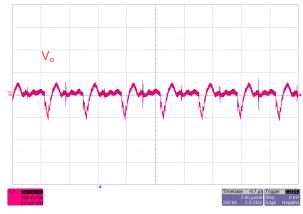

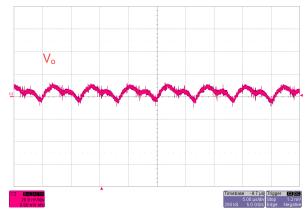

| 25 | Output Voltage Ripple in 12-V Buck-Boost Region—40-A Load             | 9  |

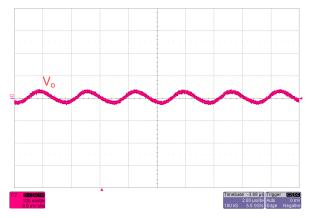

| 26 | Output Voltage Ripple in 9-V Boost Region-No Load                     | 9  |

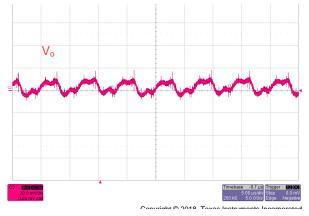

| 27 | Output Voltage Ripple in 9-V Boost Region—40-A Load                   | 9  |

| 28 | 40-A Start-Up in 36-V Buck Region—Total Output Current Waveform       | 9  |

| 29 | 40-A Start-Up in 36-V Buck Region—Two Phase Inductor Currents         | 9  |

| 30 | 40-A Start-Up in 12-V Buck-Boost Region—Total Output Current Waveform | 10 |

| 31 | 40-A Start-Up in 12-V Buck-Boost Region—Two Phase Inductor Currents   | 10 |

| 32 | 40-A Start-Up in 9-V Boost Region—Total Output Current Waveform       | 10 |

| 33 | 40-A Start-Up in 9-V Boost Region—Two Phase Inductor Currents         | 10 |

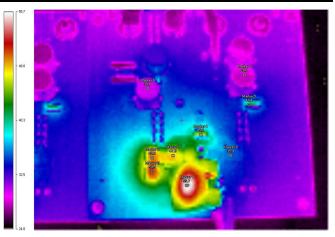

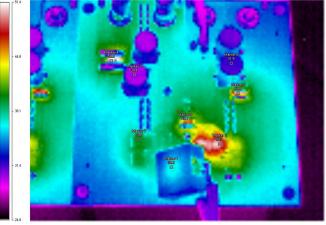

| 34 | 40-A Load Thermal Condition in 36-V Buck Region—First Board           | 10 |

| 35 | 40-A Load Thermal Condition in 36-V Buck Region—Second Board          | 10 |

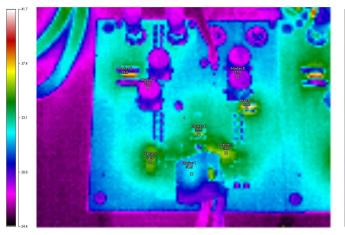

| 36 | 40-A Load Thermal Condition in 12-V Buck-Boost Region—First Board     | 11 |

| 37 | 40-A Load Thermal Condition in 12-V Buck-Boost Region—Second Board    | 11 |

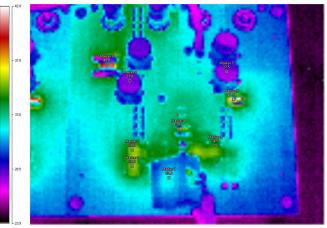

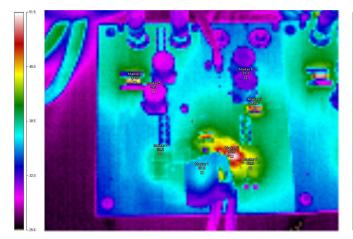

| 38 | 40-A Load Thermal Condition in 9-V Boost Region—First Board           | 11 |

| 39 | 40-A Load Thermal Condition in 9-V Boost Region—Second Board          | 11 |

| 40 | 36-V Buck Region With 40-A Load—Four Switch Nodes                     | 12 |

| 41 | 36-V Buck Region With 40-A Load—Inductor Current Waveforms            | 12 |

| 42 | 12-V Buck-Boost Region With 40-A Load—Four Switch Nodes               | 12 |

| 43 | 12-V Buck-Boost Region With 40-A Load—Inductor Current Waveforms      | 12 |

| 44 | 9-V Boost Region With 40-A Load—Four Switch Nodes                     | 12 |

| 45 | 9-V Boost Region With 40-A Load—Inductor Current Waveforms            | 12 |

| 46 | Output Voltage Ripple in 36-V Buck Region—No Load                     | 13 |

| 47 | Output Voltage Ripple in 36-V Buck Region—40-A Load                   | 13 |

| 48 | Output Voltage Ripple in 12-V Buck-Boost Region—No Load               | 13 |

| 49 | Output Voltage Ripple in 12-V Buck-Boost Region—40-A Load             | 13 |

| 50 | Output Voltage Ripple in 9-V Boost Region—No Load                     |    |

| 51 | Output Voltage Ripple in 9-V Boost Region—40-A Load                   | 14 |

|    |                                                                       |    |

#### List of Tables

| 1 | Component Parameters for Power Sharir | g Circuit | 5 |

|---|---------------------------------------|-----------|---|

|---|---------------------------------------|-----------|---|

#### Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction

The LM5176 device is a wide input voltage range, four-switch buck-boost controller IC with integrated drivers for N-channel MOSFETs. It operates in the buck mode when  $V_{IN}$  is greater than  $V_{OUT}$  and in the boost mode when  $V_{IN}$  is less than  $V_{OUT}$ . When  $V_{IN}$  is close to  $V_{OUT}$ , the device operates in a proprietary transition buck or boost mode.

One single LM5176 converter can deliver power greater than 200 W with the synchronous MOSFETs. To get higher output power, parallel power stages are needed to solve the excessive board heating problem because of the increased switching and conduction losses. The paralleling method can also provide many other benefits: enhanced modularity, design flexibility, and minimized component ratings. These benefits can be realized only if the two LM5176 converters evenly share the total load power.

This application report presents a power sharing method, which is simple, low cost, and high performance at the same time. With only one OpAmp and few resistors and capacitors, the load sharing can be well balanced. Test results show less than 1% error of sharing without sacrificing the overall performance.

# 2 Paralleling Method and its Realization

# 2.1 Why output current difference exists

Figure 1 shows the two parallel LM5176 converters.

Copyright © 2018, Texas Instruments Incorporated

Figure 1. Two Parallel LM5176 Converters as Power Supply

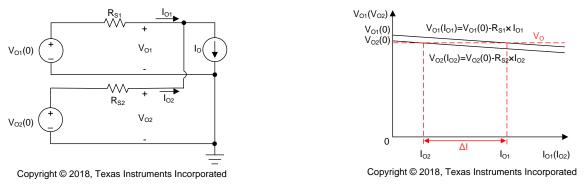

A power supply can be modeled as an ideal voltage source in series with a source resistor shown in Figure 2. Because of regulation tolerance, the two module's output voltages can be slightly different. The output I-V characteristic curves of the two individual converters are shown in Figure 3.  $V_{O1}(0)$  and  $V_{O2}(0)$  are the two ideal voltage sources at no load and  $R_{S1}$ ,  $R_{S2}$  are the source resistors in series. Figure 3 also explains why there is a big load sharing difference between the two converters if they are simply parallelly connected directly. Normally  $V_{O1}(0)$  and  $V_{O2}(0)$  are seldom the same. Owing to good regulation performance, the slope of the I-V curve is often very shallow. At the same output voltage  $V_O$ , there is a large difference between the two paralleled converters output currents  $I_{O1}$  and  $I_{O2}$ .

Figure 2. Equivalent Model

# 2.2 Paralleling method realization

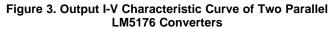

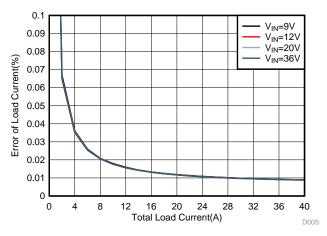

Figure 4 shows the proposed power sharing control circuit. It configures the two parallel converters as master and slave. The sharing control circuit consists of the following: (a) two equal current sense resistors  $R_{S1}$  and  $R_{S2}$ ; (b) two RC networks  $R_{Fx}$ ,  $C_{Fx}$  to filter the corresponding output voltage ripples; (c) a high precision low input offset OpAmp as the error amplifier (using LM8261 in the prototype); (d) an integral capacitor  $C_P$  across the inverting input and output of amplifier; (e) a resistor  $R_c$  to feed back the current error signal  $V_{CFB}$  to the slave control circuit so as to modulate the slave output for balanced power sharing. The whole power sharing control circuit is simple and low cost, but the performance is excellent.

Copyright © 2018, Texas Instruments Incorporated

The operating principle is as follows. The output currents of two LM5176 converters are monitored by the current sense resistors. The current difference is then amplified by the error amplifier. The amplifier output is sent to the slave converter's feedback circuit through  $R_c$  in order to modulate the slave output voltage for a balanced power sharing. To minimize the sharing error, it is important that the sharing control circuit should be laid out and routed symmetrically. As the current sense resistors values are normally very small in milliohms to minimize the incurred power loss and heat, a small resistance difference between  $R_{S1}$  and  $R_{S2}$  causes a big current sharing difference, which can be shown in the following example. Assuming 4 m $\Omega$  current sense resistors are chosen for  $R_{S1}$  and  $R_{S2}$ , the actual resistance of  $R_{S2}$  could be 5 m $\Omega$  due to the parasitic resistance of asymmetric layout. Also assuming  $V_{O1}$  and  $V_{O2}$  values are the same, the output voltage  $V_O$  is 12 V and the total load current is 40 A, then it satisfy Equation 1 and Equation 2:

$$\frac{V_{o_1} - V_o}{R_{s_1}} + \frac{V_{o_2} - V_o}{R_{s_2}} = I_o$$

(1)

$$V_{01} = V_{02} = V_0 + \frac{R_{S1}R_{S2}}{R_{S1} + R_{S2}}I_0$$

(2)

The error of two output currents can be derived by Equation 3:

$$\frac{I_{o_1} - I_{o_2}}{I_o} = \frac{R_{s_2} - R_{s_1}}{R_{s_1} + R_{s_2}}$$

(3)

Therefore, the error of load current sharing is 11.1% at 40 A if 1 m $\Omega$  difference exists between R<sub>S1</sub> and R<sub>S2</sub>. It is highly recommended to minimize the error by placing R<sub>S1</sub>, R<sub>S2</sub> and the common node of output as close as possible on the circuit board, and also placing the sensing network near R<sub>S1</sub> and R<sub>S2</sub>.

The slave LM5176 converter output voltage can be determined by Equation 4:

$$V_{O2} = \left(1 + \frac{R_{FB2}}{R_{FB1}}\right) V_{REF} + \frac{R_{FB2}}{R_{C}} (V_{REF} - V_{CFB})$$

4

Paralleling Method and its Realization

From above equations, it can be seen that by varying  $V_{CFB}$  value, the slave output voltage is adjusted up or down to compensate for the output voltage difference from the master output, thus achieving balanced power sharing.

If an extreme condition were to occur, the output of LM8261 has the risk of being railed to the V+ of amplifier or ground. For a 12 V application, with R<sub>1</sub> equals 280 k $\Omega$  and R<sub>2</sub> equals 20 k $\Omega$ , select R<sub>c</sub> as 1 M $\Omega$  to establish the boundary of V<sub>02</sub> between 8.70 V to 12.23 V.

LM8261 is a rail-to-rail input and output OpAmp which can operate with a wide supply voltage range and has low input offset voltage. Use  $V_{O1}$  as the supply voltage. To increase the current sharing accuracy, it's recommended to use resistors to connect to the error amplifier directly instead of resistor divider networks, which avoids the affect of 1% tolerance of the resistor divider network. Table 1 lists all the component parameters for this circuit.

| R <sub>s</sub> (mΩ) | R <sub>F1</sub> (kΩ) | $R_{F2}(k\Omega)$ | C <sub>F1</sub> (μF) | C <sub>F2</sub> (μF) | C <sub>P</sub> (nF) | R <sub>c</sub> (MΩ) | R <sub>F1</sub> (kΩ) | $R_{F2}(k\Omega)$ |

|---------------------|----------------------|-------------------|----------------------|----------------------|---------------------|---------------------|----------------------|-------------------|

| 4                   | 2                    | 2                 | 1                    | 1                    | 20                  | 1                   | 280                  | 20                |

| Table 1. Componen | t Parameters | for | Power | Sharing | Circuit |

|-------------------|--------------|-----|-------|---------|---------|

|-------------------|--------------|-----|-------|---------|---------|

# 3 Test Results

# 3.1 Load regulation and load distribution

Use the RT/SYNC pin of the LM5176 device to synchronize the pulse-width modulation (PWM) controller to an external clock. The clocks for the two parallel converters can either be 180° out of phase or in-phase.

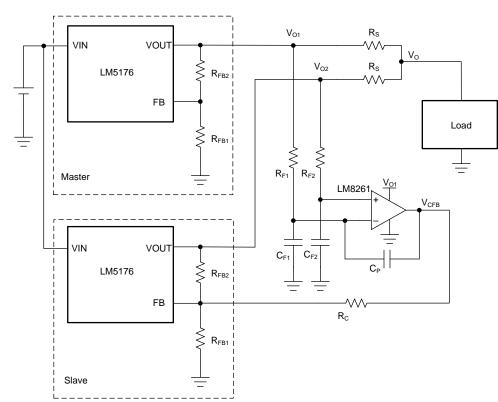

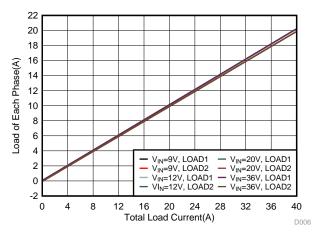

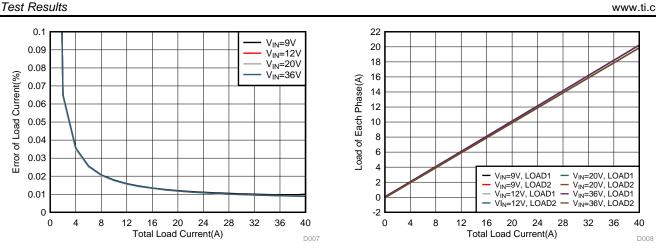

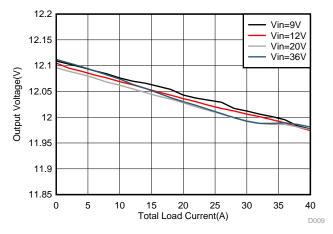

Figure 5 and Figure 7 show the test results of the error of load currents of 180° interleaved and in-phase separately. The error is less than 2% when the total load current is above 8A and the error is less than 1.1% at full load current under different input voltage conditions. Figure 6 and Figure 8 show the test results of the load distribution of two phases under different input voltage conditions.

Figure 5. Error of Load Current(Interleaved)

Figure 6. Load Distribution of Two Phases(Interleaved)

Figure 8. Load Distribution of Two Phases(In-Phase)

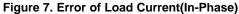

Figure 9 shows the load regulation of the whole system under different input voltage conditions. The variation of the output voltage is within ±1%, which indicates an excellent load regulation performance.

Figure 9. Load Regulation of Parallel Power

#### 3.2 Interleaved SYNC Operation

6

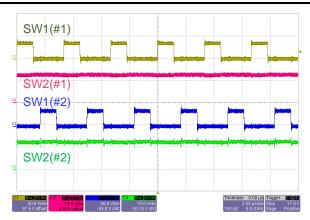

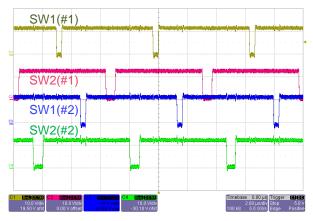

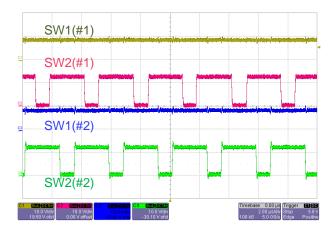

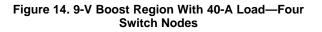

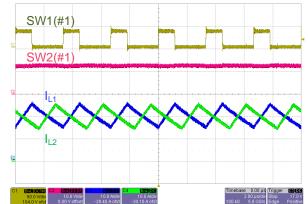

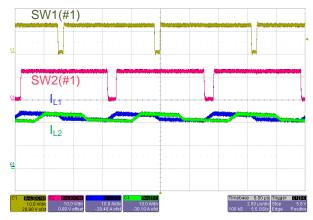

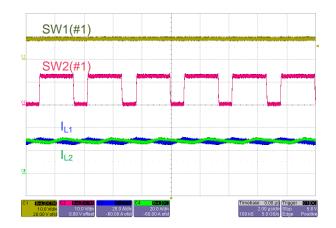

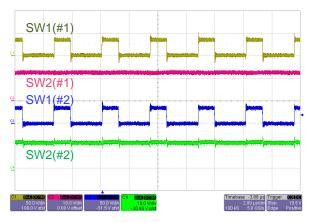

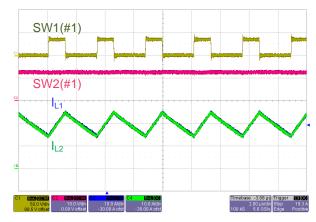

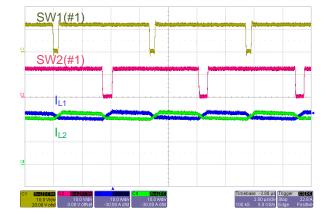

Figure 10 through Figure 15 show the four switching nodes and inductor current waveforms in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively. The waveforms show that each operation region is stable and the inductor current waveforms of the two phases indicate equally distributed load currents.

Figure 10. 36-V Buck Region With 40-A Load—Four Switch Nodes

Figure 12. 12-V Buck-Boost Region With 40-A Load—Four Switch Nodes

Figure 11. 36-V Buck Region With 40-A Load—Inductor Current Waveforms

Figure 13. 12-V Buck-Boost Region With 40-A Load—Inductor Current Waveforms

7

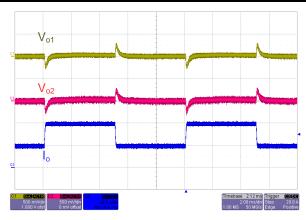

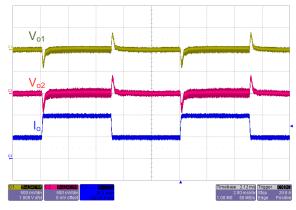

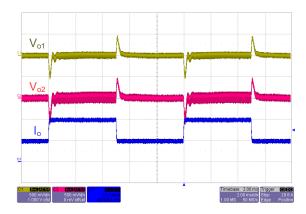

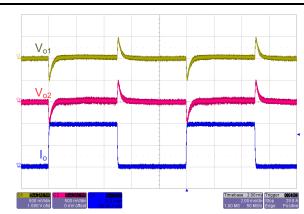

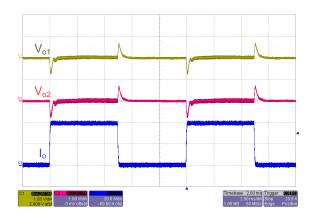

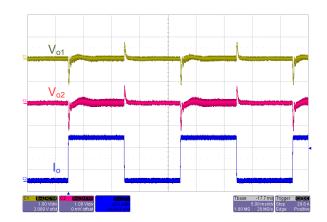

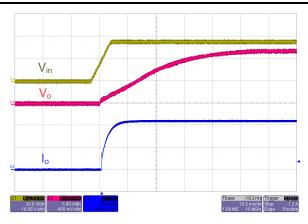

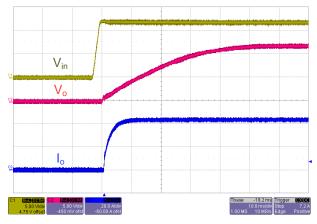

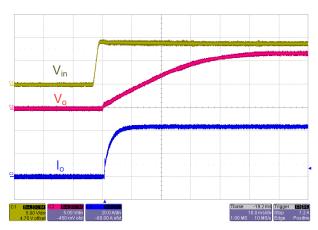

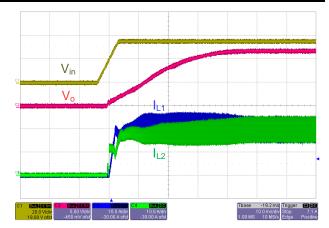

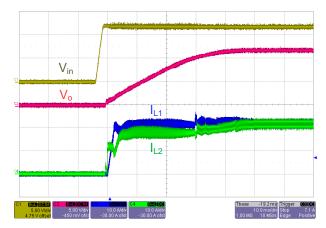

Figure 16 through Figure 21 show the load transient of 20 A-40 A and 0 A-40 A waveforms in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively.

Test Results

Figure 16. Load Transient in 36-V Buck Region—With 20-A to 40-A Load Step

Figure 18. Load Transient in 12-V Buck-Boost Region—With 20-A to 40-A Load Step

8

Figure 17. Load Transient in 36-V Buck Region—With 0-A to 40-A Load Step

Figure 19. Load Transient in 12-V Buck-Boost Region—With 0-A to 40-A Load Step

Figure 21. Load Transient in 9-V Boost Region—With 0-A to 40-A Load Step

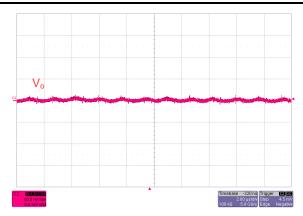

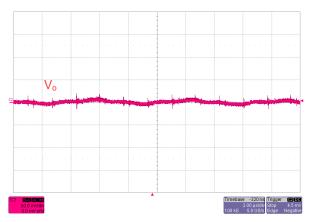

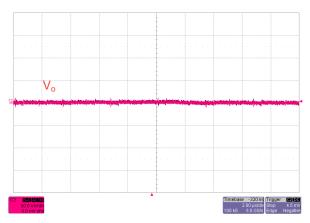

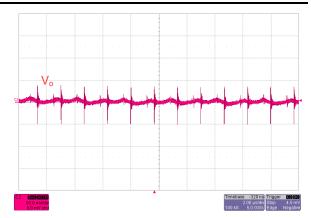

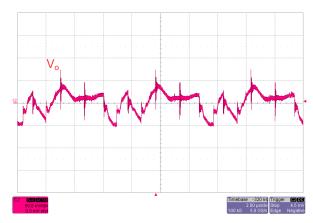

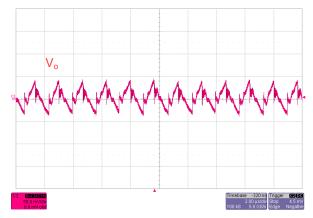

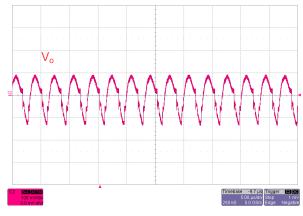

Figure 22 through Figure 27 show the output ripple waveforms in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively.

Figure 22. Output Voltage Ripple in 36-V Buck Region—No Load

Figure 24. Output Voltage Ripple in 12-V Buck-Boost Region—No Load

Figure 26. Output Voltage Ripple in 9-V Boost Region—No Load

Test Results

Figure 23. Output Voltage Ripple in 36-V Buck Region—40-A Load

Figure 25. Output Voltage Ripple in 12-V Buck-Boost Region—40-A Load

Figure 27. Output Voltage Ripple in 9-V Boost Region—40-A Load

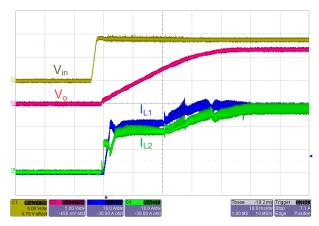

Figure 28 through Figure 33 show the start-up waveforms in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively. The loads are not equally distributed during a certain period of the start-process due to a sequential order during start-up and the necessary time for a current sharing-circuit to build up and get ready.

9

Test Results

Figure 28. 40-A Start-Up in 36-V Buck Region—Total Output Current Waveform

Figure 30. 40-A Start-Up in 12-V Buck-Boost Region—Total Output Current Waveform

Figure 32. 40-A Start-Up in 9-V Boost Region—Total Output Current Waveform

Figure 29. 40-A Start-Up in 36-V Buck Region—Two Phase Inductor Currents

Figure 31. 40-A Start-Up in 12-V Buck-Boost Region—Two Phase Inductor Currents

Figure 33. 40-A Start-Up in 9-V Boost Region—Two Phase Inductor Currents

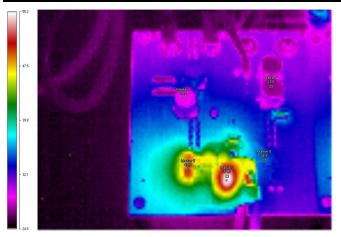

Figure 34 through Figure 39 show the 40 A load two boards thermal condition in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively. The heat is distributed on two boards equally. The test results are captured with a 600-CFM airflow.

Test Results

Figure 34. 40-A Load Thermal Condition in 36-V Buck Region—First Board

Figure 35. 40-A Load Thermal Condition in 36-V Buck Region—Second Board

Figure 36. 40-A Load Thermal Condition in 12-V Buck-Boost Region—First Board

Figure 37. 40-A Load Thermal Condition in 12-V Buck-Boost Region—Second Board

Figure 38. 40-A Load Thermal Condition in 9-V Boost Region—First Board

Figure 39. 40-A Load Thermal Condition in 9-V Boost Region—Second Board

#### Test Results

# 3.3 In-phase SYNC Operation

Synchronizing the two parallel LM5176 converters with the same clock.

Figure 40 through Figure 45 show the four switching nodes and inductor current waveforms in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively.

Figure 40. 36-V Buck Region With 40-A Load—Four Switch Nodes

Figure 41. 36-V Buck Region With 40-A Load—Inductor Current Waveforms

Figure 42. 12-V Buck-Boost Region With 40-A Load—Four Switch Nodes

Figure 43. 12-V Buck-Boost Region With 40-A Load—Inductor Current Waveforms

Figure 44. 9-V Boost Region With 40-A Load—Four Switch Nodes

Figure 46 through Figure 51 show the output ripple in the 36-V buck, 12-V buck-boost, and the 9-V boost regions, respectively. In comparison with Figure 22 through Figure 27 when two converters are interleaved paralleled, the ripples are higher. Interleaved architecture provides a better solution for smaller output voltage ripple.

Figure 46. Output Voltage Ripple in 36-V Buck Region—No Load

Figure 48. Output Voltage Ripple in 12-V Buck-Boost Region—No Load

Figure 47. Output Voltage Ripple in 36-V Buck Region—40-A Load

13

Figure 50. Output Voltage Ripple in 9-V Boost Region—No Load

Figure 51. Output Voltage Ripple in 9-V Boost Region—40-A Load

# 4 Conclusion

The proposed current sharing method provides a high performance, cost effective solution to achieve well balanced power sharing between two LM5176 converters. With a simple external circuit of only one amplifier and few resistors, capacitors, the slave can accurately follow the master to deliver the same amount of load current and with an error that is within 1% at full load. The experiment results of the parallel LM5176 converters with a 480 W capability were presented as proof of concept. The proposed method can be readily applied to support high power level.

#### 5 References

- 1. Texas Instruments, LM5176 55-V Wide VIN Synchronous 4-Switch Buck-Boost Controllers Datasheet

- 2. Texas Instruments, LM5176 Wide-VIN Buck-Boost Controller EVM

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated