# Illumination Driving for Time-of-Flight (ToF) Camera System

# ABSTRACT

This application note has guidelines and an example to explain the design of high-speed illumination driving circuits for 3D time-of-flight (ToF) cameras. Following the guidelines should considerably shorten the number of iterations it would take otherwise, to design the illumination driver circuits.

#### Contents

| 1 | Introdu  | ction                       | 2  |

|---|----------|-----------------------------|----|

| 2 | Illumina | ation Driver Specifications | 2  |

|   |          | ing Topologies              |    |

|   |          | Shunt Switching             |    |

|   |          | Series Switching            |    |

| 4 | Power    | Supply Design               | 15 |

| 5 | Conclu   | sion                        | 16 |

#### List of Figures

| 1  | Simple Shunt Switching                       | 3  |

|----|----------------------------------------------|----|

| 2  | Inductor in Series With Current Source       | 3  |

| 3  | Parasitic Components Modeled                 | 4  |

| 4  | Snubber Circuit Included                     | 5  |

| 5  | Ideal Implementation                         | 6  |

| 6  | Laser Turn on Current Transients             | 7  |

| 7  | Current Transients, Improper Layout          | 7  |

| 8  | Current Transients, Improper Layout          | 8  |

| 9  | Sub-Optimal Ground Return Path               | 8  |

| 10 | Decoupling Capacitor Ground Path             | 9  |

| 11 | Decoupling Capacitor Ground Path             | 9  |

| 12 | Good LED Placement                           | 11 |

| 13 | Sub-Optimal LED Placement                    | 11 |

| 14 | MOSFET Driver Decoupling Capacitor Placement | 11 |

| 15 | Snubber Placement                            | 12 |

| 16 | Series MOSFET, Ground Return Capacitor       | 12 |

| 17 | Layout to Scale                              | 13 |

| 18 | No Series MOSFET                             | 14 |

|    |                                              |    |

# Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction

This application note deals with the design of the Illumination driver circuit. This is aimed at sensitizing system designers to the various issues which would typically take design revisions to realize and get fixed.

The basic requirements of the circuit are examined:

The circuit is required to emit the maximum optical power at the fundamental frequency for a given amount of electrical power spent.

The first step is to choose an optical emitter (*Edge-Emitting Laser, VCSEL, LED*, and so forth). Electrically, all the normally used emitters are just diodes. They emit light when current flows through them. The easiest way to modulate the light emission is to turn on and turn off the current through the emitter. This can be achieved in 2 ways:

- Series switching: Have a voltage source, emitter and a switch in series. Turn the switch on and off at modulation frequencies. A power MOSFET is used to realize the switch. A buffer capable of driving a power MOSFET gate from 10 MHz up to 80 MHz is chosen. Higher frequencies are more relevant for lasers. This method has a fundamental disadvantage of having the MOSFET drain's node going to infinite impedance (for ideal MOSFETS) when the MOSFET is not conducting. The only reason to use this topology is that an inductor can be avoided.

- 2. **Shunt switching:** Have a current source, powering an emitter and a switch in parallel. This is like a Norton's equivalent of the previous option. This has an advantage that there is no node with infinite impedance to the ground, by design. This topology is recommended as it enables higher frequency performance.

### 2 Illumination Driver Specifications

The illumination driver is meant to give a modulated light input per the signal inputs from the sensor. The main goal of the engineer would be to maximize the amplitude of the fundamental harmonic of the transmitted light signal while consuming the minimum possible power. Following are the top-level specifications for the illumination driver circuit:

- 1. **Maximum modulation frequency:** The idea is to have the capability to modulate at a frequency as high as possible. The maximum frequency can be limited by the non-zero rise time and fall time (rise/fall time) of the illumination waveform and also the duty-cycle distortion that happens at the higher frequencies. Part of the duty-cycle distortion happens at the MOSFET gate-driving stage. OPT8241 and OPT8320 can both correct for the duty-cycle distortion in the optical output by pre-distorting the input duty cycle of the illumination driver circuit. Very small rise/fall times ensure that the amplitude of the fundamental harmonic is close to the theoretical maximum for a given peak power. If the optical rise/fall times increase, the waveform looks more like a triangular wave and the amplitude of the fundamental harmonic reduces. One can examine the Fourier series expansion of an asymmetric trapezoidal wave to understand how the fundamental harmonic's amplitude varies.

- 2. **Peak optical power:** Peak optical power is directly representative of how much signal power is present in the system. This specification will typically be derived from the *3D ToF System Estimator Tool* (SBAC124). This will decide the number of Lasers, LEDs, VCSELs, peak operating currents, and so forth.

# 3 Switching Topologies

## 3.1 Shunt Switching

2

Shunt switching is the topology of choice. This topology can give relatively high peak optical power of up to 20 W (or even higher) and high frequencies of up to 80 MHz or 100 MHz. However, for very low-power illumination circuits with peak optical power of the order of 10 mW, this topology does not work very well. The reason is that most discrete switching power MOSFETs in the market have relatively high output capacitance. The small currents from the current source will not be able to drive the MOSFET output capacitance at high frequencies. A list of advantages follows:

- 1. The output power is relatively stable against frequency, temperature, and so forth.

- 2. The supply voltage required is half of the actual peak voltage requirement of the emitters.

- 3. None of the nodes is at infinite impedance by design at any point of time in the switching operation.

- 4. There are fewer components in the high frequency switching current path.

- 5. Electrical-to-optical conversion efficiency is higher

Disadvantages are as follows:

- 1. The circuit cannot scale in power down to a few mWs of optical peak powers.

- 2. A high frequency inductor must be used

# 3.1.1 Circuit Implementation

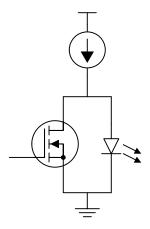

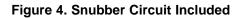

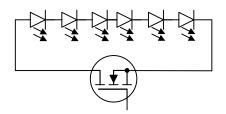

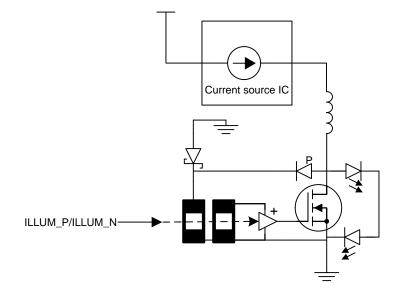

Implement the circuit as shown in Figure 1.

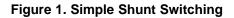

Practical current sources cannot provide high impedance as frequencies increase. It is very hard to get current sources which give high impedance at the voltage rise edge rates of the illumination circuits. Adding an inductor in series with the current source helps. The impedance of this inductor increases with frequency and increases the overall output impedance of the current source at high frequencies. The circuit now looks like Figure 2.

Figure 2. Inductor in Series With Current Source

#### Switching Topologies

www.ti.com

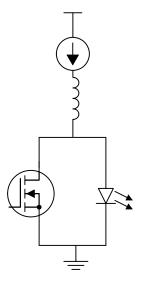

A typical requirement is for the emitter current to rise from 0 to 2.5 A in 2 ns. This means the dl/dt rates are > 1 GA/s. Circuit parasitic inductance is in the order of a few nH. It is now evident that a considerable amount of energy is stored/discharged in the parasitic inductance of the circuit. Parasitic inductance includes trace inductance and package inductance. The switch also has its own parasitic capacitance. A more accurate model of the circuit looks like Figure 3.

Figure 3. Parasitic Components Modeled

The red inductor is added intentionally. Other capacitors and inductors are all parasitic. These inductors and capacitors can resonate with each other. An order of magnitude approximation of the ringing frequency (resonant frequency) is as follows:

- Switch capacitance, C is approximately 300 pF

- Parasitic inductance, L is approximately 5 nH

- Ringing frequency is approximately 130 MHz

The ringing frequency is very close to the desired switching frequency. The ringing is going to interfere with the intended current flow through the circuit. Ringing might result in overcurrent through an edgeemitting laser causing *Catastrophic Optical Damage*. Ringing might also partially cause the laser or LED to emit some light when they are supposed to be turned off. As the switching frequency is very similar to the ringing frequency, using the usual resistor-based snubber (damping) techniques for reducing the ringing will not be effective. Any RC snubber-based circuit will damp the main switching action as well.

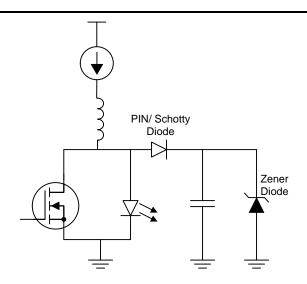

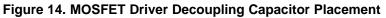

A non-linear circuit is used for damping this ringing. Instead of damping the ringing based on its frequency, the ringing energy is dampened by exploiting the excess voltage it causes across the MOSFET. The maximum voltage across the emitters can be estimated and any excess voltage is clamped by making use of the circuit in Figure 4. It helps to use a Zener diode, available in multiple voltage options for the same PCB footprint. The Zener diode voltage can be adjusted experimentally to tune out the ringing in a prototype design. The Zener diode has to be carefully chosen so that the circuit damps the first peak of the ringing and basically removes the energy in the resonant components. The rectification PIN/Schottky diode is a crucial component of the snubber. It must be able to rectify the ringing frequencies and give very low impedance while it is switching. For the low impedance, the rectification diode should have an inductance much smaller than that of the emitter power circuit to be able to respond quickly enough and damp out the ringing. It should also have a very small capacitance so it does not contribute to the ringing of the circuit itself. In general, it is very important that the snubber circuit have a very low impedance for it to successfully remove the resonant energy.

## 3.1.2 Component Choice

Concerns and tips for selecting each of the critical components are listed below:

- Power MOSFET: Choice of power MOSFET must be done in the same manner as for series switching. Special care has to be taken for lower current circuits as the switch output capacitor limits maximum frequency. Low output capacitance switches have to be used for low power circuits. CSD16301Q2 has been the workhorse for this purpose.

- 2. High frequency Inductor: Choosing the high frequency inductor has a few important considerations. One has to keep in mind that this inductor ensures that the current source has high impedance for the load at high frequencies. The inductance value should be chosen such that the LED/LASER current does not change too much because of the switching activity. Inductance value calculation is similar to designing inductor values for a current-ripple specification in DC-DC converters. LEDs and VCSELs can usually take higher peak currents and it is acceptable to have lower inductance values for these components. Edge-emitting lasers usually have a strict limit on the high frequency currents as they have issues with COD. This inductor is responsible for suddenly forcing high currents through the parasitic inductance of the emitters. It has to sustain a very high voltage rise rate at its lower node for proper circuit operation. If the voltage is expected to rise from 5% to 95% in 1ns ( $T_p$ ), as a general guideline, assume that the maximum frequency that the inductor will experience will be  $f_{MAX} = 1/(T_R \times 1)$  $\pi$ ). The voltage rise rate can be calculated from the current and the output capacitance of the MOSFET. The self resonant frequency of the chosen inductor should be greater than f<sub>MAX</sub>. Another inductor specification that has to be taken into account is the saturation current. A thumb rule is that the inductor saturation current has to be 40% greater than the emitter peak current. Some manufacturers give derating curves for current and temperature. If derating is accounted for, the 40% extra is not necessary. Average current rating can be much lower if necessary as this inductor will not

be carrying current continuously.

- 3. **Snubber rectifying diode:** This diode has to be able to rectify 100s of MHz which is much faster than any other active component on the circuit. The diode needs to provide a very low impedance path when it is conducting. As it deals with high frequencies, a diode with very low package inductance should be chosen. Any inductance in this diode will also store energy. The diode might turn out to be counterproductive if the package or layout causes this diode to have so much inductance to affect the main switching circuit. This diode should also have a very low capacitance for the same reason that the diode should not participate in the ringing. RF PIN diodes are suitable for this purpose. Although these diodes are not designed for switching, experiments have verified that these diodes are effective. The best component choice so far is: BAP65-02. Its package inductance is 0.6 nH.

- 4. **Snubber Zener diode:** The Zener diode decides the cut off voltage for the snubbing action. It needs to have a sharp cut off at the breakdown point. The diode should also be available for various voltages given the same PCB footprint. Typically, the diode breakdown voltage requirement of the circuit is not initially obvious. The best way is to have various diode voltage components ready and to figure out the best diode voltage on a prototype.

- 5. **Emitter:** Choosing emitters requires top level system performance considerations. This will be covered in another application note.

## 3.1.3 Board Physical Design

The board physical design is one of the most elusive parts of the whole design process. Unfortunately, it is also one of the neglected aspects of designing PCBs. This circuit pushes the limitations of each of its components and they all need to be chosen carefully as seen above. The board layout largely determines what the parasitic inductance values are. This has a direct effect on the performance of the system. It is important to understand that good board design is critical to the circuit performance and utmost care must be taken to ensure the PCB works. This section will deal with identifying which part of the circuit is critical and discussing how to minimize its parasitic inductance.

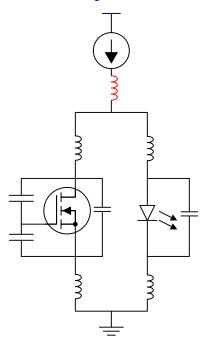

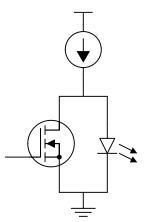

A practical implementation of the circuit, when the parasitics are modeled, looks like Figure 5.

Figure 5. Ideal Implementation

Parasitic inductance is a measure of the energy stored in the magnetic field of the current in the circuit. The first thing to be aware of is that current flows in loops. So to understand how much parasitic inductance a circuit has, it helps to identify the high frequency current loops in a given circuit. The current loops concentrated on the most, are the ones which have the maximum current slew rates (dl/dt). The most important current loop is the one with the illuminators and the high-speed switching MOSFET. The other current loop is the MOSFET gate driving circuit. Both the parts of the circuit need to have very low parasitic inductance. The current loops in the circuit are examined and methods to minimize the inductance are discussed.

# 3.1.4 Current Loops

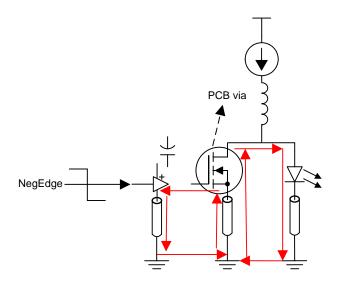

The most important loop is the one containing the illuminators and the high frequency switching MOSFET shown in Figure 6.

Switching Topologies

# Figure 6. Laser Turn on Current Transients

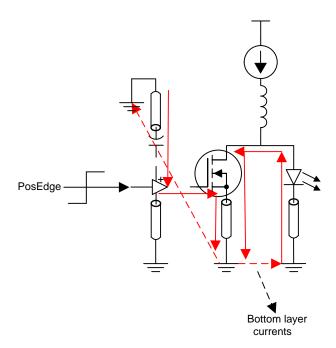

Improper layout can make the transient currents look like the ones shown in Figure 7.

# Figure 7. Current Transients, Improper Layout

Another example of improper layout is shown in Figure 8.

Figure 8. Current Transients, Improper Layout

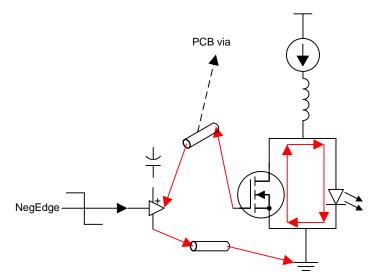

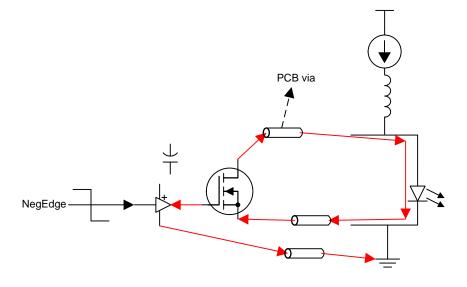

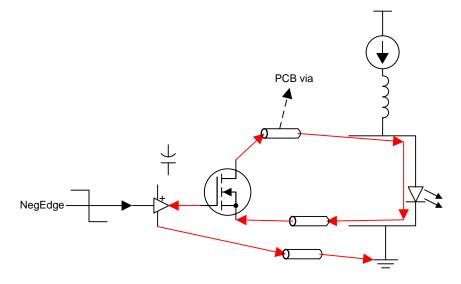

The mistakes in the above layouts are that the fast transient currents are passing through vias. Traces normally have a ground plane below them. The ground plane conducts an induced mirror current in the opposite direction and cancels the effect of the magnetic field of the trace to some extent. However, vias do not have such a ground return plane. It is possible to add mirroring ground vias, but the minimum gap between 2 vias is constrained by manufacturing tolerances. So, unless utmost care is taken, vias in the fast transient current path will almost always have more inductance than short traces of the same length as vias.

The other possible setups where it can go wrong are shown in Figure 9, Figure 10, and Figure 11.

Figure 10. Decoupling Capacitor Ground Path

Figure 11. Decoupling Capacitor Ground Path

The problem here is that the forward paths have all been well optimized. But the return paths have not been optimized. The engineer needs to think of how the currents flow through the chips and also equally importantly, through the ground return path. So, it is important to ensure that the total length of the current loop which includes the ground return path is as small as possible.

## 3.1.5 Step-by-Step Design Procedure

The specification is as follows:

- Optical peak power: 9 W

- Maximum modulation frequency: 80 MHz

- Minimum modulation frequency: 30 MHz

- 1. **Choose illuminators:** The number of illuminators and the type of illuminators has to be chosen depending on the desired modulation frequency, peak power requirement, cost, efficiency requirement, and eye safety certification. In this case, 4 parts of 22045498 by Lumentum are chosen. Another alternative is to use 4 parts of PCW-SMV-2-W0850-D86-56 by Princeton Optronics.

- 2. Choose high-speed switching MOSFET: The high-speed switching MOSFET has to switch at frequencies up to 80 MHz and conduct 2.5 A while turned on. 80 MHz is a very high frequency for most power MOSFETs and this component is the heart of the switching action. It has to have a very low package inductance, very low gate capacitance, and very low on state resistance. A specification that is often missed out is the gate series resistance of the MOSFET. Some MOSFETs have high series gate resistance which does not allow them to switch at high frequencies like 80 MHz.

A first order approximation of the losses in the MOSFET is:  $P = fCV^2 + 0.5I^2R$

The 4 lasers have a net forward voltage of 8.8 V. So the MOSFÉT Vds specification should be more than 8.8 V. Typically, the MOSFET drain voltage specification is chosen much higher than the actual requirement to account for ringing. A carefully designed snubber was chosen so it might not be necessary to overrate the MOSFET drain voltage specification by a very large value. Look at the list of N-channel MOSFETs from TI, the power loss is minimum for CSD16301Q2. There are other options with lower power losses but they are not chosen because of high series gate resistance. The high series gate resistance would prevent those MOSFETs from switching at high modulation frequencies.

3. **Choose high frequency inductor:** The maximum current that the Laser can take is 2.5 A. The average current during integration time is required to be greater than 2.25 A. Start with an assumption that 10% of the maximum current can be the peak-to-peak current ripple. A starting value for inductance is analyzed at 10% to see the order of magnitude of the inductance needed. The worst-case ripple will be observed at minimum modulation frequency:

$$\Delta I = \frac{\Delta VT}{2L}$$

where

- $\Delta I$  is the ripple current

- $\Delta V$  is the voltage across the inductor

- L is the inductance

- T is the time period of modulation

(1)

This analysis yields an inductance value of 84 nH which is practically achievable. The inductor value can be scaled up to get a lower peak-to-peak current ripple. The saturation derating increases the inductance requirement to 1.4 times the theoretically calculated value. Another variation to be accounted for is component tolerance which can vary by 20% in typical inductors and up to 30% in some. The inductor of choice is PA4334.221NLT which has inductance of 220 nH, a self resonant frequency of 328 MHz, and a footprint size of 3.2 mm × 3.2 mm. Accounting for tolerance, derating, and so forth, this inductor is expected to give less than 5% peak-to-peak ripple.

4. Choose snubber components: The PIN diode of choice is BAP65-02. It is chosen because of its ultra-low series inductance, small form factor, and very low capacitance. The Zener diode breakdown voltage is calculated by assuming 2-V forward bias voltage per laser diode. The voltage across the laser diodes is estimated at 8 V and the voltage across the high-speed PIN diode is estimated to be 1 V. A Zener diode of 9 V is selected and connected to ground. If wasting power dissipation in the snubber components is not desired, some of the energy can be sequestered by connecting an appropriately-calculated Zener diode back into the laser power supply. In this design, a 5-V Zener diode can be connected back into the laser power source which has a voltage of 4 V. A high-frequency capacitor is added in parallel with the Zener diode, providing the high-frequency current path for the snubber action. The Zener diode may connect to any region, but the capacitor should connect to the MOSFET source.

- Choose MOSFET gate driver: SN74LVC2T45 works well. It is able to drive the MOSFET gate at frequencies up to 80 MHz. The chip scale package has the lowest inductance and is easy to place in the invariably cramped space around the lasers.

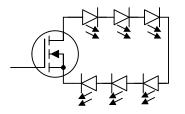

- 6. **Place all the illuminators:** The most important current loop to optimize for is the one with the illuminators. So the first step is to identify where the lasers/LEDs should be on the board and place them along with the high-speed switching MOSFET. It is important to place them as close as possible to each other. Sometimes, there are mechanical constraints like openings in external casings, and so forth, which necessitate some gap between components. However, care must be taken that they are not too far away from each other. For instance, placing illuminators on opposite sides of the lens reduces the shadowing effect. But it does not work electrically, as it will invariably cause the PCB parasitic inductance to be very high. A good way to place 6 LEDs/lasers is shown in Figure 12.

Figure 12. Good LED Placement

Figure 13. Sub-Optimal LED Placement

The high-speed switching MOSFET placement is also linked into this optimization and must be incorporated into this step.

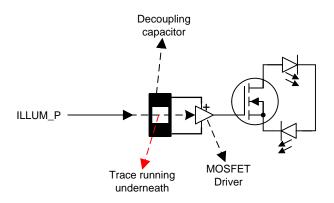

7. Place the MOSFET driver: This is the second most important current loop and needs to be placed next. Again, the MOSFET driver, its decoupling capacitor, and the MOSFET gate should be such that the current loops are the shortest. It is not always easy to optimize this because the ground pin on the MOSFET driver is sometimes inconveniently located. It might make sense to make the decoupling capacitor skip across a net to make sure this connection is made optimal. An example of the same with approximate relative physical placement is shown in Figure 14.

SBAA209B-August 2016-Revised August 2019 Submit Documentation Feedback

#### Switching Topologies

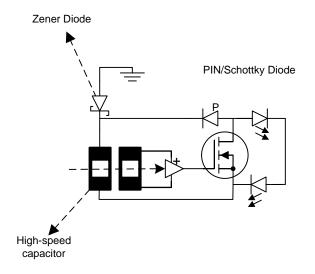

8. **Place the snubber components:** The snubber circuit ensures predictable operation of the driver. This is the third part of the placement. One must ensure that the high-speed diode and a high self resonant frequency ceramic capacitor are optimized in the layout. This takes care of efficient operation of the snubber. Figure 15 shows how to place and route the snubber:

## Figure 15. Snubber Placement

The Zener diode does not conduct high frequency currents and its placement is not critical. It can be placed wherever convenient.

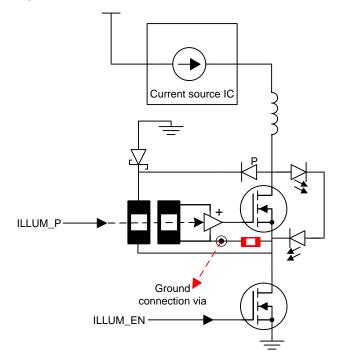

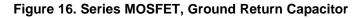

9. Integrate the entire circuit: The next step is to understand how to integrate the current source and the rest of the circuitry. Depending on design decisions, it might be required to add another series MOSFET which can block the current flow, when necessary. In this case, Figure 16 shows an example of a recommended layout:

Figure 17. Layout to Scale

Important points to note include:

- 1. There should not be any gaps between the copper traces. This minimizes the area of the current loops. Leaving gaps will only increase the parasitic inductance.

- 2. The MOSFET must be placed such that the loop area can be minimized. Most of the optimization is done at the placement stage.

- 3. The lasers are not kept at minimum gap. This is done intentionally for heat dissipation. In the case where the PCB dissipates heat very well, the lasers may be moved closer for better performance.

The capacitor in red, the ground return capacitor, lies in the ground return path for the MOSFET gate driver. This has to be placed such that the current loop length does not increase. The ground return capacitor should be of a value at least 5 times larger than the MOSFET gate capacitance and should have very high self resonant frequency. The current source IC, series inductor, and series MOSFET do not conduct high-frequency currents. These can be placed where it is convenient. The connections between the current source, inductor, and series MOSFET will typically carry large currents and wide traces should be used for the same. Figure 18 shows a recommended layout if a series MOSFET is not used for disconnecting the supply:

Figure 18. No Series MOSFET

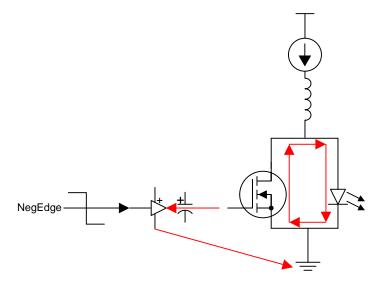

# 3.2 Series Switching

The only reason to use this architecture is to avoid the high frequency inductor. This topology is useful for implementing very small scale, simple circuits. The advantages follow:

- 1. High-frequency inductor is not required.

- 2. The current requirement from the power source is half of the peak emitter current required. This helps when it is difficult to find higher current capable power sources.

The disadvantages follow:

- 1. This design is not scalable into multiple emitters or high currents as the lowest emitter gets a reverse bias 'kick' from the parasitic inductance and capacitance. It has to be alleviated by using a fast reverse conduction diode. There is a problem because the diode is depended on for circuit functionality.

- 2. The output optical power will change with frequency, temperature, component to component differences, and so forth.

- 3. With a voltage source, the laser/LED can have a problem with thermal runaway. However, it is improbable that his happens at low integration duty cycles.

- 4. An equivalent specification circuit with shunt switching will have better EMI rating.

TI recommends that series-switching topology be used only if it is a low-power simple system which is limited in BOM cost.

# 3.2.1 Component Choice

A list of the crucial components and the concerns while choosing each follows:

1. **Power MOSFET:** Typical discrete power MOSFETs are designed to be used at frequencies of up to 5 MHz. Commonly available MOSFETs will typically have a high gate capacitance and package inductance for our use-case. In the interest of efficiency, look for a MOSFET with a very low gate capacitance. The VDS specification of the MOSFET should be at least to 3 V higher than the power supply rail connected to the emitter. A rough estimate of the power consumption by the MOSFET comes from the equation:  $P = 0.5 \times R_{DS} \times I^2 + C_G \times V^2 \times f$ . This formula will help in choosing a MOSFET. The formula might not accurately model the actual power losses. A good way to shortlist a MOSFET is to download the list of MOSFETs as an excel sheet and use the excel function features to find the best MOSFET for the cause. Gate series resistance is another cause for concern. It is observed that the gate series resistance in some of the power MOSFETs is too high for the MOSFET to be switched at frequencies up to 80 MHz.

2. **Supply AC decoupling capacitor:** The supply decoupling capacitor is a critical part of this circuit. It has to ensure that the voltage supply has a low impedance at the high-frequency currents taken by the Illumination Driver Circuit. The capacitor has to be chosen such that it can support the high frequency, high pulse current requirement of the *Series Switching Circuit*. It is important to look at the impedance versus frequency curve of the capacitor and ensure that it has a low enough impedance at the frequencies of interest. The highest frequency component of the current waveform comes from the edge rates of the current. A rough guideline for maximum frequency of interest is:  $f_{MAX} = 1 / (T_R \times \pi)$ .

# 3.2.2 Board Physical Design

Physical design is an important part of the illumination circuit design process. The circuit is heavily limited by the parasitic inductance in terms of current rise/fall times and ringing. The primary aim of the physical design on this circuit is to minimize the parasitic inductance in the critical switching current path. The current rise and fall rates can be in a few GA/s. That means even a few nH of inductance would be a considerable parasitic inductance to drive. The underlying constraints are the same as the constraints for the shunt switching circuit. However, one difference is that the supply decoupling capacitor is an important part of the high-frequency switching currents. This has to be accounted for in the critical current loops.

# 4 Power Supply Design

The power supply to the lasers has to take a voltage source as an input and give constant current as an output. There are multiple options for current source ICs. The following list includes those which have worked well in experiments:

- 1. **LM3409:** This is a useful buck DCDC converter which is meant as a current source supply for LEDs. Connecting ILLUM\_EN to enable input of the LM3409 is very useful in saving on switching losses when the converter is not needed. This can be used with both lasers and LEDs for peak currents up to 5 A.

- TPS92515: This is quite like the LM3409, except the MOSFET is integrated into the die. This is useful for peak current limits up to 2 A. ILLUM\_EN should again be connected to the enable input of this IC to save on switching losses and also to ensure the output voltage does not rise too high during operation.

- 3. **LM3429:** This is a boost converter which works as a current source. This can supply peak output currents up to 5 A. This converter is useful when the power supply voltage is limited to a value lower than what is required for driving the lasers or LEDs. This is a less efficient and more expensive solution as compared to the buck converters. It is a better idea to plan the power supplies such that only buck converters are required to power the lasers. OPT8241-CDK-EVM is an example of how this device can be used as a supply current source.

- 4. **TPS2559:** In some cases, the input voltage source is just a few 100s of mV above the laser drive requirement. In such a case, the buck converter might be too complex to use. The TPS2559 is a current-limiting load switch. It also doubles up as a very useful current limiter. This works as a linear current limiter circuit and provides a very simple solution as a current source.

ILLUM\_EN cannot be used to enable or disable this device as it does not respond as quickly. The OPT8241-CDK-EVM is an example of how this device can be used as a supply current source.

**NOTE:** The average output voltage of the power supply current source will be half of the total forward bias voltages of the 4 illuminators. This happens because the current source is connected to a series inductor on the outside and the lasers are "ON" with a duty cycle of 50%. The inductor current does not change at the modulation frequency. So the output voltage of the power stays at a relatively constant value. This average output voltage is half the maximum voltage on the emitter side of the inductor as the duty cycle is 50%. For example, a series string of 6 SFH4715AS LEDs will result in an average voltage of 9 V–10 V on the output of the current source IC.

Page

Page

# 5 Conclusion

Careful design of illumination drivers is critical to the system performance. It is important that the illumination driver be designed very carefully to be able to achieve the performance of which the chipset is capable. The required emphasis should be given to all parts of the design, this includes both component choice and PCB physical design.

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from A Revision (October 2016) to B Revision

#### Changes from Original (August 2016) to A Revision

| • | Changed Figure 3.              | 4 |

|---|--------------------------------|---|

| • | Changed Figure 6 and Figure 7. | 7 |

| • | Changed Figure 8 and Figure 9. | 8 |

| • | Changed Figure 11.             | 9 |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated