Analog Engineer's Circuit: Data Converters SBAA336A-December 2018-Revised March 2020

# Four-wire PT100 RTD measurement circuit with low-side reference

Joseph Wu

| Power Supplies |            |             |  |  |  |

|----------------|------------|-------------|--|--|--|

| AVDD           | AVSS, DGND | DVDD, IOVDD |  |  |  |

| 3.3V           | 0V         | 3.3V        |  |  |  |

#### **Design Description**

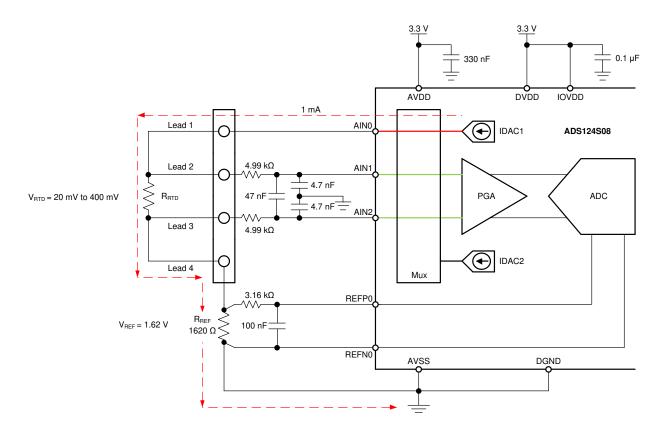

This cookbook design describes a temperature measurement for a four-wire RTD using the ADS124S08. This design uses a ratiometric measurement for a PT100 type RTD with a temperature measurement range from –200°C to 850°C. The four-wire RTD measurement is the most accurate of the RTD wiring configurations because the lead-resistance is not a factor in the measurement. Included in this design are ADC configuration register settings and pseudo code to configure and read from the device. This circuit can be used in applications such as *analog input modules* for PLCs, *lab instrumentation*, and *factory automation*. For more information about making precision ADC measurements with a variety of RTD wiring configurations, see *A Basic Guide to RTD Measurements*.

SBAA336A-December 2018-Revised March 2020 Submit Documentation Feedback

#### **Design Notes**

- Use supply decoupling capacitors for both the analog and digital supplies. AVDD must be decoupled with at least a 330-nF capacitor to AVSS. DVDD and IOVDD (when not connected to DVDD) must be decoupled with at least a 0.1-μF capacitor to DGND. See the *ADS124S0x Low-Power, Low-Noise, Highly Integrated, 6- and 12-Channel, 4-kSPS, 24-Bit, Delta-Sigma ADC with PGA and Voltage Reference* data sheet for details on power supply recommendations.

- 2. Do not route the excitation currents through input filter resistors, using the same pin as an ADC input and as the output for an IDAC current source. Excitation currents reacting with series resistance adds error to the measurement.

- 3. A 1-µF capacitor is required between REFOUT and REFCOM to enable the internal reference for the IDAC current.

- 4. Use a precision reference resistor with high accuracy and low drift. Because the measurement is ratiometric, accuracy is dependent on the error of this reference resistor. A 0.01% resistor contributes a gain error similar to that as the ADC.

- 5. When possible, use C0G (NPO) ceramic capacitors for input filtering. The dielectric used in these capacitors provides the most stable electrical properties over voltage, frequency, and temperature changes.

- 6. Input filtering for the ADC inputs and the reference inputs are selected using standard capacitor values and 1% resistor values. An example design and analysis of these filters is found in the *RTD Ratiometric Measurements and Filtering Using the ADS1148 and ADS1248 Family of Devices* application report.

- 7. This design shows connections to three input pins of the ADC multiplexer. Remaining analog inputs may be used for RTD, thermocouple, or other measurements.

- 8. The design for the four-wire RTD measurement is identical to the two-wire RTD measurement but requires four terminal connections and eliminates the lead-resistance error. For measurements with different RTD wiring configurations, see *A Basic Guide to RTD Measurements*.

#### **Component Selection**

1. Identify the range of operation for the RTD.

As an example, a PT100 RTD has a range of approximately  $20\Omega$  to  $400\Omega$  if the temperature measurement range is from  $-200^{\circ}$ C to  $850^{\circ}$ C. The reference resistor must be larger than the maximum RTD value. The reference resistance and PGA gain determines the positive full scale range of the measurement.

2. Determine values for the IDAC excitation current and reference resistor.

In this design, the IDAC current source drives the RTD through lead 1. The current exits the RTD through lead 4 and is shunted by  $R_{REF}$  to create a ratiometric measurement. The measurement is made between lead 2 and lead 3 by the ADC, making a Kelvin connection to remove the lead resistance error. With this four-terminal sensing, the 4-wire RTD measurement is the most accurate of the RTD wiring configurations.

The excitation current source in this design is selected to be 1mA. This maximizes the value of the RTD voltage while keeping the self-heating of the RTD low. The typical range of RTD self-heating coefficients is 2.5mW/°C for small, thin-film elements and 65mW/°C for larger, wire-wound elements. With 1-mA excitation at the maximum RTD resistance value, the power dissipation in the RTD is less than 0.4mW and keeps the measurement errors from self-heating to less than 0.01°C.

After selecting the IDAC current magnitude, set  $R_{REF} = 1620\Omega$ . This sets the reference at 1.62V and the maximum RTD voltage is 400mV. The reference voltage acts as a level shift to place the input measurement to near mid-supply, putting the measurement in the PGA input operating range. With these values, the PGA gain can be set to 4 so that the maximum RTD voltage is near the positive full scale range without exceeding it.

The reference resistor,  $R_{REF}$  must be a precision resistor with high accuracy and low drift. Any error in  $R_{REF}$  reflects the same error in the RTD measurement. The REFP0 and REFN0 pins are shown connecting to the  $R_{REF}$  resistor as a Kelvin connection to get the best measurement of the reference voltage. This eliminates any series resistance as an error from the reference resistance measurement.

2

www.ti.com

Using the maximum RTD resistance, the ADC input voltages are calculated in the following:

$V_{\text{AIN1}} = I_{\text{IDAC1}} \bullet (R_{\text{RTD}} + R_{\text{REF}}) = 1\text{mA} \bullet (400\Omega + 1620\Omega) = 2.02\text{V}$

$V_{AIN2} = I_{IDAC1} \bullet R_{REF} = 1mA \bullet 1620\Omega = 1.62V$

$V_{INMAX} = 1mA \bullet 400\Omega = 400mV$

3. Verify that the design is within the range of operation of the ADC.

First, verify that V<sub>AIN1</sub> and V<sub>AIN2</sub> are within the input range of the PGA given that the gain is 4 and that AVDD is 3.3V and AVSS is 0V. As the *ADS124S0x Low-Power, Low-Noise, Highly Integrated, 6- and 12-Channel, 4-kSPS, 24-Bit, Delta-Sigma ADC with PGA and Voltage Reference* data sheet shows, the absolute input voltage must satisfy the following:

$\begin{array}{l} \text{AVSS} + 0.15\text{V} + [|V_{\text{INMAX}}| \bullet (\text{Gain} - 1) / 2] < V_{\text{AIN1}}, V_{\text{AIN2}} < \text{AVDD} - 0.15\text{V} - [|V_{\text{INMAX}}| (\text{Gain} - 1) / 2] \\ \text{OV} + 0.15\text{V} + [|V_{\text{INMAX}}| \bullet (\text{Gain} - 1) / 2] < V_{\text{AIN1}}, V_{\text{AIN2}} < 3.3\text{V} - 0.15\text{V} - [|V_{\text{INMAX}}| (\text{Gain} - 1) / 2] \\ \text{O.75} < V_{\text{AIN1}}, V_{\text{AIN2}} < 2.55\text{V} \end{array}$

Because the maximum and minimum input voltages seen at AIN1 and AIN2 (2.02 V and 1.62 V) are between 0.75V and 2.55V, the inputs are in the PGA operating range.

Second, verify that the voltage at the IDAC output pin is within the current source compliance voltage. The IDAC pin is AIN0, which have the same voltage as AIN1. At the maximum voltage,  $V_{AIN0}$  is 2.02V. As shown in the Electrical Characteristics table in the *ADS124S0x Low-Power, Low-Noise, Highly Integrated, 6- and 12-Channel, 4-kSPS, 24-Bit, Delta-Sigma ADC with PGA and Voltage Reference* data sheet, the output voltage of the IDAC must be between AVSS and AVDD – 0.6V for an IDAC current of 1mA. In this example, with AVDD = 3.3V, the IDAC output must be:

$AVSS < V_{AIN0} = V_{AIN1} < AVDD - 0.6V$

$$0V < V_{AIN0} < 2.7V$$

With the above result, the output compliance of the IDAC is satisfied.

4. Select values for the differential and common-mode filtering for the ADC inputs and reference inputs.

This design includes differential and common-mode input RC filtering. The bandwidth of the differential input filtering is set to be at least 10 × higher than the data rate of the ADC. The common-mode capacitors are selected to be 1/10 of the value the differential capacitor. Because of capacitor selection, the bandwidth of common-mode input filtering is approximately 20 × higher than the differential input filtering. While series filter resistors offer some amount of input protection, keep the input resistors lower than  $10k\Omega$ , to allow for proper input sampling for the ADC.

With input filtering, differential signals are attenuated at a lower frequency than the common-mode signals, which are significantly rejected by the PGA of the device. Mismatches in common-mode capacitors cause an asymmetric noise attenuation, appearing as a differential input noise. With a lower bandwidth for differential signals, the effects from the mismatch of input common-mode capacitors be reduced. Input filtering for the ADC inputs and reference inputs are designed for the same bandwidth.

In this design, the data rate is chosen to be 20SPS using the low-latency filter of the ADS124S08. This filtering provides a low noise measurement with single-cycle settling and the ability to reject 50-Hz and 60-Hz line noise. For the ADC input filtering, the bandwidth frequency for the differential and common-mode filtering is approximated in the following equations.

$f_{\text{IN_DIFF}} = 1 / [2 \bullet \pi \bullet C_{\text{IN_DIFF}} (R_{\text{RTD}} + 2 \bullet R_{\text{IN}})]$

$f_{\text{IN}_{CM}} = 1 / [2 \bullet \pi \bullet C_{\text{IN}_{CM}} (R_{\text{RTD}} + R_{\text{IN}} + R_{\text{REF}})]$

For the ADC input filtering,  $R_{IN} = 4.99k\Omega$ ,  $C_{IN_{DIFF}} = 47nF$ , and  $C_{IN_{CM}} = 4.7nF$ . This sets the differential filter bandwidth to 330Hz and the common-mode filter bandwidth to 5kHz.

The bandwidth for the reference input filtering is approximated in the following equation.

$f_{REF} = 1 / [2 \bullet \pi \bullet C_{REF} \bullet (R_{REF} + R_{IN_REF})]$

For the reference input filtering,  $R_{IN\_REF} = 3.16k\Omega$  and  $C_{REF\_DIFF} = 100$ nF. This sets the reference filter bandwidth to 330Hz. Because REFN0 is set to ground, the common-mode filtering is removed. Matching the ADC input and reference input filtering may not be possible. However, keeping the bandwidths close may reduce the noise in the measurement.

For an in-depth analysis of component selection for input filtering, see the *RTD Ratiometric Measurements and Filtering Using the ADS1148 and ADS1248 Family of Devices* application report.

#### **Measurement Conversion**

RTD measurements are typically ratiometric measurements. Using a ratiometric measurement, the ADC output code does not need to be converted to a voltage. This means that the output code gives a measurement only as a ratio of the value of the reference resistor and does not require a precise value for the excitation current. The only requirement is that the current through the RTD and reference resistor are the same.

Equations for the measurement conversion are shown for a 24-bit ADC:

Output Code =  $2^{23} \cdot \text{Gain} \cdot (\text{V}_{\text{RTD}} / \text{V}_{\text{REF}}) = 2^{23} \cdot \text{Gain} \cdot (\text{I}_{\text{IDAC1}} \cdot \text{R}_{\text{RTD}}) / (\text{I}_{\text{IDAC1}} \cdot \text{R}_{\text{REF}}) = 2^{23} \cdot \text{Gain} \cdot (\text{R}_{\text{RTD}} / \text{R}_{\text{REF}})$  $R_{RTD} = R_{REF} \bullet [Output Code / (Gain \bullet 2^{23})]$

The ADC converts the measurement to the RTD equivalent resistance. Because of non-linearity in the RTD response, the conversion of the resistance to temperature requires an calculation from equation or lookup table. For more information about the conversion of RTD resistance to temperature, see A Basic Guide to RTD Measurements.

#### **Register Settings**

4

Configuration Register Settings for a Four-Wire PT100 RTD Measurement Circuit with Low-Side Reference Using the ADS124S08

| Register<br>Address | Register Name | Setting | Description                                                                                                                                          |

|---------------------|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02h                 | INPMUX        | 12h     | Select $AIN_P = AIN1$ and $AIN_N = AIN2$                                                                                                             |

| 03h                 | PGA           | 0Ah     | PGA enabled, Gain = 4                                                                                                                                |

| 04h                 | DATARATE      | 14h     | Continuous conversion mode, low-latency filter, 20-SPS data rate                                                                                     |

| 05h                 | REF           | 12h     | Positive reference buffer enabled, negative reference buffer disabled,<br>REFP0 and REFN0 reference inputs selected, internal reference<br>always on |

| 06h                 | IDACMAG       | 07h     | IDAC magnitude set to 1mA                                                                                                                            |

| 07h                 | IDACMUX       | F0h     | IDAC1 set to AIN0, IDAC2 disabled                                                                                                                    |

| 08h                 | VBIAS         | 00h     | VBIAS not used for any input                                                                                                                         |

| 09h                 | SYS           | 10h     | Normal mode of operation                                                                                                                             |

#### www.ti.com

#### Pseudo Code Example

The following shows a pseudo code sequence with the required steps to set up the device and the microcontroller that interfaces to the ADC to take subsequent readings from the ADS124S0x in continuous conversion mode. The dedicated DRDY pin indicates availability of new conversion data. Pseudo code is shown without the use of the STATUS byte and CRC data verification. ADS124S08 firmware example code is available from the ADS124S08 product folder.

```

Configure microcontroller for SPI mode 1 (CPOL = 0, CPHA = 1)

Configure microcontroller GPIO for /DRDY as a falling edge triggered interrupt input

Set CS low;

// RESET command to make sure the device is properly reset after power-up

Send 06;

Set CS high;

Set CS low;

// Configure the device

// WREG starting at 02h address

Send 42

// Write to 6 registers

05

12

// Select AINP = AIN1 and AINN = AIN2

0A

// PGA enabled, Gain = 4

14

// Continuous conversion mode, low-latency filter, 20-SPS data rate

12

// Positive reference buffer enabled, negative reference buffer disabled

// REFP0 and REFN0 reference selected, internal reference always on

07

// IDAC magnitude set to 1 mA

F0;

// IDAC1 set to AIN0, IDAC2 disabled

Set CS high;

Set CS low;

// For verification, read back configuration registers

Send 22

// RREG starting at 02h address

05

// Read from 6 registers

00 00 00 00 00 00; // Send 6 NOPs for the read

Set CS high;

Set CS low;

Send 08;

// Send START command to start converting in continuous conversion mode;

Set CS high;

Loop

{

Wait for DRDY to transition low;

Set CS low;

Send 12

// Send RDATA command

00 00 00; // Send 3 NOPs (24 SCLKs) to clock out data

Set CS high;

Set CS low;

//STOP command stops conversions and puts the device in standby mode;

Send OA;

Set CS to high;

```

5

## **RTD Circuit Comparison Table**

| RTD Circuit Topology                                                | Advantages                                                                                             | Disadvantages                                                                                                        |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Two-wire RTD, low-side reference                                    | Least expensive                                                                                        | Least accurate, no lead-resistance cancellation                                                                      |  |

| Three-wire RTD, low-side<br>reference, two IDAC<br>current sources  | Allows for lead-resistance cancellation                                                                | Sensitive to IDAC current mismatch, mismatch can be removed by swapping IDAC currents and averaging two measurements |  |

| Three-wire RTD, low-side<br>reference, one IDAC<br>current source   | Allows for lead-resistance cancellation                                                                | Requires two measurements, first for RTD measurement, second for lead-resistance cancellation                        |  |

| Three-wire RTD, high-side<br>reference, two IDAC<br>current sources | Allows for lead-resistance cancellation, less sensitive to IDAC mismatch than using low side reference | Requires extra resistor for biasing, added voltage may not be compatible with low supply operation                   |  |

| Four-wire RTD, low-side reference                                   | Most accurate, no lead-resistance error                                                                | Most expensive                                                                                                       |  |

## **Design Featured Devices**

| Device                   | Key Features                                                                                            | Link                         | Other Possible<br>Devices |

|--------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|

| ADS124S08                | 24-Bit, 4kSPS, 12-Ch Delta-Sigma ADC With PGA and Voltage<br>Reference for Precision Sensor Measurement | www.ti.com/product/ADS124S08 | Link to similar devices   |

| ADS114S08 <sup>(1)</sup> | 16-Bit, 4kSPS, 12-Ch Delta-Sigma ADC With PGA and Voltage<br>Reference for Precision Sensor Measurement | www.ti.com/product/ADS114S08 | Link to similar devices   |

(1) The ADS114S08 is a 16-bit version of the ADS124S08 and may be used in similar applications.

## **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

#### **Additional Resources**

- Texas Instruments, ADS124S08 Evaluation Module ٠

- Texas Instruments, ADS1x4S08 Evaluation Module User's Guide

- Texas Instruments, ADS1x4S08 Firmware Example Code .

- Texas Instruments, A Basic Guide to RTD Measurements Application Report ٠

- Texas Instruments, RTD Ratiometric Measurements and Filtering Using the ADS1148 and ADS1248 Family of Devices Application Report

## For direct support from TI Engineers use the E2E community

e2e.ti.com

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Original (December 2018) to A Revision Changed schematic to remove filtering from REFN0.....

Page

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated