Analog Engineer's Circuit: Data Converters SBAA342A–January 2019–Revised September 2019

# Power-supply margining circuit for SMPS using a precision DAC

Uttama Kumar Sahu

#### **Design Goals**

| Power Supply (DAC<br>VDD) | Nominal Output | Margin High | Margin Low |

|---------------------------|----------------|-------------|------------|

| 5V                        | 5V             | 5V + 10%    | 5V – 10%   |

#### **Design Description**

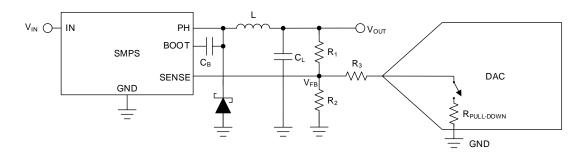

A power-supply margining circuit is used for tuning the output of a power converter. This is done either to adjust the offset and drift of the power-supply output or to program a desired value at the output. Adjustable power supplies like LDOs and DC/DC converters provide a feedback or adjust input that is used to set the desired output. A precision voltage output DAC is suitable for controlling the power-supply output linearly. An example power-supply margining circuit is shown in the following figure. Typical applications of power-supply margining is in Test and Measurement, Communications Equipment, and General Purpose Power Supply Modules.

#### **Design Notes**

- 1. Choose a DAC with required resolution, pulldown resistor value, and output range

- 2. Derive the relationship of the DAC output to  $V_{OUT}$

- 3. Choose R<sub>1</sub> based on typical current through the feedback circuit

- 4. Calculate the start-up or nominal value of  $V_{DAC}$ , considering the power-down and power-up conditions of the DAC

- 5. Select R<sub>2</sub>, and R<sub>3</sub> such that the desired start-up output voltage is met along with the DAC output voltage range for the desired tuning range

- 6. Calculate the margin low and margin high DAC outputs

- 7. Choose a compensation capacitor to get the desired step response

#### **Design Steps**

- 1. Select the switching DC/DC converter TPS5450 for the calculations. The DAC53608 device is an ultralow cost, 10-bit, 8-channel unipolar output DAC suitable for such applications

- 2. The output voltage of the power supply is given by

$$V_{OUT} = V_{REF} + I_1 R_1 = V_{REF} + (I_2 + I_3) R_1$$

where

- $I_1$  is the current flowing through  $R_1$

- I<sub>2</sub> is the current flowing through R<sub>2</sub>

- I<sub>3</sub> is the current flowing through R<sub>3</sub>

DACs in this application typically include power-down mode, which includes an internal pulldown resistor at the voltage output. Hence, replacing the values of the currents in the previous equation yields:

• When DAC is in power-down mode:

$$V_{OUT} = V_{REF} + \left( \left( \frac{V_{REF}}{R_2} \right) + \left( \frac{V_{REF}}{R_3 + R_{PULL-DOWN}} \right) \right) R_1$$

• When DAC output is powered-up:

$$V_{OUT} = V_{REF} + \left( \left( \frac{V_{REF}}{R_2} \right) + \left( \frac{V_{REF} - V_{DAC}}{R_3} \right) \right) R_1$$

For DAC53608,  $R_{PULLDOWN}$  is 10k $\Omega$ . For the LDO device TPS5450, the value of  $V_{REF}$  is 1.221V.

R<sub>1</sub> can be calculated with the following method: The current through the FB pin of the TPS5450 device is negligible. Select I<sub>1</sub> to be 50μA. So, R<sub>1</sub> is calculated as follows:

$$R_{1} = \frac{V_{OUT} - V_{REF}}{I_{1}} = 75.6 \text{ k}\Omega$$

The nominal value of  $I_1$  is given by:

• When DAC is in power-down mode:

$$I_{1-Nom} = \left(\frac{V_{REF}}{R_2}\right) + \left(\frac{V_{REF}}{R_3 + 10 \text{ k}\Omega}\right)$$

• When DAC output is powered-up:

$$I_{1-Nom} = \left(\frac{V_{REF}}{R_2}\right) + \left(\frac{V_{REF} - V_{DAC}}{R_3}\right)$$

The values of  $I_1$  at margin high and margin low outputs are given by:

$$I_{1-HIGH} = \frac{V_{OUT-HIGH} - V_{REF}}{R_1} = 56.6 \mu A$$

$$I_{1-LOW} = \frac{V_{OUT-LOW} - V_{REF}}{R_1} = 43.4$$

$$I_{1-LOW} = \frac{V_{OUT-LOW} - V_{REF}}{R_1} = 43.4$$

4. The nominal, or startup value of  $V_{\text{DAC}}$  is calculated by the following method:

To make sure the 10-k $\Omega$  resistor does not impact when the DAC is transitioning from power-down to power-up, the power-up value for the DAC voltage is calculated with:

$$\frac{V_{REF}}{R_3 + 10 \text{ k}\Omega} = \frac{V_{REF} - V_{DAC}}{R_3}$$

The previous equation is further simplified to:

$$V_{DAC} = V_{REF} \left( \frac{10 \text{ k}\Omega}{\text{R}_3 + 10 \text{ k}\Omega} \right)$$

5. The values of  $R_2$  and  $R_3$  are calculated as follows:

If the power-up or nominal value of V<sub>DAC</sub> is kept at 1/3 of V<sub>REF</sub>, that is, 407mV, then R<sub>3</sub> is 2 × 10k $\Omega$  = 20k $\Omega$ . And, R<sub>2</sub> can be calculated as:

$$\frac{V_{REF}}{R_2} + \frac{V_{REF}}{R_3 + 10 \, k\Omega} = 50 \mu A$$

Replacing the value of  $R_3$ , calculate  $R_2 = 131.3$ k $\Omega$ .

6. Subtracting the margin high and nominal values of  $I_1$  and the corresponding equations yields:

$$\frac{V_{\text{REF}} - V_{\text{DAC}}}{R_3} - \frac{V_{\text{REF}}}{R_3 + 10 \text{ k}\Omega} = 6.6 \mu\text{A}$$

The margin high value of  $V_{DAC}$  is 275mV and similarly, the margin low value is calculated as 539mV using the following equation:

$$\frac{V_{REF}}{R_3 + 10 \ k\Omega} - \frac{V_{REF} - V_{DAC}}{R_3} - = 6.6 \mu A$$

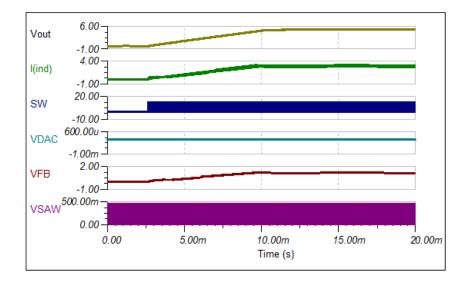

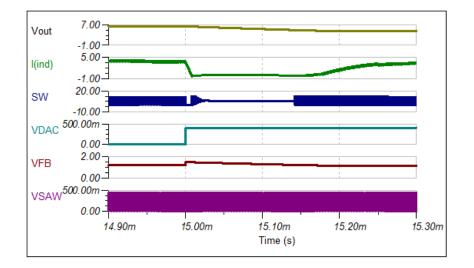

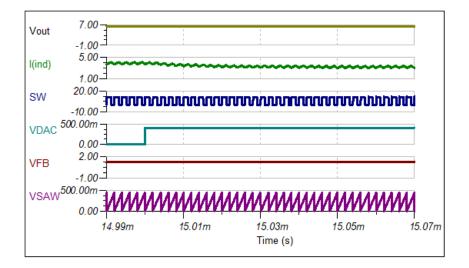

7. The step response of this circuit without a compensation capacitor causes the inductor current to reach its limit as shown in the following figure. This kind of surge can take the inductor into saturation. To minimize the surge, a compensation capacitor C<sub>1</sub> is used as the circuit diagram shows. The value of this capacitance is usually obtained through simulation. A comparative output shows the waveforms with a compensation capacitor of 10nF.

#### **Output With DAC in Power Down Mode**

#### **Small-Signal Step Response Without Compensation**

Small-Signal Step Response With C<sub>1</sub> = 10nF

#### **Design Featured Devices and Alternative Parts**

| Device   | Key Features                                                                                                                  | Link                              |

|----------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| DAC53608 | 8-channel 10-bit, I2C interface, buffered-voltage-output digital-to-analog converter (DAC) http://www.ti.com/product/DAC53608 |                                   |

| DAC60508 | 8-channel, true 12-bit, SPI, voltage-output DAC With precision internal reference http://www.ti.com/product/DAC60508          |                                   |

| DAC60501 | 12-bit, 1-LSB INL, digital-to-analog converter (DAC) with precision internal reference http://www.ti.com/product/DAC60501     |                                   |

| DAC8831  | 16-bit, ultra-low power, voltage output digital to analog converter                                                           | http://www.ti.com/product/DAC8831 |

| TPS5450  | 5.5-V to 36-V input, 5-A, 500-kHz step-down converter                                                                         | http://www.ti.com/product/TPS5450 |

#### **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

#### Link to Key Files

TINA source files - http://www.ti.com/lit/zip/sbam416.

### For direct support from TI Engineers use the E2E community

#### e2e.ti.com

## **Revision History**

| Revision | Date           | Change                                       |

|----------|----------------|----------------------------------------------|

| A        | September 2019 | Updated the circuit image on the first page. |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated