# Configuring and Operating TLV320ADCx140 as Audio Bus Master

#### 1 Introduction

The TLV320ADCx140 is a family of quad-channel audio analog to digital converters. This device family features a flexible audio serial interface that allows the device to be configured as either a master or slave. This document describes the modes, input parameters, and register coefficients required to configure the TLV320ADCx140 devices as an audio bus master.

#### 2 Master Mode

For I<sup>2</sup>S-based digital audio communication protocols, the master device generates the clocks: bit clock (BCLK) and word clock (WCLK) (or frame synchronization, FSYNC). On the other hand, a slave device receives the clocks: BCLK and WCLK (or FSYNC) from an external device. In many applications, a host processor with an advanced digital audio interface can act as the audio bus master with the TLV320ADCx140 as a slave device. However, having the audio ADC as the audio bus master is advantageous in the following circumstances:

- The host processor or DSP cannot output or generate standard audio clocks. A standard audio clock is an integer multiple of the sample rate that generates the necessary audio serial interface (ASI) FSYNC and BCLK clocks. In this case, an external PLL multiplier generates the appropriate audio clocks.

- To easily synchronize multiple TLV320ADCx140 devices for simultaneous recording across all channels and devices. In this case, one TLV320ADCx140 device is configured as a master to generate low jitter ASI clocks.

- The host does not have a flexible TDM/ASI bus to generate system required audio clocks, but allows these clocks as input when configured as a slave device.

The following sections describe the modes, input parameters, or register settings required to configure the device as an audio bus master.

#### 2.1 Master Mode Configuration Options

The TLV320ADCx140 supports two functional modes when configured as an ASI master:

- Auto Clock Generation with Internal PLL enabled. Enabling the PLL allows the auto clock generator engine to generate a system clock that can be greater than the provided MCLK.

- Auto Clock Generation with internal PLL disabled. Disabling the PLL limits the system clock to the MCLK frequency.

The system clock feeds the decimation filters and all the digital signal processing blocks (biquad filters, digital volume control, high pass filters, and so forth). Disabling the PLL limits the amount of digital signal processing available. However, with the low jitter PLL disabled, the performance of the ADC can be degraded based on the jitter from the external clock source. For devices configured as master mode in high performance applications, the recommended operating mode is to enable the PLL.

Configuring the TLV320ADCx140 as an ASI master requires that GPIO1 be configured as the MCLK input in GPIO\_CFG0 (page 0, register 0x21, Bits 7-4). The frequency of MCLK must be one of the supported frequencies or ratios supported by configuring the MCLK\_FREQ\_SEL frequency selection mode (page 0, MST\_CFG0 register 0x13, Bits 2-0), as shown in Table 1. Note that when using auto clock generation with internal PLL disabled, MCLK\_RATIO\_SEL (page 0, CLK\_SRC register 0x16, bits 5-3) must also be configured.

Master Mode www.ti.com

Table 1. MCLK Frequency Selection Mode with Supported Frequencies or Ratios

| MCLK FREQUENCY SELECTION MODE                            | SUPPORTED FREQUENCIES OR RATIOS                                             |

|----------------------------------------------------------|-----------------------------------------------------------------------------|

| MCLK_FREQ_SEL (page 0, MST_CFG0 register 0x13, bits 2-0) | 12 MHz, 12.288 MHz, 13 MHz, 16 MHz, 19.2 MHz, 19.68 MHz, 24 MHz, 24.576 MHz |

| MCLK_RATIO_SEL (page 0, CLK_SRC register 0x16, bits 5-3) | 64, 256, 384, 512, 786, 1024, 1536, 2304                                    |

### 2.1.1 Auto Clock Configuration with PLL Enabled

The auto clock configuration engine requires four user-provided parameters to generate the proper ASI clocks when the device is configured in master mode, as shown in Table 2.

Table 2. Required Input Parameters for Master mode Auto Clock Configuration with PLL Enabled

| USER PROVIDED PARAMETER                            | REGISTER                                 |  |  |  |

|----------------------------------------------------|------------------------------------------|--|--|--|

| MCLK Frequency                                     | Page 0, MST_CFG0 Register 0x13, bits 2-0 |  |  |  |

| Sampling Rate (FS) mode (multiple of 48k or 44.1k) | Page 0, MST_CFG0 Register 0x13, Bit 3    |  |  |  |

| FS_RATE                                            | Page 0, MST_CFG1 Register 0x14, Bits 7-4 |  |  |  |

| FSYNC-to-BCLK Ratio                                | Page 0, MST_CFG1 Register 0x14, Bits 3-0 |  |  |  |

### 2.1.1.1 Supported Sample-Rates

The supported sample-rates and BCLK/FSYNC ratios for multiples and sub-multiples of 48kHz are shown in Table 3.

Table 3. Supported FSYNC (Multiples or Sub-multiples of 48 kHz) and BCLK Frequencies

| BCLK-TO-       |                  |                   |                   |                   | BCLK (MHz)        |                   |                    |                    |                    |

|----------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--------------------|

| FSYNC<br>RATIO | FSYNC<br>(8 kHz) | FSYNC<br>(16 kHz) | FSYNC<br>(24 kHz) | FSYNC<br>(32 kHz) | FSYNC<br>(48 kHz) | FSYNC<br>(96 kHz) | FSYNC<br>(192 kHz) | FSYNC<br>(384 kHz) | FSYNC<br>(768 kHz) |

| 16             | Reserved         | 0.256             | 0.384             | 0.512             | 0.768             | 1.536             | 3.072              | 6.144              | 12.288             |

| 24             | Reserved         | 0.384             | 0.576             | 0.768             | 1.152             | 2.304             | 4.608              | 9.216              | 18.432             |

| 32             | 0.256            | 0.512             | 0.768             | 1.024             | 1.536             | 3.072             | 6.144              | 12.288             | 24.576             |

| 48             | 0.384            | 0.768             | 1.152             | 1.536             | 2.304             | 4.608             | 9.216              | 18.432             | Reserved           |

| 64             | 0.512            | 1.024             | 1.536             | 2.048             | 3.072             | 6.144             | 12.288             | 24.576             | Reserved           |

| 96             | 0.768            | 1.536             | 2.304             | 3.072             | 4.608             | 9.216             | 18.432             | Reserved           | Reserved           |

| 128            | 1.024            | 2.048             | 3.072             | 4.096             | 6.144             | 12.288            | 24.576             | Reserved           | Reserved           |

| 192            | 1.536            | 3.072             | 4.608             | 6.144             | 9.216             | 18.432            | Reserved           | Reserved           | Reserved           |

| 256            | 2.048            | 4.096             | 6.144             | 8.192             | 12.288            | 24.576            | Reserved           | Reserved           | Reserved           |

| 384            | 3.072            | 6.144             | 9.216             | 12.288            | 18.432            | Reserved          | Reserved           | Reserved           | Reserved           |

| 512            | 4.096            | 8.192             | 12.288            | 16.384            | 24.576            | Reserved          | Reserved           | Reserved           | Reserved           |

| 1024           | 8.192            | 16.384            | 24.576            | Reserved          | Reserved          | Reserved          | Reserved           | Reserved           | Reserved           |

| 2048           | 16.384           | Reserved          | Reserved          | Reserved          | Reserved          | Reserved          | Reserved           | Reserved           | Reserved           |

The supported sample-rates and BCLK/FSYNC ratios for multiples and sub-multiples of 44.1kHz are shown in Table 4.

Table 4. Supported FSYNC (Multiples or Sub-multiples of 44.1 kHz) and BCLK Frequencies

|   | BCLK-TO-<br>FSYNC<br>RATIO | FSYNC<br>(7.35 kHz) | FSYNC<br>(14.7 kHz) | FSYNC<br>(22.05<br>kHz) | FSYNC<br>(29.4 kHz) | FSYNC<br>(44.1 kHz) | FSYNC<br>(88.2 kHz) | FSYNC<br>(176.4<br>kHz) | FSYNC<br>(352.8<br>kHz) | FSYNC<br>(705.6<br>kHz) |

|---|----------------------------|---------------------|---------------------|-------------------------|---------------------|---------------------|---------------------|-------------------------|-------------------------|-------------------------|

|   | 16                         | Reserved            | Reserved            | 0.3528                  | 0.4704              | 0.7056              | 1.4112              | 2.8224                  | 5.6448                  | 11.2896                 |

| Ī | 24                         | Reserved            | 0.3528              | 0.5292                  | 0.7056              | 1.0584              | 2.1168              | 4.2336                  | 8.4672                  | 16.9344                 |

www.ti.com Master Mode

Table 4. Supported FSYNC (Multiples or Sub-multiples of 44.1 kHz) and BCLK Frequencies (continued)

|                            |                     |                     |                         |                     | BCLK (MHz)          |                     |                         |                         |                         |

|----------------------------|---------------------|---------------------|-------------------------|---------------------|---------------------|---------------------|-------------------------|-------------------------|-------------------------|

| BCLK-TO-<br>FSYNC<br>RATIO | FSYNC<br>(7.35 kHz) | FSYNC<br>(14.7 kHz) | FSYNC<br>(22.05<br>kHz) | FSYNC<br>(29.4 kHz) | FSYNC<br>(44.1 kHz) | FSYNC<br>(88.2 kHz) | FSYNC<br>(176.4<br>kHz) | FSYNC<br>(352.8<br>kHz) | FSYNC<br>(705.6<br>kHz) |

| 32                         | Reserved            | 0.4704              | 0.7056                  | 0.9408              | 1.4112              | 2.8224              | 5.6448                  | 11.2896                 | 22.5792                 |

| 48                         | 0.3528              | 0.7056              | 1.0584                  | 1.4112              | 2.1168              | 4.2336              | 8.4672                  | 16.9344                 | Reserved                |

| 64                         | 0.4704              | 0.9408              | 1.4112                  | 1.8816              | 2.8224              | 5.6448              | 11.2896                 | 22.5792                 | Reserved                |

| 96                         | 0.7056              | 1.4112              | 2.1168                  | 2.8224              | 4.2336              | 8.4672              | 16.9344                 | Reserved                | Reserved                |

| 128                        | 0.9408              | 1.8816              | 2.8224                  | 3.7632              | 5.6448              | 11.2896             | 22.5792                 | Reserved                | Reserved                |

| 192                        | 1.4112              | 2.8224              | 4.2336                  | 5.6448              | 8.4672              | 16.9344             | Reserved                | Reserved                | Reserved                |

| 256                        | 1.8816              | 3.7632              | 5.6448                  | 7.5264              | 11.2896             | 22.5792             | Reserved                | Reserved                | Reserved                |

| 384                        | 2.8224              | 5.6448              | 8.4672                  | 11.2896             | 16.9344             | Reserved            | Reserved                | Reserved                | Reserved                |

| 512                        | 3.7632              | 7.5264              | 11.2896                 | 15.0528             | 22.5792             | Reserved            | Reserved                | Reserved                | Reserved                |

| 1024                       | 7.5264              | 15.0528             | 22.5792                 | Reserved            | Reserved            | Reserved            | Reserved                | Reserved                | Reserved                |

| 2048                       | 15.0528             | Reserved            | Reserved                | Reserved            | Reserved            | Reserved            | Reserved                | Reserved                | Reserved                |

## 2.1.1.2 Example 12MHz MCLK

For a 12-MHz MCLK, the following I<sup>2</sup>C script configures the TLV320ADCx140 as master mode with GPIO1 as MCLK input for a 44.1-kHz or 48-kHz sampling rate:

```

w 98 21 a0 \# configure GPIO1 as MCLK input w 98 13 80 \# configure device as master with MCLK = 12 MHz w 98 14 48 \# FS = 44.1/48k BCLK/ratio = 256

```

#### 2.1.2 Auto Clock Detect with PLL Disabled

For the lowest power consumption, it can be desirable to disable the PLL and derive all clocks directly from MCLK. To disable the PLL in auto configuration mode, set bit 5 (AUTO\_MODE\_PLL\_DIS) in MST\_CFG0 (page 0, register 0x13). The required inputs for this mode are found in Table 5.

Table 5. Required Input Parameters for Master Mode Auto Clock Configuration with PLL Disabled

| USER PROVIDED PARAMETER | REGISTER                                 |

|-------------------------|------------------------------------------|

| FS MODE                 | Page 0, MST_CFG0 Register 0x13, Bit 3    |

| FS_RATE                 | Page 0, MST_CFG1 Register 0x14, Bits 7-4 |

| FS_BCLK_RATIO           | Page 0, MST_CFG1 Register 0x14, Bits 3-0 |

| MCLK_FREQ_SEL_MODE      | Page 0, CLK_SRC Register 0x16, Bit 6     |

| MCLK_RATIO_SEL          | Page 0, CLK_SRC Register 0x16, Bits 5-3  |

| MCLK_FREQ_SEL           | Page 0, MST_CFG0 Register 0x13, Bits 2-0 |

# 2.1.2.1 Supported Sample-Rates

Table 6 shows the supported sample-rates with the PLL disabled. As shown in Table 6, higher MCLK ratios allow the use of greater number or greater computation of digital processing blocks due to the greater availability of clocks in the system.

Table 6. Supported Sample Rates for Auto Clock Configuration with PLL Disabled

| SAMPLING<br>FREQUENCY<br>(kHz) | MCLK<br>FREQUENCY(MHz) | MCLK RATIO | ADC CHANNELS | DRE      | DECIMATION<br>FILTERS | BCLK RATIO | WORD LENGTH |

|--------------------------------|------------------------|------------|--------------|----------|-----------------------|------------|-------------|

| 0                              | 12.288                 | 1536       | 1            | Disabled | Linear Phase          | 32         | 32          |

| U                              | 12.200                 | 1330       | 2            | Disabled | Lilical Filase        | 48         | 24          |

Master Mode www.ti.com

Table 6. Supported Sample Rates for Auto Clock Configuration with PLL Disabled (continued)

| SAMPLING<br>FREQUENCY<br>(kHz) | MCLK<br>FREQUENCY(MHz) | MCLK RATIO | ADC CHANNELS | DRE      | DECIMATION<br>FILTERS | BCLK RATIO | WORD LENGTH |  |

|--------------------------------|------------------------|------------|--------------|----------|-----------------------|------------|-------------|--|

|                                |                        |            |              | Disabled | Linear Phase          |            |             |  |

|                                |                        |            |              | Enabled  | Lilleal Fliase        |            |             |  |

|                                |                        |            | 4            | Disabled | 1 1                   | 0.4        |             |  |

|                                |                        |            | 1            | Enabled  | Low Latency           | 24         |             |  |

| 16                             | 12.288                 | 768        |              | Disabled | Ultra-Low Latency     | -          | 24          |  |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     | 1          |             |  |

|                                |                        |            |              | Disabled | Linear Phase          |            |             |  |

|                                |                        |            | 2            | Disabled | Low Latency           | 48         |             |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     | -          |             |  |

|                                |                        |            |              | Disabled | Linear Phase          |            |             |  |

|                                |                        |            |              | Enabled  | Linear Phase          | _          |             |  |

|                                |                        |            |              | Disabled | Low Latency           | -          |             |  |

|                                |                        |            | 1            | Enabled  | Low Latency           | - 24       |             |  |

|                                |                        |            |              |          |                       | -          |             |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     | -          |             |  |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     |            |             |  |

|                                |                        |            |              | Disabled | Linear Phase          | -          |             |  |

|                                |                        |            |              | Enabled  | Linear Phase          |            |             |  |

|                                |                        |            | 2            | Disabled | Low Latency           | 48         |             |  |

| 16                             | 24.576                 | 1536       | _            | Enabled  | Low Latency           |            | -           |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     | 96         |             |  |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     |            |             |  |

|                                |                        |            |              | Disabled | Linear Phase          |            |             |  |

|                                |                        |            |              |          | Low Latency           |            |             |  |

|                                |                        |            | 3            |          | Ultra-Low Latency     |            |             |  |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     |            |             |  |

|                                |                        |            | 4            | Disabled | Linear Phase          |            |             |  |

|                                |                        |            |              |          | Low Latency           |            |             |  |

|                                |                        |            |              |          | Ultra-Low Latency     | -          |             |  |

|                                |                        |            |              | Disabled | J                     |            |             |  |

|                                |                        |            |              | Enabled  | Linear Phase          | 24         |             |  |

|                                |                        |            | -            | Disabled |                       |            |             |  |

|                                |                        |            | 1            | Enabled  | Low Latency           |            |             |  |

|                                |                        |            |              |          |                       |            |             |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     |            |             |  |

|                                |                        |            |              | Enabled  |                       |            |             |  |

|                                |                        |            |              | Disabled | Linear Phase          |            |             |  |

|                                |                        |            |              | Enabled  |                       | -          |             |  |

|                                |                        |            | 2            | Disabled | Low Latency           | 48         |             |  |

|                                |                        |            |              | Enabled  | , , , , ,             |            |             |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     |            |             |  |

| 16                             | 36.864                 | 2304       |              | Enabled  | Ollia-Low Latericy    |            | 24          |  |

| 10                             | 30.804                 | 2304       |              | Disabled | Linear Phase          |            | 24          |  |

|                                |                        |            |              | Enabled  | Lilleal Fliase        |            |             |  |

|                                |                        |            |              | Disabled |                       |            |             |  |

|                                |                        |            | 3            | Enabled  | Low Latency           |            |             |  |

|                                |                        |            |              | Disabled |                       | 1          |             |  |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     |            |             |  |

|                                |                        |            |              | Disabled |                       | 96         |             |  |

|                                |                        |            |              | Enabled  | Linear Phase          |            |             |  |

|                                |                        |            |              |          |                       | -          |             |  |

|                                |                        |            | 4            | Disabled | Low Latency           |            |             |  |

|                                |                        |            |              | Enabled  |                       | -          |             |  |

|                                |                        |            |              | Disabled | Ultra-Low Latency     | су         | v Latency   |  |

|                                |                        |            |              | Enabled  | <u> </u>              |            |             |  |

www.ti.com Master Mode

# Table 6. Supported Sample Rates for Auto Clock Configuration with PLL Disabled (continued)

| SAMPLING<br>FREQUENCY<br>(kHz) | MCLK<br>FREQUENCY(MHz) | MCLK RATIO | ADC CHANNELS | DRE      | DECIMATION<br>FILTERS     | BCLK RATIO | WORD LENGTH |

|--------------------------------|------------------------|------------|--------------|----------|---------------------------|------------|-------------|

|                                |                        |            |              | Disabled | Linear Phase              |            |             |

|                                |                        |            |              | Enabled  | Lilleal Filase            |            |             |

|                                |                        |            | 1            | Disabled | Low Latency               | 24         |             |

|                                | 12.288                 | 512        |              | Enabled  | Low Latericy              | 24         | 24          |

|                                | 12.200                 | 312        |              | Disabled | Ultra-Low Latency         |            |             |

|                                |                        |            |              | Enabled  | Ollia-Low Latericy        |            |             |

|                                |                        |            | 2            | Disabled | Linear Phase              | 48         |             |

|                                |                        |            | 2            | Disabled | Ultra-Low Latency         | 64         | 32          |

|                                |                        |            |              | Disabled | Linear Phase              |            |             |

|                                |                        |            |              | Enabled  | Lilledi Filase            |            |             |

|                                |                        |            | 1            | Disabled | Low Latency               | 32         |             |

|                                |                        |            | '            | Enabled  | LOW Laterity              | 32         |             |

| 24                             |                        |            |              | Disabled | Liltro Love Latonav       |            |             |

|                                |                        |            |              | Enabled  | Ultra-Low Latency         |            |             |

|                                |                        |            |              | Disabled | 6.                        |            |             |

|                                |                        |            |              | Enabled  | Linear Phase              |            |             |

|                                | 24.576                 | 1024       | 2            | Disabled |                           |            | 32          |

|                                |                        |            |              | Enabled  | Low Latency               | 64         |             |

|                                |                        |            |              | Disabled |                           |            |             |

|                                |                        |            |              | Enabled  | Ultra-Low Latency         |            |             |

|                                |                        |            | 3            |          | Linear Phase              |            |             |

|                                |                        |            |              |          | Low Latency               | 1          |             |

|                                |                        |            |              | Disabled | Ultra-Low Latency         | 128        |             |

|                                |                        |            |              |          | Linear Phase              | 1          |             |

|                                |                        |            | 4            |          | Ultra-Low Latency         |            |             |

|                                |                        |            |              | Disabled |                           | 24         |             |

|                                |                        |            | 1            | Enabled  | Linear Phase  Low Latency |            |             |

|                                |                        |            |              | Disabled |                           |            |             |

|                                |                        |            |              | Enabled  |                           |            |             |

|                                |                        |            |              | Disabled |                           |            |             |

|                                |                        |            |              | Enabled  | Ultra-Low Latency         |            |             |

|                                |                        |            |              | Disabled |                           |            |             |

|                                |                        |            | -            | Enabled  | Linear Phase              |            |             |

|                                |                        |            | -            | Disabled |                           |            |             |

|                                |                        |            | 2            | Enabled  | Low Latency               | 48         |             |

|                                |                        |            | -            | Disabled |                           |            |             |

| 24                             | 36.864                 | 1536       | -            | Enabled  | Ultra-Low Latency         |            | 24          |

|                                |                        |            |              | Disabled |                           |            |             |

|                                |                        |            |              | Enabled  | Linear Phase              |            |             |

|                                |                        |            |              |          |                           |            |             |

|                                |                        |            | 3            | Disabled | Low Latency               |            |             |

|                                |                        |            |              | Enabled  |                           |            |             |

|                                |                        |            |              | Disabled | Ultra-Low Latency         | 96         |             |

|                                |                        |            |              | Enabled  |                           |            |             |

|                                |                        |            |              | Disabled | Linear Phase              |            |             |

|                                |                        |            | 4            | Enabled  |                           |            |             |

|                                |                        |            | 4            | Disabled | Low Latency               |            |             |

|                                |                        |            |              |          | Ultra-Low Latency         |            | i e         |

Master Mode www.ti.com

Table 6. Supported Sample Rates for Auto Clock Configuration with PLL Disabled (continued)

| SAMPLING<br>FREQUENCY<br>(kHz) | MCLK<br>FREQUENCY(MHz) | MCLK RATIO | ADC CHANNELS          | DRE      | DECIMATION<br>FILTERS | BCLK RATIO | WORD LENGTH |  |  |  |  |   |         |             |  |  |

|--------------------------------|------------------------|------------|-----------------------|----------|-----------------------|------------|-------------|--|--|--|--|---|---------|-------------|--|--|

|                                |                        |            |                       |          | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                | 12.288                 | 384        | 1                     | Disabled | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                | 12.200                 | 304        | '                     |          | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Linear Phase          | 24         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Linear Phase          | 24         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 1                     | Disabled | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          |                       |            |             |  |  |  |  | 1 | Enabled | Low Latency |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

| 32                             |                        |            |                       | Disabled | Linear Phase          |            | 24          |  |  |  |  |   |         |             |  |  |

|                                | 0.4.570                | 700        |                       | Enabled  | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                | 24.576                 | 768        | 2                     |          | Low Latency           | 48         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 3                     |          | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     | 96         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Linear Phase          | -          |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 4                     |          | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                | 12.288                 | 256        |                       | Disabled | Low Latency           | 24         | 24          |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 1                     | Enabled  | Lilleal Fliase        |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Low Latency           | 22         |             |  |  |  |  |   |         |             |  |  |

|                                | 24.576                 | 512        |                       | Enabled  |                       | 32         | 32          |  |  |  |  |   |         |             |  |  |

| 48                             |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | Enabled  Linear Phase | Enabled  | •                     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        | V.=        |                       | 64       | 02                    |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 2                     |          | Low Latency           | 64         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                | ı                      |            | 3                     |          | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Ultra-Low Latency     | 128        |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 4                     | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 1                     | Disabled | Low Latency           | 24         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

| 48                             | 36.864                 | 768        | 2                     | Disabled | Low Latency           | 48         | 24          |  |  |  |  |   |         |             |  |  |

| -                              |                        |            |                       | Enabled  | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Enabled  | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 3                     |          | Low Latency           | 96         |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       | Disabled | Linear Phase          |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            | 4                     |          | Low Latency           |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        |            |                       |          | Ultra-Low Latency     |            |             |  |  |  |  |   |         |             |  |  |

|                                |                        | -          |              | _        |                       | -          | -           |

|--------------------------------|------------------------|------------|--------------|----------|-----------------------|------------|-------------|

| SAMPLING<br>FREQUENCY<br>(kHz) | MCLK<br>FREQUENCY(MHz) | MCLK RATIO | ADC CHANNELS | DRE      | DECIMATION<br>FILTERS | BCLK RATIO | WORD LENGTH |

|                                |                        |            | 1            |          | Linear Phase          |            | 32          |

|                                | 24.576                 | 256        |              | Disabled | Low Latency           | 32         |             |

|                                |                        |            |              |          | Ultra-Low Latency     |            |             |

|                                |                        |            |              |          | Linear Phase          | - 24       |             |

|                                |                        |            |              | Enabled  | Linear Phase          |            |             |

| 96                             |                        |            |              | Disabled | Low Latency           |            |             |

|                                | 36.864                 | 384        |              | Enabled  | Low Latency           | 24         | 24          |

|                                | 30.864                 | 364        |              | Disabled | Ultra-Low Latency     |            | 24          |

|                                |                        |            |              | Enabled  | Ultra-Low Latency     |            |             |

|                                |                        |            | 2            | Disabled | Low Latency           | 40         |             |

|                                |                        |            | 2            |          | Ultra-Low Latency     | 48         |             |

Table 6. Supported Sample Rates for Auto Clock Configuration with PLL Disabled (continued)

## 2.1.2.2 Example

For a 24.576-MHz or 22.579-MHz MCLK, the following I<sup>2</sup>C script configures the TLV320ADCx140 as master mode with GPIO1 as MCLK input for the 48-kHz or 44.1-KHz sampling rate, respectively:

```

w 98 13 a0 # enable master mode, disable PLL for auto-clock config

w 98 14 48 # FS = 44.1/48k BCLK/fsync ratio = 256

w 98 16 d8 # MCLK is audio root, use MCLK_ratio_sel, MCLK/Fsync ratio = 512

w 98 21 a0 # configure GPIO1 as MCLK input

```

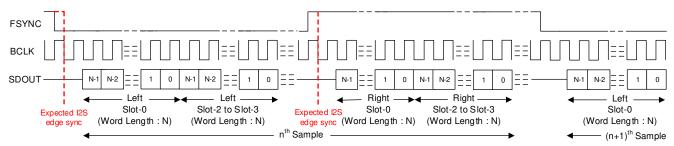

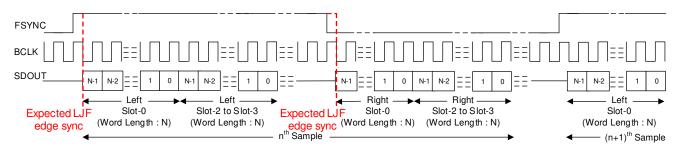

## 3 Edge Sync for I<sup>2</sup>S and LJF in Master Mode

In master mode, the FSYNC edge is synchronous to the rising edge of BCLK. However, standard I²S/LFJ bus format expect the FSYNC edge to be synchronous to the falling edge of BCLK. Figure 1 and Figure 2 show the timing diagrams supported by TLV320ADx140 in I²S and LJF mode, respectively. Note the standard I²S and LJF expect the FSYNC edge one clock cycle later than that produced by the TLV320ADC140. To support standard I²S and LJF bus formats, the following sections show configuration options to provide compatibility in master mode.

Figure 1. Default I<sup>2</sup>S in Master Mode (TX\_Offset = 0) Showing Incompatible FSYNC Edge Sync

Figure 2. Default LJF format in Master Mode (TX\_OFFSET = 0) Showing Incompatible FSYNC Edge Sync

## 3.1 Compatibility With Non-zero Offset

If the system can accommodate an additional offset for I<sup>2</sup>S or LJF format, the addition of an non-zero offset to the ASI bus of TLV320ADCx140 device allows compliance to either standard. If used in a system with other audio devices, these other devices would also need to accommodate this offset. To add non-zero offset, configure the following registers:

- BCLK\_POL (Page 0, ASI\_CFG0 Register 0x07, Bit 2) = 1

- TX\_EDGE (Page 0, ASI\_CFG0 Register 0x07, Bit 1) = 1

These settings change the base offset from the I<sup>2</sup>S and LJF formats to 1. Additional offsets can be achieved by using the TX OFFSET (Page 0, ASI CFG1 Register 0x08, Bits 4-0).

## 3.2 fS Compatibility With Zero Offset (fS only)

TLV320AlCx140 devices can comply with the I<sup>2</sup>S bus format with zero offset by modifying the default left justified format to fit the I<sup>2</sup>S format requirements, as follows:

- BCLK\_POL (Page 0, ASI\_CFG0 Register 0x07, Bit 2) = 1

- TX\_EDGE (Page 0, ASI\_CFG0 Register 0x07, Bit 1) = 1

- ASI\_FORMAT (Page 0, ASI\_CFG0 Register 0x07, Bits 7-6) = 2'b10 (LJF format)

- FSYNC\_POL (Page 0, ASI\_CFG0 Register 0x07, Bit 3) = 1

Note that the first three bitfields configure the device in LJF mode with a TX\_OFFSET = 1 as in Section 3.1. The fourth bitfield flips the polarity of FSYNC to match the  $I^2S$  protocol.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated