## A Basic Guide to Bridge Measurements

Bryan Lizon, Joseph Wu

Precision ADC

#### **ABSTRACT**

Many precision sensors are formed from a Wheatstone bridge circuit configuration. This circuit configuration enables accurate differential measurements for resistive elements. These elements can be used to measure weight, pressure, temperature, and a variety of other types of sensor parameters. Achieving the most accurate bridge measurements with precision analog-to-digital converters (ADCs) requires a detailed understanding of how these sensors work, how they are calibrated, how they connect to an ADC, and how the ADC is configured. This application note presents an overview of the bridge circuit, how bridges are used to measure different forces, how the ADC measurement is set up, and what errors can arise in the measurement. This application note starts with an overview of bridge circuit basics, how they are constructed, and what parameters are important when designing a bridge measurement system. Circuits are presented showing connections to precision ADCs.

### **Table of Contents**

| 1 I  | Bridge Overview                                                                                                | 3  |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2 I  | Bridge Construction                                                                                            | 5  |

|      | 2.1 Active Elements in Bridge Topologies                                                                       | 5  |

|      | 2.2 Strain Gauge and Bridge Construction                                                                       | 9  |

| 3 I  | Bridge Connections                                                                                             | 12 |

|      | 3.1 Ratiometric Measurements                                                                                   | 12 |

|      | 3.2 Four-Wire Bridge                                                                                           | 13 |

|      | 3.3 Six-Wire Bridge                                                                                            | 14 |

| 4 I  | Electrical Characteristics of Bridge Measurements                                                              | 15 |

|      | 4.1 Bridge Sensitivity                                                                                         | 15 |

|      | 4.2 Bridge Resistance                                                                                          |    |

|      | 4.3 Output Common-Mode Voltage                                                                                 | 16 |

|      | 4.4 Offset Voltage                                                                                             | 16 |

|      | 4.5 Full-Scale Error                                                                                           | 16 |

|      | 4.6 Non-Linearity Error and Hysteresis                                                                         | 17 |

|      | 4.7 Drift                                                                                                      | 17 |

|      | 4.8 Creep and Creep Recovery                                                                                   | 17 |

| 5 \$ | Signal Chain Design Considerations                                                                             | 18 |

|      | 5.1 Amplification                                                                                              | 18 |

|      | 5.2 Noise                                                                                                      |    |

|      | 5.3 Channel Scan Time and Signal Bandwidth                                                                     | 24 |

|      | 5.4 AC Excitation                                                                                              |    |

|      | 5.5 Calibration                                                                                                |    |

|      | Bridge Measurement Circuits                                                                                    | 36 |

|      | 6.1 Four-Wire Resistive Bridge Measurement with a Ratiometric Reference and a Unipolar, Low-Voltage (≤5 V)     |    |

|      | Excitation Source                                                                                              | 37 |

|      | 6.2 Six-Wire Resistive Bridge Measurement With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V)     |    |

|      | Excitation Source                                                                                              | 40 |

|      | 6.3 Four-Wire Resistive Bridge Measurement With a Pseudo-Ratiometric Reference and a Unipolar, High-Voltage (> |    |

|      | 5 V) Excitation Source                                                                                         | 43 |

|      | 6.4 Four-Wire Resistive Bridge Measurement with a Pseudo-Ratiometric Reference and Asymmetric, High-Voltage (> |    |

|      | 5 V) Excitation Source                                                                                         |    |

|      | 6.5 Four-Wire Resistive Bridge Measurement With a Ratiometric Reference and Current Excitation                 | 53 |

|      |                                                                                                                |    |

Trademarks www.ti.com

| 6.6 Measuring Multiple Four-Wire Resistive Bridges in Series with a Pseudo-Ratiometric Reference and a Unipolar, |      |

|------------------------------------------------------------------------------------------------------------------|------|

| Low-Voltage (≤5V) Excitation Source                                                                              | . 59 |

| 6.7 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Single-Channel ADC With a Ratiometric     |      |

| Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source                                                  | . 64 |

| 6.8 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Multichannel ADC With a Ratiometric       |      |

| Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source                                                  | . 71 |

| 7 Summary                                                                                                        | . 75 |

| 8 Revision History                                                                                               |      |

### **Trademarks**

All trademarks are the property of their respective owners.

www.ti.com Bridge Overview

### 1 Bridge Overview

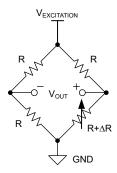

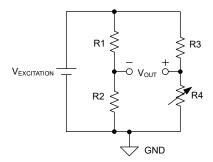

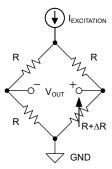

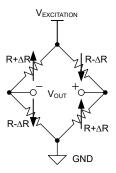

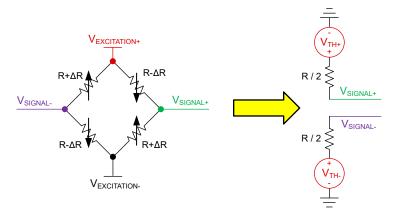

A Wheatstone bridge is a circuit used to measure a change in resistance among a set of resistive elements. The circuit has two parallel resistive branches that act as voltage dividers for the excitation voltage,  $V_{\text{EXCITATION}}$ . The output of each resistor divider is nominally at  $V_{\text{EXCITATION}}$  divided by two. With no applied load, the change in the resistance of the elements,  $\Delta R$ , is equal to zero. Assuming an ideal system where the nominal resistance of each element is R, each voltage divider is at the same potential and the differential bridge output voltage,  $V_{\text{OUT}}$ , is zero. When a load is applied, one or more of the elements changes resistance such that  $\Delta R \neq 0$   $\Omega$ . This causes a change in  $V_{\text{OUT}}$  that can be calculated very precisely by making a differential measurement across the bridge. Figure 1-1 shows the basic configuration of a simple bridge circuit using resistive elements.

Figure 1-1. Basic Configuration of a Simple Bridge Circuit

The basic bridge circuit is constructed using resistive elements with a single variable element in the bridge. This element is a resistive transducer that translates some physical parameter into a change in resistance. If this change in resistance is proportional to a change in the physical parameter, measuring  $\Delta R$  yields an accurate representation of the physical property being sensed. While this document focuses on bridges using resistive elements, it is possible to construct a bridge using inductive or capacitive elements as well.

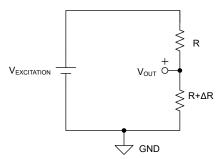

Bridge operation can be better understood by analyzing each side of the bridge in more detail. For example, the right side of the bridge in Figure 1-1 looks like the voltage divider circuit shown in Figure 1-2:

Figure 1-2. A Resistive Element Measured as a Voltage Divider

Equation 1 calculates V<sub>OUT</sub> with respect to ground for the system in Figure 1-2:

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{R + R + \Delta R}\right) = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R + \Delta R}\right) \tag{1}$$

Assuming  $V_{EXCITATION}$  = 6 V, R = 3000  $\Omega$ , and  $\Delta R$  = 3  $\Omega$ , Equation 1 can be used to calculate that  $V_{OUT}$  = 3.0015 V. Then, the voltage across R is calculated to be  $V_R$  =  $V_{EXCITATION}$  -  $V_{OUT}$  = 2.9985 V. This yields a voltage across  $\Delta R$  of  $V_{\Delta R}$  =  $V_{OUT}$  -  $V_R$  = 0.003 V. While Equation 1 works in theory to calculate  $V_{OUT}$ ,  $V_R$ , and  $V_{\Delta R}$ , a real system must measure  $V_{OUT}$  and  $V_R$  to be able to derive  $V_{\Delta R}$ . This can introduce additional challenges due to the limitations of standard measurement equipment.

For example, a simple 4-digit multimeter used to measure  $V_{OUT}$  and  $V_R$  could produce rounding errors that affect the calculation of  $V_{\Delta R}$ : if the multimeter rounds  $V_{OUT}$  = 3.0015 V up to 3.002 V and  $V_R$  = 2.9985 V down to 2.998 V, then  $V_{\Delta R}$  = 0.004 V; or, if  $V_{OUT}$  is rounded down to 3.001 V and  $V_R$  is rounded up to 2.999 V, then  $V_{\Delta R}$  = 0.002

Bridge Overview www.ti.com

V. Both of these cases yield a measurement error of 1 mV relative to a 3-mV signal, or  $\pm 33\%$  error. Ultimately, the 4-digit multimeter does not have enough resolution to consistently determine the precise value of  $\Delta R$  by measuring across either resistive element in the divider.

For better results, the single-ended measurement shown in Figure 1-2 is changed to a differential measurement by placing the resistive transducer in a bridge configuration. In Figure 1-3, the bridge uses a second resistive path in parallel with the transducer path. With no applied load,  $\Delta R = 0 \Omega$  and  $V_{OUT} = 0 V$ .

Figure 1-3. A Simple Bridge Using a Differential Measurement Across Two Resistive Paths

Equation 2 calculates the differential output voltage for the system shown in Figure 1-3 assuming R1 = R2 = R3 = R and R4 = R +  $\Delta$ R.

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R + \Delta R} - \frac{R}{2 \times R}\right) = V_{EXCITATION} \cdot \left(\frac{\Delta R}{2 \times (2 \cdot R + \Delta R)}\right)$$

(2)

Using the same values from the single-ended example where  $V_{EXCITATION}=6$  V, R = 3000  $\Omega$ , and  $\Delta R=3\Omega$ ,  $V_{OUT}$  is now calculated to be 1.49925 mV. Importantly, the same 4-digit multimeter can measure  $V_{OUT}$  much more precisely and on a millivolt scale as either 1.499 mV (rounded down) or 1.500 mV (rounded up). Measuring  $V_{OUT}$  differentially in a bridge configuration yields a measurement error of <1  $\mu$ V relative to a 1.5-mV signal, or 0.067%. This result occurs because a bridge configuration enables direct measurement of  $\Delta R$  instead of a comparative measurement between  $\Delta R$  and R. A direct measurement also enables  $V_{OUT}$  to be amplified to get a larger input signal to the ADC. This amplification enables higher-resolution measurements of smaller values of  $\Delta R$ .

One challenge with a single active resistive element bridge is that it has an inherent non-linearity in the measurement. Different bridge constructions have different non-linearities, and some topologies eliminate this inherent non-linearity. This is discussed in more detail in the next section.

www.ti.com Bridge Construction

### 2 Bridge Construction

### 2.1 Active Elements in Bridge Topologies

As Figure 1-3 illustrates, a basic bridge has a single active resistive element while the other three elements are static resistances. These single active-element bridges are simpler to construct and less expensive. However, they have less sensitivity and more non-linearity through the full-scale range of the measurement.

Other bridge topologies may have two active resistive elements and two static resistors. In some cases, all four resistive elements can be active. These bridges increase the sensitivity and reduce the non-linearity in the bridge measurements. Regardless of the configuration, the bridge functionality remains the same: measuring the change in the resistive element as a function of the excitation voltage.

### 2.1.1 Bridge With One Active Element

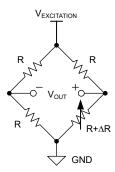

The simplest bridge topology has a single active resistive element while the remaining three elements are static resistances, as shown in Figure 2-1. This is known as a quarter bridge.

Figure 2-1. Bridge With One Active Element (Quarter Bridge)

Equation 3 calculates V<sub>OUT</sub> between the two voltages dividers in Figure 2-1:

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R + \Delta R}\right) - V_{EXCITATION} \cdot \left(\frac{R}{2 \cdot R}\right)$$

(3)

Collecting like terms and simplifying Equation 3 yields Equation 4:

$$V_{OUT} = V_{EXCITATION} \cdot \left( \frac{(R + \Delta R) - (2 \cdot R + \Delta R)/2}{2 \cdot R + \Delta R} \right) = \frac{V_{EXCITATION}}{2} \cdot \left( \frac{\Delta R}{2 \cdot R + \Delta R} \right)$$

(4)

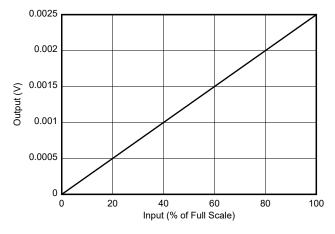

Equation 4 shows that  $V_{OUT}$  is proportional to  $V_{EXCITATION}$  and  $\Delta R$  when  $\Delta R$  is much smaller than R ( $\Delta R$  < R). This relationship can be confirmed by plotting  $V_{OUT}$  against the change in  $\Delta R$  from zero to full-scale ( $\Delta R_{FS}$ ). Figure 2-2 shows this plot when R = 1 k $\Omega$ ,  $V_{EXCITATION}$  = 10 V, and  $\Delta R_{FS}$  = 1  $\Omega$ .

Figure 2-2. Quarter Bridge Differential Output (R = 1 k $\Omega$ , V<sub>EXCITATION</sub> = 10 V,  $\Delta$ R<sub>FS</sub> = 1  $\Omega$ )

Bridge Construction www.ti.com

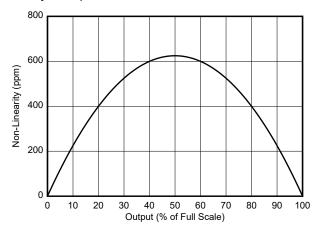

Though not obvious from Figure 2-2, this bridge topology has a small inherent non-linearity because of the  $2R + \Delta R$  term in the denominator in Equation 4. Taking the endpoints of the plot in Figure 2-2 and removing the endpoint slope from the curve reveals the non-linearity of this bridge topology. Figure 2-3 illustrates this phenomenon by plotting non-linearity as a percent of the full-scale.

Figure 2-3. Quarter Bridge Non-Linearity

The non-linearity shown in Figure 2-3 directly results from the topology of the bridge with one active element, and does not include any non-linearity in the single active resistive element.

### 2.1.1.1 Reducing Non-Linearity in a Bridge With One Active Element Using Current Excitation

It is possible to reduce the non-linearity in a bridge with one active element by using current excitation instead of voltage excitation, as shown in Figure 2-4.

Figure 2-4. Current Excitation for a Bridge with One Active Element

Equation 5 calculates the resulting output voltage,  $V_{OUT}$ , when  $I_{EXCITATION}$  splits between each branch of the bridge in Figure 2-4:

$$V_{OUT} = I_{EXCITATION} \cdot (R + \Delta R) \cdot \left(\frac{2 \cdot R}{4 \cdot R + \Delta R}\right) - I_{EXCITATION} \cdot R \cdot \left(\frac{2 \cdot R + \Delta R}{4 \cdot R + \Delta R}\right)$$

(5)

Converting and collecting like terms, Equation 5 simplifies to Equation 6:

$$V_{OUT} = I_{EXCITATION} \cdot \left( \frac{\left( 2 \cdot R^2 + 2 \cdot R \cdot \Delta R \right) - \left( 2 \cdot R^2 + R \cdot \Delta R \right)}{4 \cdot R + \Delta R} \right) = I_{EXCITATION} \cdot R \cdot \left( \frac{\Delta R}{4 \cdot R + \Delta R} \right)$$

(6)

Comparing the denominators for Equation 6 (4 · R +  $\Delta$ R) and Equation 4 (2 · R +  $\Delta$ R) reveals that the non-linearity error due to the topology of a one-active-element bridge using current excitation is reduced by approximately  $\frac{1}{2}$  relative to the same circuit using voltage excitation.

A bridge measurement system using current excitation has additional benefits and challenges. See Section 6.5 for more information about how this circuit is implemented.

www.ti.com Bridge Construction

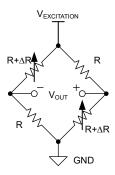

### 2.1.2 Bridge With Two Active Elements in Opposite Branches

Bridges can also be constructed with more than one active element. Figure 2-5 shows a sensor with two active elements placed in different branches and on opposite sides of the bridge. This is known as a half bridge.

Figure 2-5. Bridge With Two Active Elements in Opposite Branches (Half Bridge)

Equation 7 calculates V<sub>OUT</sub> for the bridge with two active elements in opposite branches shown in Figure 2-5:

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R + \Delta R}\right) - V_{EXCITATION} \cdot \left(\frac{R}{2 \cdot R + \Delta R}\right) = V_{EXCITATION} \cdot \left(\frac{\Delta R}{2 \cdot R + \Delta R}\right)$$

(7)

Similar to the bridge with one active element, Equation 7 shows that  $V_{OUT}$  is proportional to  $V_{EXCITATION}$  and  $\Delta R$  when  $\Delta R$  is small. Moreover, the  $V_{OUT}$  equation for both bridge types has a  $\Delta R$  term in the denominator, resulting in the same non-linearity seen in Figure 2-3.

However, the important difference between a single-active-element bridge and a bridge with two active elements is the *sensitivity*. In the latter case,  $V_{OUT}$  is two times larger for a given  $V_{EXCITATION}$ . This larger output signal doubles the dynamic range compared to the single-active-element bridge, resulting in a better ADC measurement.

# 2.1.2.1 Eliminating Non-Linearity in a Bridge With Two Active Elements in Opposite Branches Using Current Excitation

Figure 2-6 illustrates how it is possible to eliminate the non-linearity in a bridge with two active elements in opposite branches by using current excitation instead of voltage excitation.

Figure 2-6. Current Excitation for a Bridge With Two Active Elements in Opposite Branches

Equation 8 calculates the resulting output voltage, V<sub>OUT</sub>, when I<sub>EXCITATION</sub> splits between each branch of the bridge in Figure 2-6.

$$V_{OUT} = I_{EXCITATION} \cdot (R + \Delta R) \cdot \left(\frac{2 \cdot R + \Delta R}{4 \cdot R + 2 \cdot \Delta R}\right) - I_{EXCITATION} \cdot R \cdot \left(\frac{2 \cdot R + \Delta R}{4 \cdot R + 2 \cdot \Delta R}\right)$$

(8)

The ratio  $(2 \cdot R + \Delta R) / (4 \cdot R + 2 \cdot \Delta R)$  in Equation 8 reduces to  $\frac{1}{2}$ , which produces the simplified result in Equation 9:

$$V_{OUT} = \frac{I_{EXCITATION}}{2} \cdot \Delta R \tag{9}$$

Bridge Construction www.ti.com

Unlike the circuit using voltage excitation, Equation 9 has no  $\Delta R$  term in the denominator. As a result, current excitation removes the non-linearity error due to the topology of a bridge with two active elements in opposite branches. Comparatively, the same circuit using voltage excitation has a non-linearity error proportional to  $2 \cdot R + \Delta R$ .

A bridge measurement system using current excitation has additional benefits and challenges. Refer to Section 6.5 for more information about how this circuit is implemented.

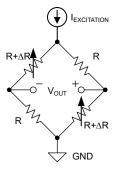

### 2.1.3 Bridge With Two Active Elements in the Same Branch

Bridges can also be constructed with two active elements in the same branch. Figure 2-7 shows an example of this type of configuration, which can also be referred to as a half bridge.

Figure 2-7. Bridge With Two Active Elements in the Same Branch (Half Bridge)

Equation 10 and Equation 11 calculate  $V_{OUT}$  for the bridge with two active elements in the same branch that is shown in Figure 2-7:

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{(R + \Delta R) + (R - \Delta R)}\right) - V_{EXCITATION} \cdot \left(\frac{R}{2 \cdot R}\right) = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R} - \frac{R}{2 \cdot R}\right) \tag{10}$$

$$V_{OUT} = V_{EXCITATION} \left( \frac{\Delta R}{2 \cdot R} \right) \tag{11}$$

Similar to the previous bridge configurations,  $V_{OUT}$  is proportional to  $V_{EXCITATION}$  and  $\Delta R$ . Unlike the previous bridge topologies, Equation 11 does not have a  $\Delta R$  term in the denominator. As such, a bridge with two active elements in the same branch does not have an inherent non-linearity, which is true for both voltage or current excitation. However, this does not include any non-linearity from the actual sensor.

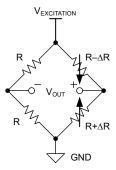

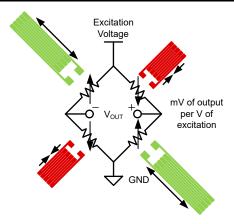

### 2.1.4 Bridge With Four Active Elements

The final bridge configuration is constructed with four active elements that each have the same magnitude change in resistance for the same strain. However, this change is in opposite directions on opposite sides of the bridge. This configuration is known as a full bridge, and is shown in Figure 2-8.

Figure 2-8. Bridge With Four Active Elements (Full Bridge)

Equation 12 and Equation 13 calculate V<sub>OUT</sub> for the bridge with four active elements shown in Figure 2-8:

www.ti.com Bridge Construction

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{R + \Delta R}{2 \cdot R}\right) - V_{EXCITATION} \cdot \left(\frac{R - \Delta R}{2 \cdot R}\right) = V_{EXCITATION} \cdot \left(\frac{2 \cdot \Delta R}{2 \cdot R}\right)$$

(12)

$$V_{OUT} = V_{EXCITATION} \cdot \left(\frac{\Delta R}{R}\right) \tag{13}$$

Similar to all of the previous bridge configurations,  $V_{OUT}$  is proportional to  $V_{EXCITATION}$  and  $\Delta R$  if  $\Delta R$  is small. The benefit of a four-active-element bridge is that the sensitivity is two times greater than both two-active-element bridge configurations and four times greater than the single-active-element bridge. Moreover, a four-active-element bridge topology has no inherent non-linearity in the bridge output. This is true for both voltage and current excitation.

### 2.2 Strain Gauge and Bridge Construction

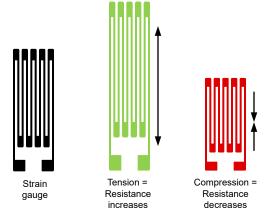

One example of a common use-case for a bridge measurement is a load cell comprised of strain gauge elements. A strain gauge is a wire or metallic foil whose resistance changes as the element deforms. When the strain gauge is tensioned (stretched), the foil elongates, causing the resistance to increase. When the strain gauge is compressed, the foil shortens, causing the resistance to decrease. Figure 2-9 illustrates the change in resistance as the strain gauge length changes. A resting strain gauge is shown in black, a tensioned strain gauge is shown in green, and a compressed strain gauge is shown in red.

Figure 2-9. Strain Gauge Resistance vs Length: Resting (left), Tension (middle), and Compression (right)

Strain gauges are typically affixed to a structure that has some small amount of flexibility. For example, a rod holding a weight experiences some tension due to the applied load. A strain gauge affixed to the rod also tensions slightly as the rod deforms, increasing the strain gauge resistance so that the tensile force can be measured. Similarly, the strain gauge compresses if the rod compresses, causing a resistance change that directly relates to the amount of compressive force on the rod.

Another example of a slightly-flexible component that uses strain gauges is a load cell, similar to the one shown in Figure 2-10.

Bridge Construction Www.ti.com

Figure 2-10. Photo of a Load Cell

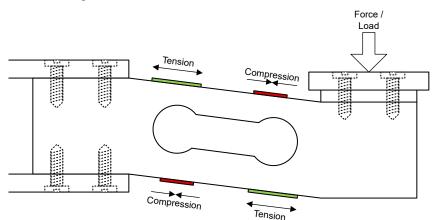

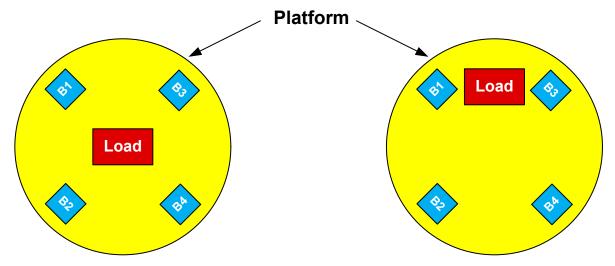

Strain gauges are placed into a bridge configuration to construct a load cell. Figure 2-11 depicts a common single-point load cell with four strain gauges at different points around the aperture. As shown, an applied downward force causes the free end of the load cell to move parallel to the fixed end. In this configuration, opposite strain gauges are tensioned (in green) and compressed (in red). This mechanical orientation allows for a proper four-active-element bridge.

Figure 2-11. Single-Point Load Cell With Approximate Positions and Responses of the Four Strain Gauges

Figure 2-12 shows the four resistors in their electrical positions in the bridge. Redrawing the elements of the load cell for tension (in green) and compression (in red) shows how these elements have opposite reactions to the strain on opposite sides of the bridge.

www.ti.com Bridge Construction

Figure 2-12. Equivalent Bridge Measurement of the Load Cell

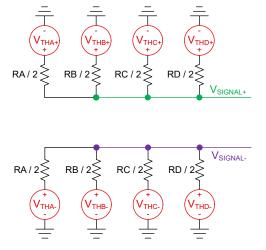

A common application using these type of load cells is a weigh scale. A weigh scale may use one or more load cells measured at the same time. The sum of these load cell measurements is used to calculate the weight of the object being measured.

Bridge Connections www.ti.com

### 3 Bridge Connections

Connecting a bridge to an ADC typically requires implementing a ratiometric measurement while choosing between a four-wire or six-wire bridge. The next sections discuss these concepts in more detail as well as demonstrate how a bridge is connected to the excitation voltage and the ADC.

### 3.1 Ratiometric Measurements

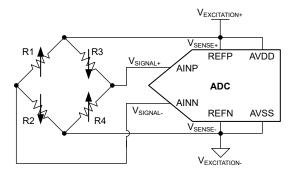

Figure 3-1 illustrates how bridge measurements are typically made with a ratiometric reference configuration. The output of the bridge is measured by the ADC while a single source is used as both the bridge excitation voltage and the ADC reference voltage.

Figure 3-1. Example of a Ratiometric Bridge Measurement

The ADC samples the input voltage,  $V_{IN}$ , and compares it against the reference voltage,  $V_{REF}$ .  $V_{IN}$  is the voltage difference between  $V_{SIGNAL+}$  and  $V_{SIGNAL-}$  (or AINP and AINN) while  $V_{REF}$  is the difference between the voltage at  $V_{SENSE+}$  and  $V_{SENSE-}$  (or REFP and REFN). The ADC generates an output code proportional to  $V_{REF}$  as per Equation 14:

Output Code

$$\propto \frac{V_{IN}}{V_{REF}} = \frac{V_{IN}}{\text{AVDD}}$$

(14)

Equation 14 substitutes AVDD for the  $V_{REF}$  term because AVDD is connected to REFP and REFN is grounded in Figure 3-1. Also, recall that Equation 13 states that  $V_{OUT}$  is equal to  $V_{EXCITATION}$  multiplied by  $\Delta R$  divided by R. In Figure 3-1, AVDD =  $V_{EXCITATION}$  -  $V_{EXCITATION}$  while  $V_{OUT}$  (Bridge) =  $V_{IN}$  (ADC). These substitutions yield Equation 15:

$$V_{IN} = V_{EXCITATION} \cdot \left(\frac{\Delta R}{R}\right) = \text{AVDD} \cdot \left(\frac{\Delta R}{R}\right)$$

(15)

Substituting Equation 15 for the V<sub>IN</sub> term in Equation 14 results in Equation 16:

Output Code

$$\propto \frac{V_{IN}}{\text{AVDD}} = \frac{\Delta R}{R}$$

(16)

The output code in Equation 16 is directly proportional to  $\Delta R$ . Moreover, Equation 16 shows that the exact values of AVDD and  $V_{IN}$  are unnecessary. Instead, the output code is directly proportional to the strain on the bridge.

One of the benefits of a ratiometric measurement is that the measurement is relatively invariant to changes in  $V_{REF}$ . This is also shown in Equation 16, where the output is proportional to  $\Delta R$  / R and is therefore independent of the exact value of  $V_{REF}$  or  $V_{EXCITATION}$ . Therefore, the ratiometric measurement is less susceptible to any  $V_{EXCITATION}$  drift over time and temperature. Any noise from the  $V_{EXCITATION}$  source should also cancel out assuming that the noise at the reference input and the measurement input are correlated. Typically, these noise sources correlate well if the filter bandwidth for the reference input and the measurement input are the same.

www.ti.com Bridge Connections

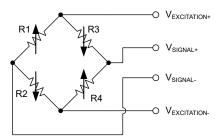

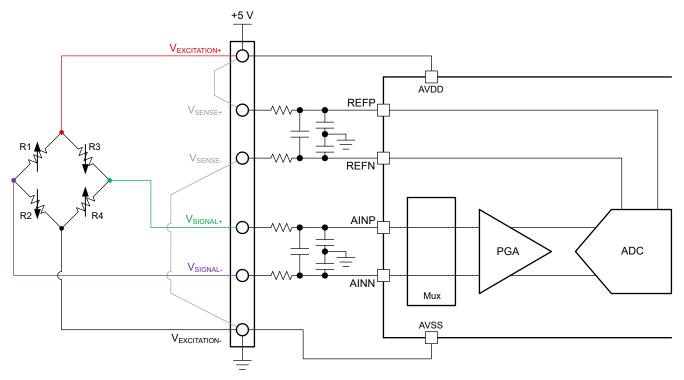

### 3.2 Four-Wire Bridge

Figure 3-2 shows the connections for a four-wire bridge. There are two wires for excitation of the bridge  $(V_{EXCITATION+})$  and  $V_{EXCITATION-})$  and two wires for the measurement  $(V_{SIGNAL+})$  and  $V_{SIGNAL-})$ . The ADC measures the differential bridge output voltage and the ADC positive and negative reference inputs connect to the excitation lines as  $V_{EXCITATION+}$  and  $V_{EXCITATION-}$ , respectively.

Figure 3-2. Connections for a Four-Wire Bridge

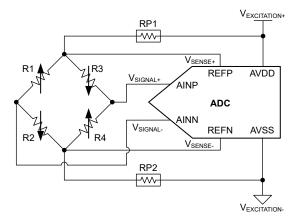

A four-wire bridge is suitable for a basic measurement in many data acquisition systems. However, long leads for  $V_{\text{EXCITATION+}}$  and  $V_{\text{EXCITATION-}}$  may have non-negligible resistance that add an error to the ADC measurement. Figure 3-3 shows an ADC connected to a four-wire bridge that has a series resistance, RP1 and RP2, in the excitation leads.

Figure 3-3. Four-Wire Bridge With Parasitic Resistance in V<sub>EXCITATION±</sub> Leads

Theoretically,  $V_{\text{EXCITATION+}}$  at the REFP input and  $V_{\text{EXCITATION-}}$  at the REFN input are the same as the voltage exciting the bridge. However, the series lead resistance lowers the voltage at the bridge itself, thereby changing the bridge output voltage as per Equation 17.

$$V_{OUT} = [V_{EXCITATION} - ([RP1 + RP2] \cdot [I_{EXCITATION}])] \cdot \left(\frac{\Delta R}{R}\right)$$

(17)

Even if RP1 and RP2 are small, the current through the bridge ( $I_{EXCITATION}$ ) can be substantial, resulting in a significant error. For example,  $I_{EXCITATION}$  = 14.3 mA when  $V_{EXCITATION}$  = 5 V and the bridge resistance is 350  $\Omega$ . Even if RP1 = RP2 = 1  $\Omega$ , the parasitic resistance results in a 0.6% measurement error.

Note that the leads for the bridge output ( $V_{SIGNAL\pm}$  in Figure 3-2) may also have a series resistance of the same magnitude as RP1 and RP2. However, the ADC input impedance is typically high and the current pulled through  $V_{SIGNAL\pm}$  is many orders of magnitude smaller than  $I_{EXCITATION}$ . Therefore, any current reacting with the  $V_{SIGNAL\pm}$  lead resistance adds a negligible error.

Bridge Connections Www.ti.com

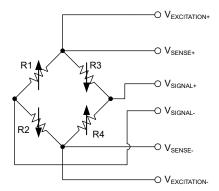

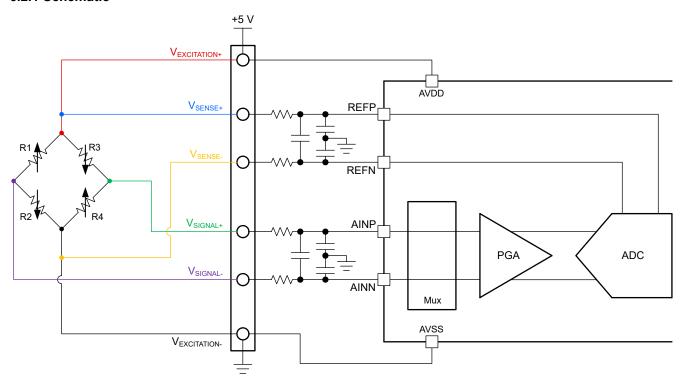

### 3.3 Six-Wire Bridge

A six-wire bridge removes the lead resistance error associated with a four-wire bridge. A six-wire topology has the same four wires as the four-wire bridge, while an additional two wires (V<sub>SENSE±</sub>) connect to the top and the bottom of the bridge. Figure 3-4 shows a six-wire bridge.

Figure 3-4. Connections for a Six-Wire Bridge

In this topology, the  $V_{SENSE\pm}$  leads at the top and bottom of the bridge are used as a Kelvin (or force-sense) connection to remove the effect of the lead resistance. This connection uses the  $V_{EXCITATION\pm}$  leads as a force line to drive the voltage to the bridge.  $V_{EXCITATION\pm}$  can be high current and create a voltage drop across the parasitic resistances going to the bridge as discussed in Section 3.2. The  $V_{SENSE\pm}$  leads are used to accurately measure the voltage at the top of the bridge by bypassing the parasitic lead resistance that carries the high current. At the same time, any resistance in the  $V_{SENSE\pm}$  leads causes a significantly lower voltage error because of the much smaller input current flowing through each lead. Figure 3-5 shows how a six-wire bridge connects to the ADC. The series resistance in the  $V_{EXCITATION\pm}$  leads is also shown.

Figure 3-5. Six-Wire Bridge With Parasitic Resistance in V<sub>EXCITATION±</sub> Leads

Using a six-wire bridge topology ensures that the ADC  $V_{REF}$  is the same as the voltage driving the bridge. Similar to the four-wire topology, resistance in the  $V_{SIGNAL\pm}$  and  $V_{SENSE\pm}$  leads can add an error, though the current through these leads will be significantly smaller than  $I_{EXCITATION}$ . This lower current minimizes the error introduced to the ADC input and reference paths, thereby improving overall system accuracy compared to the four-wire bridge.

### 4 Electrical Characteristics of Bridge Measurements

An important consideration to achieving precise and accurate bridge measurements is how the electrical characteristics of the sensor affect the ADC performance. Table 4-1 shows a generic specification table for the resistive bridges used in a typical load cell.

Table 4-1. Example Load Cell Specifications

| Specification Description    | Specification Value                | Specification Value for a Load<br>Cell With a 2-kg Capacity |  |

|------------------------------|------------------------------------|-------------------------------------------------------------|--|

| Bridge Sensitivity           | 2.0 ±15% mV/V                      |                                                             |  |

| Safe Overload                | 150 %FS                            | 3 kg                                                        |  |

| Maximum Overload             | 200 %FS                            | 4 kg                                                        |  |

| Non-linearity                |                                    |                                                             |  |

| Non-repeatability            | V 0 0 5 8/ 50                      | ±1 g                                                        |  |

| Hysteresis                   | ±0.05 %FS                          |                                                             |  |

| Creep (5 min.)               |                                    |                                                             |  |

| Temperature Effect on Output | ±0.05 %FS/°C                       | ±1 g/°C                                                     |  |

| Temperature Effect on Zero   | ±2.0 %FS/°C                        | ±40 g/°C                                                    |  |

| Zero Balance                 | ±10 %FS                            | ±0.2 kg                                                     |  |

| Bridge Resistance            | 1000 ± 10 Ω ≤ 15 V  -10°C to +40°C |                                                             |  |

| Excitation Voltage           |                                    |                                                             |  |

| Operating Temperature Range  |                                    |                                                             |  |

Many of these characteristics are errors that can be calibrated, while other errors must be added to the total error budget. The following sections briefly introduce some of the more important electrical characteristics in Table 4-1 and are therefore not meant to be comprehensive.

### 4.1 Bridge Sensitivity

The bridge sensitivity is the maximum expected output voltage for each volt of excitation,  $V_{\text{EXCITATION}}$ , when the maximum load is applied. A typical bridge load cell has a sensitivity of 1 mV/V to 3 mV/V, such as the bridge in Table 4-1 that has a sensitivity of 2 mV/V. This value means that the bridge output increases by 2 mV for every 1 V of  $V_{\text{EXCITATION}}$ . For example, exciting this bridge with 5 V yields a maximum bridge output of 10 mV when the maximum load is applied.

This 10-mV output voltage is also the maximum differential input voltage measured by the ADC. Use this value to determine how much gain is required to increase the measured input signal and use more of the ADC full-scale range. Many ADCs incorporate a programmable gain amplifier that can be used for this purpose.

### 4.2 Bridge Resistance

Bridges come in a variety of nominal resistance values, though 120  $\Omega$ , 350  $\Omega$ , and 1000  $\Omega$  are the most common (see Table 4-1). Lower bridge resistances may require significant current to drive. For example, using  $V_{\text{EXCITATION}} = 5 \text{ V}$  to drive a 350- $\Omega$  bridge requires 14.3 mA of current. This may be significantly larger than the current consumed by the measurement circuitry including the ADC and amplifiers. In fact, power dissipation through the bridge may be the largest part of the system power budget.

Additionally, this large excitation current can react with any parasitic resistance in the excitation path to cause a mismatch between the actual voltage across the bridge and the reference voltage measured by the ADC. This error can be removed using a six-wire bridge.

### 4.3 Output Common-Mode Voltage

Typically, the desired output common-mode voltage of the bridge is at the midpoint of the ADC supply, AVDD, when AVDD =  $V_{\text{EXCITATION}}$ . This is the ideal common-mode input voltage for an ADC and enables the maximum gain.

Some systems use a  $V_{\text{EXCITATION}}$  that is greater than AVDD. If this is the case, the bridge output common-mode voltage may not match the ADC input common-mode range. For example, choosing  $V_{\text{EXCITATION}} = 10 \text{ V}$  to maximize the sensor output sets the bridge common-mode voltage at 5 V. If AVDD = 5 V for the ADC, then this measurement may be very close to the ADC input range limit. Moreover, high-gain amplifiers used to amplify the bridge output typically limit the common-mode input range to well below AVDD, requiring alternative solutions. Section 6.3 and Section 6.4 show circuits that accommodate bridge configurations where  $V_{\text{EXCITATION}} > \text{AVDD}$ .

### 4.4 Offset Voltage

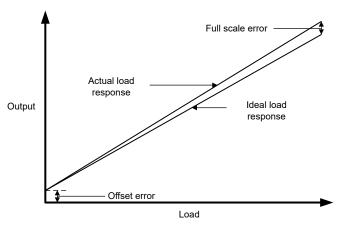

The ideal bridge output should be 0 V with no applied load. However, a real bridge has a non-zero output with load applied. This error is an offset voltage that shifts the load response up or down, as shown in Figure 4-1.

Figure 4-1. Actual vs Ideal Response of a Load on a Bridge

Offset voltage may come from a variety of sources. Manufacturing tolerances can result in difference nominal resistances among the bridge elements. This leads to an inherent offset error even with no applied load, and is typically specified in the sensor data sheet (see the *Zero Balance* parameter in Table 4-1).

Parasitic thermocouples external to the sensor in the bridge connection may give a small offset voltage that varies with temperature. Moreover, ADC input bias currents reacting with the bridge lead resistance or any ADC input filtering resistances may also give a small offset voltage.

Regardless of the offset voltage source, there are ways to calibrate this error through simple zeroing of the offset voltage digitally or other active circuit techniques such as AC excitation.

### 4.5 Full-Scale Error

Full-scale error or gain error is the difference in slope between the actual and ideal bridge measurement response under load with the offset removed. Figure 4-1 shows an example of the full-scale error. Sources of full-scale error can include wire impedance in a ratiometric measurement as discussed in Section 3.2 or the inherent gain error from an ADC. Additionally, the bridge sensitivity tolerance could change the slope of the load-vs-output-voltage curve and cause an error. For example, the  $\pm 15\%$  tolerance given in Table 4-1 allows the typical 2-mV/V bridge sensitivity to span from 1.7 mV/V to 2.3 mV/V. Assuming  $V_{\text{EXCITATION}} = 5$  V, the ideal maximum bridge output signal is 2 mV/V • 5 V = 10 mV. However, the actual maximum bridge output signal could range from 8.5 mV (negative error) to 11.5 mV (positive error).

Fortunately, full-scale error is a measurement gain error that can typically be calibrated through testing of the measurement system against known inputs.

### 4.6 Non-Linearity Error and Hysteresis

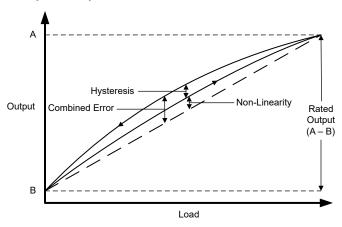

Non-linearity error is the deviation of the output curve from the expected full-scale straight-line output as the bridge output increases. This non-linearity results from the characteristics of the bridge resistive elements and is different from the bridge topology error discussed in Section 2.1.1. For example, a resistive bridge element may be more non-linear if it exceeds a certain range or load. Bridge data sheets often characterize non-linearity (see Table 4-1) and suggest limiting the maximum load to keep non-linearity small.

Similar to non-linearity error, hysteresis is a small error that changes with the bridge output. However, this error may be different depending on whether the bridge output is increasing or decreasing. The addition of hysteresis to the non-linearity error is known as the *combined error*. The combined error is the maximum error from the straight line ranging from no load to the maximum load conditions (increasing and decreasing). Figure 4-2 graphically shows the non-linearity error, hysteresis, and the combined error.

Figure 4-2. Hysteresis, Non-Linearity, and Combined Error

Non-linearity error and hysteresis are not easily calibrated. These errors may be different from unit-to-unit such that calibration requires many measurements across the full range of the bridge operation. However, these errors are typically much smaller than offset and full-scale errors. It is also worth noting that an ADC can contribute a non-linearity error, though this is generally negligible compared to bridge non-linearity.

### 4.7 Drift

Many of the parameters shown in Table 4-1 are specified at one temperature, typically 25°C. Drift errors specify how these parameters change over a temperature range. One common drift error is offset drift (*Temperature Effect on Zero* in Table 4-1), where the initial bridge offset voltage changes with temperature. Another common drift error is full-scale drift (*Temperature Effect on Output* in Table 4-1), which specifies how the slope of the bridge output changes with temperature. Similarly, ADCs have their own drift characteristics that affect measurement accuracy. Offset and gain drift errors are often described in %FS / °C, though other units are possible.

Temperature drift may be difficult to compensate due to non-linearity or different polarity. Moreover, accurately calibrating these errors can require measurements at different points across the temperature range of operation. In the design of any bridge measurement system, it is important to identify the operating temperature range and calculate the possible expected system error due to drift.

### 4.8 Creep and Creep Recovery

Creep is the change in the bridge output under a loaded condition while all other environmental factors are constant. This may be caused by deformations in a load cell under load over time. Creep recovery is the change in the bridge output after the load condition has been removed. Both errors are rated over a given amount of time and can be included in the bridge data sheet (see Table 4-1). However, these errors are not a function of the ADC measurement itself.

Similar to some of the other parameters, creep and creep recovery are errors that cannot be calibrated. The effects must fit within the error budget of the system design.

### **5 Signal Chain Design Considerations**

After selecting a bridge based on its construction, connections, and characteristics, it is necessary to design a low-noise signal chain to measure the bridge output. This section delves into several important topics related to selecting the signal chain components:

- Amplification

- Noise

- Channel Scan Time and Signal Bandwidth

- AC Excitation

- Calibration

### 5.1 Amplification

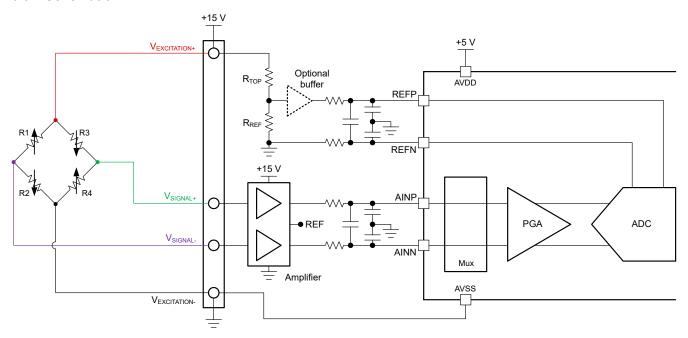

As discussed in Section 4.1, a typical bridge has a sensitivity of 1 mV/V to 3 mV/V. Such low sensitivities often require selecting the largest value of  $V_{\text{EXCITATION}}$  to increase the bridge output signal as much as possible. For example, the maximum  $V_{\text{EXCITATION}}$  in Table 4-1 is 15 V and the bridge sensitivity is 2 mV/V, resulting in a maximum bridge output signal of 30 mV. This relatively low-level signal requires amplification to achieve precision measurements.

However, choosing  $V_{\text{EXCITATION}}$  > AVDD can require level-shifting the reference or signal voltages to meet the ADC input limitations because most ADCs only support AVDD  $\leq 5$  V. In this case, use an external instrumentation amplifier (INA) in front of a gainless ADC to amplify the bridge signal and set the amplifier output common-mode voltage.

When V<sub>EXCITATION</sub> ≤ AVDD, choose an ADC with an integrated low-noise programmable gain amplifier (PGA) to reduce the system noise and improve dynamic range. Selecting an ADC with an integrated PGA also simplifies the signal chain and reduces PCB area.

The following subsections detail the operation of and use-cases for external INAs and integrated PGAs.

### 5.1.1 Instrumentation Amplifier

An INA may be necessary if the bridge signals extend beyond the ADC input limitations. This is generally the case when  $V_{\text{EXCITATION}}$  > AVDD (see Section 6.3). Or, an external INA can be used to amplify the bridge output if the selected ADC does not have an integrated PGA.

### 5.1.1.1 INA Architecture and Operation

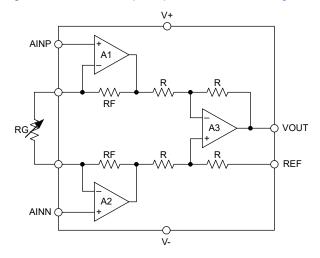

Although there are other topologies, a basic three op-amp INA is shown in Figure 5-1.

Figure 5-1. Topology of a Basic INA

The INA in Figure 5-1 amplifies the voltage between AINP and AINN. The amplifier gain is determined by an external gain-setting resistor,  $R_G$ , and the internal feedback resistors,  $R_F$ . The voltages at AINP and AINN are forced onto  $R_G$  via the output of A1 and A2 and both  $R_F$  resistors. This forces the same current through all three

resistors to create gain. A difference amplifier comprised of op amp A3 and four resistors, R, act as a unity gain buffer. The amplified voltage is measured between the REF and VOUT pins on the INA. The REF pin sets the reference point of the output voltage, and is typically chosen to match the ADC common-mode range. The INA gain is set by  $R_G$  and is determined by Equation 18:

$$G = 1 + (2 \cdot R_F) / R_G$$

(18)

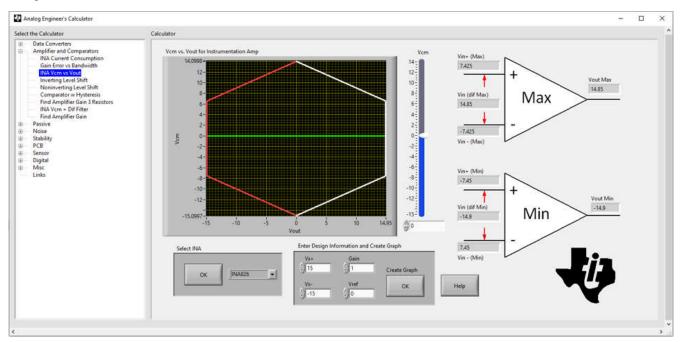

Most INAs are capable of large voltage gains up to 1000 V/V. However, one practical challenge associated with high gain is that it limits the input signal common-mode voltage to approximately mid-supply. In the INA topology, the input common-mode voltage must match the output common-mode of the first op amp stage comprised of A1 and A2 in Figure 5-1. As the voltage of R<sub>G</sub> is amplified to the output of A1 and A2, the output voltages of A1 and A2 are limited by how close those voltages are to either supply (V+ or V–). This limitation requires choosing the INA and bridge excitation supplies such that the bridge output is in the INA measurement range. The *INA Vcm vs Vout* tool in the Analog Engineer's Calculator simplifies this process by calculating the input common-mode range against the output voltage for a range of INAs. Figure 5-2 shows an example of this tool using the INA826.

Figure 5-2. INA Vcm vs Vout Tool in the Analog Engineer's Calculator

#### 5.1.1.2 INA Error Sources

Adding an INA into the signal path introduces several different errors. For example, the INA826 shown in Figure 5-2 has a gain error specification of  $\pm 0.04\%$  (typical) and  $\pm 0.15\%$  (maximum) when the gain is set to 100 V/V. This gain error results from slight mismatches in the factory trim of the resistor elements. The INA also has an offset error that is added to the measurement. The INA826 input-referred offset error is 150  $\mu$ V (maximum). Additionally, resistor  $R_G$  contributes some gain error that directly adds to the overall system error.

An INA also adds noise to the measurement. The INA826 input-referred noise is  $0.52~\mu V_{PP}$  in the 0.1-Hz to 10-Hz bandwidth. This noise may be greater than a PGA integrated into the ADC because of the INA topology. Refer to Section 5.2 for a more detailed discussion about the importance of noise in bridge measurements.

#### 5.1.2 Integrated PGA

Choose an ADC with an integrated PGA when  $V_{\text{EXCITATION}} \leq \text{AVDD}$ . These circumstances typically allow for a ratiometric reference configuration similar to the circuit described in Section 6.1. Integrated PGAs also generally offer better performance compared to external devices because integrated PGAs are optimized for use with the associated ADC.

### 5.1.2.1 Integrated PGA Architecture and Operation

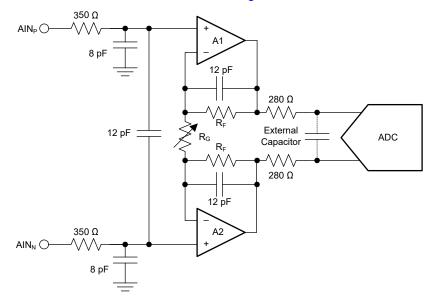

An integrated PGA is typically implemented as the front end of the basic INA. The circuit is similar to Figure 5-1 because it uses A1, A2, two  $R_F$  resistors, and a set of factory-trimmed, programmable  $R_G$  resistors that set the gain. As an example, the PGA in the ADS1235 is shown in Figure 5-3.

Figure 5-3. Simplified ADS1235 PGA Diagram

The PGA in Figure 5-3 also has low pass filters at both the input and output of the PGA. These filters help reduce sensitivity to electromagnetic interference (EMI). Some integrated PGAs also require an external capacitor that helps filter sample pulses caused by the modulator as well as perform anti-aliasing.

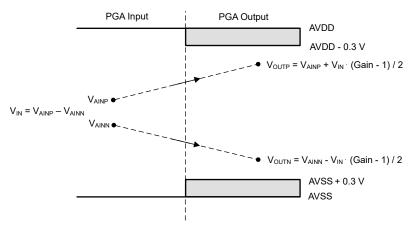

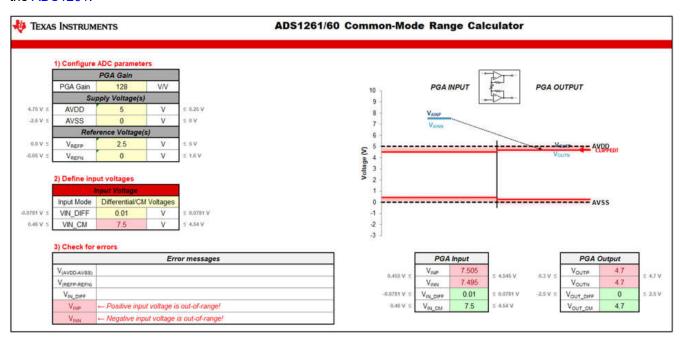

Similar to the INA, the integrated PGA has common-mode voltage requirements that are dictated by the gain and the output of the op amps. For example, the absolute input voltage ( $V_{AINP}$  or  $V_{AINN}$ ) for the PGA integrated into the ADS1235 is limited by Equation 19:

$$AVSS + 0.3 V + |V_{INMAX}| \cdot (Gain - 1) / 2 < V_{AINP}, V_{AINN} < AVDD - 0.3 V - |V_{INMAX}| \cdot (Gain - 1) / 2$$

(19)

where:

•  $V_{INMAX} = V_{AINP} - V_{AINN}$ , which describes the maximum differential input voltage.

Figure 5-4 graphically shows the relationship between the ADS1235 integrated PGA input to the PGA output.

Figure 5-4. Graphical Representation of the ADS1235 PGA Input and Output Range

The PGA output voltages ( $V_{OUTP}$  and  $V_{OUTN}$ ) in Figure 5-4 depend on the PGA gain and the input voltage magnitude,  $V_{IN}$ . For linear operation, the PGA output voltages must not exceed AVDD - 0.3 V or AVSS + 0.3 V. Note that Figure 5-4 depicts a positive differential input voltage that results in a positive differential output voltage, though negative differential voltages are also possible. See the ADS1235 Excel Calculator Tool for a common-mode input range calculator and other important design tools that help simplify projects using this ADC. Furthermore, the circuits in Section 6.3 and Section 6.6 demonstrate how to use these calculator tools to identify if the bridge output is within the PGA common-mode range.

### 5.1.2.2 Benefits of Using an Integrated PGA

One benefit of using an ADC with an integrated PGA is the integrated device does not require the output buffer difference amplifier in the INA solution (see Figure 5-1). Removing this component reduces the noise compared to using an external INA. For example, the INA826 has  $0.52-\mu V_{PP}$  input-referred noise from 0.1 Hz to 10 Hz, while the ADS1235 noise at 10 samples per second (SPS) using the FIR filter is  $0.096 \, \mu V_{PP}$ .

Another benefit of the integrated PGA is that the gain is factory-trimmed. This process typically results in much less error compared to the combined gain error of the INA and external  $R_{\rm G}$ . For example, the typical gain error of the ADS1235 is 0.05%. While the INA826 gain error is 0.04%, this does not include any additional gain error from  $R_{\rm G}$ . For example, choosing an  $R_{\rm G}$  resistor that has an initial tolerance of 0.1% more than doubles the gain error compared to using the ADS1235 integrated PGA.

#### 5.2 Noise

In data acquisition systems, noise is any unwanted signal that can interfere with or hide the signal of interest. Some noise is inherent to all electrical components, and it can come from sources internal (amplifiers, ADCs, voltage references, and so forth) or external (EMI, ground loops, line-cycle noise, and so forth) to the system. Noise is very important for bridge measurement systems because the bridge output voltage is typically on the order of 10s of millivolts. Such small signals require a low-noise, higher-resolution signal chain to achieve high dynamic range.

Even though noise is important for bridge measurement systems, complete signal chain noise analysis can be complex. As such, a comprehensive understanding of noise is beyond the scope of this application note. Instead, this document identifies how noise is reported in an ADC data sheet and how this information can be used to help achieve design targets for bridge measurement systems. For more information on noise in ADC measurements, see the *Fundamentals of Precision ADC Noise Analysis* e-book as well as the *ADC Noise* content in TI's Precision Labs training curriculum.

#### 5.2.1 Noise in an ADC Data Sheet

ADC data sheets typically report noise with the inputs shorted ( $V_{IN} = 0 \text{ V}$ ). This configuration provides the purest measurement of ADC intrinsic noise, which also includes amplifier noise if the ADC has an integrated PGA. This measurement does not include voltage reference noise, which scales linearly with the input signal. However, this is generally not a concern for bridge measurement systems that use a ratiometric reference configuration where the voltage reference noise and drift tend to cancel out.

The actual values shown in an ADC noise table are comprised of several thousand data points or several seconds worth of data. Statistical analysis is performed on this data set to determine root-mean-square (RMS) and peak-to-peak values. For delta-sigma ADCs, this information is then reported for each combination of output data rate (ODR), filter type, and gain setting (if applicable).

For example, Table 5-1 shows a portion of the noise performance information from the ADS1235 data sheet. Each row in Table 5-1 is a different ODR and filter type combination while each column represents the available PGA gains.

Table 5-1. ADS1235 Noise and Resolution at  $T_A = 25^{\circ}$ C and  $V_{REF} = 5 \text{ V}$

| ODR    | FILTER | Noise (μV <sub>RMS</sub> (μV <sub>PP</sub> )) |               | Effective Resolution (bits)(Noise-Free Resolution (bits)) |             |             |             |

|--------|--------|-----------------------------------------------|---------------|-----------------------------------------------------------|-------------|-------------|-------------|

|        |        | GAIN = 1                                      | GAIN = 64     | GAIN = 128                                                | GAIN = 1    | GAIN = 64   | GAIN = 128  |

| 20 SPS | FIR    | 0.51 (2.1)                                    | 0.032 (0.16)  | 0.029 (0.16)                                              | 24 (22)     | 22.2 (19.9) | 21.3 (18.9) |

| 20 SPS | Sinc1  | 0.44 (2.1)                                    | 0.025 (0.13)  | 0.026 (0.13)                                              | 24 (22)     | 22.6 (20.2) | 21.5 (19.2) |

| 20 SPS | Sinc2  | 0.36 (1.2)                                    | 0.02 (0.12)   | 0.02 (0.1)                                                | 24 (22.8)   | 22.9 (20.4) | 21.9 (19.5) |

| 20 SPS | Sinc3  | 0.32 (1.5)                                    | 0.017 (0.089) | 0.018 (0.096)                                             | 24 (22.5)   | 23.1 (20.8) | 22 (19.6)   |

| 20 SPS | Sinc4  | 0.3 (1.2)                                     | 0.017 (0.084) | 0.018 (0.1)                                               | 24 (22.8)   | 23.1 (20.8) | 22.1 (19.6) |

| 50 SPS | Sinc1  | 0.63 (3.6)                                    | 0.04 (0.25)   | 0.038 (0.23)                                              | 23.7 (21.2) | 21.9 (19.2) | 21 (18.4)   |

| 50 SPS | Sinc2  | 0.57 (3)                                      | 0.033 (0.21)  | 0.032 (0.18)                                              | 23.9 (21.5) | 22.2 (19.5) | 21.2 (18.7) |

| 50 SPS | Sinc3  | 0.53 (2.4)                                    | 0.03 (0.19)   | 0.03 (0.17)                                               | 24 (21.8)   | 22.3 (19.7) | 21.3 (18.8) |

| 50 SPS | Sinc4  | 0.49 (2.4)                                    | 0.028 (0.15)  | 0.026 (0.16)                                              | 24 (21.8)   | 22.4 (20)   | 21.5 (18.9) |

| 60 SPS | Sinc1  | 0.71 (3.9)                                    | 0.043 (0.27)  | 0.042 (0.26)                                              | 23.6 (21.1) | 21.8 (19.1) | 20.8 (18.2) |

| 60 SPS | Sinc2  | 0.6 (3.3)                                     | 0.036 (0.24)  | 0.034 (0.21)                                              | 23.8 (21.4) | 22.1 (19.3) | 21.1 (18.5) |

| 60 SPS | Sinc3  | 0.56 (3)                                      | 0.032 (0.19)  | 0.03 (0.17)                                               | 23.9 (21.5) | 22.2 (19.6) | 21.3 (18.8) |

| 60 SPS | Sinc4  | 0.53 (2.7)                                    | 0.031 (0.19)  | 0.03 (0.18)                                               | 24 (21.6)   | 22.3 (19.7) | 21.3 (18.7) |

The noise values in Table 5-1 are referred to the input (RTI). The RTI noise of the ADC measurement is the magnitude of the equivalent noise as seen at the input of the ADC after gain. For example, the noise in Table 5-1 is referred to a  $\pm$ 5-V range when the gain = 1 V/V. When gain = 128 V/V, the noise is referred to a significantly smaller  $\pm$ 39.06-mV range.

Table 5-1 also includes two figures of merit derived from the noise values: *effective resolution* and *noise-free resolution*. Effective resolution in an ADC data sheet is the dynamic range of the full-scale range (FSR) relative to the RMS noise in the measurement,  $V_{N,RMS}$ . Comparatively, noise-free resolution in an ADC data sheet is the dynamic range of the FSR relative to the peak-to-peak (PP) noise in the measurement,  $V_{N,PP}$ . These noise parameters are calculated using Equation 20 and Equation 21:

Effective resolution =

$$log_2(FSR / V_{N,RMS})$$

(bits) (20)

Noise-free resolution =

$$log_2(FSR / V_{NPP})$$

(bits) (21)

For example, at gain = 128 V/V and ODR = 20 SPS, Table 5-1 shows that the ADS1235 finite impulse response (FIR) digital filter offers noise performance of 0.029  $\mu$ V<sub>RMS</sub> or 0.16  $\mu$ V<sub>PP</sub>. Equation 22 and Equation 23, respectively, calculate the ADS1235 effective resolution and noise-free resolution at these settings:

Effective resolution =

$$log_2[(\pm 5 \text{ V} / 128 \text{ V/V}) / (0.029 \,\mu\text{V}_{RMS})] = log_2[2,693,966] = 21.3 \,\text{bits}$$

(22)

Noise-free resolution =

$$\log_2[(\pm 5 \text{ V} / 128 \text{ V/V}) / (0.16 \text{ µV}_{PP})] = \log_2[488,281] = 18.9 \text{ bits}$$

(23)

Note that the results in Equation 22 and Equation 23 match the reported values in the last column of Table 5-1.

Bridge measurements often characterize performance using a third parameter called noise-free counts (NFC), which is derived from noise-free resolution. This is especially important for weigh scale applications where the design requires that the smallest digit displayed in the scale measurement is stable (or noise-free). Designing a weigh scale using effective resolution targets would likely result in the last digit on the scale constantly moving because effective resolution is based on the RMS noise.

NFC is defined by Equation 24 while Equation 25 calculates NFC for the given ADC parameters:

$$NFC = 2^{\text{(Noise-free resolution)}} \text{ (counts)}$$

NFC =

$$2^{(18.9)}$$

= 488,000 counts (25)

A weigh scale with level of performance described in Equation 25 might be acceptable, though it is important to consider how this parameter is defined. Specifically, noise-free resolution and NFC are calculated assuming that the ADC input uses the entire FSR. However, if the weigh scale system does not use the entire ADC FSR, the system NFC performance will be different than the values shown in the ADC noise table. This reduction in NFC performance is described in the following section.

### 5.2.2 Calculating NFC for a Bridge Measurement System

As described in Section 4.1, a bridge sensitivity of 2 mV/V and  $V_{\text{EXCITATION}} = 5 \text{ V}$  yields a maximum bridge output signal of 10 mV. Furthermore, the minimum weight measured by a weigh scale is zero, resulting in a minimum bridge output signal of 0 V. Therefore, the bridge output signal range is 0 to 10 mV, which is significantly smaller than the FSR of most ADCs even at the highest gain. For example, the ADS1235 FSR at a gain of 128 V/V was given as  $\pm 39 \text{ mV}$  in the previous section. As such, a 0- to 10-mV input signal uses approximately one-eighth of the ADC FSR.

Substitute the *system signal range* for the ADC FSR in Equation 21 to calculate the expected noise-free resolution for a given bridge measurement design. Equation 26 returns the noise-free resolution for the 0- to 10-mV weigh scale signal range using the ADS1235 at gain = 128 V/V, ODR = 20 SPS, and the FIR filter (assuming a ratiometric 5-V V<sub>REF</sub>):

Noise-free resolution<sub>(System)</sub> =

$$log_2[(10 \text{ mV}) / (0.16 \mu V_{PP})] = log_2[62,500] = 15.9 \text{ bits}$$

(26)

Applying the result of Equation 26 to Equation 24 yields a new value for NFC shown in Equation 27:

$$NFC_{(System)} = 2^{(15.9)} = 63,000 \text{ counts}$$

(27)

Regardless of the construction of the measurement system, this noise analysis yields the noise floor of the final system. Moreover, the results from Equation 27 help determine if the ADC is sufficient to meet the target design specifications. If the NFC value is insufficient, selecting a different measurement configuration, a higher-precision ADC, or averaging the data output may reduce the noise to an acceptable level.

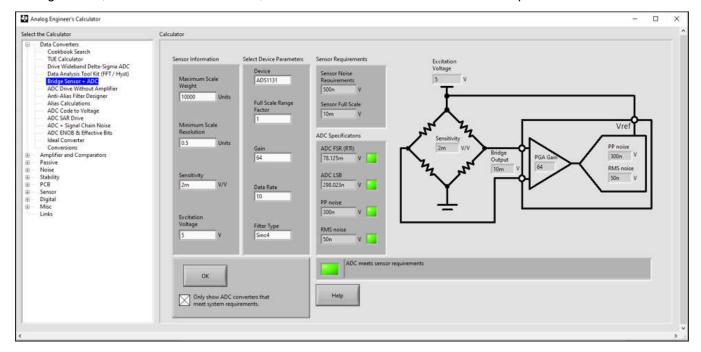

To help determine if an ADC can meet the target design specifications, use the *Bridge Sensor + ADC* tool in the Analog Engineer's Calculator. Figure 5-5 introduces this tool and shows how it can be used. Enter the system requirements on the left and the tool returns available ADC options that meet the design goals. Converting voltage to bits, bits to effective resolution, or bits to noise-free resolution can also be performed.

Figure 5-5. Bridge Sensor + ADC Tool in the Analog Engineer's Calculator

### 5.3 Channel Scan Time and Signal Bandwidth

In addition to low noise, bridge measurement systems often have channel scan time or input signal bandwidth requirements that can be affected by the ADC architecture. These applications typically use precision delta-sigma ( $\Delta\Sigma$ ) ADCs because they can offer resolution up to 32 bits and integrated PGAs. Precision  $\Delta\Sigma$  ADCs use an oversampling topology where the input signal is sampled at a high frequency and converted to a digital bitstream by the  $\Delta\Sigma$  ADC modulator. This bitstream is then filtered and decimated by the oversampling ratio (OSR) in the digital domain to yield a low-noise conversion result at the respective ODR.

The output noise depends on the OSR, where a larger OSR (or lower ODR) results in more data collected over a longer period of time and therefore lower noise. However, this also leads to extended ADC conversion latency and lower input signal bandwidth, though it may be possible to filter out line-cycle noise at lower data rates. The following subsections discuss these topics in more detail.

#### 5.3.1 Noise Performance

As stated in the previous section, the  $\Delta\Sigma$  ADC digital filter directly affects the system noise performance by taking data over a longer period of time as OSR increases (ODR decreases). This allows for lower measurement noise at lower data rates. Table 5-1 shows how the ADS1235 noise tends to reduce as ODR decreases.

It may also be possible to use external oversampling techniques to further reduce noise. If N number of ADC data points are collected and averaged by a microcontroller, the noise can be reduced by a factor of  $\sqrt{N}$ . For example, the ADS1235 noise at gain = 128 V/V, FIR filter, and ODR = 20 SPS is given in Table 5-1 as 0.029  $\mu V_{RMS}$  and 0.16  $\mu V_{PP}$ . Averaging 20 data points reduces the noise by a factor of  $\sqrt{20}$  = 4.47 to 0.0065  $\mu V_{RMS}$  and 0.036  $\mu V_{PP}$ , respectively. However, the tradeoff to applying additional averaging is longer latency.

### 5.3.2 ADC Conversion Latency

One consequence of the digital filter is that it introduces some latency between the start of conversion and the final result. As previously stated, the  $\Delta\Sigma$  ADC modulator output is collected over a specific period of time and the digital filter calculates the ADC data. Depending on the filter construction as well as other factors, the final ADC conversion data can be delayed by several conversion periods.

To quantify this delay, many precision  $\Delta\Sigma$  ADCs include a conversion latency table in the data sheet. For example, Table 5-2 reports the ADS1235 conversion latency across all filter types (FIR and sinc) and ODRs.

| ODR (SPS) | CONVERSION LATENCY <sup>(1)</sup> - t <sub>(STDR)</sub> (ms) |       |       |       |       |  |  |

|-----------|--------------------------------------------------------------|-------|-------|-------|-------|--|--|

| ODR (SPS) | FIR                                                          | SINC1 | SINC2 | SINC3 | SINC4 |  |  |

| 2.5       | 402.2                                                        | 400.4 | 800.4 | 1,200 | 1,600 |  |  |

| 5         | 202.2                                                        | 200.4 | 400.4 | 600.4 | 800.4 |  |  |

| 10        | 102.2                                                        | 100.4 | 200.4 | 300.4 | 400.4 |  |  |

| 16.6      | _                                                            | 60.43 | 120.4 | 180.4 | 240.4 |  |  |

| 20        | 52.23                                                        | 50.43 | 100.4 | 150.4 | 200.4 |  |  |

| 50        | _                                                            | 20.43 | 40.43 | 60.43 | 80.43 |  |  |

| 60        | _                                                            | 17.09 | 33.76 | 50.43 | 67.09 |  |  |

| 100       | _                                                            | 10.43 | 20.43 | 30.43 | 40.43 |  |  |

| 400       | _                                                            | 2.925 | 5.425 | 7.925 | 10.43 |  |  |

| 1200      | _                                                            | 1.258 | 2.091 | 2.925 | 3.758 |  |  |

| 2400      | _                                                            | 0.841 | 1.258 | 1.675 | 2.091 |  |  |

| 4800      | _                                                            | 0.633 | 0.841 | 1.05  | 1.258 |  |  |

| 7200      | _                                                            | 0.564 | 0.702 | 0.841 | 0.98  |  |  |

Table 5-2. ADS1235 Conversion Latency

Table 5-2 shows that the FIR filter has a latency of approximately one conversion period, or about 50 ms, when ODR = 20 SPS for example. Table 5-2 also shows that the ADS1235 has sinc filters from first to fourth order. The sinc filter is the equivalent of a moving average filter of the previous data periods. For example, the sinc<sup>3</sup> filter is a third-order filter using a moving average of the previous three data points. Therefore, first data does not

<sup>(1)</sup> Chop mode off, conversion-start delay = 50 μs (DELAY[3:0] = 0001)

appear until after the first three conversion periods, resulting in a latency of approximately 150 ms when ODR = 20 SPS. Second and subsequent conversion data may appear after the next conversion period depending on the conversion mode. Refer to the application note explaining  $\Delta\Sigma$  ADC conversion latency for more detailed information on this topic.

Ultimately, bridge measurement systems requiring fast channel scan time or switching between multiple channels should always consider how ODR and digital filter type affect ADC conversion latency.

### 5.3.3 Digital Filter Frequency Response

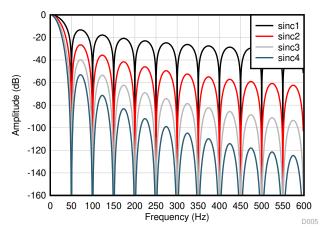

Digital filters also have a specific frequency response that can affect how the signal is converted by the ADC. This response depends on the frequency of the input signal because the digital filter is collecting modulator outputs over a period of time. Figure 5-6 shows the frequency response of the different sinc filters in the ADS1235 at ODR = 50 SPS.

Figure 5-6. ADS1235 Sinc Filter Frequency Responses at ODR = 50 SPS

While not shown in Figure 5-6, the bandwidth of the ADS1235 sinc filters is significantly lower than the ODR. For example, the sinc<sup>1</sup> cutoff frequency is only 22.1 Hz at ODR = 50 SPS. Therefore, bridge measurement systems that need to sample signals with higher frequency components require a higher ODR or a wider bandwidth digital filter. Refer to the *Digital Filter Types in Delta-Sigma ADCs* application note for more detailed information on this topic.

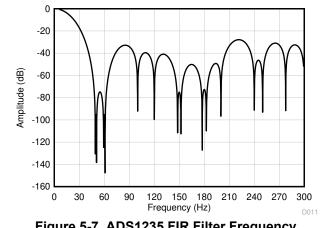

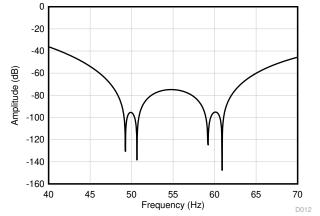

Another consideration of the digital filter frequency response is the rejection of specific frequencies. Figure 5-7 shows the frequency response for the ADS1235 FIR filter at ODR = 20 SPS, while Figure 5-8 zooms in on the response at 50 and 60 Hz.

Figure 5-7. ADS1235 FIR Filter Frequency Response at ODR = 20 SPS

Figure 5-8. ADS1235 FIR Frequency Response

Detail at ODR = 20 SPS

As Figure 5-8 shows, this digital filter frequency response is designed to reject 50-Hz and 60-Hz frequencies. For example, the ADS1235 attenuates an input signal at 50 Hz or 60 Hz (with up to a ±2 Hz deviation) by 94 dB. This is particularly useful to reduce line-cycle noise in the system. Moreover, the ADC digital filter can help reject this noise whether it couples in from the system supply or comes from other line-induced EMI.

### 5.4 AC Excitation

In addition to low noise, bridge measurement systems typically require high accuracy. As discussed in Section 4.4, AC excitation is one solution to remove offset error from a bridge measurement. This method is similar to amplifier chopping where the input channel is swapped between the positive and negative inputs. However, AC excitation swaps the polarity of V<sub>EXCITATION</sub> between the top (Phase 1) and bottom (Phase 2) of the bridge. The ADC measures the output of the bridge during both phases, subtracts the Phase 2 measurement from the Phase 1 measurement, and averages the result. This process cancels any systemic offsets after the bridge that can be caused by parasitic thermocouples or external amplifier offsets for example. This technique produces a measured result that is just the bridge output voltage.

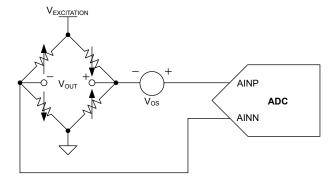

Figure 5-9 shows an ADC bridge measurement during Phase 1 where  $V_{\text{EXCITATION}}$  is at the top of the bridge, the bottom of the bridge is grounded, and an offset ( $V_{\text{OS}}$ ) is shown as a source voltage between the bridge and the ADC.

Figure 5-9. Bridge Measurement During AC Excitation (Phase 1)

Equation 28 calculates the voltage measured by the ADC during Phase 1:

Phase 1 = AINP – AINN =

$$+V_{OUT} + V_{OS}$$

(28)

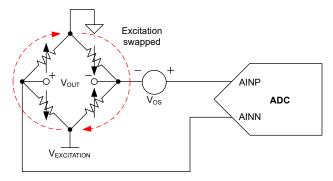

After the first ADC measurement completes, Phase 2 swaps the bridge polarity such that  $V_{\text{EXCITATION}}$  is routed to the bottom of the bridge and the top of the bridge is grounded. This swapping inverts the output voltage while maintaining the polarity of  $V_{\text{OS}}$ . The Phase 2 configuration is shown in Figure 5-10.

Figure 5-10. Bridge Measurement During AC Excitation (Phase 2)

Equation 29 calculates the voltage measured by the ADC during Phase 2:

Phase 2 = AINP – AINN =

$$-V_{OUT} + V_{OS}$$

(29)

Subtracting the result of Equation 29 from Equation 28 and dividing by two yields Equation 30:

$$(\text{Phase 1 - Phase 2}) / 2 = [(+V_{\text{OUT}} + V_{\text{OS}}) - (-V_{\text{OUT}} + V_{\text{OS}})] / 2 = V_{\text{OUT}}$$

(30)

Ultimately, Equation 30 shows that  $V_{OS}$  cancels out and the final result is just  $V_{OUT}$ , thereby removing the total offset error after the bridge. However, it is important to note that systemic offsets that occur inside the bridge or before the chopping circuitry are not removed by AC excitation. Instead, use calibration to remove the inherent bridge offset.

Implementing AC excitation requires external transistors, gate drivers, or other switches to swap the bridge excitation voltage polarity. General purpose outputs (GPOs) from the ADC or host typically control the switching, and should be implemented with non-overlapping clocks to prevent bridge cross-conduction during voltage reversal.

Several TI precision ADCs are designed to implement AC excitation. The ADS1235 has specific pins to control external switches that swap the bridge polarity. For more information about implementing AC excitation for bridge measurements, see the *Reduce Bridge Measurement Offset and Drift Using the AC Excitation Mode* application note.

### 5.5 Calibration

Achieving high-accuracy results from a bridge measurement system can require calibration. Choose one of three calibration methods depending on the overall accuracy requirements:

- A one-point offset error calibration easy to implement, offers some accuracy improvement

- · A two-point offset and gain error calibration improved accuracy, requires two measurements

- A piecewise-linear calibration highest accuracy, ideal for nonlinear systems and calibration over temperature, requires several calibration points or a look-up table (LUT)

This document focuses on the two-point calibration method because it can significantly improve the system accuracy through a relatively simple calibration process.

The first step of a two-point calibration calculates the offset error, while the second step uses a test load to determine the gain error. A two-point calibration assumes that both the bridge response and the ADC measurement are linear. This assumption helps the user determine how the actual measurements deviate from the ideal measurements using the equation for a line:

$$y = M \cdot x + B \tag{31}$$

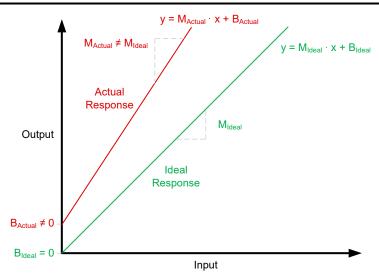

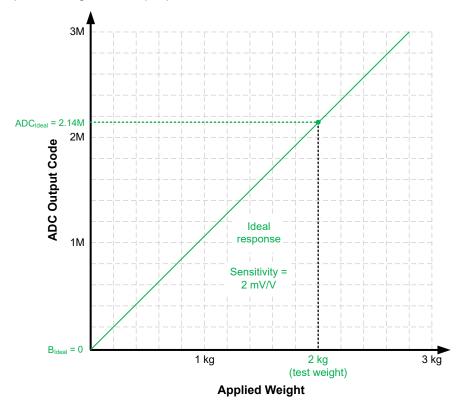

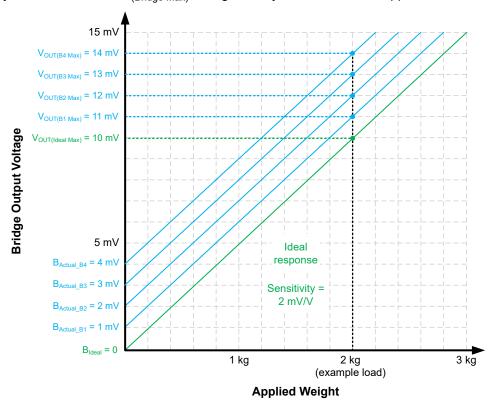

Figure 5-11 plots the ideal response of a bridge measurement with a green line that has some slope ( $M_{Ideal}$ ) and y-intercept ( $B_{Ideal}$ ) that is equal to zero. Comparatively, the actual bridge measurement response in red has a slope ( $M_{Actual}$ ) that is not equal to  $M_{Ideal}$  as well as a nonzero y-intercept ( $B_{Actual}$ ).

Figure 5-11. Bridge Measurement Response: Ideal vs Actual

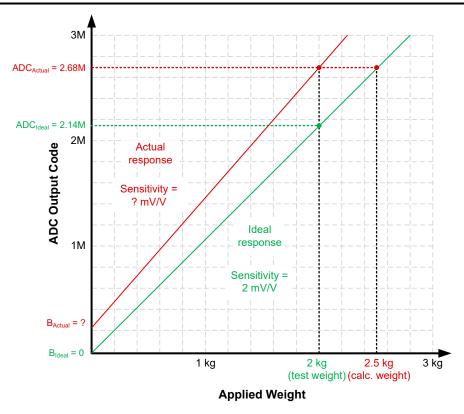

The calibration process calculates the values of B<sub>Actual</sub> and a scaling factor related to M<sub>Actual</sub> in Figure 5-11, which helps remove the offset error and gain error, respectively. Figure 5-11 specifically shows a positive offset and gain error, though it is possible for one or both of these errors to be negative. This information is then used to accurately correlate the system input to the ADC output. For example, Figure 5-12 shows how calibration might be implemented for a weigh scale system.

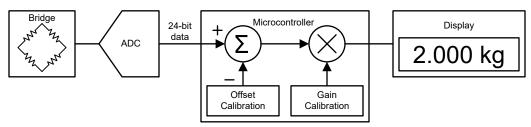

Figure 5-12. Block Diagram for a Weigh Scale Application with Calibration

In Figure 5-12, an ADC measures a bridge using a ratiometric configuration. A microcontroller captures the data from the ADC, then calculates and stores the calibration values. The offset calibration stores a value for  $B_{Actual}$ , while the gain calibration stores a scaling factor, M, that is related to  $M_{Actual}$ . The microcontroller then subtracts  $B_{Actual}$  from the ADC measurement and scales the result by M. Finally, a display shows the calculated result.

The following two subsections step through the offset and gain calibration process for a generic bridge system that might measure physical parameters such as weight, pressure, or flow. The final subsection applies this information to an example calculation for the weigh scale system shown in Figure 5-12.

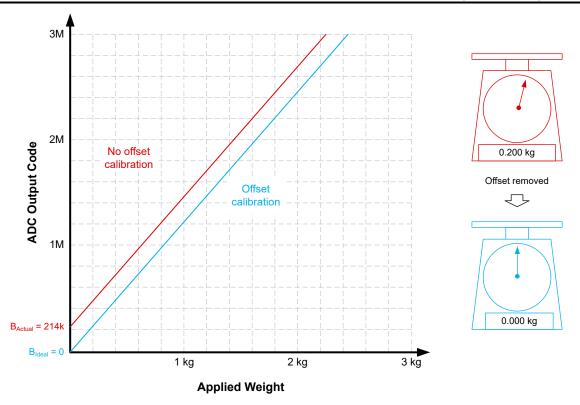

#### 5.5.1 Offset Calibration

The first calibration step is to measure and remove the offset voltage. Offset may come from an inherent bridge imbalance, from the signal conditioning circuitry, or both. Offset is the measured value that represents zero applied load, and can be either positive or negative. During an offset calibration, the ADC measures the system output with no applied load. The resulting ADC code is stored as the offset calibration constant. The microcontroller subtracts this offset value from subsequent ADC measurements before calculating the measured weight. Note that the offset measurement itself has some noise. Reduce the noise of the stored offset voltage by averaging multiple consecutive offset measurements.

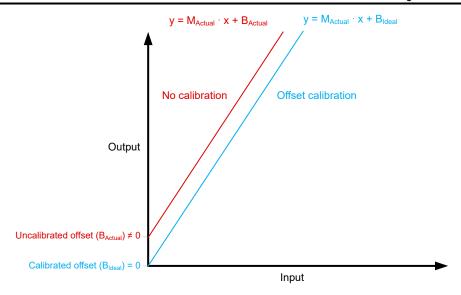

Figure 5-13 shows how an offset calibration changes the bridge measurement response before (red) and after (blue) the calibration process.

Figure 5-13. First Calibration Step Calculates and Remove Offset (Bactual)

Figure 5-13 reveals that the purpose of an offset calibration is to measure the y-axis intercept ( $B_{Actual}$ ) of the uncalibrated response. This value is then removed from the final result so that the system output is zero with no load applied, similar to  $B_{Ideal}$ . The calibration process therefore shifts the bridge measurement response from the red, uncalibrated plot to the blue, calibrated plot. This first step describes a one-point calibration as per Section 5.5.

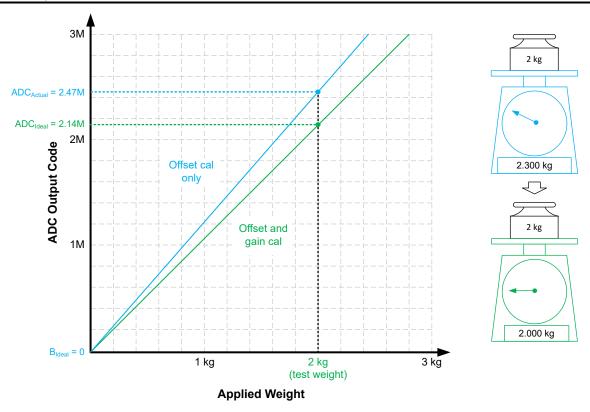

One important characteristic of both plots in Figure 5-13 is that the blue, calibrated response has the same slope ( $M_{Actual}$ ) as the red, uncalibrated response. In other words, the blue, calibrated response can still have a significant gain error compared to the green, ideal response from Figure 5-11. The second calibration step corrects this issue by calculating the slope of the actual bridge response to help determine the gain error.

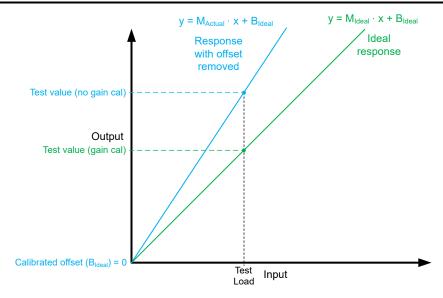

### 5.5.2 Gain Calibration

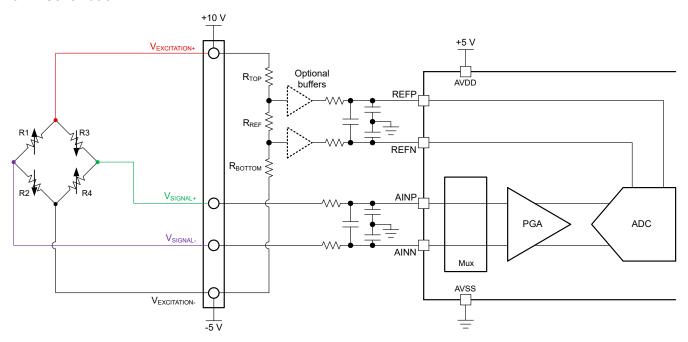

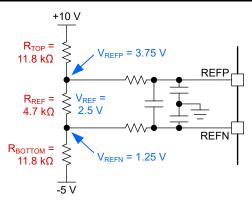

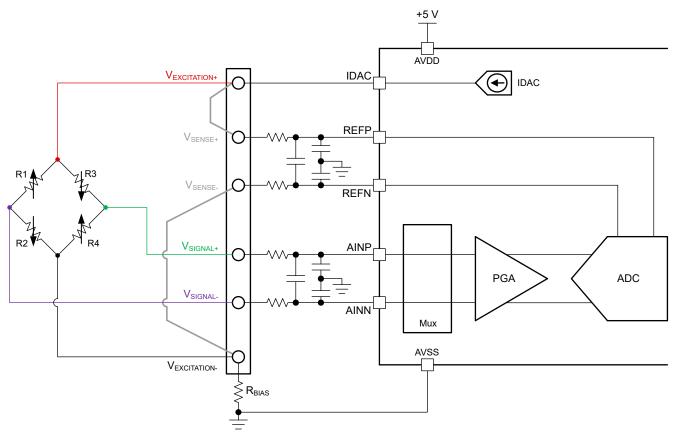

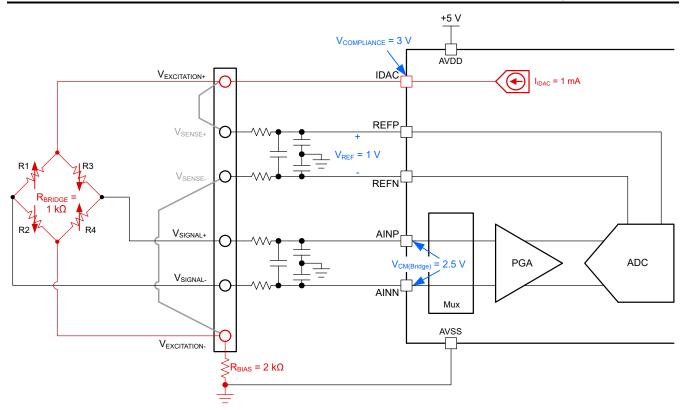

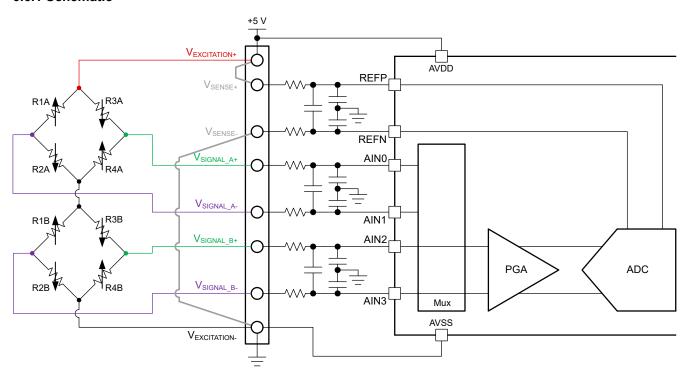

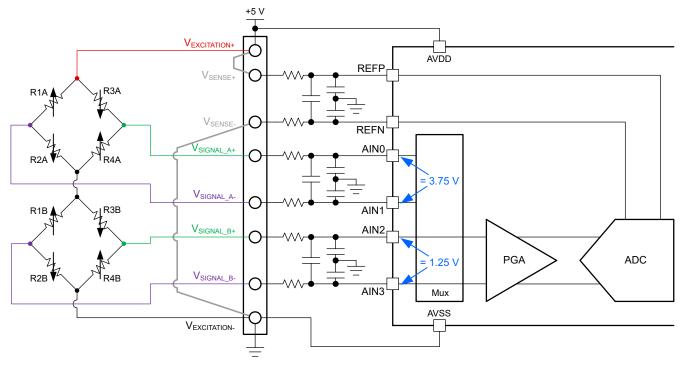

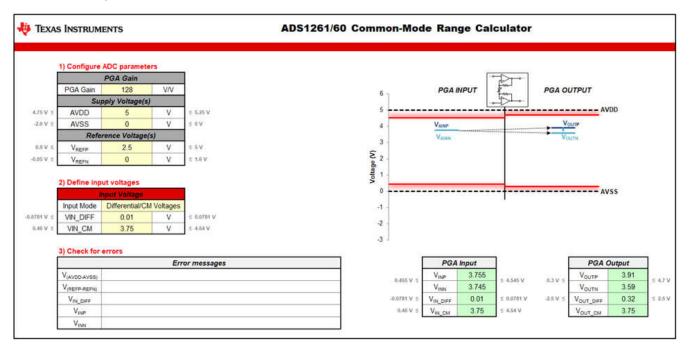

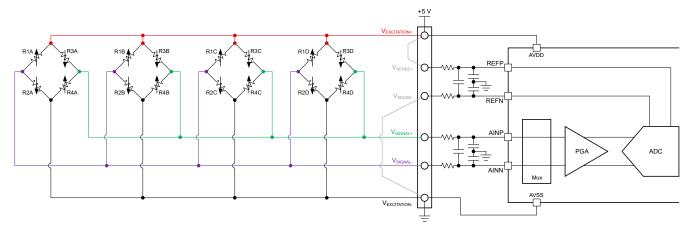

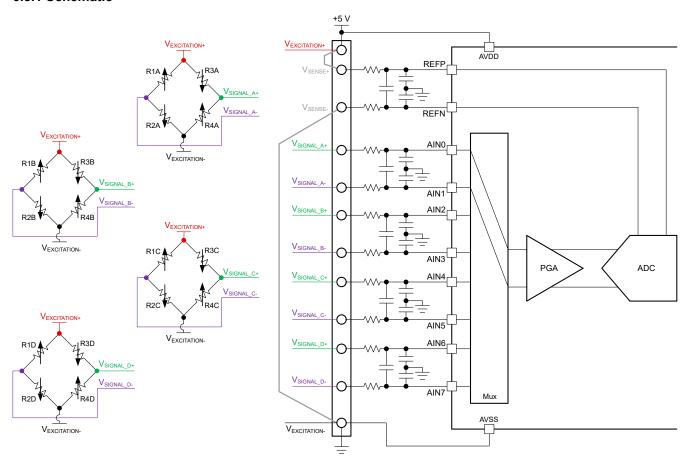

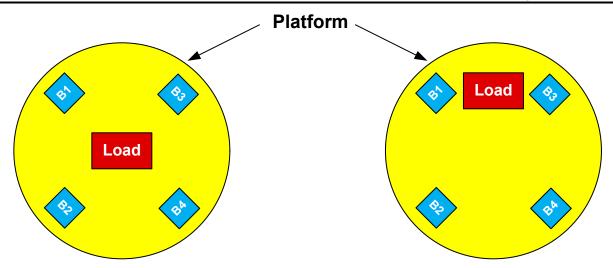

After completing offset calibration, correct any gain error by first applying a calibrated test load to the system. For example, a weigh scale would use a calibrated weight. This test load does not necessarily need to be the maximum load of the measurement system. Instead, the test load should be large enough to accurately determine the slope of the bridge measurement response over the target measurement range. Typically, choosing a test load that is 80% or more of the target measurement range is sufficient. A scaling factor relative to the slope of the bridge measurement response is then stored in the microcontroller as the gain calibration coefficient. Similar to offset calibration, gain calibration measurements have noise that can be reduced by averaging multiple ADC samples.